JP5372002B2 - メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス - Google Patents

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス Download PDFInfo

- Publication number

- JP5372002B2 JP5372002B2 JP2010533058A JP2010533058A JP5372002B2 JP 5372002 B2 JP5372002 B2 JP 5372002B2 JP 2010533058 A JP2010533058 A JP 2010533058A JP 2010533058 A JP2010533058 A JP 2010533058A JP 5372002 B2 JP5372002 B2 JP 5372002B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- mesa

- conductivity type

- buffer layer

- emitter

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

- H10D10/40—Vertical BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D12/00—Bipolar devices controlled by the field effect, e.g. insulated-gate bipolar transistors [IGBT]

- H10D12/01—Manufacture or treatment

- H10D12/031—Manufacture or treatment of IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/102—Constructional design considerations for preventing surface leakage or controlling electric field concentration

- H10D62/103—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices

- H10D62/104—Constructional design considerations for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse-biased devices having particular shapes of the bodies at or near reverse-biased junctions, e.g. having bevels or moats

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/13—Semiconductor regions connected to electrodes carrying current to be rectified, amplified or switched, e.g. source or drain regions

- H10D62/133—Emitter regions of BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/83—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge

- H10D62/832—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group IV materials, e.g. B-doped Si or undoped Ge being Group IV materials comprising two or more elements, e.g. SiGe

- H10D62/8325—Silicon carbide

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D10/00—Bipolar junction transistors [BJT]

- H10D10/01—Manufacture or treatment

- H10D10/051—Manufacture or treatment of vertical BJTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D18/00—Thyristors

- H10D18/01—Manufacture or treatment

- H10D18/031—Manufacture or treatment of lateral or planar thyristors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0297—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the gate electrodes, e.g. to form trench gate electrodes

Landscapes

- Bipolar Transistors (AREA)

- Electrodes Of Semiconductors (AREA)

- Thyristors (AREA)

Description

本出願は、2007年11月9日出願の「SILICON CARBIDE BIPOLAR JUNCTION TRANSISTOR」という名称の米国特許仮出願第60/986,694号明細書の利益および優先権を主張する。同出願の開示は、参照によりその全体を本明細書に組み込む。

本発明は、Army Research Laboratoryにより授与された契約番号W911NF−04−2−0022のもとに政府の支援でなされた。政府は本発明に一定の権利を有する。

Claims (15)

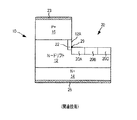

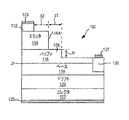

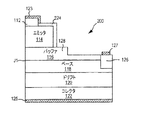

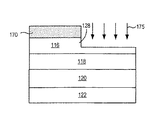

- 第1の導電型を有するコレクタと、

前記コレクタ上の、前記第1の導電型を有するドリフト層と、

前記ドリフト層上の、前記第1の導電型と反対の第2の導電型を有するベース層と、

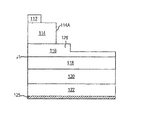

前記ベース層上の、前記第1の導電型を有し前記ベース層とp−n接合部を形成するバッファ層であって、前記ベース層のドーピング濃度よりも低いドーピング濃度を有するバッファ層と、

前記バッファ層上の、前記第1の導電型を有し側壁を有するエミッタメサと、

前記バッファ層を貫通して前記ベース層の中へと延びるベースコンタクト領域であって、第2の導電型を有し、かつ前記ベース層のドーピング濃度よりも高いドーピング濃度を有する前記ベースコンタクト領域と

を備え、

前記バッファ層は、前記エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を備え、前記エミッタメサの下の前記バッファ層の第1の厚さは、前記メサ段差外側の前記バッファ層の第2の厚さよりも厚いことを特徴とするバイポーラ接合トランジスタ。 - 前記エミッタメサ上の局所エミッタコンタクト領域であって、第1の導電型を有し、前記エミッタメサのドーピング濃度よりも高いドーピング濃度を有し、前記エミッタメサの側壁から横方向に間隔を置いて配置されたエミッタコンタクト領域と、

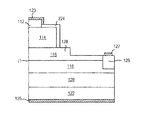

前記局所エミッタコンタクト領域上のエミッタオーミックコンタクトと

をさらに備えることを特徴とする請求項1に記載のバイポーラ接合トランジスタ。 - 前記エミッタメサの側壁上の、前記局所エミッタコンタクト領域と前記バッファ層の両方に接触するように延びる導電層をさらに備え、前記エミッタオーミックコンタクトは、前記導電層とオーミックコンタクトを形成することを特徴とする請求項2に記載のバイポーラ接合トランジスタ。

- 前記局所エミッタコンタクト領域は、前記エミッタメサの側壁から2μm以上の間隔で配置されることを特徴とする請求項2に記載のバイポーラ接合トランジスタ。

- 前記ベース層の申に延びるベースコンタクト領域であって、第2の導電型を有し、前記ベース層のドーピング濃度よりも高いドーピング濃度を有するベースコンタクト領域と、

前記ベースコンタクト領域上のベースオーミックコンタクトと

をさらに備えることを特徴とする請求項4に記載のバイポーラ接合トランジスタ。 - 前記ベースコンタクト領域上のベースオーミックコンタクトをさらに備えることを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

- 前記メサ段差は、0.3μm以下の高さを有することを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

- 前記メサ段差は、前記エミッタメサの側壁から2μm以上の間隔で配置されることを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

- 前記バッファ層は、前記エミッタメサのドーピング濃度よりも低いドーピング濃度を有することを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

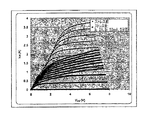

- 前記バッファ層は、前記バッファ層と前記ベース層の間のp−n接合部のビルトイン電位によって前記バッファ層の、前記第2の厚さを有する部分が完全に空乏化されるように選択されたドーピング濃度を有することを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

- 前記コレクタ、前記ドリフト層、前記ベース層、前記バッファ層および前記エミッタメサは炭化ケイ素を含むことを特徴とする請求項1に記載のバイポーラ接合トランジスタ。

- 第1の導電型を有する第1の層と、

前記第1の層上の第2の層であって、前記第1の導電型と反対の第2の導電型を有し、前記第1の層の第1のドーピング濃度よりも高い第2のドーピング濃度を有する第2の層と、

前記第2の層上の、前記第1の導電型を有し前記第2の層とp−n接合部を形成する第3の層であって、前記第2の層の前記第2のドーピング濃度よりも低い第3のドーピング濃度を有する第3の層と、

前記第3の層上の、前記第1の導電型を有し側壁を有するメサと、

前記第3の層を貫通して第2の層の中へと延びるコンタクト領域であって、第2の導電型を有し、かつ前記第2の層のドーピング濃度よりも高いドーピング濃度を有する前記コンタクト領域と

を備え、

前記第3の層は、前記メサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を備え、前記メサの下の前記第3の層の第1の厚さは、前記メサ段差外側の前記第3の層の第2の厚さよりも厚いことを特徴とする電力半導体デバイス。 - 前記メサ上のコンタクト領域であって、第1の導電型を有し、前記メサの第5のドーピング濃度よりも高い第4のドービング濃度を有し、前記メサの側壁から横方向に間隔を置いて配置されたコンタクト領域と、

前記コンタクト領域上のオーミックコンタクトと

をさらに備えることを特徴とする請求項12に記載の電力半導体デバイス。 - 前記メサの側壁上の、前記コンタクト領域と前記第3の層の両方に接触するように延びる導電層をさらに備え、前記オーミックコンタクトは、前記導電層とオーミックコンタクトを形成することを特徴とする請求項13に記載の電力半導体デバイス。

- 電子デバイスを形成する方法であって、

第1の導電型を有するドリフト層を設けるステップと、

前記ドリフト層上に、前記第1の導電型と反対の第2の導電型を有する半導体層を設けるステップと、

前記半導体層上に、前記第1の導電型を有するバッファ層を設けるステップと、

前記バッファ層を選択的にエッチングして、前記バッファ層の、第1の厚さを有する第1の部分、および前記バッファ層の、前記第1の厚さよりも薄い第2の厚さを有する第2の部分を画定するメサ段差を形成するステップと、

前記バッファ層を貫通して前記半導体層の中へと延びるコンタクト層であって、第2の導電型を有し、かつ前記半導体層のドーピング濃度よりも高いドーピング濃度を有する前記コンタクト層を形成するステップと、

前記バッファ層の前記第1の部分上にメサを設けるステップであって、前記メサは、前記第1の導電型を有するとともに、前記バッファ層の前記第1の部分を部分的に露出し前記バッファ層の前記メサ段差から横方向に間隔を置いて配置されたメサ側壁を有する、ステップと

を含む電子デバイスを形成する方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US98669407P | 2007-11-09 | 2007-11-09 | |

| US60/986,694 | 2007-11-09 | ||

| PCT/US2008/010538 WO2009061340A1 (en) | 2007-11-09 | 2008-09-08 | Power semiconductor devices with mesa structures and buffer layers including mesa steps |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011503871A JP2011503871A (ja) | 2011-01-27 |

| JP2011503871A5 JP2011503871A5 (ja) | 2012-07-12 |

| JP5372002B2 true JP5372002B2 (ja) | 2013-12-18 |

Family

ID=40032742

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010533058A Active JP5372002B2 (ja) | 2007-11-09 | 2008-09-08 | メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7838377B2 (ja) |

| EP (1) | EP2208230B1 (ja) |

| JP (1) | JP5372002B2 (ja) |

| KR (1) | KR101494935B1 (ja) |

| CN (1) | CN101855726B (ja) |

| WO (1) | WO2009061340A1 (ja) |

Families Citing this family (45)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7728402B2 (en) * | 2006-08-01 | 2010-06-01 | Cree, Inc. | Semiconductor devices including schottky diodes with controlled breakdown |

| US8432012B2 (en) | 2006-08-01 | 2013-04-30 | Cree, Inc. | Semiconductor devices including schottky diodes having overlapping doped regions and methods of fabricating same |

| WO2008020911A2 (en) | 2006-08-17 | 2008-02-21 | Cree, Inc. | High power insulated gate bipolar transistors |

| US8835987B2 (en) | 2007-02-27 | 2014-09-16 | Cree, Inc. | Insulated gate bipolar transistors including current suppressing layers |

| US9640609B2 (en) * | 2008-02-26 | 2017-05-02 | Cree, Inc. | Double guard ring edge termination for silicon carbide devices |

| US8232558B2 (en) | 2008-05-21 | 2012-07-31 | Cree, Inc. | Junction barrier Schottky diodes with current surge capability |

| US8097919B2 (en) * | 2008-08-11 | 2012-01-17 | Cree, Inc. | Mesa termination structures for power semiconductor devices including mesa step buffers |

| US8497552B2 (en) | 2008-12-01 | 2013-07-30 | Cree, Inc. | Semiconductor devices with current shifting regions and related methods |

| US8294507B2 (en) | 2009-05-08 | 2012-10-23 | Cree, Inc. | Wide bandgap bipolar turn-off thyristor having non-negative temperature coefficient and related control circuits |

| US8637386B2 (en) * | 2009-05-12 | 2014-01-28 | Cree, Inc. | Diffused junction termination structures for silicon carbide devices and methods of fabricating silicon carbide devices incorporating same |

| US8629509B2 (en) * | 2009-06-02 | 2014-01-14 | Cree, Inc. | High voltage insulated gate bipolar transistors with minority carrier diverter |

| US8193848B2 (en) | 2009-06-02 | 2012-06-05 | Cree, Inc. | Power switching devices having controllable surge current capabilities |

| US8541787B2 (en) * | 2009-07-15 | 2013-09-24 | Cree, Inc. | High breakdown voltage wide band-gap MOS-gated bipolar junction transistors with avalanche capability |

| US8354690B2 (en) | 2009-08-31 | 2013-01-15 | Cree, Inc. | Solid-state pinch off thyristor circuits |

| US20110084332A1 (en) * | 2009-10-08 | 2011-04-14 | Vishay General Semiconductor, Llc. | Trench termination structure |

| US9117739B2 (en) | 2010-03-08 | 2015-08-25 | Cree, Inc. | Semiconductor devices with heterojunction barrier regions and methods of fabricating same |

| SE537101C2 (sv) | 2010-03-30 | 2015-01-07 | Fairchild Semiconductor | Halvledarkomponent och förfarande för utformning av en struktur i ett målsubstrat för tillverkning av en halvledarkomponent |

| US8415671B2 (en) | 2010-04-16 | 2013-04-09 | Cree, Inc. | Wide band-gap MOSFETs having a heterojunction under gate trenches thereof and related methods of forming such devices |

| US8552435B2 (en) | 2010-07-21 | 2013-10-08 | Cree, Inc. | Electronic device structure including a buffer layer on a base layer |

| US8809904B2 (en) | 2010-07-26 | 2014-08-19 | Cree, Inc. | Electronic device structure with a semiconductor ledge layer for surface passivation |

| US8803277B2 (en) | 2011-02-10 | 2014-08-12 | Cree, Inc. | Junction termination structures including guard ring extensions and methods of fabricating electronic devices incorporating same |

| US9318623B2 (en) | 2011-04-05 | 2016-04-19 | Cree, Inc. | Recessed termination structures and methods of fabricating electronic devices including recessed termination structures |

| US9029945B2 (en) | 2011-05-06 | 2015-05-12 | Cree, Inc. | Field effect transistor devices with low source resistance |

| US9142662B2 (en) | 2011-05-06 | 2015-09-22 | Cree, Inc. | Field effect transistor devices with low source resistance |

| US9337268B2 (en) | 2011-05-16 | 2016-05-10 | Cree, Inc. | SiC devices with high blocking voltage terminated by a negative bevel |

| US9349797B2 (en) | 2011-05-16 | 2016-05-24 | Cree, Inc. | SiC devices with high blocking voltage terminated by a negative bevel |

| CN102244003A (zh) * | 2011-06-20 | 2011-11-16 | 中国科学院微电子研究所 | 一种InP HBT器件侧墙的制备方法 |

| US9640617B2 (en) | 2011-09-11 | 2017-05-02 | Cree, Inc. | High performance power module |

| US8664665B2 (en) | 2011-09-11 | 2014-03-04 | Cree, Inc. | Schottky diode employing recesses for elements of junction barrier array |

| EP2754177A1 (en) | 2011-09-11 | 2014-07-16 | Cree, Inc. | High current density power module comprising transistors with improved layout |

| US8680587B2 (en) | 2011-09-11 | 2014-03-25 | Cree, Inc. | Schottky diode |

| US8618582B2 (en) | 2011-09-11 | 2013-12-31 | Cree, Inc. | Edge termination structure employing recesses for edge termination elements |

| US9373617B2 (en) | 2011-09-11 | 2016-06-21 | Cree, Inc. | High current, low switching loss SiC power module |

| EP2761660B1 (en) | 2012-01-18 | 2017-09-27 | Fairchild Semiconductor Corporation | Bipolar junction transistor with spacer layer and method of manufacturing the same |

| CN103378138B (zh) * | 2012-04-18 | 2016-12-14 | 朱恩均 | 双极晶体管及其制作方法 |

| US9425265B2 (en) | 2013-08-16 | 2016-08-23 | Cree, Inc. | Edge termination technique for high voltage power devices having a negative feature for an improved edge termination structure |

| CN105957886B (zh) * | 2016-06-28 | 2019-05-14 | 中国科学院微电子研究所 | 一种碳化硅双极结型晶体管 |

| CN105977287B (zh) * | 2016-07-25 | 2018-11-09 | 电子科技大学 | 一种碳化硅双极结型晶体管 |

| CN107482057B (zh) * | 2017-06-29 | 2019-04-09 | 厦门市三安集成电路有限公司 | 多重外延层的共射共基晶体管 |

| JP6740986B2 (ja) * | 2017-08-31 | 2020-08-19 | 株式会社デンソー | 炭化珪素半導体装置およびその製造方法 |

| US10573516B2 (en) * | 2017-12-06 | 2020-02-25 | QROMIS, Inc. | Methods for integrated devices on an engineered substrate |

| JP2020184580A (ja) * | 2019-05-08 | 2020-11-12 | 株式会社村田製作所 | 半導体装置 |

| CN112768438B (zh) * | 2019-11-05 | 2022-07-15 | 深圳第三代半导体研究院 | 一种压接式功率模块及其制备方法 |

| CN113809071B (zh) * | 2021-07-26 | 2024-03-29 | 浙江芯国半导体有限公司 | 包含肖特基二极管的电路及相关应用 |

| CN115172471A (zh) * | 2022-06-28 | 2022-10-11 | 东莞市中镓半导体科技有限公司 | 高耐压垂直型二极管及其制备方法 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4927772A (en) * | 1989-05-30 | 1990-05-22 | General Electric Company | Method of making high breakdown voltage semiconductor device |

| JPH03225870A (ja) * | 1990-01-31 | 1991-10-04 | Toshiba Corp | ヘテロ接合バイポーラトランジスタの製造方法 |

| JPH0492434A (ja) * | 1990-08-08 | 1992-03-25 | Sumitomo Electric Ind Ltd | ヘテロ接合バイポーラトランジスタの製造方法 |

| TW286435B (ja) | 1994-07-27 | 1996-09-21 | Siemens Ag | |

| US5967795A (en) | 1995-08-30 | 1999-10-19 | Asea Brown Boveri Ab | SiC semiconductor device comprising a pn junction with a voltage absorbing edge |

| JP3225870B2 (ja) | 1996-12-05 | 2001-11-05 | トヨタ車体株式会社 | ルーフスポイラの取付構造 |

| SE9700156D0 (sv) * | 1997-01-21 | 1997-01-21 | Abb Research Ltd | Junction termination for Si C Schottky diode |

| EP1062700A1 (de) * | 1999-01-12 | 2000-12-27 | EUPEC Europäische Gesellschaft für Leistungshalbleiter mbH & Co. KG | Leistungshalbleiterbauelement mit mesa-randabschluss |

| JP2001035857A (ja) * | 1999-07-21 | 2001-02-09 | Nec Corp | 化合物ヘテロバイポーラトランジスタおよびその製造方法 |

| DE102004045768B4 (de) * | 2004-09-21 | 2007-01-04 | Infineon Technologies Ag | Verfahren zur Herstellung eines Randabschlusses eines Halbleiterbauelements |

| JP4777699B2 (ja) | 2005-06-13 | 2011-09-21 | 本田技研工業株式会社 | バイポーラ型半導体装置およびその製造方法 |

| US7304334B2 (en) * | 2005-09-16 | 2007-12-04 | Cree, Inc. | Silicon carbide bipolar junction transistors having epitaxial base regions and multilayer emitters and methods of fabricating the same |

| JP2007103784A (ja) * | 2005-10-06 | 2007-04-19 | Matsushita Electric Ind Co Ltd | ヘテロ接合バイポーラトランジスタ |

| US7345310B2 (en) * | 2005-12-22 | 2008-03-18 | Cree, Inc. | Silicon carbide bipolar junction transistors having a silicon carbide passivation layer on the base region thereof |

| JP2007287782A (ja) * | 2006-04-13 | 2007-11-01 | Hitachi Ltd | メサ型バイポーラトランジスタ |

-

2008

- 2008-09-08 JP JP2010533058A patent/JP5372002B2/ja active Active

- 2008-09-08 CN CN200880115194.2A patent/CN101855726B/zh active Active

- 2008-09-08 KR KR20107010197A patent/KR101494935B1/ko active Active

- 2008-09-08 WO PCT/US2008/010538 patent/WO2009061340A1/en not_active Ceased

- 2008-09-08 EP EP08846287.4A patent/EP2208230B1/en active Active

- 2008-09-09 US US12/207,028 patent/US7838377B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| EP2208230B1 (en) | 2015-10-21 |

| JP2011503871A (ja) | 2011-01-27 |

| CN101855726B (zh) | 2015-09-16 |

| WO2009061340A1 (en) | 2009-05-14 |

| EP2208230A1 (en) | 2010-07-21 |

| KR20100085971A (ko) | 2010-07-29 |

| US7838377B2 (en) | 2010-11-23 |

| KR101494935B1 (ko) | 2015-02-23 |

| US20090121319A1 (en) | 2009-05-14 |

| CN101855726A (zh) | 2010-10-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5372002B2 (ja) | メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス | |

| JP7182594B2 (ja) | ゲート・トレンチと、埋め込まれた終端構造とを有するパワー半導体デバイス、及び、関連方法 | |

| US8460977B2 (en) | Mesa termination structures for power semiconductor devices and methods of forming power semiconductor devices with mesa termination structures | |

| US11961904B2 (en) | Semiconductor device including trench gate structure and buried shielding region and method of manufacturing | |

| KR100937276B1 (ko) | 반도체 디바이스 및 그 제조 방법 | |

| US9318623B2 (en) | Recessed termination structures and methods of fabricating electronic devices including recessed termination structures | |

| EP2710635B1 (en) | Sic devices with high blocking voltage terminated by a negative bevel | |

| KR101630895B1 (ko) | 전류 시프팅 영역들을 갖는 반도체 장치들 및 관련 방법들 | |

| EP1485942B1 (en) | POWER SiC DEVICES HAVING RAISED GUARD RINGS | |

| US9349797B2 (en) | SiC devices with high blocking voltage terminated by a negative bevel | |

| WO2019053199A1 (en) | CONCEPT FOR SILICON CARBIDE POWER DEVICES | |

| US20220246770A1 (en) | Jbs device with improved electrical performances, and manufacturing process of the jbs device | |

| CN111164759B (zh) | 具有高电流容量的馈线设计 | |

| WO2013119548A1 (en) | Sic devices with high blocking voltage terminated by a negative bevel |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20101207 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121102 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121109 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130212 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130219 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130311 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130318 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20130409 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20130416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130509 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130823 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130917 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5372002 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |