JP5355363B2 - 半導体装置内蔵基板及びその製造方法 - Google Patents

半導体装置内蔵基板及びその製造方法 Download PDFInfo

- Publication number

- JP5355363B2 JP5355363B2 JP2009271902A JP2009271902A JP5355363B2 JP 5355363 B2 JP5355363 B2 JP 5355363B2 JP 2009271902 A JP2009271902 A JP 2009271902A JP 2009271902 A JP2009271902 A JP 2009271902A JP 5355363 B2 JP5355363 B2 JP 5355363B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating layer

- semiconductor device

- connection terminal

- support

- wiring pattern

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/538—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates

- H01L23/5389—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames the interconnection structure between a plurality of semiconductor chips being formed on, or in, insulating substrates the chips being integrally enclosed by the interconnect and support structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/67—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere

- H01L21/683—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping

- H01L21/6835—Apparatus specially adapted for handling semiconductor or electric solid state devices during manufacture or treatment thereof; Apparatus specially adapted for handling wafers during manufacture or treatment of semiconductor or electric solid state devices or components ; Apparatus not specifically provided for elsewhere for supporting or gripping using temporarily an auxiliary support

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L24/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/96—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being encapsulated in a common layer, e.g. neo-wafer or pseudo-wafer, said common layer being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

- H01L2224/0233—Structure of the redistribution layers

- H01L2224/02333—Structure of the redistribution layers being a bump

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/04105—Bonding areas formed on an encapsulation of the semiconductor or solid-state body, e.g. bonding areas on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/1302—Disposition

- H01L2224/13022—Disposition the bump connector being at least partially embedded in the surface

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/20—Structure, shape, material or disposition of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

- H01L23/49816—Spherical bumps on the substrate for external connection, e.g. ball grid arrays [BGA]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01024—Chromium [Cr]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/0103—Zinc [Zn]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01075—Rhenium [Re]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01078—Platinum [Pt]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/013—Alloys

- H01L2924/014—Solder alloys

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

- H01L2924/1815—Shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

- H01L2924/1815—Shape

- H01L2924/1816—Exposing the passive side of the semiconductor or solid-state body

- H01L2924/18162—Exposing the passive side of the semiconductor or solid-state body of a chip with build-up interconnect

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Structures For Mounting Electric Components On Printed Circuit Boards (AREA)

Description

[第1の実施の形態に係る半導体装置内蔵基板の構造]

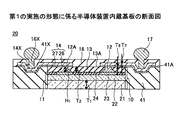

始めに、第1の実施の形態に係る半導体装置内蔵基板の構造について説明する。図1は、第1の実施の形態に係る半導体装置内蔵基板の断面図である。図1を参照するに、半導体装置内蔵基板20は、半導体装置10と、配線パターン14と、ソルダーレジスト層16と、外部接続端子17と、絶縁層41とを有する。

続いて、第1の実施の形態に係る半導体装置内蔵基板の製造方法について説明する。図2〜図19は、第1の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図である。図2〜図19において、図1に示す半導体装置内蔵基板20と同一構成部分には同一符号を付し、その説明を省略する場合がある。図2〜図11において、Cはダイシングブレードが半導体基板31を切断する位置(以下、「基板切断位置C」とする)、Aは複数の半導体装置形成領域(以下、「半導体装置形成領域A」とする)、Bは複数の半導体装置形成領域Aを分離する、基板切断位置Cを含むスクライブ領域(以下、「スクライブ領域B」とする)を示している。

[第2の実施の形態に係る半導体装置内蔵基板の構造]

始めに、第2の実施の形態に係る半導体装置内蔵基板の構造について説明する。図20は、第2の実施の形態に係る半導体装置内蔵基板の断面図である。図20に示す半導体装置内蔵基板50において、図1に示す半導体装置内蔵基板20と同一構成部分には同一符号を付し、その説明を省略する場合がある。図20を参照するに、第2の実施の形態に係る半導体装置内蔵基板50は、第1の実施の形態に係る半導体装置内蔵基板20の絶縁層41が絶縁層51に置換された以外は、半導体装置内蔵基板20と同様である。以下、半導体装置内蔵基板20と異なる部分についてのみ説明する。

続いて、第2の実施の形態に係る半導体装置内蔵基板の製造方法について説明する。図21及び図22は、第2の実施の形態に係る半導体装置内蔵基板の製造工程を例示する図である。図21及び図22において、図20に示す半導体装置内蔵基板50と同一構成部分には同一符号を付し、その説明を省略する場合がある。

第3の実施の形態では、第1及び第2の実施の形態の図12〜図14に示す工程を、異なる工程(図23及び図24参照)に変更する例を示す。

第4の実施の形態では、第1の実施の形態に係る半導体装置内蔵基板とは異なる半導体装置内蔵基板の例を示す。

配線パターン14の凹部14Xの底面及び内側面(傾斜面)の一部を露出する開口部16Yを有する。ソルダーレジスト層16の材料は、例えば感光性樹脂組成物である。

第5の実施の形態では、第1の実施の形態に係る半導体装置内蔵基板とは異なる半導体装置内蔵基板の例を示す。

11 半導体チップ

12 接続端子

12A,13A,25A,25B,40A,40B,41A,42A,43A 面

13,41,51 絶縁層

14 配線パターン

14X、41X 凹部

16 ソルダーレジスト層

16X,16Y,16Z 開口部

17,67,77 外部接続端子

20,50,60,70 半導体装置内蔵基板

21,31 半導体基板

22 半導体集積回路

23 電極パッド

24 保護膜

25 板状体

26,27 金属層

40 第1支持体

40X,42X,43X 凸部

42 第2支持体

43 第3支持体

A 半導体装置形成領域

B スクライブ領域

C 基板切断位置

T1〜T7 厚さ

H1 高さ

Claims (12)

- 半導体集積回路に形成された電極パッド上に接続端子が形成され、前記半導体集積回路上に前記接続端子の一部を露出する第1絶縁層が形成された半導体装置と、

前記半導体装置の少なくとも側面部を埋め、前記接続端子の露出部側の面に凹部が形成された第2絶縁層と、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に形成され、前記第2絶縁層の前記凹部の形状に対応する凹部を有し前記接続端子の露出部と電気的に接続する配線パターンと、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部に形成された前記配線パターンの一部のみを露出する開口部が設けられた第3絶縁層と、を有する半導体装置内蔵基板。 - 前記開口部は、前記配線パターンの凹部の底面及び内側面の一部を露出するように前記第3絶縁層に設けられている請求項1記載の半導体装置内蔵基板。

- 前記開口部は、前記配線パターンの凹部の全面を露出するように前記第3絶縁層に設けられている請求項1記載の半導体装置内蔵基板。

- 前記第2絶縁層は、前記半導体装置の側面部及び裏面部を覆うように形成されている請求項1乃至3の何れか一項記載の半導体装置内蔵基板。

- 半導体集積回路に形成された電極パッド上に接続端子を形成する工程と、前記接続端子を覆うように前記半導体集積回路上に第1絶縁層を形成する工程と、前記第1絶縁層上に、前記第1絶縁層と対向する側の面が粗面とされた板状体を配設する工程と、前記板状体の前記粗面を前記第1絶縁層に圧着することにより、前記接続端子の一部を前記第1絶縁層から露出させる工程と、前記板状体を除去する工程と、を含む工程により半導体装置を製造する第1工程と、

一方の面に凸部が設けられた支持体を前記接続端子の露出部側に配置し、前記半導体装置の少なくとも側面部を埋めるように、前記接続端子の露出部側の面に前記凸部によって凹部が設けられた第2絶縁層を形成する第2工程と、

前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部の形状に対応する凹部を有し前記接続端子の露出部と電気的に接続する配線パターンを形成する第3工程と、を有する半導体装置内蔵基板の製造方法。 - 前記第2工程は、一方の面に凸部が設けられた支持体を準備し、前記接続端子の露出部が前記支持体の前記一方の面と対向するように、前記半導体装置を前記支持体の前記一方の面の前記凸部を含まない領域に配置する第2A工程と、

前記支持体の前記一方の面に配置された前記半導体装置の少なくとも側面部を埋めるように、前記支持体の前記一方の面の前記凸部を含む領域に第2絶縁層を形成する第2B工程と、

前記支持体を除去し、前記第2絶縁層に前記凸部に対応する前記凹部を形成する第2C工程と、を有する請求項5記載の半導体装置内蔵基板の製造方法。 - 前記第2工程は、第1支持体を準備し、前記接続端子の露出部が前記第1支持体の一方の面と対向するように、前記半導体装置を前記第1支持体の前記一方の面に配置する第2D工程と、

一方の面に凸部が設けられた第2支持体を準備し、前記半導体装置が配置された前記第1支持体の他方の面を前記第2支持体の前記一方の面と対向させ、前記第2支持体の前記凸部を含まない領域に前記半導体装置が配置されるように、前記第1支持体を前記第2支持体の前記一方の面に吸着保持させ、前記第1支持体の前記一方の面に前記第2支持体の前記凸部の形状に対応する凸部を形成する第2E工程と、

前記第1支持体の前記一方の面に配置された前記半導体装置の少なくとも側面部を埋めるように、前記第1支持体の前記一方の面の前記凸部を含む領域に第2絶縁層を形成する第2F工程と、

前記第1支持体及び前記第2支持体を除去し、前記第2絶縁層に前記第1支持体の前記凸部に対応する前記凹部を形成する第2G工程と、を有する請求項5記載の半導体装置内蔵基板の製造方法。 - 前記第1絶縁層の前記接続端子の露出部側の面、及び前記第2絶縁層の前記凹部を含む領域に、前記第2絶縁層の前記凹部に形成された前記配線パターンの少なくとも一部を露出する開口部が設けられた第3絶縁層を形成する第4工程を更に有する請求項5乃至7の何れか一項記載の半導体装置内蔵基板の製造方法。

- 前記第3絶縁層上に、前記開口部内に露出する前記配線パターンと電気的に接続される外部接続端子を形成する第5工程を更に有する請求項8記載の半導体装置内蔵基板の製造方法。

- 前記第4工程では、前記第2絶縁層の前記凹部に形成された前記配線パターンの一部のみを前記開口部から露出する請求項8又は9記載の半導体装置内蔵基板の製造方法。

- 前記第4工程では、前記第2絶縁層の前記凹部の底面に形成された前記配線パターンのみを前記開口部から露出する請求項10記載の半導体装置内蔵基板の製造方法。

- 前記第2工程において、前記半導体装置の前記側面部及び裏面部を埋めるように、前記第2絶縁層を形成する請求項5乃至11の何れか一項記載の半導体装置内蔵基板の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009271902A JP5355363B2 (ja) | 2009-11-30 | 2009-11-30 | 半導体装置内蔵基板及びその製造方法 |

| US12/952,452 US8232639B2 (en) | 2009-11-30 | 2010-11-23 | Semiconductor-device mounted board and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009271902A JP5355363B2 (ja) | 2009-11-30 | 2009-11-30 | 半導体装置内蔵基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011114304A JP2011114304A (ja) | 2011-06-09 |

| JP2011114304A5 JP2011114304A5 (ja) | 2012-10-18 |

| JP5355363B2 true JP5355363B2 (ja) | 2013-11-27 |

Family

ID=44068236

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009271902A Active JP5355363B2 (ja) | 2009-11-30 | 2009-11-30 | 半導体装置内蔵基板及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8232639B2 (ja) |

| JP (1) | JP5355363B2 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012134270A (ja) * | 2010-12-21 | 2012-07-12 | Shinko Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| US9070685B2 (en) * | 2012-08-24 | 2015-06-30 | Win Semiconductors Corp. | Compound semiconductor integrated circuit |

| JP6500572B2 (ja) * | 2015-04-14 | 2019-04-17 | オムロン株式会社 | 回路構造体 |

| JP7046639B2 (ja) * | 2018-02-21 | 2022-04-04 | 新光電気工業株式会社 | 配線基板及びその製造方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2842378B2 (ja) | 1996-05-31 | 1999-01-06 | 日本電気株式会社 | 電子回路基板の高密度実装構造 |

| JP2001185444A (ja) * | 1999-12-24 | 2001-07-06 | Kyocera Corp | 薄膜電子部品 |

| JP3652281B2 (ja) * | 2000-06-30 | 2005-05-25 | 京セラ株式会社 | 薄膜電子部品および基板 |

| JP3888267B2 (ja) * | 2002-08-30 | 2007-02-28 | カシオ計算機株式会社 | 半導体装置およびその製造方法 |

| JP4056360B2 (ja) * | 2002-11-08 | 2008-03-05 | 沖電気工業株式会社 | 半導体装置及びその製造方法 |

| JP2005079431A (ja) * | 2003-09-02 | 2005-03-24 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| JP4298559B2 (ja) * | 2004-03-29 | 2009-07-22 | 新光電気工業株式会社 | 電子部品実装構造及びその製造方法 |

| JP4441325B2 (ja) | 2004-05-18 | 2010-03-31 | 新光電気工業株式会社 | 多層配線の形成方法および多層配線基板の製造方法 |

| JP2006222164A (ja) | 2005-02-08 | 2006-08-24 | Shinko Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2007201254A (ja) * | 2006-01-27 | 2007-08-09 | Ibiden Co Ltd | 半導体素子内蔵基板、半導体素子内蔵型多層回路基板 |

| JP5224845B2 (ja) * | 2008-02-18 | 2013-07-03 | 新光電気工業株式会社 | 半導体装置の製造方法及び半導体装置 |

-

2009

- 2009-11-30 JP JP2009271902A patent/JP5355363B2/ja active Active

-

2010

- 2010-11-23 US US12/952,452 patent/US8232639B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2011114304A (ja) | 2011-06-09 |

| US20110127656A1 (en) | 2011-06-02 |

| US8232639B2 (en) | 2012-07-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4803844B2 (ja) | 半導体パッケージ | |

| JP5864180B2 (ja) | 半導体パッケージ及びその製造方法 | |

| US20110221069A1 (en) | Semiconductor device and method of manufacturing the same | |

| JP2006222164A (ja) | 半導体装置及びその製造方法 | |

| JP2008218926A (ja) | 半導体装置及びその製造方法 | |

| JP5406572B2 (ja) | 電子部品内蔵配線基板及びその製造方法 | |

| JP6029958B2 (ja) | 配線基板の製造方法 | |

| JP5135246B2 (ja) | 半導体モジュールおよびその製造方法、ならびに携帯機器 | |

| JP6041731B2 (ja) | インターポーザ、及び電子部品パッケージ | |

| JP2009004544A (ja) | 電子装置の製造方法及び電子装置 | |

| JP5436837B2 (ja) | 半導体装置内蔵基板の製造方法 | |

| US8766101B2 (en) | Wiring substrate, method for manufacturing wiring substrate, and semiconductor package including wiring substrate | |

| JP4420965B1 (ja) | 半導体装置内蔵基板の製造方法 | |

| JP5355363B2 (ja) | 半導体装置内蔵基板及びその製造方法 | |

| US7964493B2 (en) | Method of manufacturing semiconductor device | |

| JP5139039B2 (ja) | 半導体装置及びその製造方法 | |

| JP2008135553A (ja) | 基板積層方法及び基板が積層された半導体装置 | |

| TWI420610B (zh) | 半導體裝置及其製造方法 | |

| JP5436836B2 (ja) | 半導体装置内蔵基板の製造方法 | |

| JP5880036B2 (ja) | 電子部品内蔵基板及びその製造方法と積層型電子部品内蔵基板 | |

| JP2002231765A (ja) | 半導体装置 | |

| JP2006173234A (ja) | 半導体装置およびその製造方法 | |

| WO2023157892A1 (ja) | 半導体パッケージ、半導体パッケージ中間体、再配線層チップ、再配線層チップ中間体、半導体パッケージの製造方法及び半導体パッケージ中間体の製造方法 | |

| JP2011082404A (ja) | 半導体装置の製造方法 | |

| JP5273749B2 (ja) | プリント配線板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120830 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120830 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130718 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130820 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130827 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5355363 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |