JP5278317B2 - 発光ダイオードの製造方法 - Google Patents

発光ダイオードの製造方法 Download PDFInfo

- Publication number

- JP5278317B2 JP5278317B2 JP2009521598A JP2009521598A JP5278317B2 JP 5278317 B2 JP5278317 B2 JP 5278317B2 JP 2009521598 A JP2009521598 A JP 2009521598A JP 2009521598 A JP2009521598 A JP 2009521598A JP 5278317 B2 JP5278317 B2 JP 5278317B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor layer

- type semiconductor

- type

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 34

- 239000004065 semiconductor Substances 0.000 claims description 217

- 238000000034 method Methods 0.000 claims description 75

- 238000007747 plating Methods 0.000 claims description 57

- 238000000926 separation method Methods 0.000 claims description 57

- 238000000605 extraction Methods 0.000 claims description 49

- 239000000758 substrate Substances 0.000 claims description 48

- 229920002120 photoresistant polymer Polymers 0.000 claims description 45

- 238000005530 etching Methods 0.000 claims description 19

- 229910052710 silicon Inorganic materials 0.000 claims description 15

- 239000002019 doping agent Substances 0.000 claims description 14

- 238000001312 dry etching Methods 0.000 claims description 14

- 238000007788 roughening Methods 0.000 claims description 11

- 239000010703 silicon Substances 0.000 claims description 11

- 230000001681 protective effect Effects 0.000 claims description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 6

- 238000001552 radio frequency sputter deposition Methods 0.000 claims description 5

- -1 silicon halide Chemical class 0.000 claims description 5

- 238000005520 cutting process Methods 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 437

- 230000004888 barrier function Effects 0.000 description 32

- 230000008569 process Effects 0.000 description 27

- 239000007789 gas Substances 0.000 description 17

- 238000004544 sputter deposition Methods 0.000 description 17

- 229910052594 sapphire Inorganic materials 0.000 description 16

- 239000010980 sapphire Substances 0.000 description 16

- 238000000137 annealing Methods 0.000 description 15

- 239000013078 crystal Substances 0.000 description 13

- 230000015572 biosynthetic process Effects 0.000 description 12

- 239000000463 material Substances 0.000 description 10

- 150000004767 nitrides Chemical class 0.000 description 10

- 239000000470 constituent Substances 0.000 description 8

- 238000009792 diffusion process Methods 0.000 description 8

- 239000012535 impurity Substances 0.000 description 8

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical group [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 8

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 7

- 230000000052 comparative effect Effects 0.000 description 7

- 239000011777 magnesium Substances 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 238000005253 cladding Methods 0.000 description 6

- 229910052732 germanium Inorganic materials 0.000 description 6

- 238000010030 laminating Methods 0.000 description 6

- 230000002265 prevention Effects 0.000 description 6

- 239000002994 raw material Substances 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 230000000694 effects Effects 0.000 description 5

- 238000009832 plasma treatment Methods 0.000 description 5

- 229910001316 Ag alloy Inorganic materials 0.000 description 4

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 4

- 229910003902 SiCl 4 Inorganic materials 0.000 description 4

- 230000017525 heat dissipation Effects 0.000 description 4

- 229910052697 platinum Inorganic materials 0.000 description 4

- 239000012495 reaction gas Substances 0.000 description 4

- 229910002704 AlGaN Inorganic materials 0.000 description 3

- 229910004298 SiO 2 Inorganic materials 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 3

- 238000009713 electroplating Methods 0.000 description 3

- 229910052741 iridium Inorganic materials 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 238000001451 molecular beam epitaxy Methods 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 229910052703 rhodium Inorganic materials 0.000 description 3

- JLTRXTDYQLMHGR-UHFFFAOYSA-N trimethylaluminium Chemical compound C[Al](C)C JLTRXTDYQLMHGR-UHFFFAOYSA-N 0.000 description 3

- XCZXGTMEAKBVPV-UHFFFAOYSA-N trimethylgallium Chemical compound C[Ga](C)C XCZXGTMEAKBVPV-UHFFFAOYSA-N 0.000 description 3

- 238000007740 vapor deposition Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- OAKJQQAXSVQMHS-UHFFFAOYSA-N Hydrazine Chemical compound NN OAKJQQAXSVQMHS-UHFFFAOYSA-N 0.000 description 2

- 229910021529 ammonia Inorganic materials 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 239000012159 carrier gas Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000002542 deteriorative effect Effects 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 2

- 229910021478 group 5 element Inorganic materials 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 238000012423 maintenance Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910052707 ruthenium Inorganic materials 0.000 description 2

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 2

- 229910010271 silicon carbide Inorganic materials 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- VOITXYVAKOUIBA-UHFFFAOYSA-N triethylaluminium Chemical compound CC[Al](CC)CC VOITXYVAKOUIBA-UHFFFAOYSA-N 0.000 description 2

- RGGPNXQUMRMPRA-UHFFFAOYSA-N triethylgallium Chemical compound CC[Ga](CC)CC RGGPNXQUMRMPRA-UHFFFAOYSA-N 0.000 description 2

- OTRPZROOJRIMKW-UHFFFAOYSA-N triethylindigane Chemical compound CC[In](CC)CC OTRPZROOJRIMKW-UHFFFAOYSA-N 0.000 description 2

- IBEFSUTVZWZJEL-UHFFFAOYSA-N trimethylindium Chemical compound C[In](C)C IBEFSUTVZWZJEL-UHFFFAOYSA-N 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 1

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 1

- 238000004380 ashing Methods 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 150000002291 germanium compounds Chemical class 0.000 description 1

- 229910052734 helium Inorganic materials 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 238000002248 hydride vapour-phase epitaxy Methods 0.000 description 1

- 150000004678 hydrides Chemical class 0.000 description 1

- 239000001257 hydrogen Substances 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical class [H]* 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 150000002500 ions Chemical class 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 229910052743 krypton Inorganic materials 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910052749 magnesium Inorganic materials 0.000 description 1

- QBJCZLXULXFYCK-UHFFFAOYSA-N magnesium;cyclopenta-1,3-diene Chemical compound [Mg+2].C1C=CC=[C-]1.C1C=CC=[C-]1 QBJCZLXULXFYCK-UHFFFAOYSA-N 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910052754 neon Inorganic materials 0.000 description 1

- 229910052762 osmium Inorganic materials 0.000 description 1

- 238000005546 reactive sputtering Methods 0.000 description 1

- 238000002310 reflectometry Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- QQXSEZVCKAEYQJ-UHFFFAOYSA-N tetraethylgermanium Chemical compound CC[Ge](CC)(CC)CC QQXSEZVCKAEYQJ-UHFFFAOYSA-N 0.000 description 1

- ZRLCXMPFXYVHGS-UHFFFAOYSA-N tetramethylgermane Chemical compound C[Ge](C)(C)C ZRLCXMPFXYVHGS-UHFFFAOYSA-N 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- 238000001771 vacuum deposition Methods 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

- H10H20/011—Manufacture or treatment of bodies, e.g. forming semiconductor layers

- H10H20/018—Bonding of wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/83—Electrodes

- H10H20/832—Electrodes characterised by their material

- H10H20/835—Reflective materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10H—INORGANIC LIGHT-EMITTING SEMICONDUCTOR DEVICES HAVING POTENTIAL BARRIERS

- H10H20/00—Individual inorganic light-emitting semiconductor devices having potential barriers, e.g. light-emitting diodes [LED]

- H10H20/80—Constructional details

- H10H20/84—Coatings, e.g. passivation layers or antireflective coatings

Description

本願は、2007年6月29日に、日本に出願された特願2007−171920号に基づき優先権を主張し、その内容をここに援用する。

[1] 基板上に、n型半導体層、発光層及びp型半導体層を順次積層して積層半導体層を形成するとともに、前記p型半導体層上に複数の反射性p型電極を形成する積層工程と、前記反射性p型電極及び前記p型半導体層を覆うようにシード層を形成した後、前記複数の反射性p型電極を相互に隔てる境界部分に沿って分離用フォトレジストを形成するとともに、前記分離用フォトレジストを覆うように、前記シード層上にメッキ層を形成するメッキ工程と、前記n型半導体層から前記基板を取り除いて、前記n型半導体層の光取出面を露出させる除去工程と、前記除去工程の後、前記境界部分の前記分離用フォトレジストに沿って前記積層半導体層の前記光取出面側に分割溝を形成する分割工程と、前記分割溝を形成する分割工程の後、前記n型半導体層の前記光取出面に、前記n型半導体層中のドーパント元素であるケイ素と同一の元素を含有するハロゲン化ケイ素をエッチングガスに用いてドライエッチングを施してから、前記光取出面にn型電極を形成する電極形成工程と、前記電極形成工程の後、前記分離用フォトレジストの一部が露出するまで前記メッキ層を研磨するとともに、前記分離用フォトレジストを除去することによって前記メッキ層に別の分割溝を設け、更に前記分離溝と前記別の分離溝とに沿って前記シード層を切断するダイシング工程と、を具備してなることを特徴とする発光ダイオードの製造方法。

[2] 基板上に、n型半導体層、発光層及びp型半導体層を順次積層して積層半導体層を形成するとともに、前記p型半導体層上に複数の反射性p型電極を形成する積層工程と、前記反射性p型電極及び前記p型半導体層を覆うようにシード層を形成した後、前記複数の反射性p型電極を相互に隔てる境界部分に沿って分離用フォトレジストを形成するとともに、前記分離用フォトレジストを覆うように、前記シード層上にメッキ層を形成するメッキ工程と、前記n型半導体層から前記基板を取り除いて、前記n型半導体層の光取出面を露出させる除去工程と、前記除去工程の後、前記境界部分の前記分離用フォトレジストに沿って前記積層半導体層の前記光取出面側に分割溝を形成する分割工程と、前記分割溝を形成する分割工程の後、前記n型半導体層の前記光取出面に、前記n型半導体層中のドーパント元素であるケイ素と同一の元素を含有するハロゲン化ケイ素をエッチングガスに用いてドライエッチングを施してから、前記光取出面にn型電極を形成する電極形成工程と、前記電極形成工程の後、前記分離用フォトレジストの一部が露出するまで前記メッキ層を研磨してから、機械的応力を印加することによって前記分割溝に沿って前記積層半導体層及び前記メッキ層を分割する分割工程と、を具備してなることを特徴とする発光ダイオードの製造方法。

[3] 前記分割工程と前記電極形成工程との間において、前記分割溝によって複数に分割された半導体層の各分割面に、保護用の絶縁膜を形成する絶縁膜形成工程を設けることを特徴とする前項[1]に記載の発光ダイオードの製造方法。

[4] 前記分割工程と前記電極形成工程との間において、前記分割溝によって複数に分割された半導体層の各分割面に、保護用の絶縁膜を形成する絶縁膜形成工程を設けることを特徴とする前項[2]に記載の発光ダイオードの製造方法。

[5] 前記絶縁膜形成工程と前記電極形成工程との間に、前記n型半導体層の前記光取出面を粗面化する粗面化工程を設けることを特徴とする前項[3]に記載の発光ダイオードの製造方法。

[6] 前記絶縁膜形成工程と前記電極形成工程との間に、前記n型半導体層の前記光取出面を粗面化する粗面化工程を設けることを特徴とする前項[4]に記載の発光ダイオードの製造方法。

[7] 前記積層工程において、前記反射性p型電極をRFスパッタリング法によって形成することを特徴とする前項[1]〜[6]のいずれか一項に記載の発光ダイオードの製造方法。

図1に示す発光ダイオードAは、基体となるメッキ層1と、メッキ層1上に配置されたシード層2と、シード層2の上に配置されたバリア層3と、バリア層3上に配置された反射性p型電極5と、反射性p型電極5上に配置された積層半導体層11と、積層半導体層11上に配置されたn型電極9と、から概略構成されている。

このn型電極9は、後述するように、光取出面11aをドライエッチングした後にCr膜9a、Ti膜9b及びAu膜9cを順次積層することによって形成され、これによりアニール処理を施すことなくn型半導体層8との間でオーミック接触が得られるようになっている。

また、反射性p型電極5は、図1に示すように、積層半導体層11に接するオーミックコンタクト層5cと、オーミックコンタクト層5cに接する反射層5bと、反射層5bに接する相互拡散防止層5aとから構成されている。反射層5bを備えることによって反射性p型電極5は、発光層7から発した光を光取出面11a側に反射させる反射層となっている。

この反射性p型電極5は、後述するように、オーミックコンタクト層5cをRFスパッタリング法を用いて積層し、反射層5b及び相互拡散防止層5aは例えばDCスパッタリング法を用いて積層することによって形成され、これによりアニール処理を施すことなく積層半導体層11との間でオーミック接触が得られるようになっている。

このバリア層3は、発光ダイオードAの構成部材として必ずしも必須な積層膜ではなく、シード層2や反射性p型電極5にバリア機能を持たせることができれば、バリア層3は省略してもよい。

このシード層2は、発光ダイオードAの構成部材として必ずしも必須な積層膜ではなく、バリア層3や反射性p型電極5にメッキの下地層としての機能を持たせることができれば、シード層2は省略してもよい。

またCuは、電気抵抗が低く熱伝導性が高い点においても上下電極構造の発光ダイオードAの基体の材質として好ましい。メッキ層1の厚みは、例えば150μm程度がよい。メッキ層1を備えることによって、発光ダイオードAの放熱効率が高められる。

積層半導体層11としては、GaN系単結晶、GaP系単結晶、GaAs系単結晶、ZnO系単結晶など周知の半導体発光材料を用いることができるが、後述するサファイア単結晶またはSiC単結晶からなる基板に対してエピタキシャル成長可能な点において、GaN系単結晶またはZnO系単結晶がより好ましく、GaN系単結晶が更に好ましい。

下地層はAlXGa1―XN層(0≦x≦1、好ましくは0≦x≦0.5、さらに好ましくは0≦x≦0.1)から構成されることが好ましい。その膜厚は0.1μm以上、好ましくは0.5μm以上、さらに好ましくは1μm以上である。この膜厚以上にした方が結晶性の良好なAlXGa1―XN層が得られやすい。

下地層にはn型不純物を1×1017〜1×1019/cm3の範囲内であればドープしても良いが、アンドープ(<1×1017/cm3)の方が良好な結晶性の維持という点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeであり、より好ましくはSiである。

また、nコンタクト層にはn型不純物がドープされていることが好ましく、n型不純物を1×1017〜1×1019/cm3、好ましくは1×1018〜1×1019/cm3の濃度で含有すると、n型電極9との良好なオーミック接触の維持、クラック発生の抑制、良好な結晶性の維持の点で好ましい。n型不純物としては、特に限定されないが、例えば、Si、GeおよびSn等が挙げられ、好ましくはSiおよびGeであり、より好ましくはSiである。

nコンタクト層を構成するGaN系半導体は、下地層と同一組成であることが好ましく、nコンタクト層と下地層との合計の膜厚を1〜20μm、好ましくは2〜15μm、さらに好ましくは3〜12μmの範囲に設定することが好ましい。nコンタクト層と下地層との合計の膜厚が上記範囲にあると、半導体の結晶性が良好に維持される。

nクラッド層の膜厚は、特に限定されないが、好ましくは0.005〜0.5μmであり、より好ましくは0.005〜0.1μmである。nクラッド層のn型ドープ濃度は1×1017〜1×1020/cm3が好ましく、より好ましくは1×1018〜1×1019/cm3である。ドープ濃度がこの範囲であると、良好な結晶性の維持および素子の動作電圧低減の点で好ましい。

また、発光層7は、上記のような単一量子井戸(SQW)構造の他に、上記Ga1-sInsNを井戸層として、この井戸層よりバンドギャップエネルギーが大きいAlcGa1-cN(0≦c<0.3)障壁層とからなる多重量子井戸(MQW)構造としてもよい。また、井戸層および障壁層には、不純物をドープしてもよい。

pクラッド層としては、発光層7のバンドギャップエネルギーより大きくなる組成であり、発光層7へのキャリアの閉じ込めができるものであれば特に限定されないが、好ましくは、AldGa1-dN(0<d≦0.4、好ましくは0.1≦d≦0.3)のものが挙げられる。pクラッド層が、このようなAlGaNからなると、発光層7へのキャリアの閉じ込めの点で好ましい。pクラッド層の膜厚は、特に限定されないが、好ましくは1〜400nmであり、より好ましくは5〜100nmである。pクラッド層のp型ドープ濃度は、1×1018〜1×1021/cm3が好ましく、より好ましくは1×1019〜1×1020/cm3である。p型ドープ濃度が上記範囲であると、結晶性を低下させることなく良好なp型結晶が得られる。

次に、図2〜図5を参照して、発光ダイオードAの製造方法について説明する。本実施形態の発光ダイオードAの製造方法は、基板21上に積層半導体層11を形成するとともに反射性p型電極5を形成する積層工程と、シード層2を形成するとともにシード層2上にメッキ層1を形成するメッキ工程と、基板21を取り除く除去工程と、積層半導体層11の光取出面側に分割溝を形成する分割工程と、積層半導体層11の分割面に保護用の絶縁膜10を形成する絶縁膜形成工程と、n型半導体層8の光取出面11aを粗面化する粗面化工程と、n型半導体層8の光取出面11aにドライエッチングを施してからn型電極9を形成する電極形成工程と、メッキ層1に別の分割溝を設けるとともに分離溝と別の分離溝とに沿ってシード層2を切断するダイシング工程と、から構成されている。

以下、各工程について図面を参照しつつ説明する。

積層工程では、図2(a)〜図2(b)に示すように、基板21上に、n型半導体層8、発光層7及びp型半導体層6を順次積層して積層半導体層11を形成するとともに、p型半導体層6上に、素子となる単位毎に複数の反射性p型電極5を形成する。

また、n型半導体層8にはn型ドーパントとしてSi等をドープさせることが望ましく、p型半導体層6にはp型ドーパントとしてMg等をドープさせることが望ましい。

更に、基板21上に積層半導体層11を形成する際には、あらかじめ基板21上にバッファ層を形成することが望ましい。すなわち、基板21としてサファイア基板を用い、n型半導体層8としてGaNを形成する場合には、基板21とn型半導体層8との格子定数が10%以上も異なる。この場合に、バッファ層として、基板21とn型半導体層8との中間の格子定数を有するAlNやAlGaNなどを用いることで、n型半導体層8を構成するGaNの結晶性を向上させることができる。

また、MOCVD法では、キャリアガスとして水素(H2)または窒素(N2)、III族原料であるGa源としてトリメチルガリウム(TMG)またはトリエチルガリウム(TEG)、Al源としてトリメチルアルミニウム(TMA)またはトリエチルアルミニウム(TEA)、In源としてトリメチルインジウム(TMI)またはトリエチルインジウム(TEI)、V族原料であるN源としてアンモニア(NH3)、ヒドラジン(N2H4)などが用いられる。また、ドーパントとしては、n型にはSi原料としてモノシラン(SiH4)またはジシラン(Si2H6)を、Ge原料としてゲルマンガス(GeH4)や、テトラメチルゲルマニウム((CH3)4Ge)やテトラエチルゲルマニウム((C2H5)4Ge)等の有機ゲルマニウム化合物を利用できる。

MBE法では、元素状のゲルマニウムもドーピング源として利用できる。p型にはMg原料としては例えばビスシクロペンタジエニルマグネシウム(Cp2Mg)またはビスエチルシクロペンタジエニルマグネシウム(EtCp2Mg)を用いればよい。

スパッタリング用ガスとしては、He、Ne、Ar、Kr、Xe等が使用できる。入手の容易さからArとするのが望ましい。これらの内の一つのガスをチャンバ内に導入し、0.1〜10Paにしたのち放電を行う。好ましくは0.2〜5Paの範囲に設定する。供給する電力は0.2〜2.0kWの範囲が好ましい。この際、放電時間と供給電力を調節することによって、形成する層の厚さを調節することができる。

オーミックコンタクト層をp型半導体層6上に形成するにあたり、真空蒸着法により形成しても同等の効果が得られる。

次に、メッキ工程では、図2(c)〜図3(b)に示すように、反射性p型電極5及びp型半導体層6を覆うようにバリア層3及びシード層2を形成し、反射性p型電極5同士を相互に隔てる境界部分に沿って分離用フォトレジスト22を形成し、分離用フォトレジスト22を覆うようにシード層2上にメッキ層1を形成する。尚、分離用フォトレジスト材料としては公知のものを使用することができる。

次に、図2(d)に示す如く、バリア層3を覆うように、Ti膜2cとTa膜2bとCu膜2aとを順次積層してシード層2を形成する。

次に図3(b)に示すように、シード層2及び分離用フォトレジスト22を覆うようにメッキ層1を形成する。メッキ層1の形成は、シード層2に電流を印加しつつ電気メッキ法で行うとよい。このときのメッキ層1の厚みは、1.0〜2mm程度にすればよい。

次に除去工程では、図3(c)〜図4(a)に示すように、n型半導体層8からバッファ層及び基板21を取り除いて、下地層を露出させる。

バッファ層及び基板21を取り除く方法としては、研磨法、エッチング法、レーザリフトオフ法など公知の技術を何ら制限なく用いることが出来るが、本実施形態では生産性の観点からレーザリフトオフ法を用いることが好ましい。

具体的には図3(c)に示すように、バッファ層と基板21との界面近傍にレーザー光Lを照射し、主にバッファ層を熱分解させることによって、図4(a)に示すようにn型半導体層8から基板21を剥離させる。n型半導体層8から基板21及びバッファ層を取り除くことによって、n型半導体層8のバッファ層との接合面が露出される。

次に分割工程では、図4(b)に示すように、境界部分の分離用フォトレジスト22に沿って積層半導体層11の光取出面11a側に分割溝11cを形成する。

具体的には図4(b)に示すように、積層半導体層11上にマスクを形成し、ドライエッチング等の手段によって積層半導体層11を格子状にエッチングすることにより、積層半導体層11に平面視略格子状の分離溝11cを設ける。エッチングは、バリア層3が露出した時点で終了する。分離溝11cは、分離用フォトレジスト22とほぼ重なるように形成することが好ましい。このようにして、積層半導体層11が格子状の分割溝11cによって複数に分割される。

次に、絶縁膜形成工程では、図4(c)に示すように、分割溝11cによって複数に分割された積層半導体層11の各側面(分割面)11bに、保護用の絶縁膜10を形成する。

具体的には図4(c)に示すように、CVD法やスパッタ法等の手段によって、SiO2からなる絶縁膜10を、各積層半導体層11の側面11bと、各積層半導体層11同士の間に露出するバリア層3と、各積層半導体層11の光取り出し面11aの外周部分を覆うように形成する。積層半導体層11の全体に絶縁膜10を形成し、光取出面11aの中央部以外の部分にレジストを形成し、ドライエッチングすることで、目的の絶縁膜10を形成できる。

次に、粗面化工程では、n型半導体層8の光取出面11aを粗面化する。

具体的には、加熱KOH溶液に浸漬して、光取出面11aの中央の絶縁膜10に被覆されずに露出している部分の、n型半導体層8を構成する下地層を除去するとともに、n型半導体層8の光取出面11aを粗面化する。

下地層の除去には、PEC(photo electrochemical etch)を使用することもできる。

また、下地層の除去及び光取出面11aの粗面化にはドライエッチングを適用することもできる。

尚、上記の下地層の除去操作は、下地層がアンドープ層である場合に必要な操作であって、下地層にSi等がドープされている場合には下地層の除去操作は不要である。

電極形成工程では、図5(a)及び図5(b)に示すように、n型半導体層8の光取出面11aを、n型半導体層8中のドーパント元素と同一の元素を含有するエッチングガスによりドライエッチングしてから、光取出面11aにn型電極9を形成する。

具体的には図5(a)に示すように、メッキ層1、反射性p型電極5及び積層半導体層11等を含むメッキ基板をプラズマドライエッチング装置のチャンバに収納し、n型半導体層8中のドーパント元素と同一の元素を含有するエッチングガスからなる反応ガスをチャンバ内に供給し、積層半導体層11の上方においてプラズマを発生させ、エッチングガスを含むプラズマによって光取出面11aをドライエッチングする。

また、反応ガスを導入した際のチャンバ内の圧力は、例えば0.2〜2Paの範囲にすることが好ましく、エッチングガスの流量は15sccm〜50sccmの範囲が好ましく、プラズマのパワーは120W程度が好ましく、バイアスは50W程度が好ましく、処理時間は150秒程度がよい。

さらに、エッチング速度は5nm/分以上100nm/分以下が好ましい。100nm/分を超えると、作製されたオーミックコンタクトの耐熱性が悪くなる傾向がある。さらに好ましくは5nm/分以上40nm/分以下、特に好ましくは5nm/分以上25nm/分以下である。

このようなエッチング処理を行うことによって、n型半導体層8の表面近傍にエッチングガスに含まれるSiが打ち込まれて、表面近傍のSi濃度が高められると考えられる。

上記の如く、n型半導体層8の表面をプラズマで処理してから、Cr膜またはTi膜等を積層することによって、n型電極9を構成するCr膜またはTi膜とn型半導体層8とをオーミック接触させることができる。この場合、n型電極9の形成後のアニールを必要としない。むしろ、アニールすることによって電気特性を悪化させてしまうことがあるので好ましくない。

ダイシング工程では、図5(c)〜図5(d)に示すように、分離用フォトレジスト22の一部が露出するまでメッキ層1を研磨するとともに、分離用フォトレジスト22を除去することによってメッキ層1に別の分割溝1bを設け、更に分離溝11cと別の分離溝1bとに沿ってシード層2を切断する。

具体的にはまず、図5(c)に示すように、メッキ層1の積層半導体層11と反対側の面を例えばCMP等で研磨することによって、分離用フォトレジスト22を露出させる。

また、上記の発光ダイオードAの製造方法によれば、分離用フォトレジスト22を覆うようにメッキ層1を形成し、その後、メッキ層1を研磨して分離用フォトレジスト22を露出させ、その後、機械的応力を加えて発光ダイオードAの分割を行ってもよく、これにより、メッキ層1を分断するためのダイシング操作が不要になり、発光ダイオードAの分割を容易に行うことができる。

(実施例1)

図1に示す発光ダイオードAを以下に示すようにして作成した。

すなわち、サファイアからなる基板上に、AlNからなる厚さ40nmのバッファ層を形成し、バッファ層上に、厚さ2μmのアンドープGaN下地層、厚さ2μmのSiドープn型GaNコンタクト層及び厚さ20nmのn型In0.1Ga0.9Nクラッド層(n型半導体層)、厚さ15nmのSiドープGaN障壁層および厚さ2nmのIn0.2Ga0.8N井戸層を5回積層し、最後に障壁層を設けた多重井戸構造の発光層、厚さ10nmのMgドープp型Al0.1Ga0.9Nクラッド層及び厚さ200nmのMgドープp型Al0.02Ga0.98Nコンタクト層(p型半導体層)を順に積層し、積層半導体層を得た。

次に、反射性p型電極及びp型半導体層を覆うように、厚さ100nmのNi膜と厚さ200nmのAu膜とを蒸着法により順次積層してバリア層を形成した。

次に、バリア層上に、厚さ200nmのTi膜と厚さ400nmのTa膜と厚さ300nmのCu膜とをスパッタリング法により順次積層してシード層を形成した。

次に、シード層に電流を印加しつつ電気メッキ法によって、シード層及び分離用フォトレジストを覆うようにメッキ層を厚さ1.2mm程度に形成した。

次に、積層半導体層に格子状の分割溝をドライエッチング法によって形成した。エッチングは、バリア層が露出した時点で終了した。分割溝は、分離用フォトレジストとほぼ重なるように形成した。

次に、n型半導体層の光取出面に対して加熱KOH溶液処理を施すことによって、光取出面を粗面化させた。

反応ガスを導入した際のチャンバ内の圧力を0.5Paに設定し、エッチングガスの流量を30sccmに設定し、プラズマのパワーを120Wに設定し、バイアスを50Wに設定し、処理時間を150秒に設定した。

このようにして、1000μm角の実施例1の発光ダイオードを製造した。

プラズマ処理を行わなかったこと以外は上記実施例1と同様にして、比較例1の発光ダイオードを製造した。

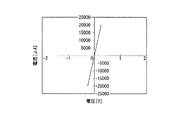

一方、図7から明らかなように、比較例1では電流と電圧との関係が直線関係にならず、n型電極とn型半導体層との間でオーミック接合が形成されていないことが明らかになった。

以上説明した通り、n型電極の形成前にプラズマ処理を行うことによって、アニール処理を行うことなく、n型電極とn型半導体層との間でオーミック接合が得られることが明らかになった。

Claims (7)

- 基板上に、n型半導体層、発光層及びp型半導体層を順次積層して積層半導体層を形成するとともに、前記p型半導体層上に複数の反射性p型電極を形成する積層工程と、

前記反射性p型電極及び前記p型半導体層を覆うようにシード層を形成した後、前記複数の反射性p型電極を相互に隔てる境界部分に沿って分離用フォトレジストを形成するとともに、前記分離用フォトレジストを覆うように、前記シード層上にメッキ層を形成するメッキ工程と、

前記n型半導体層から前記基板を取り除いて、前記n型半導体層の光取出面を露出させる除去工程と、

前記除去工程の後、前記境界部分の前記分離用フォトレジストに沿って前記積層半導体層の前記光取出面側に分割溝を形成する分割工程と、

前記分割溝を形成する分割工程の後、前記n型半導体層の前記光取出面に、前記n型半導体層中のドーパント元素であるケイ素と同一の元素を含有するハロゲン化ケイ素をエッチングガスに用いてドライエッチングを施してから、前記光取出面にn型電極を形成する電極形成工程と、

前記電極形成工程の後、前記分離用フォトレジストの一部が露出するまで前記メッキ層を研磨するとともに、前記分離用フォトレジストを除去することによって前記メッキ層に別の分割溝を設け、更に前記分離溝と前記別の分離溝とに沿って前記シード層を切断するダイシング工程と、

を具備してなることを特徴とする発光ダイオードの製造方法。 - 基板上に、n型半導体層、発光層及びp型半導体層を順次積層して積層半導体層を形成するとともに、前記p型半導体層上に複数の反射性p型電極を形成する積層工程と、

前記反射性p型電極及び前記p型半導体層を覆うようにシード層を形成した後、前記複数の反射性p型電極を相互に隔てる境界部分に沿って分離用フォトレジストを形成するとともに、前記分離用フォトレジストを覆うように、前記シード層上にメッキ層を形成するメッキ工程と、

前記n型半導体層から前記基板を取り除いて、前記n型半導体層の光取出面を露出させる除去工程と、

前記除去工程の後、前記境界部分の前記分離用フォトレジストに沿って前記積層半導体層の前記光取出面側に分割溝を形成する分割工程と、

前記分割溝を形成する分割工程の後、前記n型半導体層の前記光取出面に、前記n型半導体層中のドーパント元素であるケイ素と同一の元素を含有するハロゲン化ケイ素をエッチングガスに用いてドライエッチングを施してから、前記光取出面にn型電極を形成する電極形成工程と、

前記電極形成工程の後、前記分離用フォトレジストの一部が露出するまで前記メッキ層を研磨してから、機械的応力を印加することによって前記分割溝に沿って前記積層半導体層及び前記メッキ層を分割する分割工程と、

を具備してなることを特徴とする発光ダイオードの製造方法。 - 前記分割工程と前記電極形成工程との間において、前記分割溝によって複数に分割された半導体層の各分割面に、保護用の絶縁膜を形成する絶縁膜形成工程を設けることを特徴とする請求項1に記載の発光ダイオードの製造方法。

- 前記分割工程と前記電極形成工程との間において、前記分割溝によって複数に分割された半導体層の各分割面に、保護用の絶縁膜を形成する絶縁膜形成工程を設けることを特徴とする請求項2に記載の発光ダイオードの製造方法。

- 前記絶縁膜形成工程と前記電極形成工程との間に、前記n型半導体層の前記光取出面を粗面化する粗面化工程を設けることを特徴とする請求項3に記載の発光ダイオードの製造方法。

- 前記絶縁膜形成工程と前記電極形成工程との間に、前記n型半導体層の前記光取出面を粗面化する粗面化工程を設けることを特徴とする請求項4に記載の発光ダイオードの製造方法。

- 前記積層工程において、前記反射性p型電極をRFスパッタリング法によって形成することを特徴とする請求項1〜請求項6のいずれか一項に記載の発光ダイオードの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009521598A JP5278317B2 (ja) | 2007-06-29 | 2008-06-26 | 発光ダイオードの製造方法 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007171920 | 2007-06-29 | ||

| JP2007171920 | 2007-06-29 | ||

| PCT/JP2008/061654 WO2009004980A1 (ja) | 2007-06-29 | 2008-06-26 | 発光ダイオードの製造方法 |

| JP2009521598A JP5278317B2 (ja) | 2007-06-29 | 2008-06-26 | 発光ダイオードの製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2009004980A1 JPWO2009004980A1 (ja) | 2010-08-26 |

| JP5278317B2 true JP5278317B2 (ja) | 2013-09-04 |

Family

ID=40226027

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009521598A Active JP5278317B2 (ja) | 2007-06-29 | 2008-06-26 | 発光ダイオードの製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US8097478B2 (ja) |

| JP (1) | JP5278317B2 (ja) |

| TW (1) | TWI360896B (ja) |

| WO (1) | WO2009004980A1 (ja) |

Families Citing this family (76)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101449030B1 (ko) * | 2008-04-05 | 2014-10-08 | 엘지이노텍 주식회사 | 그룹 3족 질화물계 반도체 발광다이오드 소자 및 이의 제조방법 |

| KR101363022B1 (ko) * | 2008-12-23 | 2014-02-14 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 |

| KR100974776B1 (ko) | 2009-02-10 | 2010-08-06 | 엘지이노텍 주식회사 | 발광 소자 |

| JP2011029574A (ja) * | 2009-03-31 | 2011-02-10 | Toyoda Gosei Co Ltd | Iii族窒化物系化合物半導体素子の製造方法 |

| JP2011035017A (ja) * | 2009-07-30 | 2011-02-17 | Hitachi Cable Ltd | 発光素子 |

| KR101072034B1 (ko) | 2009-10-15 | 2011-10-10 | 엘지이노텍 주식회사 | 반도체 발광소자 및 그 제조방법 |

| KR101014013B1 (ko) * | 2009-10-15 | 2011-02-10 | 엘지이노텍 주식회사 | 반도체 발광소자 및 그 제조방법 |

| KR101081193B1 (ko) | 2009-10-15 | 2011-11-07 | 엘지이노텍 주식회사 | 반도체 발광소자 및 그 제조방법 |

| JP5423390B2 (ja) * | 2009-12-26 | 2014-02-19 | 豊田合成株式会社 | Iii族窒化物系化合物半導体素子及びその製造方法 |

| JP5185308B2 (ja) * | 2010-03-09 | 2013-04-17 | 株式会社東芝 | 半導体発光装置の製造方法 |

| JP5531794B2 (ja) | 2010-06-09 | 2014-06-25 | 日亜化学工業株式会社 | 半導体発光素子の製造方法 |

| CN102064146A (zh) * | 2010-12-03 | 2011-05-18 | 北京大学 | 一种芯片的散热结构 |

| KR101752663B1 (ko) * | 2010-12-22 | 2017-06-30 | 엘지이노텍 주식회사 | 발광소자 및 발광소자 제조방법 |

| US9496454B2 (en) | 2011-03-22 | 2016-11-15 | Micron Technology, Inc. | Solid state optoelectronic device with plated support substrate |

| US8809875B2 (en) | 2011-11-18 | 2014-08-19 | LuxVue Technology Corporation | Micro light emitting diode |

| US8573469B2 (en) * | 2011-11-18 | 2013-11-05 | LuxVue Technology Corporation | Method of forming a micro LED structure and array of micro LED structures with an electrically insulating layer |

| US8518204B2 (en) | 2011-11-18 | 2013-08-27 | LuxVue Technology Corporation | Method of fabricating and transferring a micro device and an array of micro devices utilizing an intermediate electrically conductive bonding layer |

| US8349116B1 (en) | 2011-11-18 | 2013-01-08 | LuxVue Technology Corporation | Micro device transfer head heater assembly and method of transferring a micro device |

| US9620478B2 (en) | 2011-11-18 | 2017-04-11 | Apple Inc. | Method of fabricating a micro device transfer head |

| TW201324863A (zh) * | 2011-12-13 | 2013-06-16 | 新世紀光電股份有限公司 | 發光二極體元件以及覆晶式發光二極體封裝元件 |

| CN105449072A (zh) * | 2011-12-20 | 2016-03-30 | 新世纪光电股份有限公司 | 发光二极管元件 |

| JP2013157496A (ja) * | 2012-01-31 | 2013-08-15 | Sony Corp | 発光素子およびその製造方法、並びに発光装置 |

| US9773750B2 (en) | 2012-02-09 | 2017-09-26 | Apple Inc. | Method of transferring and bonding an array of micro devices |

| KR101286211B1 (ko) * | 2012-02-16 | 2013-07-15 | 고려대학교 산학협력단 | 발광 소자 제조 방법 및 이를 이용하여 제조된 발광 소자 |

| TWI528578B (zh) * | 2012-03-28 | 2016-04-01 | 鴻海精密工業股份有限公司 | 發光二極體製造方法 |

| US9548332B2 (en) | 2012-04-27 | 2017-01-17 | Apple Inc. | Method of forming a micro LED device with self-aligned metallization stack |

| US9437783B2 (en) * | 2012-05-08 | 2016-09-06 | Cree, Inc. | Light emitting diode (LED) contact structures and process for fabricating the same |

| US9105492B2 (en) | 2012-05-08 | 2015-08-11 | LuxVue Technology Corporation | Compliant micro device transfer head |

| US9608016B2 (en) * | 2012-05-17 | 2017-03-28 | Koninklijke Philips N.V. | Method of separating a wafer of semiconductor devices |

| US8415768B1 (en) | 2012-07-06 | 2013-04-09 | LuxVue Technology Corporation | Compliant monopolar micro device transfer head with silicon electrode |

| US8791530B2 (en) | 2012-09-06 | 2014-07-29 | LuxVue Technology Corporation | Compliant micro device transfer head with integrated electrode leads |

| US9162880B2 (en) | 2012-09-07 | 2015-10-20 | LuxVue Technology Corporation | Mass transfer tool |

| US8941215B2 (en) | 2012-09-24 | 2015-01-27 | LuxVue Technology Corporation | Micro device stabilization post |

| US8835940B2 (en) | 2012-09-24 | 2014-09-16 | LuxVue Technology Corporation | Micro device stabilization post |

| US9558721B2 (en) | 2012-10-15 | 2017-01-31 | Apple Inc. | Content-based adaptive refresh schemes for low-power displays |

| US9236815B2 (en) | 2012-12-10 | 2016-01-12 | LuxVue Technology Corporation | Compliant micro device transfer head array with metal electrodes |

| US9105714B2 (en) | 2012-12-11 | 2015-08-11 | LuxVue Technology Corporation | Stabilization structure including sacrificial release layer and staging bollards |

| US9166114B2 (en) | 2012-12-11 | 2015-10-20 | LuxVue Technology Corporation | Stabilization structure including sacrificial release layer and staging cavity |

| US9308649B2 (en) | 2013-02-25 | 2016-04-12 | LuxVue Techonology Corporation | Mass transfer tool manipulator assembly |

| US9095980B2 (en) | 2013-02-25 | 2015-08-04 | LuxVue Technology Corporation | Micro pick up array mount with integrated displacement sensor |

| US9252375B2 (en) | 2013-03-15 | 2016-02-02 | LuxVue Technology Corporation | Method of fabricating a light emitting diode display with integrated defect detection test |

| US8791474B1 (en) | 2013-03-15 | 2014-07-29 | LuxVue Technology Corporation | Light emitting diode display with redundancy scheme |

| US9484504B2 (en) | 2013-05-14 | 2016-11-01 | Apple Inc. | Micro LED with wavelength conversion layer |

| US9217541B2 (en) | 2013-05-14 | 2015-12-22 | LuxVue Technology Corporation | Stabilization structure including shear release posts |

| US9136161B2 (en) | 2013-06-04 | 2015-09-15 | LuxVue Technology Corporation | Micro pick up array with compliant contact |

| WO2014201187A2 (en) | 2013-06-12 | 2014-12-18 | Rohinni, Inc. | Keyboard backlighting with deposited light-generating sources |

| US8987765B2 (en) | 2013-06-17 | 2015-03-24 | LuxVue Technology Corporation | Reflective bank structure and method for integrating a light emitting device |

| US8928021B1 (en) | 2013-06-18 | 2015-01-06 | LuxVue Technology Corporation | LED light pipe |

| US9111464B2 (en) | 2013-06-18 | 2015-08-18 | LuxVue Technology Corporation | LED display with wavelength conversion layer |

| US9035279B2 (en) | 2013-07-08 | 2015-05-19 | LuxVue Technology Corporation | Micro device with stabilization post |

| US9296111B2 (en) | 2013-07-22 | 2016-03-29 | LuxVue Technology Corporation | Micro pick up array alignment encoder |

| US9087764B2 (en) | 2013-07-26 | 2015-07-21 | LuxVue Technology Corporation | Adhesive wafer bonding with controlled thickness variation |

| US9153548B2 (en) | 2013-09-16 | 2015-10-06 | Lux Vue Technology Corporation | Adhesive wafer bonding with sacrificial spacers for controlled thickness variation |

| DE102013111496A1 (de) | 2013-10-18 | 2015-04-23 | Osram Opto Semiconductors Gmbh | Verfahren zum Herstellen von optoelektronischen Halbleiterbauelementen und optoelektronisches Halbleiterbauelement |

| US9367094B2 (en) | 2013-12-17 | 2016-06-14 | Apple Inc. | Display module and system applications |

| TWI552386B (zh) | 2013-12-20 | 2016-10-01 | 新世紀光電股份有限公司 | 半導體發光結構及半導體封裝結構 |

| US9768345B2 (en) | 2013-12-20 | 2017-09-19 | Apple Inc. | LED with current injection confinement trench |

| US9450147B2 (en) | 2013-12-27 | 2016-09-20 | Apple Inc. | LED with internally confined current injection area |

| US9583466B2 (en) | 2013-12-27 | 2017-02-28 | Apple Inc. | Etch removal of current distribution layer for LED current confinement |

| US9542638B2 (en) | 2014-02-18 | 2017-01-10 | Apple Inc. | RFID tag and micro chip integration design |

| US9583533B2 (en) | 2014-03-13 | 2017-02-28 | Apple Inc. | LED device with embedded nanowire LEDs |

| US9522468B2 (en) | 2014-05-08 | 2016-12-20 | Apple Inc. | Mass transfer tool manipulator assembly with remote center of compliance |

| US9318475B2 (en) | 2014-05-15 | 2016-04-19 | LuxVue Technology Corporation | Flexible display and method of formation with sacrificial release layer |

| US9741286B2 (en) | 2014-06-03 | 2017-08-22 | Apple Inc. | Interactive display panel with emitting and sensing diodes |

| US9624100B2 (en) | 2014-06-12 | 2017-04-18 | Apple Inc. | Micro pick up array pivot mount with integrated strain sensing elements |

| US9425151B2 (en) | 2014-06-17 | 2016-08-23 | Apple Inc. | Compliant electrostatic transfer head with spring support layer |

| US9570002B2 (en) | 2014-06-17 | 2017-02-14 | Apple Inc. | Interactive display panel with IR diodes |

| US9828244B2 (en) | 2014-09-30 | 2017-11-28 | Apple Inc. | Compliant electrostatic transfer head with defined cavity |

| US9705432B2 (en) | 2014-09-30 | 2017-07-11 | Apple Inc. | Micro pick up array pivot mount design for strain amplification |

| KR101637186B1 (ko) * | 2014-11-24 | 2016-07-07 | 주식회사 에스에프에이반도체 | 관통 실리콘 비아 웨이퍼의 집적회로 분단 방법 |

| US9478583B2 (en) | 2014-12-08 | 2016-10-25 | Apple Inc. | Wearable display having an array of LEDs on a conformable silicon substrate |

| WO2017124109A1 (en) | 2016-01-15 | 2017-07-20 | Rohinni, LLC | Apparatus and method of backlighting through a cover on the apparatus |

| TWI646680B (zh) * | 2017-01-10 | 2019-01-01 | 英屬開曼群島商錼創科技股份有限公司 | 微型發光二極體晶片以及顯示面板 |

| CN109768137B (zh) * | 2018-12-29 | 2022-06-14 | 晶能光电(江西)有限公司 | 垂直结构led芯片及其制备方法 |

| WO2021203355A1 (zh) * | 2020-04-09 | 2021-10-14 | 厦门市三安光电科技有限公司 | 一种发光二极管器件及其制备方法 |

| CN115458647B (zh) * | 2022-10-31 | 2025-08-19 | 天津三安光电有限公司 | 一种垂直led芯片结构及其制造方法及发光装置 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2005029573A1 (en) * | 2003-09-19 | 2005-03-31 | Tinggi Technologies Private Limited | Fabrication of semiconductor devices |

| JP2005223165A (ja) * | 2004-02-06 | 2005-08-18 | Sanyo Electric Co Ltd | 窒化物系発光素子 |

| JP2005252222A (ja) * | 2004-02-03 | 2005-09-15 | Matsushita Electric Ind Co Ltd | 半導体発光装置、照明モジュール、照明装置、表示素子、および半導体発光装置の製造方法 |

| JP2005259832A (ja) * | 2004-03-10 | 2005-09-22 | Sanyo Electric Co Ltd | 窒化物系半導体発光素子 |

| JP2005268769A (ja) * | 2004-02-20 | 2005-09-29 | Nichia Chem Ind Ltd | 窒化物半導体素子及び窒化物半導体基板の製造方法、並びに窒化物半導体素子の製造方法 |

| JP2007019511A (ja) * | 2005-07-05 | 2007-01-25 | Lg Electronics Inc | 発光素子及びその製造方法 |

| WO2007032421A1 (en) * | 2005-09-13 | 2007-03-22 | Showa Denko K.K. | Nitride semiconductor light emitting device and production thereof |

| JP2007103934A (ja) * | 2005-10-05 | 2007-04-19 | Samsung Electro Mech Co Ltd | 垂直構造発光ダイオードの製造方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1658642B1 (en) | 2003-08-28 | 2014-02-26 | Panasonic Corporation | Semiconductor light emitting device, light emitting module, lighting apparatus, display element and manufacturing method of semiconductor light emitting device |

| WO2005029572A1 (en) | 2003-09-19 | 2005-03-31 | Tinggi Technologies Private Limited | Fabrication of conductive metal layer on semiconductor devices |

| US8089093B2 (en) | 2004-02-20 | 2012-01-03 | Nichia Corporation | Nitride semiconductor device including different concentrations of impurities |

| CN1998094B (zh) * | 2004-04-07 | 2012-12-26 | 霆激技术有限公司 | 半导体发光二极管上的反射层的制造 |

| US7897420B2 (en) * | 2005-01-11 | 2011-03-01 | SemiLEDs Optoelectronics Co., Ltd. | Light emitting diodes (LEDs) with improved light extraction by roughening |

| JP5091233B2 (ja) * | 2006-06-23 | 2012-12-05 | エルジー エレクトロニクス インコーポレイティド | 垂直型発光素子及びその製造方法 |

-

2008

- 2008-06-26 JP JP2009521598A patent/JP5278317B2/ja active Active

- 2008-06-26 US US12/666,192 patent/US8097478B2/en active Active

- 2008-06-26 WO PCT/JP2008/061654 patent/WO2009004980A1/ja not_active Ceased

- 2008-06-27 TW TW097124274A patent/TWI360896B/zh active

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2005029573A1 (en) * | 2003-09-19 | 2005-03-31 | Tinggi Technologies Private Limited | Fabrication of semiconductor devices |

| JP2005252222A (ja) * | 2004-02-03 | 2005-09-15 | Matsushita Electric Ind Co Ltd | 半導体発光装置、照明モジュール、照明装置、表示素子、および半導体発光装置の製造方法 |

| JP2005223165A (ja) * | 2004-02-06 | 2005-08-18 | Sanyo Electric Co Ltd | 窒化物系発光素子 |

| JP2005268769A (ja) * | 2004-02-20 | 2005-09-29 | Nichia Chem Ind Ltd | 窒化物半導体素子及び窒化物半導体基板の製造方法、並びに窒化物半導体素子の製造方法 |

| JP2005259832A (ja) * | 2004-03-10 | 2005-09-22 | Sanyo Electric Co Ltd | 窒化物系半導体発光素子 |

| JP2007019511A (ja) * | 2005-07-05 | 2007-01-25 | Lg Electronics Inc | 発光素子及びその製造方法 |

| WO2007032421A1 (en) * | 2005-09-13 | 2007-03-22 | Showa Denko K.K. | Nitride semiconductor light emitting device and production thereof |

| JP2007103934A (ja) * | 2005-10-05 | 2007-04-19 | Samsung Electro Mech Co Ltd | 垂直構造発光ダイオードの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| TW200917528A (en) | 2009-04-16 |

| US8097478B2 (en) | 2012-01-17 |

| WO2009004980A1 (ja) | 2009-01-08 |

| JPWO2009004980A1 (ja) | 2010-08-26 |

| US20100203661A1 (en) | 2010-08-12 |

| TWI360896B (en) | 2012-03-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5278317B2 (ja) | 発光ダイオードの製造方法 | |

| CN101882656B (zh) | 半导体器件及其制造方法 | |

| JP2009099675A (ja) | 発光ダイオードの製造方法及び発光ダイオード、並びにランプ | |

| JP5074138B2 (ja) | 発光ダイオードの製造方法 | |

| JP5232975B2 (ja) | 発光ダイオードの製造方法及び発光ダイオード、並びにランプ | |

| JP4137936B2 (ja) | 窒化ガリウム系化合物半導体発光素子 | |

| JP4951443B2 (ja) | 発光ダイオードの製造方法 | |

| JP2009105123A (ja) | 発光ダイオードおよびその製造方法 | |

| US8932890B2 (en) | Vertical-structure semiconductor light emitting element and a production method therefor | |

| US20090045431A1 (en) | Semiconductor light-emitting device having a current-blocking layer formed between a semiconductor multilayer film and a metal film and located at the periphery. , method for fabricating the same and method for bonding the same | |

| US8871547B2 (en) | Method for fabricating vertical light emitting diode (VLED) structure using a laser pulse to remove a carrier substrate | |

| JP2013102240A (ja) | 二重ヘテロ構造の発光領域を有するiii族窒化物発光デバイス | |

| CN101371370A (zh) | 半导体器件及其制造方法 | |

| JP2010093186A (ja) | 窒化ガリウム系化合物半導体発光素子の製造方法、窒化ガリウム系化合物半導体素子の積層構造及び窒化ガリウム系化合物半導体発光素子、並びにランプ | |

| KR100916366B1 (ko) | 반도체 발광소자용 지지기판 및 이를 이용한 수직구조의 반도체 발광소자 제조 방법 | |

| JP2008543032A (ja) | InGaAlN発光装置とその製造方法 | |

| US7884381B2 (en) | Light emitting device and method for fabricating the same including a back surface electrode with an Au alloy | |

| TW201220528A (en) | Vertical light emitting diode (VLED) die having n-type confinement structure with etch stop layer and method of fabrication | |

| US20100065870A1 (en) | Light emitting device | |

| KR100886110B1 (ko) | 반도체 발광소자용 지지기판 및 이를 이용한 수직구조의 반도체 발광소자 제조 방법 | |

| JP2007081312A (ja) | 窒化物系半導体発光素子の製造方法 | |

| JP4034015B2 (ja) | Iii族窒化物系化合物半導体発光素子 | |

| KR101231118B1 (ko) | 반도체 발광소자용 지지기판 및 상기 지지기판을 이용한고성능 수직구조의 반도체 발광소자 | |

| KR101171855B1 (ko) | 반도체 발광소자용 지지기판 및 상기 지지기판을 이용한고성능 수직구조의 반도체 발광소자 | |

| JP5880880B2 (ja) | 窒化物発光素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110303 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121218 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130213 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130423 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130506 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5278317 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |