JP5263755B2 - トンネル・ナノチューブ電界効果トランジスタおよびそれを製作する方法 - Google Patents

トンネル・ナノチューブ電界効果トランジスタおよびそれを製作する方法 Download PDFInfo

- Publication number

- JP5263755B2 JP5263755B2 JP2007515262A JP2007515262A JP5263755B2 JP 5263755 B2 JP5263755 B2 JP 5263755B2 JP 2007515262 A JP2007515262 A JP 2007515262A JP 2007515262 A JP2007515262 A JP 2007515262A JP 5263755 B2 JP5263755 B2 JP 5263755B2

- Authority

- JP

- Japan

- Prior art keywords

- drain

- transistor

- source region

- nanotube

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000002071 nanotube Substances 0.000 title claims description 53

- 230000005669 field effect Effects 0.000 title claims description 20

- 238000004519 manufacturing process Methods 0.000 title claims description 9

- 238000000034 method Methods 0.000 claims description 17

- 239000002019 doping agent Substances 0.000 claims description 16

- 230000005641 tunneling Effects 0.000 claims description 15

- 239000004065 semiconductor Substances 0.000 claims description 10

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 6

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 4

- 239000002800 charge carrier Substances 0.000 claims description 4

- 239000000460 chlorine Substances 0.000 claims description 4

- 239000011734 sodium Substances 0.000 claims description 4

- 229910052799 carbon Inorganic materials 0.000 claims description 3

- WKBOTKDWSSQWDR-UHFFFAOYSA-N Bromine atom Chemical compound [Br] WKBOTKDWSSQWDR-UHFFFAOYSA-N 0.000 claims description 2

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 claims description 2

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 claims description 2

- 229920002873 Polyethylenimine Polymers 0.000 claims description 2

- ZLMJMSJWJFRBEC-UHFFFAOYSA-N Potassium Chemical compound [K] ZLMJMSJWJFRBEC-UHFFFAOYSA-N 0.000 claims description 2

- GDTBXPJZTBHREO-UHFFFAOYSA-N bromine Substances BrBr GDTBXPJZTBHREO-UHFFFAOYSA-N 0.000 claims description 2

- 229910052794 bromium Inorganic materials 0.000 claims description 2

- 229910052801 chlorine Inorganic materials 0.000 claims description 2

- 229910052700 potassium Inorganic materials 0.000 claims description 2

- 239000011591 potassium Substances 0.000 claims description 2

- 229910052708 sodium Inorganic materials 0.000 claims description 2

- 239000010410 layer Substances 0.000 description 16

- 239000000463 material Substances 0.000 description 11

- 239000000758 substrate Substances 0.000 description 5

- 238000010586 diagram Methods 0.000 description 4

- 239000010936 titanium Substances 0.000 description 4

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 3

- 239000002041 carbon nanotube Substances 0.000 description 3

- 229910021393 carbon nanotube Inorganic materials 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 229910052751 metal Inorganic materials 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910052720 vanadium Inorganic materials 0.000 description 3

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 2

- 238000000231 atomic layer deposition Methods 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000005137 deposition process Methods 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 229910001092 metal group alloy Inorganic materials 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 239000002070 nanowire Substances 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- 238000001771 vacuum deposition Methods 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 1

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 229910052802 copper Inorganic materials 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000009429 electrical wiring Methods 0.000 description 1

- 230000002349 favourable effect Effects 0.000 description 1

- 239000003574 free electron Substances 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(iv) oxide Chemical compound O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 238000004806 packaging method and process Methods 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0665—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body the shape of the body defining a nanostructure

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0657—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body

- H01L29/0665—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape of the body the shape of the body defining a nanostructure

- H01L29/0669—Nanowires or nanotubes

- H01L29/0673—Nanowires or nanotubes oriented parallel to a substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/88—Tunnel-effect diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K10/00—Organic devices specially adapted for rectifying, amplifying, oscillating or switching; Organic capacitors or resistors having potential barriers

- H10K10/40—Organic transistors

- H10K10/46—Field-effect transistors, e.g. organic thin-film transistors [OTFT]

- H10K10/462—Insulated gate field-effect transistors [IGFETs]

- H10K10/484—Insulated gate field-effect transistors [IGFETs] characterised by the channel regions

- H10K10/486—Insulated gate field-effect transistors [IGFETs] characterised by the channel regions the channel region comprising two or more active layers, e.g. forming pn heterojunctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K85/00—Organic materials used in the body or electrodes of devices covered by this subclass

- H10K85/20—Carbon compounds, e.g. carbon nanotubes or fullerenes

- H10K85/221—Carbon nanotubes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K85/00—Organic materials used in the body or electrodes of devices covered by this subclass

- H10K85/60—Organic compounds having low molecular weight

- H10K85/615—Polycyclic condensed aromatic hydrocarbons, e.g. anthracene

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/734—Fullerenes, i.e. graphene-based structures, such as nanohorns, nanococoons, nanoscrolls or fullerene-like structures, e.g. WS2 or MoS2 chalcogenide nanotubes, planar C3N4, etc.

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/734—Fullerenes, i.e. graphene-based structures, such as nanohorns, nanococoons, nanoscrolls or fullerene-like structures, e.g. WS2 or MoS2 chalcogenide nanotubes, planar C3N4, etc.

- Y10S977/742—Carbon nanotubes, CNTs

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/734—Fullerenes, i.e. graphene-based structures, such as nanohorns, nanococoons, nanoscrolls or fullerene-like structures, e.g. WS2 or MoS2 chalcogenide nanotubes, planar C3N4, etc.

- Y10S977/742—Carbon nanotubes, CNTs

- Y10S977/745—Carbon nanotubes, CNTs having a modified surface

- Y10S977/749—Modified with dissimilar atoms or molecules substituted for carbon atoms of the cnt, e.g. impurity doping or compositional substitution

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/755—Nanosheet or quantum barrier/well, i.e. layer structure having one dimension or thickness of 100 nm or less

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/70—Nanostructure

- Y10S977/813—Of specified inorganic semiconductor composition, e.g. periodic table group IV-VI compositions

- Y10S977/815—Group III-V based compounds, e.g. AlaGabIncNxPyAsz

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/84—Manufacture, treatment, or detection of nanostructure

- Y10S977/849—Manufacture, treatment, or detection of nanostructure with scanning probe

- Y10S977/855—Manufacture, treatment, or detection of nanostructure with scanning probe for manufacture of nanostructure

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S977/00—Nanotechnology

- Y10S977/902—Specified use of nanostructure

- Y10S977/932—Specified use of nanostructure for electronic or optoelectronic application

- Y10S977/936—Specified use of nanostructure for electronic or optoelectronic application in a transistor or 3-terminal device

- Y10S977/938—Field effect transistors, FETS, with nanowire- or nanotube-channel region

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Ceramic Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Crystallography & Structural Chemistry (AREA)

- Mathematical Physics (AREA)

- Theoretical Computer Science (AREA)

- Materials Engineering (AREA)

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

Claims (11)

- トンネル・ナノチューブ電界効果トランジスタを製作する方法であって、

半導体特性を有する炭素(C)ナノチューブを設けるステップと、

前記トランジスタのチャネル領域、第1のドレイン/ソース領域、および第2のドレイン/ソース領域を前記ナノチューブに定義するステップであって、前記第1のドレイン/ソース領域が前記チャネル領域の第1の端に近接し、さらに前記第2のドレイン/ソース領域が前記チャネル領域の第2の端に近接しているステップと、

前記チャネル領域の上にゲート誘電体層を形成するステップと、

前記ゲート誘電体層の上にゲート電極を形成するステップと、

n型ドーパントを使用して前記第1のドレイン/ソース領域に選択的にドープするステップと、

p型ドーパントを使用して前記第2のドレイン/ソース領域に選択的にドープするステップと、

前記ゲート電極および前記ドレイン/ソース領域の各々に少なくとも1つの電気コンタクトを形成するステップと、を含む方法。 - 前記n型ドーパントをドープするステップによってドープされた前記第1のドレイン/ソース領域と、前記p型ドーパントをドープするステップによってドープされた前記第2のドレイン/ソース領域とは、前記チャネル領域で電荷担体の量子力学的トンネリングを可能にする、請求項1に記載の方法。

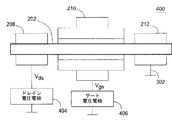

- トンネル・ナノチューブ電界効果トランジスタであって、

炭素(C)ナノチューブに画定された、半導体特性を有するチャネル領域と、

前記チャネル領域の上に形成されたゲート誘電体層と、

前記ゲート誘電体層の上に形成されたゲート電極と、

前記チャネル領域の第1の端に近接して前記ナノチューブに形成された第1のドレイン/ソース領域であって、n型ドーパントを使用して選択的にドープされた第1のドレイン/ソース領域と、

前記チャネル領域の第2の端に近接して前記ナノチューブに形成された第2のドレイン/ソース領域であって、p型ドーパントを使用して選択的にドープされた第2のドレイン/ソース領域と、

前記ゲート電極および前記ドレイン/ソース領域の各々の上の少なくとも1つの電気コンタクトと、を備えるトンネル・ナノチューブ電界効果トランジスタ。 - 前記第1のドレイン/ソース領域が接地電位の電源に結合され、前記第2のドレイン/ソース領域がドレイン電圧の電源に結合され、さらに前記ゲート電極がゲート電圧の電源に結合され、それによってp型トランジスタ・デバイスを形成している、請求項3に記載のトランジスタ。

- 前記第2のドレイン/ソース領域が接地電位の電源に結合され、前記第1のドレイン/ソース領域がドレイン電圧の電源に結合され、さらに前記ゲート電極がゲート電圧の電源に結合され、それによってn型トランジスタ・デバイスを形成している、請求項3に記載のトランジスタ。

- 前記ナノチューブが、軸方向の開口を有しない、請求項3に記載のトランジスタ。

- 前記ナノチューブの外径が、5nm未満である、請求項3に記載のトランジスタ。

- 前記n型ドーパントでドープされた前記第1のドレイン/ソース領域と前記p型ドーパントでドープされた前記第2のドレイン/ソース領域とは、前記チャネル領域で電荷担体の量子力学的トンネリングを可能にする、請求項3に記載のトランジスタ。

- 前記n型ドーパントが、カリウム(K)、ナトリウム(Na)、およびポリエチレンイミン分子のうちの少なくとも1つを含む、請求項3に記載のトランジスタ。

- 前記p型ドーパントが、塩素(Cl2)および臭素(Br2)のうちの少なくとも1つを含む、請求項3に記載のトランジスタ。

- 前記ゲート誘電体層が、SiO2、HfO2、およびAl2O3のうちの少なくとも1つで1から10nmの厚さに形成されている、請求項3に記載のトランジスタ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/852,891 US7180107B2 (en) | 2004-05-25 | 2004-05-25 | Method of fabricating a tunneling nanotube field effect transistor |

| US10/852,891 | 2004-05-25 | ||

| PCT/US2005/018201 WO2006073477A2 (en) | 2004-05-25 | 2005-05-24 | Method of fabricating a tunneling nanotube field effect transistor |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008500735A JP2008500735A (ja) | 2008-01-10 |

| JP2008500735A5 JP2008500735A5 (ja) | 2008-05-22 |

| JP5263755B2 true JP5263755B2 (ja) | 2013-08-14 |

Family

ID=35459605

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007515262A Expired - Fee Related JP5263755B2 (ja) | 2004-05-25 | 2005-05-24 | トンネル・ナノチューブ電界効果トランジスタおよびそれを製作する方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US7180107B2 (ja) |

| EP (1) | EP1754262B1 (ja) |

| JP (1) | JP5263755B2 (ja) |

| CN (1) | CN101065811B (ja) |

| TW (1) | TWI339852B (ja) |

| WO (1) | WO2006073477A2 (ja) |

Families Citing this family (54)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB0415891D0 (en) * | 2004-07-16 | 2004-08-18 | Koninkl Philips Electronics Nv | Nanoscale fet |

| KR101025846B1 (ko) * | 2004-09-13 | 2011-03-30 | 삼성전자주식회사 | 탄소나노튜브 채널을 포함하는 반도체 장치의 트랜지스터 |

| WO2006077585A2 (en) * | 2005-01-18 | 2006-07-27 | Shye Shapira | Apparatus and method for control of tunneling in a small-scale electronic structure |

| KR100682925B1 (ko) * | 2005-01-26 | 2007-02-15 | 삼성전자주식회사 | 멀티비트 비휘발성 메모리 소자 및 그 동작 방법 |

| DE102005046427B4 (de) * | 2005-09-28 | 2010-09-23 | Infineon Technologies Ag | Leistungstransistor mit parallelgeschalteten Nanodrähten |

| US7492015B2 (en) * | 2005-11-10 | 2009-02-17 | International Business Machines Corporation | Complementary carbon nanotube triple gate technology |

| WO2007086009A1 (en) * | 2006-01-25 | 2007-08-02 | Nxp B.V. | Nanowire tunneling transistor |

| JP5029600B2 (ja) * | 2006-03-03 | 2012-09-19 | 富士通株式会社 | カーボンナノチューブを用いた電界効果トランジスタとその製造方法及びセンサ |

| CN100435351C (zh) * | 2006-04-28 | 2008-11-19 | 北京芯技佳易微电子科技有限公司 | 利用偶极效应调制纳米级场效应晶体管的输运特性的方法 |

| EP1901355B1 (en) * | 2006-09-15 | 2015-11-11 | Imec | Tunnel effect transistors based on monocrystalline nanowires having a heterostructure |

| EP1900681B1 (en) | 2006-09-15 | 2017-03-15 | Imec | Tunnel Field-Effect Transistors based on silicon nanowires |

| US7893476B2 (en) * | 2006-09-15 | 2011-02-22 | Imec | Tunnel effect transistors based on silicon nanowires |

| EP1901354B1 (en) | 2006-09-15 | 2016-08-24 | Imec | A tunnel field-effect transistor with gated tunnel barrier |

| JP5171161B2 (ja) * | 2006-09-15 | 2013-03-27 | アイメック | ナノワイヤトンネル電界効果トランジスタ半導体装置およびその製造方法 |

| US8120115B2 (en) * | 2007-03-12 | 2012-02-21 | Imec | Tunnel field-effect transistor with gated tunnel barrier |

| WO2008157509A2 (en) * | 2007-06-14 | 2008-12-24 | University Of Florida Research Foundation, Inc. | Room temperature carbon nanotubes integrated on cmos |

| US8378333B2 (en) * | 2007-09-27 | 2013-02-19 | University Of Maryland | Lateral two-terminal nanotube devices and method for their formation |

| US8043978B2 (en) * | 2007-10-11 | 2011-10-25 | Riken | Electronic device and method for producing electronic device |

| EP2161755A1 (en) * | 2008-09-05 | 2010-03-10 | University College Cork-National University of Ireland, Cork | Junctionless Metal-Oxide-Semiconductor Transistor |

| US8912522B2 (en) * | 2009-08-26 | 2014-12-16 | University Of Maryland | Nanodevice arrays for electrical energy storage, capture and management and method for their formation |

| US10032569B2 (en) * | 2009-08-26 | 2018-07-24 | University Of Maryland, College Park | Nanodevice arrays for electrical energy storage, capture and management and method for their formation |

| US8288803B2 (en) * | 2009-08-31 | 2012-10-16 | International Business Machines Corporation | Tunnel field effect devices |

| CN102576726B (zh) | 2009-09-30 | 2015-01-07 | 国立大学法人北海道大学 | 隧道场效应晶体管及其制造方法 |

| US8173993B2 (en) * | 2009-12-04 | 2012-05-08 | International Business Machines Corporation | Gate-all-around nanowire tunnel field effect transistors |

| US8384065B2 (en) * | 2009-12-04 | 2013-02-26 | International Business Machines Corporation | Gate-all-around nanowire field effect transistors |

| US8129247B2 (en) * | 2009-12-04 | 2012-03-06 | International Business Machines Corporation | Omega shaped nanowire field effect transistors |

| US8143113B2 (en) * | 2009-12-04 | 2012-03-27 | International Business Machines Corporation | Omega shaped nanowire tunnel field effect transistors fabrication |

| US8097515B2 (en) * | 2009-12-04 | 2012-01-17 | International Business Machines Corporation | Self-aligned contacts for nanowire field effect transistors |

| US8455334B2 (en) | 2009-12-04 | 2013-06-04 | International Business Machines Corporation | Planar and nanowire field effect transistors |

| EP2517250A1 (en) * | 2009-12-21 | 2012-10-31 | Imec | Double gate nanostructure fet |

| US8722492B2 (en) | 2010-01-08 | 2014-05-13 | International Business Machines Corporation | Nanowire pin tunnel field effect devices |

| CN101777499B (zh) | 2010-01-22 | 2011-08-24 | 北京大学 | 一种基于平面工艺自对准制备隧穿场效应晶体管的方法 |

| US8324940B2 (en) | 2010-04-13 | 2012-12-04 | International Business Machines Corporation | Nanowire circuits in matched devices |

| US8361907B2 (en) | 2010-05-10 | 2013-01-29 | International Business Machines Corporation | Directionally etched nanowire field effect transistors |

| US8324030B2 (en) | 2010-05-12 | 2012-12-04 | International Business Machines Corporation | Nanowire tunnel field effect transistors |

| US8445320B2 (en) * | 2010-05-20 | 2013-05-21 | International Business Machines Corporation | Graphene channel-based devices and methods for fabrication thereof |

| US8835231B2 (en) | 2010-08-16 | 2014-09-16 | International Business Machines Corporation | Methods of forming contacts for nanowire field effect transistors |

| US8536563B2 (en) | 2010-09-17 | 2013-09-17 | International Business Machines Corporation | Nanowire field effect transistors |

| KR101733050B1 (ko) | 2010-11-22 | 2017-05-08 | 삼성전자주식회사 | 3개의 단자를 갖는 공진기 및 그 제조 방법 |

| CN102683209B (zh) * | 2011-03-18 | 2015-01-21 | 中国科学院微电子研究所 | 一种半导体器件及其制造方法 |

| CN103094347B (zh) * | 2013-01-11 | 2015-09-02 | 南京邮电大学 | 一种双材料欠叠异质栅结构的碳纳米管场效应管 |

| CN103247688B (zh) * | 2013-04-22 | 2016-08-17 | 南京邮电大学 | 一种双材料栅线性掺杂的石墨烯场效应管 |

| US8975123B2 (en) | 2013-07-09 | 2015-03-10 | International Business Machines Corporation | Tunnel field-effect transistors with a gate-swing broken-gap heterostructure |

| US9203041B2 (en) * | 2014-01-31 | 2015-12-01 | International Business Machines Corporation | Carbon nanotube transistor having extended contacts |

| CN105097904B (zh) | 2014-05-05 | 2019-01-25 | 中芯国际集成电路制造(上海)有限公司 | 隧穿碳纳米管场效应晶体管及其制造方法 |

| CN105097913B (zh) * | 2014-05-05 | 2018-12-04 | 中芯国际集成电路制造(上海)有限公司 | 场效应晶体管及其制造方法 |

| KR102154185B1 (ko) | 2014-09-19 | 2020-09-09 | 삼성전자 주식회사 | 반도체 소자 |

| CN105990147B (zh) * | 2015-02-27 | 2019-01-22 | 中芯国际集成电路制造(上海)有限公司 | 一种半导体器件及其制作方法和电子装置 |

| CN106601738B (zh) * | 2015-10-15 | 2018-08-24 | 上海新昇半导体科技有限公司 | 互补场效应晶体管及其制备方法 |

| JP6730598B2 (ja) * | 2016-07-19 | 2020-07-29 | 富士通株式会社 | 半導体装置 |

| US10170702B2 (en) | 2017-01-12 | 2019-01-01 | International Business Machines Corporation | Intermetallic contact for carbon nanotube FETs |

| JP6773615B2 (ja) * | 2017-08-21 | 2020-10-21 | 日本電信電話株式会社 | ナノワイヤトランジスタの製造方法 |

| US10818785B2 (en) * | 2017-12-04 | 2020-10-27 | Ecole Polytechnique Federale De Lausanne (Epfl) | Sensing device for sensing minor charge variations |

| CN108598170B (zh) * | 2018-05-24 | 2022-07-08 | 厦门半导体工业技术研发有限公司 | 纳米线晶体管及其制作方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US130333A (en) * | 1872-08-06 | Improvement in machines for glazing and polishing saw-blades | ||

| JPS5754370A (en) * | 1980-09-19 | 1982-03-31 | Nippon Telegr & Teleph Corp <Ntt> | Insulating gate type transistor |

| JP2773474B2 (ja) * | 1991-08-06 | 1998-07-09 | 日本電気株式会社 | 半導体装置 |

| JP3393237B2 (ja) | 1994-10-04 | 2003-04-07 | ソニー株式会社 | 半導体装置の製造方法 |

| US6331262B1 (en) * | 1998-10-02 | 2001-12-18 | University Of Kentucky Research Foundation | Method of solubilizing shortened single-walled carbon nanotubes in organic solutions |

| EP1299914B1 (de) * | 2000-07-04 | 2008-04-02 | Qimonda AG | Feldeffekttransistor |

| JP2002026154A (ja) * | 2000-07-11 | 2002-01-25 | Sanyo Electric Co Ltd | 半導体メモリおよび半導体装置 |

| CN1251962C (zh) | 2000-07-18 | 2006-04-19 | Lg电子株式会社 | 水平生长碳纳米管的方法和使用碳纳米管的场效应晶体管 |

| US6524920B1 (en) | 2001-02-09 | 2003-02-25 | Advanced Micro Devices, Inc. | Low temperature process for a transistor with elevated source and drain |

| JP3731486B2 (ja) | 2001-03-16 | 2006-01-05 | 富士ゼロックス株式会社 | トランジスタ |

| JP2003017508A (ja) | 2001-07-05 | 2003-01-17 | Nec Corp | 電界効果トランジスタ |

| AU2003215840A1 (en) | 2002-03-28 | 2003-10-13 | Koninklijke Philips Electronics N.V. | Nanowire and electronic device |

| JP4974263B2 (ja) * | 2002-05-20 | 2012-07-11 | 富士通株式会社 | 半導体装置の製造方法 |

| CN1176499C (zh) * | 2002-06-13 | 2004-11-17 | 上海交通大学 | 纳米金属氧化线单电子晶体管 |

| JP2004055649A (ja) * | 2002-07-17 | 2004-02-19 | Konica Minolta Holdings Inc | 有機薄膜トランジスタ及びその製造方法 |

| US7115916B2 (en) | 2002-09-26 | 2006-10-03 | International Business Machines Corporation | System and method for molecular optical emission |

| EP2218681A2 (en) * | 2002-09-30 | 2010-08-18 | Nanosys, Inc. Et AL. | Applications of Nano-Enabled Large Area Macroelectronic Substrates Incorporating Nanowires and Nanowire Composites |

| US6933222B2 (en) * | 2003-01-02 | 2005-08-23 | Intel Corporation | Microcircuit fabrication and interconnection |

-

2004

- 2004-05-25 US US10/852,891 patent/US7180107B2/en not_active Expired - Lifetime

-

2005

- 2005-05-20 TW TW094116452A patent/TWI339852B/zh not_active IP Right Cessation

- 2005-05-24 CN CN2005800165130A patent/CN101065811B/zh active Active

- 2005-05-24 EP EP05856753.8A patent/EP1754262B1/en active Active

- 2005-05-24 WO PCT/US2005/018201 patent/WO2006073477A2/en not_active Application Discontinuation

- 2005-05-24 JP JP2007515262A patent/JP5263755B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP1754262A2 (en) | 2007-02-21 |

| CN101065811B (zh) | 2011-03-30 |

| EP1754262A4 (en) | 2012-03-14 |

| TW200603228A (en) | 2006-01-16 |

| CN101065811A (zh) | 2007-10-31 |

| US20050274992A1 (en) | 2005-12-15 |

| TWI339852B (en) | 2011-04-01 |

| WO2006073477A2 (en) | 2006-07-13 |

| WO2006073477A3 (en) | 2007-01-25 |

| EP1754262B1 (en) | 2015-04-08 |

| JP2008500735A (ja) | 2008-01-10 |

| US7180107B2 (en) | 2007-02-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5263755B2 (ja) | トンネル・ナノチューブ電界効果トランジスタおよびそれを製作する方法 | |

| JP5695255B2 (ja) | ヘテロ構造を有する細長い単結晶ナノ構造に基づくトンネル効果トランジスタ | |

| US8900935B2 (en) | Deposition on a nanowire using atomic layer deposition | |

| US7141727B1 (en) | Method and apparatus for fabricating a carbon nanotube transistor having unipolar characteristics | |

| US8120115B2 (en) | Tunnel field-effect transistor with gated tunnel barrier | |

| US7709827B2 (en) | Vertically integrated field-effect transistor having a nanostructure therein | |

| JP5171161B2 (ja) | ナノワイヤトンネル電界効果トランジスタ半導体装置およびその製造方法 | |

| US10381586B2 (en) | Carbon nanotube field-effect transistor with sidewall-protected metal contacts | |

| US20070012961A1 (en) | N-type carbon nanotube field effect transistor and method of fabricating the same | |

| JP2008500735A5 (ja) | ||

| US7511344B2 (en) | Field effect transistor | |

| Xie et al. | Highly-scaled self-aligned GaN complementary technology on a GaN-on-Si platform | |

| US20170162806A1 (en) | Carbon nanotube device with n-type end-bonded metal contacts | |

| Liu et al. | Vertical heterojunction Ge0. 92Sn0. 08/Ge gate-all-around nanowire pMOSFETs with NiGeSn contact | |

| Liu et al. | Vertical heterojunction Ge0. 92Sn0. 08/Ge gate-all-around nanowire pMOSFETs | |

| US10141529B1 (en) | Enhancing drive current and increasing device yield in N-type carbon nanotube field effect transistors | |

| JP2018032662A (ja) | ダイヤモンドコンタクト構造とこれを用いた電子素子 | |

| Yang et al. | Schottky-Barrier Si nanowire MOSFET: Effects of source/drain metals and gate dielectrics | |

| CN113659077A (zh) | 一种半导体晶体管及其制备方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080328 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080328 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111006 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111018 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111227 |

|

| RD12 | Notification of acceptance of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7432 Effective date: 20111227 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20111227 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120727 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120803 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121227 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130128 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130326 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20130326 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130327 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A821 Effective date: 20130329 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130423 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5263755 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |