JP5255279B2 - 電極を基板内の他の導電性部材に接続する導電性部材を含む電子デバイス、および電子デバイスを形成するためのプロセス - Google Patents

電極を基板内の他の導電性部材に接続する導電性部材を含む電子デバイス、および電子デバイスを形成するためのプロセス Download PDFInfo

- Publication number

- JP5255279B2 JP5255279B2 JP2007549671A JP2007549671A JP5255279B2 JP 5255279 B2 JP5255279 B2 JP 5255279B2 JP 2007549671 A JP2007549671 A JP 2007549671A JP 2007549671 A JP2007549671 A JP 2007549671A JP 5255279 B2 JP5255279 B2 JP 5255279B2

- Authority

- JP

- Japan

- Prior art keywords

- conductive member

- electrode

- organic layer

- forming

- conductive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000000758 substrate Substances 0.000 title claims description 74

- 238000000034 method Methods 0.000 title claims description 72

- 230000008569 process Effects 0.000 title description 19

- 239000010410 layer Substances 0.000 claims description 139

- 239000012044 organic layer Substances 0.000 claims description 127

- 230000005855 radiation Effects 0.000 claims description 38

- 238000005530 etching Methods 0.000 claims description 29

- 125000006850 spacer group Chemical group 0.000 claims description 23

- 230000005540 biological transmission Effects 0.000 claims description 22

- 238000001035 drying Methods 0.000 claims description 5

- 239000000463 material Substances 0.000 description 51

- 239000007789 gas Substances 0.000 description 36

- 238000004519 manufacturing process Methods 0.000 description 16

- 230000000873 masking effect Effects 0.000 description 15

- 238000000151 deposition Methods 0.000 description 14

- 230000008901 benefit Effects 0.000 description 11

- 238000001312 dry etching Methods 0.000 description 11

- 239000011261 inert gas Substances 0.000 description 10

- 239000000203 mixture Substances 0.000 description 10

- 238000007796 conventional method Methods 0.000 description 9

- 230000008021 deposition Effects 0.000 description 9

- 238000005516 engineering process Methods 0.000 description 9

- 238000005538 encapsulation Methods 0.000 description 7

- 229910052736 halogen Inorganic materials 0.000 description 7

- 150000002367 halogens Chemical class 0.000 description 7

- 229910052751 metal Inorganic materials 0.000 description 7

- 239000002184 metal Substances 0.000 description 7

- 230000002093 peripheral effect Effects 0.000 description 7

- 238000001228 spectrum Methods 0.000 description 7

- 230000015572 biosynthetic process Effects 0.000 description 6

- 239000003990 capacitor Substances 0.000 description 6

- 239000002274 desiccant Substances 0.000 description 6

- 239000011159 matrix material Substances 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 239000000356 contaminant Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 239000004065 semiconductor Substances 0.000 description 5

- 229920001609 Poly(3,4-ethylenedioxythiophene) Polymers 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 238000013461 design Methods 0.000 description 4

- 238000001514 detection method Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000005525 hole transport Effects 0.000 description 4

- 238000002347 injection Methods 0.000 description 4

- 239000007924 injection Substances 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 230000003071 parasitic effect Effects 0.000 description 4

- 238000001020 plasma etching Methods 0.000 description 4

- 229920000767 polyaniline Polymers 0.000 description 4

- 238000012545 processing Methods 0.000 description 4

- 230000002829 reductive effect Effects 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 240000007320 Pinus strobus Species 0.000 description 3

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 3

- 229910052739 hydrogen Inorganic materials 0.000 description 3

- 238000000608 laser ablation Methods 0.000 description 3

- 229920002120 photoresistant polymer Polymers 0.000 description 3

- 239000011359 shock absorbing material Substances 0.000 description 3

- 238000003860 storage Methods 0.000 description 3

- 239000000126 substance Substances 0.000 description 3

- BSYNRYMUTXBXSQ-UHFFFAOYSA-N Aspirin Chemical compound CC(=O)OC1=CC=CC=C1C(O)=O BSYNRYMUTXBXSQ-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 238000005352 clarification Methods 0.000 description 2

- 239000004020 conductor Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 238000010981 drying operation Methods 0.000 description 2

- 230000003628 erosive effect Effects 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000001257 hydrogen Substances 0.000 description 2

- 238000009616 inductively coupled plasma Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 238000010849 ion bombardment Methods 0.000 description 2

- 238000010884 ion-beam technique Methods 0.000 description 2

- 150000002500 ions Chemical class 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- -1 member Substances 0.000 description 2

- 229910044991 metal oxide Inorganic materials 0.000 description 2

- 150000004706 metal oxides Chemical class 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- NJPPVKZQTLUDBO-UHFFFAOYSA-N novaluron Chemical compound C1=C(Cl)C(OC(F)(F)C(OC(F)(F)F)F)=CC=C1NC(=O)NC(=O)C1=C(F)C=CC=C1F NJPPVKZQTLUDBO-UHFFFAOYSA-N 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000000737 periodic effect Effects 0.000 description 2

- 238000005240 physical vapour deposition Methods 0.000 description 2

- 229920000642 polymer Polymers 0.000 description 2

- 230000002441 reversible effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 238000000992 sputter etching Methods 0.000 description 2

- 229910052715 tantalum Inorganic materials 0.000 description 2

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 229920001621 AMOLED Polymers 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- NINIDFKCEFEMDL-UHFFFAOYSA-N Sulfur Chemical compound [S] NINIDFKCEFEMDL-UHFFFAOYSA-N 0.000 description 1

- 230000004913 activation Effects 0.000 description 1

- 230000002730 additional effect Effects 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- AXCZMVOFGPJBDE-UHFFFAOYSA-L calcium dihydroxide Chemical compound [OH-].[OH-].[Ca+2] AXCZMVOFGPJBDE-UHFFFAOYSA-L 0.000 description 1

- 239000000920 calcium hydroxide Substances 0.000 description 1

- 229910001861 calcium hydroxide Inorganic materials 0.000 description 1

- 229910010293 ceramic material Inorganic materials 0.000 description 1

- 239000002800 charge carrier Substances 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 239000003086 colorant Substances 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 239000000306 component Substances 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000005137 deposition process Methods 0.000 description 1

- 239000011532 electronic conductor Substances 0.000 description 1

- 230000003203 everyday effect Effects 0.000 description 1

- 230000005284 excitation Effects 0.000 description 1

- 239000000835 fiber Substances 0.000 description 1

- NBVXSUQYWXRMNV-UHFFFAOYSA-N fluoromethane Chemical compound FC NBVXSUQYWXRMNV-UHFFFAOYSA-N 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 238000007641 inkjet printing Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 238000012886 linear function Methods 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000011368 organic material Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 239000011241 protective layer Substances 0.000 description 1

- 238000010926 purge Methods 0.000 description 1

- 230000009257 reactivity Effects 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 150000003384 small molecules Chemical class 0.000 description 1

- 239000011734 sodium Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 230000003595 spectral effect Effects 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 239000011593 sulfur Substances 0.000 description 1

- 239000013077 target material Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/131—Interconnections, e.g. wiring lines or terminals

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K77/00—Constructional details of devices covered by this subclass and not covered by groups H10K10/80, H10K30/80, H10K50/80 or H10K59/80

- H10K77/10—Substrates, e.g. flexible substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/027—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34

- H01L21/0271—Making masks on semiconductor bodies for further photolithographic processing not provided for in group H01L21/18 or H01L21/34 comprising organic layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/28008—Making conductor-insulator-semiconductor electrodes

- H01L21/28017—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon

- H01L21/28026—Making conductor-insulator-semiconductor electrodes the insulator being formed after the semiconductor body, the semiconductor being silicon characterised by the conductor

- H01L21/28123—Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects

- H01L21/28132—Lithography-related aspects, e.g. sub-lithography lengths; Isolation-related aspects, e.g. to solve problems arising at the crossing with the side of the device isolation; Planarisation aspects conducting part of electrode is difined by a sidewall spacer or a similar technique, e.g. oxidation under mask, plating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/11—OLEDs or polymer light-emitting diodes [PLED] characterised by the electroluminescent [EL] layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/10—OLEDs or polymer light-emitting diodes [PLED]

- H10K50/14—Carrier transporting layers

- H10K50/15—Hole transporting layers

- H10K50/156—Hole transporting layers comprising a multilayered structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/60—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation

- H01L2021/60007—Attaching or detaching leads or other conductive members, to be used for carrying current to or from the device in operation involving a soldering or an alloying process

- H01L2021/6027—Mounting on semiconductor conductive members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/1201—Manufacture or treatment

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

- Y02E10/549—Organic PV cells

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Optics & Photonics (AREA)

- Electroluminescent Light Sources (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

Description

以下で説明される実施形態の詳細を扱う前、いくつかの用語を定義または明確化する。ここで使用されるように、層または材料に言及するときの「活性」という用語は、電気放射特性または電磁特性を示す層または材料を意味することが意図される。活性層材料は、放射線を放出することができるか、放射線を受けるとき電子−正孔対の濃度の変化を示すことができる。

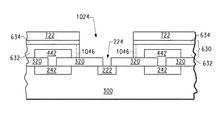

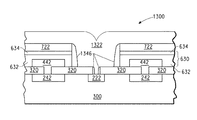

図1は、ピクセル102、104、106、および108を含む電子デバイス100内のアレイの一部の回路図を含む。代替実施形態において、ピクセル102、104、106、および108の各々は、サブピクセルであることができる。本明細書の目的のため、ピクセルという用語が使用されるが、当業者は、ここで説明される概念を、ピクセル内のサブピクセルに拡大することができることを理解するであろう。図1に示されているように、ピクセル102、104、106、および108の各々は、選択トランジスタ122と、蓄積キャパシタ124と、駆動トランジスタ126とを含むピクセル駆動回路を含む。選択トランジスタ122のゲート電極が選択線142に接続される。一実施形態において、選択線142は時間の関数として活性化され、したがって、各選択線142は走査線である。選択トランジスタ122の第1のソース/ドレイン領域が、データ線144に接続される。選択トランジスタ122の第2のソース/ドレイン領域、蓄積キャパシタ124の第1の電極、および駆動トランジスタ126のゲート電極が、互いに接続される。駆動トランジスタ126の第1のソース/ドレイン領域が、電子部品128のアノードに接続される。一実施形態において、電子部品128は放射線放出部品であり、別の実施形態において、電子部品128は放射線応答部品である。電子部品128のカソードが、この実施形態においてVss線148である電力伝送線に接続される。蓄積キャパシタ124の第2の電極、および駆動トランジスタ126の第2のソース/ドレイン領域が、この実施形態においてVdd線146である別の電力伝送線に接続される。本明細書を読んだ後、当業者は、アレイが、1つまたは複数の方向に延在することができ、かつ、ほとんどいかなる有限数の、図1に示されたものと同様のピクセルを含むことができることを理解するであろう。

いくつかの追加の代替実施形態を以下で説明する。ここで説明される代替実施形態は、多くの他の実施形態が可能であるので、本発明の範囲を例示し、限定しないことが意図される。

ここで説明される実施形態は、ここで説明されるような利点のいずれか1つまたは複数を有することができる。一実施形態において、ピクセル駆動回路242を含む基板300を、1つの製造業者によって製造することができ、電子部品128を、異なった製造業者によって製造することができる。基板300の製造業者は、電子デバイス100、1200、または1300のための端子接続および電力伝送線をすでに含むことができる。したがって、異なった製造業者が、電子デバイス100、1200、または1300の製造を開始するとき、第2の導電性部材222は、すでに存在することができる。第3の導電性部材1122、1222、1322、またはそれらの任意の組合せは、追加の基板領域を消費することなく、第2の電極722と第2の導電性部材222との間の接続を可能にする。

[1]第1のピクセル駆動回路、第1の導電性部材、および第2の導電性部材を含む基板であって、前記第1および第2の導電性部材が互いに隔置され、前記第1の導電性部材が前記第1のピクセル駆動回路に接続され、前記第2の導電性部材が電力伝送線の一部である、基板と、第1の電子部品、前記第1の導電性部材と接触する第1の電極、前記第2の導電性部材に接続されるが接触しない第2の電極、および前記第1の電極と前記第2の電極との間にある有機層を含む第1の電子部品と、第3の導電性部材であって、前記第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材と接触する第3の導電性部材とを備えたことを特徴とする電子デバイス。

[2]前記基板が、前記第1のピクセル駆動回路を含む複数のピクセル駆動回路と、追加の第1の導電性部材と、追加の第2の導電性部材とを含み、前記第1の導電性部材の各々が、前記第2の導電性部材の各々から隔置され、前記電子デバイスが、前記第1の電子部品を含む電子部品のアレイを含み、前記電子部品の各々が、前記第1の導電性部材の少なくとも1つと接触する第1の電極と、前記第2の導電性部材の少なくとも1つに接続されるが、前記第2の導電性部材のいずれにも接触しない第2の電極とを含み、前記有機層が、前記第1の電極と前記第2の電極との間にあり、前記第3の導電性部材が、第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材の少なくともいくつかと接触することを特徴とする[1]に記載の電子デバイス。

[3]前記電子部品が、前記第1の電子部品と同じ行または同じ列に沿って配置された第2の電子部品を含むことを特徴とする[2]に記載の電子デバイス。

[4]前記電子部品が、前記第1の電子部品と異なった行および異なった列に沿って配置された第2の電子部品を含むことを特徴とする[2]に記載の電子デバイス。

[5]前記第3の導電性部材が、すべてではないがいくつかの前記電子部品の第2の電極と接触することを特徴とする[2]に記載の電子デバイス。

[6]前記第3の導電性部材が、前記アレイ内の前記第2の導電性部材の実質的にすべてと接触することを特徴とする[2]に記載の電子デバイス。

[7]前記第3の導電性部材が、第2の導電性電極と接触することを特徴とする[1]に記載の電子デバイス。

[8]前記有機層が、前記第1の電極と前記第2の電極との間にある導電性部分と、前記第2の導電性部材および前記第3の導電性部材が前記導電性部分と接触するのを実質的に防止する抵抗部分とを含むことを特徴とする[1]に記載の電子デバイス。

[9]前記第3の導電性部材を前記有機層から絶縁する側壁スペーサをさらに備えたことを特徴とする[1]に記載の電子デバイス。

[10]前記有機層が有機活性層を含むことを特徴とする[1]に記載の電子デバイス。

[11]前記第1の電子部品が、放射線放出電子部品または放射線応答電子部品を含むことを特徴とする[10]に記載の電子デバイス。

[12]前記電力伝送線がVdd線またはVss線であることを特徴とする[1]に記載の電子デバイス。

[13]電子デバイスを形成するための方法であって、第1の電極を、基板内の第1の導電性部材の上に形成する工程であって、前記基板が、第1のピクセル駆動回路と、前記第1の導電性部材と、第2の導電性部材とを含み、前記第1および第2の導電性部材が互いに隔置され、前記第1の導電性部材が前記第1のピクセル駆動回路に接続され、前記第2の導電性部材が電力伝送線の一部である第1の電極を形成する工程と、第1の有機層を前記第1および第2の電極の上に形成する工程と、第2の電極を、前記第2の導電性部材の上にこないように前記第1の有機層の上に形成する工程と、前記第2の電極によって被覆されない、前記第1の有機層の露出された部分を除去して、前記第2の導電性部材を露出する工程と、第3の導電性部材を露出する工程であって、前記第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材と接触する第3の導電性部材を形成する工程とを有することを特徴とする方法。

[14]前記第1の有機層の露出された部分を除去する工程が、前記第2の導電性部材に隣接した側壁を形成し、前記側壁に隣接した前記第1の有機層の抵抗部分を形成する工程をさらに有することを特徴とする[13]に記載の方法。

[15]前記第1の有機層の抵抗部分を形成する工程が、前記第1の有機層を乾燥処理作業に曝す工程を含むことを特徴とする[14]に記載の方法。

[16]前記第1の有機層の露出された部分を除去した後、絶縁層を形成する工程と、前記絶縁層を異方性エッチングして、前記第1の有機層の露出された部分の側壁に沿って側壁スペーサを形成する工程とをさらに有することを特徴とする[13]に記載の方法。

[17]前記基板が、前記第1のピクセル駆動回路を含む複数のピクセル駆動回路と、付加的な第1の導電性部材と、付加的な第2の導電性部材とを含み、前記第1の導電性部材の各々が、前記第2の導電性部材から隔置され、前記電子デバイスが電子部品のアレイを含み、前記ピクセル駆動回路が前記アレイ内にあり、前記第1の電極を形成する工程が、前記第1の電極を前記第1の導電性部材の上に形成する工程を含み、前記第2の電極を形成する工程が、前記第2の電極を、前記アレイ内の第2の導電性部材のいずれの上にもなく前記第1の有機層の上に形成する工程を含み、前記第1の有機層の部分を除去する工程が、前記第1の有機層の、前記第2の電極によって被覆されない部分を除去して、前記第2の導電性部材を露出する工程を含み、前記第3の導電性部材を形成する工程が、前記第3の導電性部材が、前記第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材の少なくともいくつかと接触するように、前記第3の導電性部材を形成する工程を含むことを特徴とする[13]に記載の方法。

[18]前記第1の電極を形成した後であって、かつ前記第2の電極を形成する前に、有機活性層を形成する工程をさらに有することを特徴とする[13]に記載の方法。

[19]第1の電子部品が、放射線放出電子部品または放射線応答電子部品を含むことを特徴とする[18]に記載の方法。

[20]前記第3の導電性部材が前記第2の電極と接触することを特徴とする[13]に記載の方法。

[21]前記電力伝送線がVdd線またはVss線であることを特徴とする[13]に記載の方法。

Claims (10)

- 電子デバイスを形成するための方法であって、

第1の電極を、基板内の第1の導電性部材の上に形成するステップであって、

前記基板が、第1のピクセル駆動回路と、前記第1の導電性部材と、第2の導電性部材とを含み、

前記第1および第2の導電性部材が互いに隔置され、

前記第1の導電性部材が前記第1のピクセル駆動回路に接続され、

前記第2の導電性部材が電力伝送線の一部である、ステップと、

第1の有機層を前記第1の電極の上に形成するステップと、

開口部を有する第2の電極を前記第1の有機層の上に形成するステップであって、前記第2の電極は前記第2の導電性部材を跨がないようにし、前記開口部は少なくとも前記第1の有機層の一部を露出させる、ステップと、

前記第2の電極によって被覆されない、前記第1の有機層の露出された部分を除去して、前記第2の導電性部材を露出するステップと、

第3の導電性部材を露出するステップであって、

前記第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材と接触する第3の導電性部材を形成するステップと

を有することを特徴とする方法。 - 前記第1の有機層の露出された部分を除去するステップが、前記第2の導電性部材に隣接した側壁を形成し、前記側壁に隣接した前記第1の有機層の抵抗部分を形成するステップをさらに有することを特徴とする請求項1に記載の方法。

- 前記第1の有機層の抵抗部分を形成するステップが、前記第1の有機層を乾燥処理作業に曝すステップを含むことを特徴とする請求項2に記載の方法。

- 前記第1の有機層の露出された部分を除去した後、絶縁層を形成するステップと、

前記絶縁層を異方性エッチングして、前記第1の有機層の露出された部分の側壁に沿って側壁スペーサを形成するステップと

をさらに有することを特徴とする請求項1に記載の方法。 - 前記基板が、

前記第1のピクセル駆動回路を含む複数のピクセル駆動回路と、

前記複数のピクセル駆動回路にそれぞれ接続された複数の前記第1の導電性部材と、

複数の前記第2の導電性部材とを含み、

前記第1の導電性部材の各々が、前記第2の導電性部材から隔置され、

前記電子デバイスが電子部品のアレイおよび前記アレイ内にある前記ピクセル駆動回路を含み、

前記第1の電極を形成するステップが、前記第1の電極を前記第1の導電性部材の上に形成するステップを含み、

前記第2の電極を形成するステップが、前記第1の有機層上に開口部を有する前記第2の電極を形成するステップを含み、前記第2の電極は前記第2の導電性部材のいずれも跨がず、前記開口部が前記第1の有機層の一部を露出させるステップを含み、

前記第1の有機層の一部を除去するステップが、前記第1の有機層の、前記第2の電極によって被覆されない部分を除去して、前記第2の導電性部材を露出するステップを含み、

前記第3の導電性部材が、前記第2の電極および前記第2の導電性部材に接続され、かつ、前記第2の導電性部材の少なくともいくつかと接触するように、前記第3の導電性部材を形成するステップを含むことを特徴とする請求項1に記載の方法。 - 前記第1の電極を形成した後であって、かつ前記第2の電極を形成する前に、有機活性層を形成する工程をさらに有することを特徴とする請求項1に記載の方法。

- 前記第1の電極、前記第2の電極、および前記第1の有機層を含む第1の電子部品が、放射線放出電子部品または放射線応答電子部品を含むことを特徴とする請求項6に記載の方法。

- 前記第3の導電性部材が前記第2の電極と接触することを特徴とする請求項1に記載の方法。

- 前記電力伝送線がVdd線またはVss線であることを特徴とする請求項1に記載の方法。

- 第1のピクセル駆動回路、第1の導電性部材、第2の導電性部材および開口部を有する絶縁層を含む基板であって、前記第1および第2の導電性部材が互いに隔置され、前記第1の導電性部材が前記第1のピクセル駆動回路に接続され、前記第2の導電性部材が電力伝送線の一部であり、前記絶縁層は前記第1のピクセル駆動回路、前記第1の導電性部材および第2の導電性部材の上に形成された、基板と、

第1の電子部品であって

前記絶縁層上に形成され、前記絶縁層の開口部を通って前記第1の導電性部材と接触する第1の電極、

前記第2の導電性部材に接続されるが接触しない開口部を有する第2の電極、および

前記第1の電極と前記第2の電極との間にある有機層

を含む第1の電子部品と、

第3の導電性部材であって

前記第2の電極および前記第2の導電性部材に接続され、かつ

前記絶縁層および前記第2の電極の開口部を通して前記第2の導電性部材と接触する

第3の導電性部材と

を備えたことを特徴とする電子デバイス。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/025,110 US7189991B2 (en) | 2004-12-29 | 2004-12-29 | Electronic devices comprising conductive members that connect electrodes to other conductive members within a substrate and processes for forming the electronic devices |

| US11/025,110 | 2004-12-29 | ||

| PCT/US2005/047519 WO2006072024A2 (en) | 2004-12-29 | 2005-12-29 | Electronic devices comprising conductive members that connect electrodes to other conductive members within a substrate and processes for forming the electronic devices |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008527424A JP2008527424A (ja) | 2008-07-24 |

| JP2008527424A5 JP2008527424A5 (ja) | 2009-02-19 |

| JP5255279B2 true JP5255279B2 (ja) | 2013-08-07 |

Family

ID=36610342

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007549671A Expired - Fee Related JP5255279B2 (ja) | 2004-12-29 | 2005-12-29 | 電極を基板内の他の導電性部材に接続する導電性部材を含む電子デバイス、および電子デバイスを形成するためのプロセス |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7189991B2 (ja) |

| EP (1) | EP1839336A4 (ja) |

| JP (1) | JP5255279B2 (ja) |

| KR (1) | KR101261653B1 (ja) |

| CN (1) | CN100505288C (ja) |

| TW (1) | TWI377711B (ja) |

| WO (1) | WO2006072024A2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7189991B2 (en) * | 2004-12-29 | 2007-03-13 | E. I. Du Pont De Nemours And Company | Electronic devices comprising conductive members that connect electrodes to other conductive members within a substrate and processes for forming the electronic devices |

| US7563392B1 (en) * | 2004-12-30 | 2009-07-21 | E.I. Du Pont De Nemours And Company | Organic conductive compositions and structures |

| DE102005037290A1 (de) * | 2005-08-08 | 2007-02-22 | Siemens Ag | Flachbilddetektor |

| US7642109B2 (en) * | 2005-08-29 | 2010-01-05 | Eastman Kodak Company | Electrical connection in OLED devices |

| US7638416B2 (en) * | 2005-12-13 | 2009-12-29 | Versatilis Llc | Methods of making semiconductor-based electronic devices on a wire and articles that can be made using such devices |

| US7700471B2 (en) * | 2005-12-13 | 2010-04-20 | Versatilis | Methods of making semiconductor-based electronic devices on a wire and articles that can be made thereby |

| JP5191650B2 (ja) * | 2005-12-16 | 2013-05-08 | シャープ株式会社 | 窒化物半導体発光素子および窒化物半導体発光素子の製造方法 |

| US8247824B2 (en) * | 2005-12-19 | 2012-08-21 | Matthew Stainer | Electronic devices comprising electrodes that connect to conductive members within a substrate and processes for forming the electronic devices |

| US7314786B1 (en) * | 2006-06-16 | 2008-01-01 | International Business Machines Corporation | Metal resistor, resistor material and method |

| US8153029B2 (en) * | 2006-12-28 | 2012-04-10 | E.I. Du Pont De Nemours And Company | Laser (230NM) ablatable compositions of electrically conducting polymers made with a perfluoropolymeric acid applications thereof |

| US8227877B2 (en) * | 2010-07-14 | 2012-07-24 | Macronix International Co., Ltd. | Semiconductor bio-sensors and methods of manufacturing the same |

| CN114616515A (zh) * | 2019-10-10 | 2022-06-10 | 康宁公司 | 用于形成包覆电极的系统及方法 |

| US11929388B2 (en) * | 2021-09-23 | 2024-03-12 | Apple Inc. | Local passive matrix displays |

Family Cites Families (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3530362B2 (ja) * | 1996-12-19 | 2004-05-24 | 三洋電機株式会社 | 自発光型画像表示装置 |

| KR100257811B1 (ko) * | 1997-10-24 | 2000-06-01 | 구본준 | 액정표시장치의 기판의 제조방법 |

| TW484238B (en) * | 2000-03-27 | 2002-04-21 | Semiconductor Energy Lab | Light emitting device and a method of manufacturing the same |

| KR100495702B1 (ko) * | 2001-04-13 | 2005-06-14 | 삼성에스디아이 주식회사 | 유기 전계 발광 표시 장치 및 그 제조 방법 |

| KR100437475B1 (ko) * | 2001-04-13 | 2004-06-23 | 삼성에스디아이 주식회사 | 평판 디스플레이 장치용 표시 소자 제조 방법 |

| US6900470B2 (en) * | 2001-04-20 | 2005-05-31 | Kabushiki Kaisha Toshiba | Display device and method of manufacturing the same |

| KR100682377B1 (ko) * | 2001-05-25 | 2007-02-15 | 삼성전자주식회사 | 유기 전계발광 디바이스 및 이의 제조 방법 |

| KR100443831B1 (ko) * | 2001-12-20 | 2004-08-09 | 엘지.필립스 엘시디 주식회사 | 액정표시소자의 제조 방법 |

| JP4310984B2 (ja) * | 2002-02-06 | 2009-08-12 | 株式会社日立製作所 | 有機発光表示装置 |

| US7190335B2 (en) * | 2002-03-26 | 2007-03-13 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and method of manufacturing the same |

| KR100435054B1 (ko) * | 2002-05-03 | 2004-06-07 | 엘지.필립스 엘시디 주식회사 | 유기전계 발광소자와 그 제조방법 |

| KR100478759B1 (ko) * | 2002-08-20 | 2005-03-24 | 엘지.필립스 엘시디 주식회사 | 유기전계 발광소자와 그 제조방법 |

| US7049636B2 (en) * | 2002-10-28 | 2006-05-23 | Universal Display Corporation | Device including OLED controlled by n-type transistor |

| KR100905473B1 (ko) | 2002-12-03 | 2009-07-02 | 삼성전자주식회사 | 유기 이엘 표시판 및 그 제조 방법 |

| JP3861816B2 (ja) | 2003-01-24 | 2006-12-27 | 住友電気工業株式会社 | 光送受信モジュール及びその製造方法 |

| CA2419704A1 (en) * | 2003-02-24 | 2004-08-24 | Ignis Innovation Inc. | Method of manufacturing a pixel with organic light-emitting diode |

| JP3915734B2 (ja) * | 2003-05-12 | 2007-05-16 | ソニー株式会社 | 蒸着マスクおよびこれを用いた表示装置の製造方法、ならびに表示装置 |

| US6953705B2 (en) * | 2003-07-22 | 2005-10-11 | E. I. Du Pont De Nemours And Company | Process for removing an organic layer during fabrication of an organic electronic device |

| CN1890698B (zh) * | 2003-12-02 | 2011-07-13 | 株式会社半导体能源研究所 | 显示器件及其制造方法和电视装置 |

| US7189991B2 (en) * | 2004-12-29 | 2007-03-13 | E. I. Du Pont De Nemours And Company | Electronic devices comprising conductive members that connect electrodes to other conductive members within a substrate and processes for forming the electronic devices |

| KR100700650B1 (ko) * | 2005-01-05 | 2007-03-27 | 삼성에스디아이 주식회사 | 유기 전계 발광 장치 및 그 제조 방법 |

| US7554261B2 (en) * | 2006-05-05 | 2009-06-30 | Eastman Kodak Company | Electrical connection in OLED devices |

-

2004

- 2004-12-29 US US11/025,110 patent/US7189991B2/en active Active

-

2005

- 2005-12-29 KR KR1020077017237A patent/KR101261653B1/ko not_active IP Right Cessation

- 2005-12-29 WO PCT/US2005/047519 patent/WO2006072024A2/en active Application Filing

- 2005-12-29 CN CNB200580045246XA patent/CN100505288C/zh not_active Expired - Fee Related

- 2005-12-29 TW TW094147293A patent/TWI377711B/zh not_active IP Right Cessation

- 2005-12-29 EP EP05855999A patent/EP1839336A4/en not_active Withdrawn

- 2005-12-29 JP JP2007549671A patent/JP5255279B2/ja not_active Expired - Fee Related

-

2006

- 2006-12-12 US US11/637,453 patent/US7488975B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN100505288C (zh) | 2009-06-24 |

| CN101091254A (zh) | 2007-12-19 |

| WO2006072024A3 (en) | 2007-05-18 |

| KR101261653B1 (ko) | 2013-05-06 |

| TW200633283A (en) | 2006-09-16 |

| JP2008527424A (ja) | 2008-07-24 |

| TWI377711B (en) | 2012-11-21 |

| EP1839336A2 (en) | 2007-10-03 |

| EP1839336A4 (en) | 2010-12-15 |

| KR20070093137A (ko) | 2007-09-17 |

| US20070085077A1 (en) | 2007-04-19 |

| US7189991B2 (en) | 2007-03-13 |

| US7488975B2 (en) | 2009-02-10 |

| WO2006072024A2 (en) | 2006-07-06 |

| US20060138401A1 (en) | 2006-06-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5255279B2 (ja) | 電極を基板内の他の導電性部材に接続する導電性部材を含む電子デバイス、および電子デバイスを形成するためのプロセス | |

| US7235420B2 (en) | Process for removing an organic layer during fabrication of an organic electronic device and the organic electronic device formed by the process | |

| US8604463B2 (en) | Organic light emitting diode display and method of manufacturing the same | |

| US8395160B2 (en) | Organic light emitting display apparatus and method of manufacturing the same | |

| JP2005078073A (ja) | 有機電界発光表示装置 | |

| US20050110021A1 (en) | Active matrix organic light emitting display (OLED) and method of fabrication | |

| KR20150020140A (ko) | 소수성 뱅크 | |

| CN105280835A (zh) | 有机发光装置 | |

| JP2010272447A (ja) | 有機el装置、有機el装置の製造方法、および電子機器 | |

| CN102740524A (zh) | 制造有机发光器件的方法 | |

| CN100505255C (zh) | 有机电子器件 | |

| US6822256B2 (en) | Forming organic light emitting device displays | |

| EP1647064B1 (en) | Process for removing an organic layer during fabrication of an organic electronic device | |

| WO1999053726A1 (fr) | Element organique electroluminescent et son procede de fabrication | |

| JP2006002243A (ja) | マスク、マスクの製造方法、成膜方法、電子デバイス、及び電子機器 | |

| JP2008527636A (ja) | 電子デバイスを形成するためのプロセス、およびそのようなプロセスによって形成された電子デバイス | |

| JP2009170336A (ja) | 表示装置の製造方法 | |

| KR100768715B1 (ko) | 유기 전계 발광 소자 및 그 제조방법 | |

| KR100662622B1 (ko) | 유기 전계 발광 소자 및 그 제조 방법 | |

| CN114141852B (zh) | 柔性显示面板及柔性显示装置 | |

| US20240315088A1 (en) | Display substrate and electronic apparatus | |

| US20230209937A1 (en) | Organic light emitting display device and manufacturing method thereof | |

| US20240179951A1 (en) | Display substrate and electronic apparatus | |

| JP2009230987A (ja) | Elパネル及びelパネルの製造方法 | |

| KR20070011010A (ko) | 유기 전계 발광 소자의 제조방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081222 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110603 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110905 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120608 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120910 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130322 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130419 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160426 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |