JP5230726B2 - ゲイン制御を備える画像センサ画素 - Google Patents

ゲイン制御を備える画像センサ画素 Download PDFInfo

- Publication number

- JP5230726B2 JP5230726B2 JP2010506226A JP2010506226A JP5230726B2 JP 5230726 B2 JP5230726 B2 JP 5230726B2 JP 2010506226 A JP2010506226 A JP 2010506226A JP 2010506226 A JP2010506226 A JP 2010506226A JP 5230726 B2 JP5230726 B2 JP 5230726B2

- Authority

- JP

- Japan

- Prior art keywords

- charge

- voltage conversion

- voltage

- transfer gate

- conversion region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/778—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising amplifiers shared between a plurality of pixels, i.e. at least one part of the amplifier must be on the sensor array itself

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/50—Control of the SSIS exposure

- H04N25/57—Control of the dynamic range

- H04N25/59—Control of the dynamic range by controlling the amount of charge storable in the pixel, e.g. modification of the charge conversion ratio of the floating node capacitance

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

- H04N25/771—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components comprising storage means other than floating diffusion

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Transforming Light Signals Into Electric Signals (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Facsimile Heads (AREA)

Description

105,305 行デコーダ回路

110,310 タイミング発生器

115,315 アナログ−デジタル変換器

120,320 集積画像処理

125,325 相関二重サンプリング(CDS)回路

130,308 光感受画素

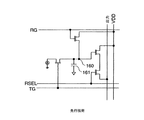

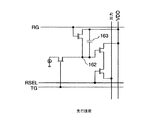

150,206 リセットトランジスタ

151 フォトダイオード

152 トランスファートランジスタ

153,207 出力トランジスタ

154,208 行選択トランジスタ

155,160,162,166 浮遊拡散ノード

161,163 キャパシタ

165 ダングリングトランジスタゲート

167,168,169 トランジスタゲート

200 画素

201,202 フォトダイオード埋め込み

203,204 トランスファーゲート

205 電荷−電圧変換ノード

209 出力信号線

210 電源電圧

211 表面ピンニング層埋め込み/ピンフォトダイオード

220,221 カラーフィルタ材質

222,223 マイクロレンズ

224 光線

230,234 光発生電荷(フォトダイオード)

231,232,233 チャネルポテンシャル

240,241 出力電圧曲線

242 高ゲイン曲線

243 点

244 曲線

400 デジタルカメラ

Claims (2)

- 画像信号を読み出す方法であって、

少なくとも2つの光感受領域を設けるステップと、

前記少なくとも2つの光感受領域の夫々に各自関連する少なくとも2つのトランスファーゲートを設けるステップと、

前記少なくとも2つのトランスファーゲートに電気的に接続されるコモン電荷−電圧変換領域を設けるステップと、

前記コモン電荷−電圧変換領域をリセットするリセットメカニズムを設けるステップと、

前記少なくとも2つの光感受領域のうち少なくとも1つの光感受領域から電荷を運んだ後、第1の時点で前記少なくとも2つのトランスファーゲートの全てを無効にするステップと、

続く第2の時点で少なくとも1つのトランスファーゲートを有効にするステップと、

前記第2の時点から前記少なくとも1つのトランスファーゲートが有効なままである間、続く第3の時点で前記少なくとも2つの光感受領域のうち少なくとも1つの他の光感受領域から電荷を運ぶステップとを含み、

前記第2の時点と前記第3の時点との間に前記コモン電荷−電圧変換領域をリセットするステップを更に含む、方法。 - 前記少なくとも2つの光感受領域に少なくとも2つの異なる光感受性を与えるステップと、

より高い光感受性を有する前記少なくとも2つの光感受領域のうち少なくとも1つの他の光感受領域から前記第3の時点に電荷を運ぶステップと

を更に含む請求項1記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/742,883 | 2007-05-01 | ||

| US11/742,883 US8159585B2 (en) | 2007-05-01 | 2007-05-01 | Image sensor pixel with gain control |

| PCT/US2008/005148 WO2008133861A1 (en) | 2007-05-01 | 2008-04-22 | Image sensor pixel with gain control |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010526479A JP2010526479A (ja) | 2010-07-29 |

| JP2010526479A5 JP2010526479A5 (ja) | 2011-06-16 |

| JP5230726B2 true JP5230726B2 (ja) | 2013-07-10 |

Family

ID=39473856

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010506226A Active JP5230726B2 (ja) | 2007-05-01 | 2008-04-22 | ゲイン制御を備える画像センサ画素 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US8159585B2 (ja) |

| EP (2) | EP2150038B1 (ja) |

| JP (1) | JP5230726B2 (ja) |

| KR (1) | KR101388276B1 (ja) |

| CN (1) | CN101675657B (ja) |

| TW (1) | TWI450579B (ja) |

| WO (1) | WO2008133861A1 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2009136285A2 (en) * | 2008-04-16 | 2009-11-12 | Quantum Semiconductor Llc | Pixel circuitry for ultra wide dynamic range |

| JP4538528B2 (ja) * | 2008-12-26 | 2010-09-08 | 廣津 和子 | 固体撮像素子 |

| US8411184B2 (en) * | 2009-12-22 | 2013-04-02 | Omnivision Technologies, Inc. | Column output circuits for image sensors |

| US9000500B2 (en) | 2009-12-30 | 2015-04-07 | Omnivision Technologies, Inc. | Image sensor with doped transfer gate |

| FR2995725A1 (fr) * | 2012-09-19 | 2014-03-21 | St Microelectronics Sa | Procede de commande d'un pixel cmos |

| CN102843524B (zh) * | 2012-09-25 | 2015-09-23 | 中国科学院上海高等研究院 | Cmos图像传感器及其工作方法 |

| CN111225161B (zh) * | 2013-03-14 | 2023-04-18 | 株式会社尼康 | 摄像元件及摄像装置 |

| US9578223B2 (en) | 2013-08-21 | 2017-02-21 | Qualcomm Incorporated | System and method for capturing images with multiple image sensing elements |

| US9160958B2 (en) | 2013-12-18 | 2015-10-13 | Omnivision Technologies, Inc. | Method of reading out an image sensor with transfer gate boost |

| JP6254048B2 (ja) * | 2014-06-05 | 2017-12-27 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| KR102591364B1 (ko) | 2015-09-23 | 2023-10-19 | 삼성디스플레이 주식회사 | 광 센서 및 이를 포함하는 표시 장치 |

| CN105681692B (zh) * | 2016-01-11 | 2018-10-30 | 珠海艾思克科技有限公司 | Cmos图像传感器及其复位噪声评估方法 |

| DE102016212784A1 (de) | 2016-07-13 | 2018-01-18 | Robert Bosch Gmbh | CMOS Pixel, Bildsensor und Kamera sowie Verfahren zum Auslesen eienes CMOS Pixels |

| JP6420450B2 (ja) * | 2017-11-29 | 2018-11-07 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US11317038B2 (en) | 2017-12-19 | 2022-04-26 | SmartSens Technology (HK) Co., Ltd. | Pixel unit with a design for half row reading, an imaging apparatus including the same, and an imaging method thereof |

| JP7299680B2 (ja) | 2018-08-23 | 2023-06-28 | キヤノン株式会社 | 撮像装置及び撮像システム |

| KR102902358B1 (ko) | 2019-11-20 | 2025-12-22 | 기가조트 테크널러지 인코포레이티드 | 스케일러블 픽셀 크기 이미지센서 |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05251480A (ja) * | 1992-03-04 | 1993-09-28 | Sony Corp | 電荷電圧変換装置 |

| JP2000152086A (ja) * | 1998-11-11 | 2000-05-30 | Canon Inc | 撮像装置および撮像システム |

| JP3592106B2 (ja) * | 1998-11-27 | 2004-11-24 | キヤノン株式会社 | 固体撮像装置およびカメラ |

| US6730897B2 (en) | 2000-12-29 | 2004-05-04 | Eastman Kodak Company | Linearity and dynamic range for complementary metal oxide semiconductor active pixel image sensors |

| US6960796B2 (en) | 2002-11-26 | 2005-11-01 | Micron Technology, Inc. | CMOS imager pixel designs with storage capacitor |

| JP2004336469A (ja) * | 2003-05-08 | 2004-11-25 | Fuji Film Microdevices Co Ltd | 固体撮像素子、撮像装置、及び画像処理方法 |

| US7075049B2 (en) * | 2003-06-11 | 2006-07-11 | Micron Technology, Inc. | Dual conversion gain imagers |

| US7026596B2 (en) * | 2003-10-30 | 2006-04-11 | Micron Technology, Inc. | High-low sensitivity pixel |

| US7091531B2 (en) * | 2004-04-07 | 2006-08-15 | Micron Technology, Inc. | High dynamic range pixel amplifier |

| JP4317115B2 (ja) * | 2004-04-12 | 2009-08-19 | 国立大学法人東北大学 | 固体撮像装置、光センサおよび固体撮像装置の動作方法 |

| JP4380439B2 (ja) * | 2004-07-16 | 2009-12-09 | ソニー株式会社 | データ処理方法およびデータ処理装置並びに物理量分布検知の半導体装置および電子機器 |

| KR100656666B1 (ko) * | 2004-09-08 | 2006-12-11 | 매그나칩 반도체 유한회사 | 이미지 센서 |

| US7193198B2 (en) | 2004-10-01 | 2007-03-20 | Omnivision Technologies, Inc. | Image sensor and pixel that has variable capacitance output or floating node |

| US20060103749A1 (en) | 2004-11-12 | 2006-05-18 | Xinping He | Image sensor and pixel that has switchable capacitance at the floating node |

| US7830437B2 (en) | 2005-05-11 | 2010-11-09 | Aptina Imaging Corp. | High fill factor multi-way shared pixel |

| US7238926B2 (en) * | 2005-06-01 | 2007-07-03 | Eastman Kodak Company | Shared amplifier pixel with matched coupling capacitances |

| KR101010489B1 (ko) | 2005-06-21 | 2011-01-21 | 미츠비시덴키 가부시키가이샤 | 프로그램 실행 시스템을 위한 프로그래밍 시스템 및검사장치용 프로그램 작성 시스템 |

| US7432540B2 (en) * | 2005-08-01 | 2008-10-07 | Micron Technology, Inc. | Dual conversion gain gate and capacitor combination |

| JP4747781B2 (ja) * | 2005-10-27 | 2011-08-17 | 船井電機株式会社 | 撮像装置 |

| JP4650249B2 (ja) * | 2005-12-13 | 2011-03-16 | 船井電機株式会社 | 撮像装置 |

| JP4747858B2 (ja) * | 2006-01-27 | 2011-08-17 | 船井電機株式会社 | 撮像装置 |

-

2007

- 2007-05-01 US US11/742,883 patent/US8159585B2/en active Active

-

2008

- 2008-04-22 CN CN200880014156.8A patent/CN101675657B/zh active Active

- 2008-04-22 EP EP09176344.1A patent/EP2150038B1/en active Active

- 2008-04-22 EP EP08743163.1A patent/EP2140676B1/en active Active

- 2008-04-22 JP JP2010506226A patent/JP5230726B2/ja active Active

- 2008-04-22 KR KR1020097022858A patent/KR101388276B1/ko active Active

- 2008-04-22 WO PCT/US2008/005148 patent/WO2008133861A1/en not_active Ceased

- 2008-04-30 TW TW097116019A patent/TWI450579B/zh active

-

2012

- 2012-03-12 US US13/418,182 patent/US8717476B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8717476B2 (en) | 2014-05-06 |

| EP2150038A2 (en) | 2010-02-03 |

| KR20100016124A (ko) | 2010-02-12 |

| EP2140676B1 (en) | 2015-08-19 |

| CN101675657B (zh) | 2014-09-10 |

| EP2140676A1 (en) | 2010-01-06 |

| US20080273104A1 (en) | 2008-11-06 |

| EP2150038A3 (en) | 2012-05-30 |

| EP2150038B1 (en) | 2013-06-12 |

| US20120168611A1 (en) | 2012-07-05 |

| US8159585B2 (en) | 2012-04-17 |

| WO2008133861A1 (en) | 2008-11-06 |

| CN101675657A (zh) | 2010-03-17 |

| TW200922284A (en) | 2009-05-16 |

| JP2010526479A (ja) | 2010-07-29 |

| KR101388276B1 (ko) | 2014-04-22 |

| TWI450579B (zh) | 2014-08-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5230726B2 (ja) | ゲイン制御を備える画像センサ画素 | |

| US12495628B2 (en) | Imaging device including photoelectric converters and capacitor | |

| CN102098456B (zh) | 可扩大动态范围的固体摄像装置 | |

| KR101398767B1 (ko) | 축소된 픽셀 영역 이미지 센서 | |

| US7468501B2 (en) | Linear dynamic range enhancement in a CMOS imager | |

| US7427790B2 (en) | Image sensor with gain control | |

| US20060266922A1 (en) | Pinned-photodiode pixel with global shutter | |

| US6882022B2 (en) | Dual gate BCMD pixel suitable for high performance CMOS image sensor arrays | |

| CN210168124U (zh) | 图像传感器 | |

| KR100801758B1 (ko) | 이미지 센서 및 그 제어 방법 | |

| KR100962470B1 (ko) | 고체 촬상 소자의 픽셀 회로 | |

| JP4320693B2 (ja) | 固体撮像装置 | |

| US20200059612A1 (en) | Pixel apparatus and cmos image sensor using the same | |

| JP2011199050A (ja) | 固体撮像デバイスおよび電子機器 | |

| JP4718169B2 (ja) | Cmos撮像デバイス回路 | |

| JP2008053333A (ja) | 固体撮像デバイス | |

| JP4345145B2 (ja) | 固体撮像装置 | |

| JP5868451B2 (ja) | 光電変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110419 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110419 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20110530 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120724 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121030 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130305 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130319 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160329 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5230726 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |