JP5207896B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP5207896B2 JP5207896B2 JP2008239751A JP2008239751A JP5207896B2 JP 5207896 B2 JP5207896 B2 JP 5207896B2 JP 2008239751 A JP2008239751 A JP 2008239751A JP 2008239751 A JP2008239751 A JP 2008239751A JP 5207896 B2 JP5207896 B2 JP 5207896B2

- Authority

- JP

- Japan

- Prior art keywords

- lead frame

- semiconductor element

- lead

- opening

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 162

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 48

- 238000007789 sealing Methods 0.000 claims abstract description 38

- 239000011347 resin Substances 0.000 claims abstract description 35

- 229920005989 resin Polymers 0.000 claims abstract description 35

- 238000000034 method Methods 0.000 claims description 66

- 239000000463 material Substances 0.000 claims description 17

- 230000002093 peripheral effect Effects 0.000 claims description 11

- 239000000758 substrate Substances 0.000 claims description 8

- 238000010030 laminating Methods 0.000 claims description 4

- 238000003475 lamination Methods 0.000 claims description 2

- 239000002313 adhesive film Substances 0.000 claims 1

- 238000004806 packaging method and process Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 127

- 239000010949 copper Substances 0.000 description 37

- 238000000465 moulding Methods 0.000 description 21

- 238000012986 modification Methods 0.000 description 18

- 230000004048 modification Effects 0.000 description 18

- 239000010408 film Substances 0.000 description 15

- 229910000679 solder Inorganic materials 0.000 description 11

- 238000012545 processing Methods 0.000 description 10

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 9

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 9

- 229910052802 copper Inorganic materials 0.000 description 9

- 239000000853 adhesive Substances 0.000 description 8

- 230000001070 adhesive effect Effects 0.000 description 8

- 239000011651 chromium Substances 0.000 description 8

- 239000010936 titanium Substances 0.000 description 8

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 7

- 229920001721 polyimide Polymers 0.000 description 7

- 239000009719 polyimide resin Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- HEMHJVSKTPXQMS-UHFFFAOYSA-M Sodium hydroxide Chemical compound [OH-].[Na+] HEMHJVSKTPXQMS-UHFFFAOYSA-M 0.000 description 6

- 239000010931 gold Substances 0.000 description 6

- 229910052751 metal Inorganic materials 0.000 description 6

- 239000002184 metal Substances 0.000 description 6

- 229920002120 photoresistant polymer Polymers 0.000 description 6

- 238000007747 plating Methods 0.000 description 6

- 238000004544 sputter deposition Methods 0.000 description 5

- 238000000059 patterning Methods 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 229910052804 chromium Inorganic materials 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000011161 development Methods 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 230000000694 effects Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 239000003822 epoxy resin Substances 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 239000007788 liquid Substances 0.000 description 3

- 229920000647 polyepoxide Polymers 0.000 description 3

- 229920001187 thermosetting polymer Polymers 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- CURLTUGMZLYLDI-UHFFFAOYSA-N Carbon dioxide Chemical compound O=C=O CURLTUGMZLYLDI-UHFFFAOYSA-N 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- 244000126211 Hericium coralloides Species 0.000 description 2

- 239000004820 Pressure-sensitive adhesive Substances 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 238000004380 ashing Methods 0.000 description 2

- 238000007772 electroless plating Methods 0.000 description 2

- 230000004907 flux Effects 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 238000000206 photolithography Methods 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000012779 reinforcing material Substances 0.000 description 2

- HZAXFHJVJLSVMW-UHFFFAOYSA-N 2-Aminoethan-1-ol Chemical compound NCCO HZAXFHJVJLSVMW-UHFFFAOYSA-N 0.000 description 1

- 229910000640 Fe alloy Inorganic materials 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910052581 Si3N4 Inorganic materials 0.000 description 1

- 239000000654 additive Substances 0.000 description 1

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 1

- 239000001569 carbon dioxide Substances 0.000 description 1

- 229910002092 carbon dioxide Inorganic materials 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000011521 glass Substances 0.000 description 1

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000001746 injection moulding Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 239000004850 liquid epoxy resins (LERs) Substances 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 239000001301 oxygen Substances 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 229920001225 polyester resin Polymers 0.000 description 1

- 239000004645 polyester resin Substances 0.000 description 1

- 238000003825 pressing Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000002344 surface layer Substances 0.000 description 1

- 239000012756 surface treatment agent Substances 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 238000001721 transfer moulding Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L24/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the groups H01L21/18 - H01L21/326 or H10D48/04 - H10D48/07 e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/568—Temporary substrate used as encapsulation process aid

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/12105—Bump connectors formed on an encapsulation of the semiconductor or solid-state body, e.g. bumps on chip-scale packages

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/18—High density interconnect [HDI] connectors; Manufacturing methods related thereto

- H01L2224/19—Manufacturing methods of high density interconnect preforms

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32135—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/32145—Disposition the layer connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/4805—Shape

- H01L2224/4809—Loop shape

- H01L2224/48091—Arched

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48225—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/48227—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/42—Wire connectors; Manufacturing methods related thereto

- H01L2224/47—Structure, shape, material or disposition of the wire connectors after the connecting process

- H01L2224/48—Structure, shape, material or disposition of the wire connectors after the connecting process of an individual wire connector

- H01L2224/481—Disposition

- H01L2224/48151—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/48221—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/48245—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic

- H01L2224/48247—Connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being metallic connecting the wire to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73265—Layer and wire connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73251—Location after the connecting process on different surfaces

- H01L2224/73267—Layer and HDI connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/97—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips the devices being connected to a common substrate, e.g. interposer, said common substrate being separable into individual assemblies after connecting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01024—Chromium [Cr]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01079—Gold [Au]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/102—Material of the semiconductor or solid state bodies

- H01L2924/1025—Semiconducting materials

- H01L2924/10251—Elemental semiconductors, i.e. Group IV

- H01L2924/10253—Silicon [Si]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/153—Connection portion

- H01L2924/1531—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface

- H01L2924/15311—Connection portion the connection portion being formed only on the surface of the substrate opposite to the die mounting surface being a ball array, e.g. BGA

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Lead Frames For Integrated Circuits (AREA)

Description

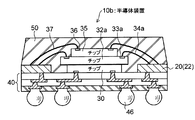

図1は本発明の第1の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

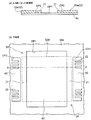

図7は本発明の第2の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

図13は本発明の第3の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

図19は本発明の第4の実施形態に係る半導体装置の構成を断面図の形態で示したものである。

20,20a,20b…リードフレーム、

21…支持部、

22…リード部、

30(a,b),32(a,b),35…シリコンチップ(半導体素子)、

31(a,b),33(a,b),36…電極パッド(端子)、

32L,32M,32N…上側チップの外形(実装エリア)、

34(a,b),37…ボンディングワイヤ、

40,40a…積層配線層(パッケージ)、

41,43…絶縁層、

42,44…配線層(再配線層)、

44P…(外部接続端子接合用の)パッド部、

45…ソルダレジスト層(保護膜)、

46…外部接続端子、

50,50a…封止樹脂(層)、

60…テープ(片面に粘着剤が塗布されたフィルム状の基材)、

OP,OP1,OP2,OP3…リードフレームの開口部。

Claims (10)

- 開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームと、

前記リードフレームの開口部に、フェイスダウンの態様で配置された第1の半導体素子と、

前記第1の半導体素子上にフェイスアップの態様で搭載され、その電極パッドがワイヤを介して前記リードフレームのリード部に接続された第2の半導体素子と、

前記第1の半導体素子及び前記リードフレームをその一面側に搭載する態様で設けられた積層配線層と、

前記積層配線層上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように形成された封止樹脂層とを備え、

前記積層配線層は、前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれひき出された配線パターンが、前記積層配線層の他面側に設けられるパッド部と電気的に繋がるようにそれぞれパターン形成された複数の配線層を含み、

前記第1の半導体素子及び前記リードフレームは、前記積層配線層の一面側において同一平面上に搭載されており、かつ、前記第1の半導体素子は、前記積層配線層の配線層と直接接続されていることを特徴とする半導体装置。 - 前記リードフレームの開口部は、前記第1の半導体素子が配置される第1の開口部と、その周囲にリード部が櫛歯状に延在するように成形された第2の開口部とを有し、

前記第2の半導体素子は、前記第1の半導体素子より大きいサイズを有し、その周辺部分が前記第1、第2の開口部間のリードフレーム部分で支持された構造を有することを特徴とする請求項1に記載の半導体装置。 - 前記第2の半導体素子は、前記第1の半導体素子より大きいサイズを有し、その周辺部分が前記リードフレームの各リード部で支持された構造を有することを特徴とする請求項1に記載の半導体装置。

- 前記第1の半導体素子として複数個の半導体素子が、前記リードフレームの開口部に並設されていることを特徴とする請求項1に記載の半導体装置。

- 前記第1の半導体素子の厚さは、前記リードフレームのリード部の厚さと同じであることを特徴とする請求項1に記載の半導体装置。

- 開口部を有し、該開口部の周囲にリード部が櫛歯状に延在するように成形されたリードフレームを、フィルム状の基材に貼り付けたものを用意する工程と、

前記基材上の、前記リードフレームの開口部に対応する部分に、第1の半導体素子をフェイスダウンの態様で搭載する工程と、

前記第1の半導体素子上に第2の半導体素子をフェイスアップの態様で搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程と、

前記基材上の前記リードフレームと前記第1、第2の半導体素子及び前記ワイヤを埋め込むように封止樹脂で封止する工程と、

前記基材を除去する工程と、

前記第1の半導体素子の電極パッド及び前記リードフレームのリード部からそれぞれ配線パターンをひき出し、以降、所要の数の配線層を積層する工程であって、前記配線パターンが、積層後の配線層の露出する面側に設けられるパッド部と電気的に繋がるように各配線層を積層する工程とを含むことを特徴とする半導体装置の製造方法。 - 前記リードフレームを前記基材に貼り付けたものを用意する工程において、前記リードフレームを、第1の半導体素子が配置される第1の開口部と、その周囲に前記リード部が櫛歯状に延在するように成形された第2の開口部とを有するように成形し、

前記第1の半導体素子上に前記第2の半導体素子を搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程において、前記第1の半導体素子より大きいサイズを有した第2の半導体素子を、その周辺部分を前記第1、第2の開口部間のリードフレーム部分上に位置合わせして搭載することを特徴とする請求項6に記載の半導体装置の製造方法。 - 前記第1の半導体素子上に前記第2の半導体素子を搭載し、さらに該第2の半導体素子の電極パッドと前記リードフレームのリード部とをワイヤにより接続する工程において、前記第1の半導体素子より大きいサイズを有した第2の半導体素子を、その周辺部分を前記リードフレームの各リード部上に位置合わせして搭載することを特徴とする請求項6に記載の半導体装置の製造方法。

- 前記第1の半導体素子を搭載する工程において、前記基材上の、前記リードフレームの開口部に対応する部分に、該第1の半導体素子として複数個の半導体素子を並設することを特徴とする請求項6に記載の半導体装置の製造方法。

- 前記第1の半導体素子の厚さは、前記リードフレームのリード部の厚さと同じであることを特徴とする請求項6に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008239751A JP5207896B2 (ja) | 2008-09-18 | 2008-09-18 | 半導体装置及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008239751A JP5207896B2 (ja) | 2008-09-18 | 2008-09-18 | 半導体装置及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010073893A JP2010073893A (ja) | 2010-04-02 |

| JP2010073893A5 JP2010073893A5 (ja) | 2011-08-18 |

| JP5207896B2 true JP5207896B2 (ja) | 2013-06-12 |

Family

ID=42205410

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008239751A Active JP5207896B2 (ja) | 2008-09-18 | 2008-09-18 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5207896B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5100715B2 (ja) * | 2009-07-13 | 2012-12-19 | 株式会社東芝 | 半導体装置及び半導体装置の製造方法 |

| KR101131447B1 (ko) * | 2010-10-05 | 2012-03-29 | 앰코 테크놀로지 코리아 주식회사 | 반도체 패키지 제조 방법 |

| KR101297015B1 (ko) | 2011-11-03 | 2013-08-14 | 주식회사 네패스 | 리드프레임을 이용한 팬-아웃 반도체 패키지 제조방법, 이에 의한 반도체 패키지 및 패키지 온 패키지 |

| JP5924110B2 (ja) * | 2012-05-11 | 2016-05-25 | 株式会社ソシオネクスト | 半導体装置、半導体装置モジュールおよび半導体装置の製造方法 |

| KR101999114B1 (ko) * | 2013-06-03 | 2019-07-11 | 에스케이하이닉스 주식회사 | 반도체 패키지 |

| US10074628B2 (en) | 2013-10-04 | 2018-09-11 | Mediatek Inc. | System-in-package and fabrication method thereof |

| US10103128B2 (en) | 2013-10-04 | 2018-10-16 | Mediatek Inc. | Semiconductor package incorporating redistribution layer interposer |

| KR101809521B1 (ko) * | 2015-09-04 | 2017-12-18 | 주식회사 네패스 | 반도체 패키지 및 그 제조방법 |

| KR101819558B1 (ko) * | 2015-09-04 | 2018-01-18 | 주식회사 네패스 | 반도체 패키지 및 그 제조방법 |

| EP3151275A3 (en) * | 2015-09-11 | 2017-04-19 | MediaTek Inc. | System-in-package and fabrication method thereof |

| KR101944007B1 (ko) * | 2015-12-16 | 2019-01-31 | 주식회사 네패스 | 반도체 패키지 및 그 제조방법 |

| JP7096741B2 (ja) | 2018-09-11 | 2022-07-06 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2023082375A (ja) * | 2021-12-02 | 2023-06-14 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及び電子機器 |

| CN119008564A (zh) * | 2024-09-04 | 2024-11-22 | 甬矽半导体(宁波)有限公司 | 扇出型封装结构和扇出型封装结构的制备方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000294722A (ja) * | 1999-04-01 | 2000-10-20 | Nec Corp | 積層化チップ半導体装置 |

| JP3649064B2 (ja) * | 1999-11-10 | 2005-05-18 | 松下電器産業株式会社 | 半導体装置の製造方法 |

| JP4321758B2 (ja) * | 2003-11-26 | 2009-08-26 | カシオ計算機株式会社 | 半導体装置 |

| JP5378643B2 (ja) * | 2006-09-29 | 2013-12-25 | ピーエスフォー ルクスコ エスエイアールエル | 半導体装置及びその製造方法 |

| JP2008187203A (ja) * | 2008-04-25 | 2008-08-14 | Sanyo Electric Co Ltd | 半導体装置の製造方法 |

-

2008

- 2008-09-18 JP JP2008239751A patent/JP5207896B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2010073893A (ja) | 2010-04-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5207896B2 (ja) | 半導体装置及びその製造方法 | |

| JP5005603B2 (ja) | 半導体装置及びその製造方法 | |

| JP5249173B2 (ja) | 半導体素子実装配線基板及びその製造方法 | |

| JP5460388B2 (ja) | 半導体装置及びその製造方法 | |

| JP3925809B2 (ja) | 半導体装置およびその製造方法 | |

| JP6125332B2 (ja) | 半導体装置 | |

| JP4379102B2 (ja) | 半導体装置の製造方法 | |

| TWI801417B (zh) | 半導體元件用基板及其製造方法、半導體裝置及其製造方法 | |

| JP2010199148A (ja) | 半導体センサデバイス及びその製造方法、パッケージ及びその製造方法、モジュール及びその製造方法、並びに電子機器 | |

| JP5406572B2 (ja) | 電子部品内蔵配線基板及びその製造方法 | |

| WO2003098687A1 (fr) | Dispositif a semiconducteur et procede de fabrication | |

| KR20060101385A (ko) | 반도체 장치 및 그 제조 방법 | |

| US20070054439A1 (en) | Multi-chip stack structure | |

| US20190088506A1 (en) | Semiconductor package and method of manufacturing the same | |

| JP2010161222A (ja) | 半導体パッケージの製造方法、半導体パッケージ及び半導体チップ | |

| CN111199924A (zh) | 半导体封装结构及其制作方法 | |

| JP4577316B2 (ja) | 半導体装置の製造方法 | |

| JP4337858B2 (ja) | 半導体装置 | |

| CN113725096B (zh) | 半导体封装方法及半导体封装结构 | |

| JP4321758B2 (ja) | 半導体装置 | |

| CN101740410B (zh) | 芯片封装结构的制程 | |

| JP2004158747A (ja) | 半導体装置の製造方法 | |

| JP4439339B2 (ja) | 半導体装置およびその製造方法 | |

| JP2007049183A (ja) | 半導体装置 | |

| TWI474413B (zh) | 晶片封裝結構的製程 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110630 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110630 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120201 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120522 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120710 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130219 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160301 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5207896 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |