JP5167478B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP5167478B2 JP5167478B2 JP2006044370A JP2006044370A JP5167478B2 JP 5167478 B2 JP5167478 B2 JP 5167478B2 JP 2006044370 A JP2006044370 A JP 2006044370A JP 2006044370 A JP2006044370 A JP 2006044370A JP 5167478 B2 JP5167478 B2 JP 5167478B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor region

- type

- region

- semiconductor

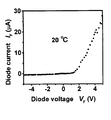

- diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Landscapes

- Bipolar Transistors (AREA)

Description

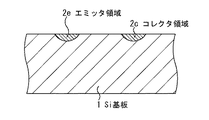

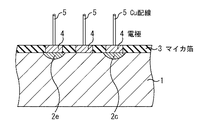

2e:エミッタ領域

2c:コレクタ領域

3:マイカ箔

4:電極

5:Cu配線

Claims (7)

- p型の第1の半導体領域と、

前記第1の半導体領域と隣接し、ダングリングボンドを電子の供給源とするn型の第2の半導体領域と、

を有し、

前記第1の半導体領域及び前記第2の半導体領域はシリコン又は炭化珪素からなることを特徴とする半導体装置。 - 前記第1の半導体領域は、シリコン又は炭化珪素にp型の不純物を導入して構成されていることを特徴とする請求項1に記載の半導体装置。

- 前記第2の半導体領域との間で前記第1の半導体領域を挟み込むn型の第3の半導体領域を有し、前記第3の半導体領域はシリコン又は炭化珪素からなることを特徴とする請求項1又は2に記載の半導体装置。

- 前記第2の半導体領域は、p型のシリコン又は炭化珪素への希ガス元素イオンの打ち込みにより形成されていることを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

- p型の第1の半導体領域内にダングリングボンドを発生させて、前記ダングリングボンドを電子の供給源とするn型の第2の半導体領域を形成する工程を有し、

前記第1の半導体領域及び前記第2の半導体領域はシリコン又は炭化珪素からなることを特徴とする半導体装置の製造方法。 - 前記第2の半導体領域の形成と並行して、前記第2の半導体領域との間で前記第1の半導体領域を挟み込むn型の第3の半導体領域を形成し、前記第3の半導体領域はシリコン又は炭化珪素からなることを特徴とする請求項5に記載の半導体装置の製造方法。

- 前記ダングリングボンドを発生させる際に、前記第1の半導体領域に対して希ガス元素イオンを打ち込むことを特徴とする請求項5又は6に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006044370A JP5167478B2 (ja) | 2005-02-22 | 2006-02-21 | 半導体装置及びその製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005046087 | 2005-02-22 | ||

| JP2005046087 | 2005-02-22 | ||

| JP2006044370A JP5167478B2 (ja) | 2005-02-22 | 2006-02-21 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006270074A JP2006270074A (ja) | 2006-10-05 |

| JP5167478B2 true JP5167478B2 (ja) | 2013-03-21 |

Family

ID=37205632

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006044370A Active JP5167478B2 (ja) | 2005-02-22 | 2006-02-21 | 半導体装置及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5167478B2 (ja) |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02217397A (ja) * | 1989-02-15 | 1990-08-30 | Kobe Steel Ltd | n型半導体ダイヤモンド薄膜の気相合成法 |

| JPH09129902A (ja) * | 1995-11-01 | 1997-05-16 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JPH09320972A (ja) * | 1996-05-28 | 1997-12-12 | Kobe Steel Ltd | 半導体基板に対する不純物導入方法、及び半導体装置の製造方法 |

-

2006

- 2006-02-21 JP JP2006044370A patent/JP5167478B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006270074A (ja) | 2006-10-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Graul et al. | High-performance transistors with arsenic-implanted polysil emitters | |

| JPH0845869A (ja) | 特に集積化された電子装置における電荷キャリアの寿命の局所化される短縮のための処理、および電荷キャリアの寿命の局所化される短縮を伴う集積化された電子装置 | |

| JP3727827B2 (ja) | 半導体装置 | |

| WO2021075330A1 (ja) | 半導体装置および半導体装置の製造方法 | |

| Tang et al. | An implanted-emitter 4H-SiC bipolar transistor with high current gain | |

| US5756387A (en) | Method for forming zener diode with high time stability and low noise | |

| JPS6112388B2 (ja) | ||

| CN108155225A (zh) | 恒流器件及其制造方法 | |

| TWI474481B (zh) | 高增益常數β雙極性接面電晶體及其製造方法 | |

| CN101536177B (zh) | 适于形成半导体结型二极管器件的半导体晶片及其形成方法 | |

| US6770912B2 (en) | Semiconductor device and method for producing the same | |

| JP5167478B2 (ja) | 半導体装置及びその製造方法 | |

| CN107534059B (zh) | 半导体装置和半导体装置的制造方法 | |

| JP2009004763A (ja) | 半導体装置 | |

| JP2022124784A (ja) | 半導体装置およびその製造方法 | |

| CN110164814B (zh) | Soi衬底及其制备方法 | |

| JP2008535214A (ja) | ダイオード構造 | |

| JP4857590B2 (ja) | 半導体素子 | |

| CN114051653A (zh) | 半导体装置和半导体装置的制造方法 | |

| EP0109888A2 (en) | Subsurface Zener diode | |

| CN114695513B (zh) | 半导体装置及其制造方法 | |

| JP2817247B2 (ja) | 半導体装置 | |

| JP2841419B2 (ja) | 多結晶ダイオードおよびその製造方法 | |

| JPH0233976A (ja) | ツェナーダイオード | |

| JP7415913B2 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080709 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120327 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120522 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120731 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120924 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20121127 |