JP5122959B2 - Oledデバイスのための電流駆動型配置の提供 - Google Patents

Oledデバイスのための電流駆動型配置の提供 Download PDFInfo

- Publication number

- JP5122959B2 JP5122959B2 JP2007532424A JP2007532424A JP5122959B2 JP 5122959 B2 JP5122959 B2 JP 5122959B2 JP 2007532424 A JP2007532424 A JP 2007532424A JP 2007532424 A JP2007532424 A JP 2007532424A JP 5122959 B2 JP5122959 B2 JP 5122959B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- channel region

- current

- semiconductor layer

- pixel

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims description 103

- 239000000758 substrate Substances 0.000 claims description 35

- 238000000034 method Methods 0.000 claims description 25

- 238000000137 annealing Methods 0.000 claims description 18

- 230000004044 response Effects 0.000 claims description 12

- 238000004519 manufacturing process Methods 0.000 claims description 8

- 229920001621 AMOLED Polymers 0.000 claims description 6

- 230000008569 process Effects 0.000 claims description 6

- 238000006243 chemical reaction Methods 0.000 description 171

- 239000004020 conductor Substances 0.000 description 53

- 239000003990 capacitor Substances 0.000 description 44

- 238000003860 storage Methods 0.000 description 32

- 239000011159 matrix material Substances 0.000 description 26

- 238000005401 electroluminescence Methods 0.000 description 23

- 230000006870 function Effects 0.000 description 11

- 238000010586 diagram Methods 0.000 description 9

- 235000013405 beer Nutrition 0.000 description 7

- 239000000463 material Substances 0.000 description 7

- 229910052710 silicon Inorganic materials 0.000 description 7

- 239000010703 silicon Substances 0.000 description 7

- 239000010409 thin film Substances 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 230000008859 change Effects 0.000 description 4

- 238000005530 etching Methods 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 238000000206 photolithography Methods 0.000 description 4

- 230000000704 physical effect Effects 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 3

- 230000005525 hole transport Effects 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 238000005224 laser annealing Methods 0.000 description 3

- 230000003071 parasitic effect Effects 0.000 description 3

- 238000000059 patterning Methods 0.000 description 3

- 230000035945 sensitivity Effects 0.000 description 3

- 238000004904 shortening Methods 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 239000003086 colorant Substances 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 238000002425 crystallisation Methods 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 239000010408 film Substances 0.000 description 2

- 239000011521 glass Substances 0.000 description 2

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 239000011368 organic material Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 235000012239 silicon dioxide Nutrition 0.000 description 2

- 239000000377 silicon dioxide Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910000838 Al alloy Inorganic materials 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000003989 dielectric material Substances 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 238000007641 inkjet printing Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 230000007774 longterm Effects 0.000 description 1

- SJCKRGFTWFGHGZ-UHFFFAOYSA-N magnesium silver Chemical compound [Mg].[Ag] SJCKRGFTWFGHGZ-UHFFFAOYSA-N 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 239000004033 plastic Substances 0.000 description 1

- 239000002861 polymer material Substances 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000006798 recombination Effects 0.000 description 1

- 238000005215 recombination Methods 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- 150000003384 small molecules Chemical class 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 239000012780 transparent material Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

- G09G3/3233—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element

- G09G3/3241—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix with pixel circuitry controlling the current through the light-emitting element the current through the light-emitting element being set using a data current provided by the data driver, e.g. by using a two-transistor current mirror

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1296—Multistep manufacturing methods adapted to increase the uniformity of device parameters

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/30—Organic light-emitting transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/0271—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping

- G09G2320/0276—Adjustment of the gradation levels within the range of the gradation scale, e.g. by redistribution or clipping for the purpose of adaptation to the characteristics of a display device, i.e. gamma correction

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/302—Details of OLEDs of OLED structures

- H10K2102/3023—Direction of light emission

- H10K2102/3026—Top emission

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K71/00—Manufacture or treatment specially adapted for the organic devices covered by this subclass

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Theoretical Computer Science (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Manufacturing & Machinery (AREA)

- Geometry (AREA)

- Optics & Photonics (AREA)

- Electroluminescent Light Sources (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Devices For Indicating Variable Information By Combining Individual Elements (AREA)

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含む方法によって達成される。

ISD = (1/2)×μ×(W/L)×Cゲート×(VGS - VTH)2 (式1)

ただし、

ISDは、ソース端子とドレイン端子の間を流れる電流であり;

μは、キャリア(電子または正孔)の移動度であり;

Wは、チャネル幅であり;

Lは、チャネル長であり;

Cゲートは、チャネル領域の上方にあるゲートの単位面積当たりの容量であり;

VGSは、ゲート端子とソース端子の電圧差であり;

VTHは、トランジスタの閾値電圧である。

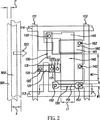

111 データ線

112 電力線

113 第1の走査線

114 第2の走査線

120 選択用トランジスタ

121 半導体領域

122 ビア

123 ビア

125 導電体ブリッジ

125a 導電体ブリッジ

130 スイッチング用トランジスタ

131 半導体領域

131a 半導体領域

132 ビア

133 ビア

140 変換用トランジスタ

140a 第1の変換用トランジスタ

140b 第2の変換用トランジスタ

141b 半導体領域

142 ビア

142a ビア

142b ビア

143a ビア

143b ビア

145 ゲート導電体

150 駆動用トランジスタ

150a 第1の駆動用トランジスタ

150b 第2の駆動用トランジスタ

151 半導体領域

151a 半導体領域

151b 半導体領域

152 ビア

152a ビア

152b ビア

153 ビア

153a ビア

153b ビア

160 記憶用キャパシタ

161 半導体領域

162 ビア

170 電流源

200 基板

212 第1の誘電体層

213 第2の誘電体層

214 第3の誘電体層

230 有機発光ダイオード

240 有機EL媒体

241 正孔注入層

242 正孔輸送層

243 発光層

245 電子輸送層

250 第2の電極

260 第1の電極

270 光

501 レーザー・パルス

502 レーザー・パルス

510 レーザーの走査方向

Claims (3)

- 電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタと上記第2のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含み、

上記第1のトランジスタのチャネル領域が形成される半導体層と上記第2のトランジスタのチャネル領域が形成される半導体層とが同一の工程で形成され、

上記第1のトランジスタのゲートと上記第2のトランジスタのゲートを電気的に接続し、データ線から供給される電流を上記第1のトランジスタに通過させ、該電流が上記第2のトランジスタに再現されるように電流ミラー回路を構成し、かつ

上記第1のトランジスタのチャネル領域と上記第2のトランジスタのチャネル領域との大きさが異なるが、上記第1及び第2のトランジスタのチャネル領域の長さ又は幅が同一であり、その同一の長さ又は幅が上記レーザー・パルスと直角になるように配置し、上記レーザ・パルスがほぼ同時に両方のチャネル領域に到達し、ほぼ同時に両方のチャネル領域のアニーリングを終了させるようにすることを特徴とする方法。 - 電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流としてのデータ信号を受け取って対応する画素から出る光の明るさを調節するため、上記半導体層の中に形成されたチャネル領域と、上記導電層の中に形成されたゲートとを備える第1のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第2のトランジスタと第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含み、

上記第1のトランジスタのチャネル領域が形成される半導体層と上記第2のトランジスタのチャネル領域が形成される半導体層とが同一の工程で形成され、

上記第1のトランジスタのゲートを、上記第2、3のトランジスタのゲートに接続し、データ線から供給される電流を上記第1のトランジスタに通過させ、該電流に対して所定の比の電流が上記第2、3のトランジスタに再現されるように電流ミラー回路を構成し、かつ

上記第1のトランジスタのチャネル領域の大きさは、上記第2、3のトランジスタのチャネル領域の大きさと異なるが、上記第1、第2及び第3のトランジスタのチャネル領域の長さ又は幅が同一であり、その同一の長さ又は幅が上記レーザー・パルスと直角になるように配置し、上記レーザ・パルスがほぼ同時にすべてのチャネル領域に到達し、ほぼ同時にすべてのチャネル領域のアニーリングを終了させるようにすることを特徴とする方法。 - 電流型アクティブ・マトリックスOLEDデバイスの製造方法であって、

a)基板の上方に半導体層を設け;

b)その基板の上方に導電層を設け;

c)上記半導体層と上記導電層の間に絶縁層を設け;

d)各画素を発光させるため、上記半導体層または上記導電層の上方に有機発光ダイオードを設け;

e)第1の電流データとしての信号を受け取って対応する画素から出る光の明るさを調節するため、半導体層の中に形成されたチャネル領域と、導電層の中に形成されたゲートとをそれぞれが備える第1のトランジスタと第2のトランジスタを画素ごとに形成し;

f)上記第1の電流に応答して上記有機発光ダイオードの中を流れる電流を調節するため、上記導電層の中に形成されたゲートと、上記半導体層の中に形成されたチャネル領域とを備える第3のトランジスタを画素ごとに形成し;

g)上記第1のトランジスタ、上記第2のトランジスタ、上記第3のトランジスタを形成する前、または形成した後に、供給源から供給されて1個以上のレーザー・パルスを発生させるパルス式レーザーを用いた照射により、上記半導体層のうちで、その第1のトランジスタのチャネル領域の一部に関係する領域と、その第2のトランジスタのチャネル領域の一部に関係する領域と、その第3のトランジスタのチャネル領域の一部に関係する領域をアニーリングする操作を含み、

上記第1のトランジスタのチャネル領域が形成される半導体層と上記第2のトランジスタのチャネル領域が形成される半導体層とが同一の工程で形成され、

上記第1、2のトランジスタのゲートを、上記第3のトランジスタのゲートに接続し、データ線から供給される電流を上記第1、2のトランジスタに通過させ、該電流に対して所定の比の電流が上記第3のトランジスタに再現されるように電流ミラー回路を構成し、かつ

上記第1、2のトランジスタのチャネル領域の大きさは、上記第3のトランジスタのチャネル領域の大きさと異なるが、上記第1、第2及び第3のトランジスタのチャネル領域の長さ又は幅が同一であり、その同一の長さ又は幅が上記レーザー・パルスと直角になるように配置し、上記レーザ・パルスがほぼ同時にすべてのチャネル領域に到達し、ほぼ同時にすべてのチャネル領域のアニーリングを終了させるようにすることを特徴とする方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/945,484 US7105855B2 (en) | 2004-09-20 | 2004-09-20 | Providing driving current arrangement for OLED device |

| US10/945,484 | 2004-09-20 | ||

| PCT/US2005/032745 WO2006033919A2 (en) | 2004-09-20 | 2005-09-13 | Providing driving current arrangement for oled device |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012188568A Division JP5449488B2 (ja) | 2004-09-20 | 2012-08-29 | Oledデバイスのための電流駆動型配置の提供 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008513960A JP2008513960A (ja) | 2008-05-01 |

| JP2008513960A5 JP2008513960A5 (ja) | 2008-10-23 |

| JP5122959B2 true JP5122959B2 (ja) | 2013-01-16 |

Family

ID=35840633

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007532424A Active JP5122959B2 (ja) | 2004-09-20 | 2005-09-13 | Oledデバイスのための電流駆動型配置の提供 |

| JP2012188568A Active JP5449488B2 (ja) | 2004-09-20 | 2012-08-29 | Oledデバイスのための電流駆動型配置の提供 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012188568A Active JP5449488B2 (ja) | 2004-09-20 | 2012-08-29 | Oledデバイスのための電流駆動型配置の提供 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7105855B2 (ja) |

| JP (2) | JP5122959B2 (ja) |

| KR (3) | KR101210484B1 (ja) |

| WO (1) | WO2006033919A2 (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW513593B (en) * | 2001-10-03 | 2002-12-11 | Chunghwa Picture Tubes Ltd | Liquid display device |

| CA2443206A1 (en) | 2003-09-23 | 2005-03-23 | Ignis Innovation Inc. | Amoled display backplanes - pixel driver circuits, array architecture, and external compensation |

| KR20060091157A (ko) * | 2005-02-14 | 2006-08-18 | 매그나칩 반도체 유한회사 | 전원라인의 전압 감소를 방지할 수 있는 이미지센서 및 이미지센서의 전원라인 배치 방법 |

| US7652291B2 (en) * | 2005-05-28 | 2010-01-26 | Samsung Mobile Display Co., Ltd. | Flat panel display |

| KR20070037848A (ko) * | 2005-10-04 | 2007-04-09 | 삼성전자주식회사 | 유기 발광 표시 장치 |

| US7700471B2 (en) * | 2005-12-13 | 2010-04-20 | Versatilis | Methods of making semiconductor-based electronic devices on a wire and articles that can be made thereby |

| US7638416B2 (en) * | 2005-12-13 | 2009-12-29 | Versatilis Llc | Methods of making semiconductor-based electronic devices on a wire and articles that can be made using such devices |

| US8654045B2 (en) * | 2006-07-31 | 2014-02-18 | Sony Corporation | Display and method for manufacturing display |

| US7911459B2 (en) * | 2007-03-28 | 2011-03-22 | Himax Technologies Limited | Pixel circuit |

| JP2008298970A (ja) * | 2007-05-30 | 2008-12-11 | Canon Inc | 有機el画素回路及びその駆動方法 |

| KR20100087077A (ko) * | 2007-10-31 | 2010-08-03 | 스미또모 가가꾸 가부시키가이샤 | 박막 능동 소자군, 박막 능동 소자 어레이, 유기 발광 장치, 표시 장치 및 박막 능동 소자군의 제조 방법 |

| JP2009224595A (ja) | 2008-03-17 | 2009-10-01 | Fujifilm Corp | 有機電界発光表示装置及びその製造方法 |

| KR101099167B1 (ko) * | 2008-07-02 | 2011-12-27 | 후지 덴키 가부시키가이샤 | 면발광 표시장치 |

| JP2010049041A (ja) * | 2008-08-22 | 2010-03-04 | Sony Corp | 画像表示装置及び画像表示装置の駆動方法 |

| JP5287262B2 (ja) * | 2009-01-07 | 2013-09-11 | セイコーエプソン株式会社 | アクティブマトリクス基板、電気泳動表示装置及び電子機器 |

| US8692742B2 (en) * | 2009-09-01 | 2014-04-08 | Au Optronics Corporation | Pixel driving circuit with multiple current paths in a light emitting display panel |

| US8642363B2 (en) * | 2009-12-09 | 2014-02-04 | Nano And Advanced Materials Institute Limited | Monolithic full-color LED micro-display on an active matrix panel manufactured using flip-chip technology |

| KR101818451B1 (ko) | 2010-12-24 | 2018-01-16 | 엘지디스플레이 주식회사 | 유기발광다이오드 표시소자 및 그 제조방법 |

| CN102708787A (zh) * | 2011-08-25 | 2012-10-03 | 京东方科技集团股份有限公司 | Amoled像素单元驱动电路和方法、像素单元以及显示装置 |

| CN102708786B (zh) * | 2011-08-25 | 2014-12-10 | 京东方科技集团股份有限公司 | Amoled像素单元驱动电路和方法、像素单元以及显示装置 |

| CN102708798B (zh) * | 2012-04-28 | 2015-05-13 | 京东方科技集团股份有限公司 | 一种像素单元驱动电路、驱动方法、像素单元和显示装置 |

| CN111403455B (zh) * | 2020-03-27 | 2022-11-11 | 京东方科技集团股份有限公司 | 显示面板及显示装置 |

Family Cites Families (38)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4356429A (en) | 1980-07-17 | 1982-10-26 | Eastman Kodak Company | Organic electroluminescent cell |

| US5276380A (en) | 1991-12-30 | 1994-01-04 | Eastman Kodak Company | Organic electroluminescent image display device |

| US5714968A (en) * | 1994-08-09 | 1998-02-03 | Nec Corporation | Current-dependent light-emitting element drive circuit for use in active matrix display device |

| US5550066A (en) | 1994-12-14 | 1996-08-27 | Eastman Kodak Company | Method of fabricating a TFT-EL pixel |

| JP3795606B2 (ja) * | 1996-12-30 | 2006-07-12 | 株式会社半導体エネルギー研究所 | 回路およびそれを用いた液晶表示装置 |

| JP3520396B2 (ja) * | 1997-07-02 | 2004-04-19 | セイコーエプソン株式会社 | アクティブマトリクス基板と表示装置 |

| JP3541625B2 (ja) * | 1997-07-02 | 2004-07-14 | セイコーエプソン株式会社 | 表示装置及びアクティブマトリクス基板 |

| JP3252897B2 (ja) | 1998-03-31 | 2002-02-04 | 日本電気株式会社 | 素子駆動装置および方法、画像表示装置 |

| JP2000228284A (ja) | 1998-12-01 | 2000-08-15 | Sanyo Electric Co Ltd | カラーel表示装置 |

| JP3406884B2 (ja) * | 1999-02-25 | 2003-05-19 | 株式会社東芝 | 集積回路装置及びこれを用いた液晶ディスプレイ装置 |

| JP3863325B2 (ja) * | 1999-09-10 | 2006-12-27 | 株式会社日立製作所 | 画像表示装置 |

| JP4497596B2 (ja) | 1999-09-30 | 2010-07-07 | 三洋電機株式会社 | 薄膜トランジスタ及び表示装置 |

| JP2001147659A (ja) * | 1999-11-18 | 2001-05-29 | Sony Corp | 表示装置 |

| JP2001318627A (ja) * | 2000-02-29 | 2001-11-16 | Semiconductor Energy Lab Co Ltd | 発光装置 |

| KR100327374B1 (ko) | 2000-03-06 | 2002-03-06 | 구자홍 | 액티브 구동 회로 |

| JP5030345B2 (ja) | 2000-09-29 | 2012-09-19 | 三洋電機株式会社 | 半導体装置 |

| US7015882B2 (en) * | 2000-11-07 | 2006-03-21 | Sony Corporation | Active matrix display and active matrix organic electroluminescence display |

| KR100370286B1 (ko) * | 2000-12-29 | 2003-01-29 | 삼성에스디아이 주식회사 | 전압구동 유기발광소자의 픽셀회로 |

| US6753654B2 (en) | 2001-02-21 | 2004-06-22 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device and electronic appliance |

| JP4212815B2 (ja) * | 2001-02-21 | 2009-01-21 | 株式会社半導体エネルギー研究所 | 発光装置 |

| JP4831874B2 (ja) | 2001-02-26 | 2011-12-07 | 株式会社半導体エネルギー研究所 | 発光装置及び電子機器 |

| JP3608613B2 (ja) * | 2001-03-28 | 2005-01-12 | 株式会社日立製作所 | 表示装置 |

| JP2003007720A (ja) * | 2001-06-21 | 2003-01-10 | Matsushita Electric Ind Co Ltd | 多結晶薄膜、薄膜トランジスタアレイ、画像表示装置およびそれらの製造方法 |

| JP2003005710A (ja) | 2001-06-25 | 2003-01-08 | Nec Corp | 電流駆動回路及び画像表示装置 |

| JP4075505B2 (ja) * | 2001-09-10 | 2008-04-16 | セイコーエプソン株式会社 | 電子回路、電子装置、及び電子機器 |

| TW563088B (en) * | 2001-09-17 | 2003-11-21 | Semiconductor Energy Lab | Light emitting device, method of driving a light emitting device, and electronic equipment |

| JP3810725B2 (ja) * | 2001-09-21 | 2006-08-16 | 株式会社半導体エネルギー研究所 | 発光装置及び電子機器 |

| CN107230450A (zh) * | 2001-09-21 | 2017-10-03 | 株式会社半导体能源研究所 | 显示装置及其驱动方法 |

| TWI261217B (en) * | 2001-10-31 | 2006-09-01 | Semiconductor Energy Lab | Driving circuit of signal line and light emitting apparatus |

| JP2003204067A (ja) | 2001-12-28 | 2003-07-18 | Semiconductor Energy Lab Co Ltd | 表示装置およびそれを用いた電子機器 |

| GB2384100B (en) * | 2002-01-09 | 2005-10-26 | Seiko Epson Corp | An electronic circuit for controlling the current supply to an element |

| JP2004207616A (ja) | 2002-12-26 | 2004-07-22 | Hitachi Displays Ltd | 表示装置 |

| JP4358644B2 (ja) * | 2003-01-06 | 2009-11-04 | 株式会社半導体エネルギー研究所 | 電子回路、表示装置及び電子機器 |

| JP4028805B2 (ja) * | 2003-01-14 | 2007-12-26 | ローム株式会社 | 有機el駆動回路およびこれを用いる有機el表示装置 |

| US6961032B2 (en) * | 2003-05-06 | 2005-11-01 | Eastman Kodak Company | Reducing the effects of shorts in pixels of an active matrix organic electroluminescent device |

| TW200500979A (en) * | 2003-05-20 | 2005-01-01 | Adv Lcd Tech Dev Ct Co Ltd | Light emission type display apparatus |

| JP4163567B2 (ja) * | 2003-07-09 | 2008-10-08 | 株式会社 日立ディスプレイズ | 発光型表示装置 |

| US7053875B2 (en) * | 2004-08-21 | 2006-05-30 | Chen-Jean Chou | Light emitting device display circuit and drive method thereof |

-

2004

- 2004-09-20 US US10/945,484 patent/US7105855B2/en not_active Expired - Lifetime

-

2005

- 2005-09-13 WO PCT/US2005/032745 patent/WO2006033919A2/en active Application Filing

- 2005-09-13 JP JP2007532424A patent/JP5122959B2/ja active Active

- 2005-09-13 KR KR1020127003251A patent/KR101210484B1/ko active IP Right Grant

- 2005-09-13 KR KR1020117023992A patent/KR101147352B1/ko active IP Right Grant

- 2005-09-13 KR KR1020077006223A patent/KR101197217B1/ko active IP Right Grant

-

2006

- 2006-04-17 US US11/405,250 patent/US7195949B2/en not_active Expired - Lifetime

-

2012

- 2012-08-29 JP JP2012188568A patent/JP5449488B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20060063298A1 (en) | 2006-03-23 |

| KR20110129463A (ko) | 2011-12-01 |

| WO2006033919A2 (en) | 2006-03-30 |

| JP5449488B2 (ja) | 2014-03-19 |

| KR20070053276A (ko) | 2007-05-23 |

| US7195949B2 (en) | 2007-03-27 |

| KR101147352B1 (ko) | 2012-05-22 |

| KR20120028398A (ko) | 2012-03-22 |

| KR101197217B1 (ko) | 2012-11-02 |

| JP2013012766A (ja) | 2013-01-17 |

| US7105855B2 (en) | 2006-09-12 |

| US20060186402A1 (en) | 2006-08-24 |

| KR101210484B1 (ko) | 2012-12-11 |

| JP2008513960A (ja) | 2008-05-01 |

| WO2006033919A3 (en) | 2006-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5122959B2 (ja) | Oledデバイスのための電流駆動型配置の提供 | |

| US10497757B2 (en) | Display device | |

| JP4074099B2 (ja) | 平面表示装置およびその製造方法 | |

| US6501448B1 (en) | Electroluminescence display device with improved driving transistor structure | |

| KR100553859B1 (ko) | 전기 광학 장치 | |

| EP0940796B1 (en) | Active matrix display | |

| US7382384B2 (en) | OLED displays with varying sized pixels | |

| US7863602B2 (en) | Organic light emitting diode display and method for manufacturing the same | |

| EP1850382A2 (en) | Modular display device and organic thin-film transistor | |

| US7554261B2 (en) | Electrical connection in OLED devices | |

| JP2000252550A (ja) | スイッチング素子及び有機エレクトロルミネッセンス素子表示装置 | |

| US20110121720A1 (en) | Electrical connection in oled devices | |

| US20060001363A1 (en) | Active matrix organic light emitting display device and method of fabricating the same | |

| JP2010225780A (ja) | 薄膜トランジスタ及び薄膜トランジスタの製造方法 | |

| KR100573108B1 (ko) | 박막 트랜지스터를 구비한 평판표시장치 | |

| KR100553744B1 (ko) | 박막 트랜지스터를 구비한 평판표시장치 | |

| CN116525623A (zh) | 阵列基板及其制备方法、显示面板和显示装置 | |

| JP2003066871A (ja) | 有機el表示装置及びその製造方法 | |

| KR20040094058A (ko) | 박막 트랜지스터를 구비한 평판표시장치 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080902 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080902 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20100804 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110315 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110614 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110621 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110914 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120124 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120131 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120424 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120529 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120829 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120925 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121025 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151102 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 5122959 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |