JP5082271B2 - チップコイルとその製造方法 - Google Patents

チップコイルとその製造方法 Download PDFInfo

- Publication number

- JP5082271B2 JP5082271B2 JP2006082278A JP2006082278A JP5082271B2 JP 5082271 B2 JP5082271 B2 JP 5082271B2 JP 2006082278 A JP2006082278 A JP 2006082278A JP 2006082278 A JP2006082278 A JP 2006082278A JP 5082271 B2 JP5082271 B2 JP 5082271B2

- Authority

- JP

- Japan

- Prior art keywords

- coil

- magnetic layer

- magnetic

- forming

- chip coil

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Measuring Magnetic Variables (AREA)

- Coils Or Transformers For Communication (AREA)

Description

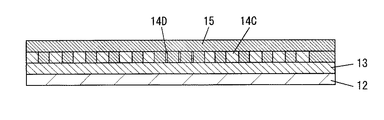

以下、本発明の実施の形態1におけるチップコイルについて図面を参照しながら説明する。

7 スルーホール部

8A コイル

8B、8C 端子

9 磁性体層

10 壁

Claims (2)

- フォトレジストから形成された素体と、この素体に設けられたスルーホール部と、このスルーホール部の外周方向において前記素体内に形成されたコイルと、このコイルに電気的に接続された端子と、前記スルーホール部の内周面に形成された磁性体層とを備え、この磁性体層には、前記コイルの巻回平面に略垂直な絶縁性の壁を設けるとともに、この絶縁性の壁は素体と同一のフォトレジストから形成されてなるチップコイル。

- フォトレジストから形成された素体と、この素体に設けられたスルーホール部と、このスルーホール部の外周方向において前記素体内に形成されたコイルと、このコイルに電気的に接続された端子と、前記スルーホール部の内周面に形成された磁性体層とを備え、この磁性体層には、前記コイルの巻回平面に略垂直な絶縁性の壁を設けるとともに、この絶縁性の壁は素体と同一のフォトレジストから形成されてなるチップコイルの製造方法であって、

前記磁性体層および前記絶縁性の壁を製造する工程は、

フォトレジストを用いて絶縁層を形成する第1の工程と、

前記絶縁層の一部を除去して磁性体層形成部を形成するとともに前記絶縁性の壁となる非磁性体層形成部を形成する第2の工程と、

前記磁性体層形成部に前記磁性体層を形成する第3の工程とを有する

前記チップコイルの製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006082278A JP5082271B2 (ja) | 2006-03-24 | 2006-03-24 | チップコイルとその製造方法 |

| US11/909,756 US8248200B2 (en) | 2006-03-24 | 2007-03-19 | Inductance component |

| CN2007800005291A CN101326597B (zh) | 2006-03-24 | 2007-03-19 | 感应器件 |

| PCT/JP2007/055535 WO2007119426A1 (ja) | 2006-03-24 | 2007-03-19 | インダクタンス部品 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006082278A JP5082271B2 (ja) | 2006-03-24 | 2006-03-24 | チップコイルとその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007258521A JP2007258521A (ja) | 2007-10-04 |

| JP2007258521A5 JP2007258521A5 (ja) | 2009-04-02 |

| JP5082271B2 true JP5082271B2 (ja) | 2012-11-28 |

Family

ID=38632445

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006082278A Expired - Fee Related JP5082271B2 (ja) | 2006-03-24 | 2006-03-24 | チップコイルとその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP5082271B2 (ja) |

| CN (1) | CN101326597B (ja) |

Families Citing this family (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5359842B2 (ja) * | 2009-12-11 | 2013-12-04 | Tdk株式会社 | 積層型コモンモードフィルタ |

| KR101862409B1 (ko) * | 2011-12-22 | 2018-07-05 | 삼성전기주식회사 | 칩 인덕터 및 칩 인덕터 제조방법 |

| JP6265031B2 (ja) * | 2014-04-25 | 2018-01-24 | 住友電装株式会社 | コア片及びリアクトル |

| KR101681406B1 (ko) * | 2015-04-01 | 2016-12-12 | 삼성전기주식회사 | 코일 전자부품 및 그 제조방법 |

| US10269481B2 (en) | 2016-05-27 | 2019-04-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Stacked coil for wireless charging structure on InFO package |

| KR101994754B1 (ko) | 2017-08-23 | 2019-07-01 | 삼성전기주식회사 | 인덕터 |

| JP7140481B2 (ja) | 2017-09-25 | 2022-09-21 | 日東電工株式会社 | インダクタおよびその製造方法 |

| KR102617535B1 (ko) * | 2018-07-25 | 2023-12-27 | 아지노모토 가부시키가이샤 | 자성 페이스트 |

| KR102597726B1 (ko) * | 2018-07-25 | 2023-11-06 | 아지노모토 가부시키가이샤 | 자성 페이스트 |

| JP7738986B2 (ja) * | 2020-09-28 | 2025-09-16 | Tdk株式会社 | 積層コイル部品 |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2986520B2 (ja) * | 1990-07-31 | 1999-12-06 | ティーディーケイ株式会社 | 電子部品及びその製造方法 |

| JPH04101403A (ja) * | 1990-08-21 | 1992-04-02 | Tdk Corp | 電子部品及びその製造方法 |

| JP2003158017A (ja) * | 2001-11-21 | 2003-05-30 | Jhc Osaka:Kk | トランス |

-

2006

- 2006-03-24 JP JP2006082278A patent/JP5082271B2/ja not_active Expired - Fee Related

-

2007

- 2007-03-19 CN CN2007800005291A patent/CN101326597B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN101326597B (zh) | 2012-05-02 |

| CN101326597A (zh) | 2008-12-17 |

| JP2007258521A (ja) | 2007-10-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5673359B2 (ja) | コイル部品及びその製造方法 | |

| CN100580825C (zh) | 超薄挠性电感器 | |

| US8248200B2 (en) | Inductance component | |

| US12340937B2 (en) | Coil component and manufacturing method therefor | |

| JP2015512155A (ja) | 電力伝送用途のための大電流かつ低等価直列抵抗のプリント回路基板コイル | |

| KR20130072813A (ko) | 칩 인덕터 및 칩 인덕터 제조방법 | |

| US11942255B2 (en) | Inductor component | |

| JP5082271B2 (ja) | チップコイルとその製造方法 | |

| US20130241684A1 (en) | Method for manufacturing common mode filter and common mode filter | |

| CN103377811A (zh) | 电磁器件及其线圈结构 | |

| KR20070032259A (ko) | 인덕터 및 인덕터 제조 방법 | |

| CN109427468B (zh) | 线圈组件 | |

| JP2022139098A (ja) | インダクタ部品および電子部品 | |

| JP2007227730A (ja) | チップコイル | |

| JP2009182188A (ja) | チップコイルおよびその製造方法 | |

| JP5082293B2 (ja) | インダクタンス部品とその製造方法 | |

| JP2007227729A (ja) | インダクタンス部品 | |

| JP2022143260A (ja) | インダクタ部品およびその製造方法 | |

| TWI885676B (zh) | 具內埋電感的電路板及其製造方法 | |

| JP5082282B2 (ja) | インダクタンス部品とその製造方法 | |

| JP2008010695A (ja) | インダクタンス部品 | |

| JP2008270383A (ja) | インダクタンス部品とその製造方法 | |

| JP2024132032A (ja) | 磁気部品 | |

| JP2005259969A (ja) | 半導体装置およびその製造方法 | |

| WO2026044249A2 (en) | Low resistance hybrid material inductor coils |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090213 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090213 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111004 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111202 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120807 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120820 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150914 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |