JP5036096B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP5036096B2 JP5036096B2 JP2000238080A JP2000238080A JP5036096B2 JP 5036096 B2 JP5036096 B2 JP 5036096B2 JP 2000238080 A JP2000238080 A JP 2000238080A JP 2000238080 A JP2000238080 A JP 2000238080A JP 5036096 B2 JP5036096 B2 JP 5036096B2

- Authority

- JP

- Japan

- Prior art keywords

- contact hole

- conductive film

- film

- unit area

- contact holes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Weting (AREA)

- Mechanical Treatment Of Semiconductor (AREA)

Description

【発明の属する技術分野】

この発明は半導体装置およびその製造方法に関し、特にコンタクトホール部の構造およびその製造方法に関するものである。

【0002】

【従来の技術】

近年、半導体装置の高集積化には目覚ましいものがある。それに伴い、微細加工技術の研究開発はとどまる所を知らず、コンタクトホール部の微細化も例外ではない。

【0003】

図7(a)〜(d)は従来のコンタクトホール部の製造方法を示す工程断面図である。図に従って順次説明を行なう。

まず、図7(a)に示すように、シリコン基板1上に素子分離領域2を形成する。その後、シリコン基板1にシリコン基板1と逆導電型のイオン注入を行ない、シリコン基板1と逆導電型の導電層3を形成する。更に全面に層間絶縁膜4を形成して、導電層3上の層間絶縁膜4をエッチングして導電層3上に至るコンタクトホール5を形成する。アルゴンなどのスパッタエッチングを施すことにより、コンタクトホール5上部に面取り部6を形成する。この面取り部6はアスペクト比の高いコンタクトホール5内への埋込み特性を向上させるために設けている。

【0004】

次に、図7(b)に示すように、全面にスパッタまたはCVD法によりTiN等のバリアメタル7を形成する。続いて、全面にWF6、H2ガス等を用いて、W−CVD法によりタングステン(W)膜8を形成する。この時、コンタクトホール5の上部には面取り部6を設け、コンタクトホール5内への埋込み特性を向上させてはいるが、コンタクトホール5内のバリアメタル7およびW膜8のカバレッジは100%とはならず、コンタクトホール5内にボイド9が形成されてしまう。

【0005】

次に、図7(c)に示すように、全面にCMP(Chemical Mechanical Polish)を施し、層間絶縁膜4上のバリアメタル7およびW膜8を除去してコンタクトホール5内にのみW膜8を埋込んでWプラグ10を形成する。

【0006】

次に、図7(d)に示すように、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。

【0007】

【発明が解決しようとする課題】

従来のコンタクトホール部の製造方法は以上のようであったので、図7に示すように、コンタクトホール5上部に面取り部6を設けている。この面取り部6はアスペクト比の高いコンタクトホール5内への埋込み特性を向上させることができるとともに、面取り部6の形成と同時に導電層3上の自然酸化膜等の絶縁膜を除去できるという効果がある。

【0008】

ところが、コンタクトホール5間の距離が小さい場合、面取り部6によってコンタクトホール5上部のコンタクトホール5径が大きくなってしまい、上部配線13間の分離、コンタクトホール5間の分離が難しくなリ、微細化の妨げとなるという問題点があった。

【0009】

また、コンタクトホール5内に発生しているボイド9によりコンタクトホール5内側壁のW膜8の膜厚が薄くなってしまい、Wプラグ10の垂直方向の抵抗が上昇するという問題点があった。

更に、後工程において、エッチング等に使用される薬液がボイド9内に浸入してW膜8を腐食させるという問題点があった。

【0010】

この発明は上記のような問題点を解消するためになされたもので、コンタクトホール間の距離が縮小しても良好な上部配線およびコンタクトホールの分離ができるとともに、アスペクト比の高いコンタクトホール内への良好な埋込みのできる半導体装置およびその製造方法を提供することを目的としている。

【0016】

【課題を解決するための手段】

この発明の請求項1に係る半導体装置の製造方法は、全面にCMPを施して、絶縁膜上の導電膜を除去してコンタクトホール内に上記導電膜を残す工程が、上記CMPを行なう時間を制御することによって、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部を除去するようにしたものである。単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した後に、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内及び絶縁膜上に、上部導電膜を堆積する工程と、絶縁膜上の上記上部導電膜を除去して、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内に、上記上部導電膜を埋込む工程とを備えるようにしたものである。

【0017】

この発明の請求項2に係る半導体装置の製造方法は、全面にCMPを施して、絶縁膜上の導電膜を除去してコンタクトホール内に上記導電膜を残す工程が、上記CMPを行なう時間を制御することによって、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部を除去するようにしたものである。単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した後に、単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内及び絶縁膜上に、上部導電膜を堆積する工程と、上記上部導電膜をパターニングして、単位面積当たりのコンタクトホール数の多少にかかわらず、上記導電膜上に上部配線を形成する工程とを備えるようにしたものである。

【0019】

【発明の実施の形態】

実施の形態1.

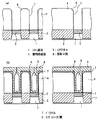

図1および2はこの発明のコンタクトホール部の製造方法を示す工程断面図であり、各図において、左側の図は単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域を示し、右側の図は左側の図と同一ウエハ内で単位面積当たりのコンタクトホール数が比較的少ない領域を示している。図に従って順次説明を行なう。

【0020】

まず図1(a)に示すように、シリコン基板1上に素子分離領域2を形成する。その後、シリコン基板1にシリコン基板1と逆導電型のイオン注入を行ない、シリコン基板1と逆導電型の導電層3を形成する。更に全面に層間絶縁膜4を形成して、導電層3上の層間絶縁膜4をエッチングして導電層3上に至るコンタクトホール5を形成する。アルゴンなどのスパッタエッチングを施すことにより、コンタクトホール5上部に面取り部6を形成する。この面取り部6はアスペクト比の高いコンタクトホール5内への埋込み特性を向上させるために設けている。

【0021】

次に、図1(b)に示すように、全面にスパッタまたはCVD法により導電膜であるTiN等のバリアメタル7を形成する。続いて、全面にWF6、H2ガス等を用いて、W−CVD法により導電膜であるW膜8を形成する。この時、コンタクトホール5の上部には面取り部6を設け、コンタクトホール5内への埋込み特性を向上させてはいるが、コンタクトホール5内のバリアメタル7およびW膜8のカバレッジは100%とはならず、コンタクトホール5内にボイド9が形成されてしまう。ここまでの工程では、左側の図と右側の図とのコンタクトホール部の構造は同じである。

【0022】

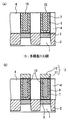

次に、図2(a)に示すように、全面にCMPを施し、層間絶縁膜4上のバリアメタル7およびW膜8を除去してコンタクトホール5内にのみバリアメタル7およびW膜8を埋込んでWプラグ10を形成するのであるが、この時、CMPを行なう時間を長くして、左側の図においてのみコンタクトホール5上部に面取り部6がなくなるまでCMPを行なう。

【0023】

一般に、CMPはコンタクトホールの占有面積が多い部分ではコンタクトホールの占有面積が少ない部分に比べて研磨される速度が早いので、同じ時間でCMPを行なうと、コンタクトホールの占有面積が多い部分が沢山削られることになる。

【0024】

従って、全面にCMPを行なう時間を延長すれば、単位面積当たりのコンタクトホール5数が多く、コンタクトホール5の占有面積が多い左側の図では、単位面積当たりのコンタクトホール5数が比較的少ない右側の図よりも削れる量が多くなる。

つまり、左側の図で、面取り部6がなくなるように時間を制御して全面にCMPを行なうと、右側の図では面取り部6は消失せずに残存する。

【0025】

次に、図2(b)に示すように、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。この時、左側の図にはコンタクトホール5上部の面取り部6は存在せず、コンタクトホール5間の距離を確保することができ上部配線13間の分離を確実に行える。右側の図にはコンタクトホール5上部の面取り部6が残存しているが、コンタクトホール5間の距離は初めから充分にあるので問題はない。

【0026】

以上のように、コンタクトホール5内へW膜8を埋込んでWプラグ10を形成する際に、CMPを通常よりも長く行なうことによって、単位面積当たりのコンタクトホール5が多い領域の面取り部6をなくすことができ、上部配線13間の分離、コンタクトホール5間の分離を確実に行なうことができる。したがって、更にコンタクトホール5間の距離を縮小することができ、半導体装置の高集積化を図ることができる。

【0027】

また、バリアメタル7、11はWN、TaN等でも良い。更に、導電膜12はアルミ合金、高融点金属、高融点金属のシリサイドでも良く、導電層3とバリアメタル7との界面にTiSi、CoSi等の高融点金属シリサイドを形成しても良い。上記いずれの場合も同様の効果が得られる。

【0028】

実施の形態2.

上記実施の形態1では単位面積当たりのコンタクトホールの多い領域において、コンタクトホール上部の面取り部を完全に除去する場合について説明をしたが、ここでは、単位面積当たりのコンタクトホールの多い領域においても面取り部を一部残す場合について説明する。

【0029】

図3(a)(b)はこの発明の実施の形態2のコンタクトホール部の製造方法を示す断面図であり、左側の図は単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域を示し、右側の図は左側の図と同一ウエハ内で単位面積当たりのコンタクトホール数が比較的少ない領域を示している。14は層間絶縁膜4中に形成された下層配線である。

図3に至るまでは上記実施の形態1の図1(a)(b)と同様に行なう。

【0030】

図3(a)に示すように、右側の図は実施の形態1の図2(a)の右側の図と同様である。左側の図は実施の形態1の図2(a)の左側の図とは異なり、コンタクトホール5上部の面取り部6を完全に除去するのではなく、後に形成される上部配線13間およびコンタクトホール5間が分離できる程度にCMPの時間を制御して行ない、コンタクトホール5上部の面取り部6の一部を残存させている。

【0031】

次に、図3(b)に示すように、図2(b)と同様にして、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。この時、左側の図ではコンタクトホール5上部の面取り部6はコンタクトホール5間の距離を確保することができる程度に存在し、上部配線13間の分離を確実に行える。

【0032】

従って、上記実施の形態1と同様の効果を有するとともに、CMPを行なう時間を上記実施の形態1の場合よりも短く設定でき、単位面積当たりのコンタクトホール5が多い領域においてCMPによって削れる量を少なくすることができる。これにより、CMP工程後の平坦度は上記実施の形態1よりも高くすることができる。また、層間絶縁膜4中に下層配線14等が存在していても、CMPによって削られる可能性を低くおさえられる。

【0033】

実施の形態3.

上記実施の形態1ではCMP後ボイドを塞ぐことなく、上部配線を形成していたが、ここではCMP後コンタクトホール内にさらに導電膜を埋込む場合について説明する。

【0034】

図4(a)(b)はこの発明の実施の形態3のコンタクトホール部の製造方法を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。

図4に至るまでは上記実施の形態1の図1(a)(b)図2(a)と同様に行なう。

【0035】

図4(a)に示すように、CMPを行なう時間を長くすることによって、単位面積当たりのコンタクトホール数の多い領域ではコンタクトホール5上部の面取り部6を除去すると同時にコンタクトホール5上部に埋込まれていたW膜8が除去され、コンタクトホール5内のボイド9が開口する。

【0036】

この開口を含む全面に上部導電膜である不純物をド−プした多結晶シリコン膜15をCVD法で堆積した後、CMPを施すことにより層間絶縁膜4上の多結晶シリコン膜15を除去してボイド9内にのみ多結晶シリコン膜15を埋込む。

【0037】

次に、図4(b)に示すように、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。

【0038】

この様にすれば、ボイド9を塞ぐことができるので、後処理によるボイド9への薬液の染み込みを防止することができる。また、ボイド9を多結晶シリコン膜15で埋込んだので、コンタクトホール5の垂直方向の抵抗を下げることができる。

【0039】

実施の形態4.

上記実施の形態3ではボイド9内に多結晶シリコン膜15を埋込む場合について説明を行なったが、ここでは更に低抵抗な導電膜を埋込む場合について説明する。

【0040】

図5はこの発明の実施の形態4のコンタクトホール部を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。

図5に至るまでは上記実施の形態1の図1(a)(b)図2(a)と同様に行なう。

【0041】

図5に示すように、CMPによって開口したボイド9内を含む全面にスパッタまたはCVD法により上部導電膜であるTiN等のバリアメタル7aを形成する。続いて、全面にWF6、H2ガス等を用いて、W−CVD法により上部導電膜であるW膜8aを形成する。その後全面にCMPを施し、層間絶縁膜4上のバリアメタル7aおよびW膜8aを除去してボイド9内にのみバリアメタル7aおよびW膜8aを埋込む。

【0042】

その後、全面にTiNなどのバリアメタル11、Wなどの導電膜12をスパッタまたはCVD法で堆積する。その後、バリアメタル11および導電膜12に所望のパターニングを施して上部配線13を形成する。

【0043】

この様にすれば、より低抵抗なバリアメタル7aおよびW膜8aでコンタクトホール5内のボイド9を塞ぐことができ、コンタクトホール5の垂直方向の抵抗をさらに下げることができる。

【0044】

実施の形態5.

上記実施の形態4では上部配線13の形成とコンタクトホール5内の埋込みとを別々に行なっていたがここでは一度に形成する方法について説明する。

【0045】

図6はこの発明の実施の形態4のコンタクトホール部を示す断面図であり、単位面積当たりのコンタクトホール数が多く、コンタクトホール間の距離が短い領域の断面図である。

図6に至るまでは上記実施の形態1の図1(a)(b)図2(a)と同様に行なう。

【0046】

図6に示すように、CMPによって開口したボイド9内を含む全面にスパッタまたはCVD法によりTiN等のバリアメタル7aを形成する。続いて、全面にWF6、H2ガス等を用いて、W−CVD法によりW膜8aを形成する。その後、上部配線13用のパターニングを行ないW膜8aからなる上部配線13を形成する。

【0047】

この様にすれば、上記実施の形態4に比べて、CMP、バリアメタル11の形成、導電膜12の形成工程を省略することができ、製造工程数を減らすことができる。又、上部配線13とコンタクトホール5内との界面などの導電膜間の界面を減少させることができるのでより低抵抗なコンタクトホールを形成することができる。

【0048】

【発明の効果】

以上のようにこの発明によれば、各コンタクトホールのうち、単位面積当たりの上記コンタクトホール数の少ない領域に形成されたコンタクトホールは、その上部に面取り部を備え、単位面積当たりの上記コンタクトホール数の多い領域に形成されたコンタクトホールは、その上部に上記面取り部を備えないようにしたので、単位面積当たりのコンタクトホール数の多い領域において、コンタクトホール間の分離が良好に行え、コンタクトホール間の距離をさらに縮小することができる。

【0049】

また、各コンタクトホールのうち、単位面積当たりの上記コンタクトホール数の多い領域に形成されたコンタクトホールは、単位面積当たりの上記コンタクトホール数の少ない領域に形成されたコンタクトホールよりも小さな面取り部を備えるようにしたので、コンタクトホール間の分離が良好に行えるとともに、ウエハの平坦度が向上し、層間絶縁膜中の下部配線を損なうこともない。

【0050】

また、単位面積当たりのコンタクトホール数の多い領域に形成された導電膜を有するコンタクトホールにおいて、上記導電膜上に上部導電膜を設け、上記導電膜がバリアメタルとタングステン膜とから成り、上記上部導電膜が多結晶シリコン膜から成り、上記コンタクトホール内に、上記バリアメタルと上記タングステン膜と上記多結晶シリコン膜との三層を備えるようにしたので、コンタクトホール内のボイドを塞ぐことができ、コンタクトホール内の垂直方向の抵抗を低くできる。

【0051】

単位面積当たりのコンタクトホール数の多い領域に形成された導電膜を有するコンタクトホールにおいて、上記導電膜上に上部導電膜を設け、上記導電膜および上記上部導電膜がともにバリアメタルとタングステン膜とから成り、上記コンタクトホール内に、上記バリアメタルと上記タングステン膜と上記バリアメタルと上記タングステン膜との四層を備えるようにしたので、コンタクトホール内の抵抗をより低くすることができる。

【0052】

コンタクトホールの導電膜上に上部配線を備えるようにしたので、上部配線の分離を良好に行える。

【0053】

全面にCMPを施して、絶縁膜上の導電膜を除去してコンタクトホール内にのみ上記導電膜を埋込む工程が、上記CMPを行なう時間を制御することによって、単位面積当たりのコンタクトホール数の少ない領域の上記コンタクトホール上部の上記面取り部の大きさより、単位面積当たりのコンタクトホール数の多い領域の上記コンタクトホール上部の上記面取り部の大きさを小さくまたは除去するようにしたので、

コンタクトホール間の距離に応じて面取り部の大きさを選択することができ、素子に応じて面取り部の大きさを選択する自由度が広がる。

【0054】

単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した場合、この除去を行なった後に、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内を含む全面に、上部導電膜を堆積する工程と、絶縁膜上の上記上部導電膜を除去して、上記単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内に、上記上部導電膜を埋込む工程とを備えるようにしたもので、コンタクトホール内のボイドを塞ぐことができ、コンタクトホール内の垂直方向の抵抗を低くできる。

【0055】

単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール上部の面取り部を除去した場合、この除去を行なった後に、単位面積当たりのコンタクトホール数の多い領域の導電膜を埋込んだコンタクトホール内を含む全面に、上部導電膜を堆積する工程と、上記上部導電膜をパターニングして、単位面積当たりのコンタクトホール数の多少にかかわらず、上記導電膜上に上部配線を形成する工程とを備えるようにしたので、上部配線の形成とコンタクトホール内の埋込みを一度で行なうことができ、製造工程数を減少させることができる。

【図面の簡単な説明】

【図1】 この発明のコンタクトホール部の製造方法を示す工程断面図である。

【図2】 この発明のコンタクトホール部の製造方法を示す工程断面図である。

【図3】 この発明の実施の形態2のコンタクトホール部の製造方法を示す工程断面図である。

【図4】 この発明の実施の形態3のコンタクトホール部の製造方法を示す工程断面図である。

【図5】 この発明の実施の形態4のコンタクトホール部を示す断面図である。

【図6】 この発明の実施の形態5のコンタクトホール部を示す断面図である。

【図7】 従来のコンタクトホール部の製造方法示す工程断面図である。

【符号の説明】

1 シリコン基板、4 層間絶縁膜、5 コンタクトホール、6 面取り部、7,7a バリアメタル、8,8a W膜、13 上部配線、15 多結晶シリコン膜。

Claims (2)

- シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜中に単位面積当たりの数が異なる複数のコンタクトホールを形成する工程と、前記コンタクトホールの上部に面取り部を形成する工程と、前記コンタクトホール内及び前記絶縁膜上に導電膜を形成する工程と、CMPを施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程とを備えた半導体装置の製造方法において、

前記CMPを施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程が、前記単位面積当たりの前記コンタクトホール数の多い領域の前記コンタクトホール上部の前記面取り部を除去するようにしたことを特徴とし、

前記面取り部を除去した後に、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内及び前記絶縁膜上に、上部導電膜を堆積する工程と、前記絶縁膜上の前記上部導電膜を除去して、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内に、前記上部導電膜を埋込む工程とを備えた事を特徴とする半導体装置の製造方法。 - シリコン基板上に絶縁膜を形成する工程と、前記絶縁膜中に単位面積当たりの数が異なる複数のコンタクトホールを形成する工程と、前記コンタクトホールの上部に面取り部を形成する工程と、前記コンタクトホール内及び前記絶縁膜上に導電膜を形成する工程と、CMPを施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程とを備えた半導体装置の製造方法において、

前記CMPを施して、前記絶縁膜上の前記導電膜を除去して前記コンタクトホール内に前記導電膜を残す工程が、前記単位面積当たりの前記コンタクトホール数の多い領域の前記コンタクトホール上部の前記面取り部を除去するようにしたことを特徴とし、

前記面取り部を除去した後に、前記単位面積当たりの前記コンタクトホール数の多い領域の前記導電膜を埋込んだ前記コンタクトホール内及び前記絶縁膜上に、上部導電膜を堆積する工程と、前記上部導電膜をパターニングして、前記導電膜上に上部配線を形成する工程とを備えたことを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000238080A JP5036096B2 (ja) | 2000-08-07 | 2000-08-07 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000238080A JP5036096B2 (ja) | 2000-08-07 | 2000-08-07 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002050689A JP2002050689A (ja) | 2002-02-15 |

| JP2002050689A5 JP2002050689A5 (ja) | 2007-09-20 |

| JP5036096B2 true JP5036096B2 (ja) | 2012-09-26 |

Family

ID=18729837

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000238080A Expired - Fee Related JP5036096B2 (ja) | 2000-08-07 | 2000-08-07 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5036096B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7224068B2 (en) * | 2004-04-06 | 2007-05-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Stable metal structure with tungsten plug |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09148431A (ja) * | 1995-11-21 | 1997-06-06 | Nec Corp | 半導体装置の製造方法 |

| JP3393436B2 (ja) * | 1996-12-03 | 2003-04-07 | ソニー株式会社 | 配線の形成方法 |

| JP3111924B2 (ja) * | 1997-04-11 | 2000-11-27 | 日本電気株式会社 | 半導体装置の製造方法 |

| JP2000003912A (ja) * | 1998-06-16 | 2000-01-07 | Hitachi Ltd | 半導体装置の製造方法および半導体装置 |

| JP3141939B2 (ja) * | 1998-11-26 | 2001-03-07 | 日本電気株式会社 | 金属配線形成方法 |

-

2000

- 2000-08-07 JP JP2000238080A patent/JP5036096B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002050689A (ja) | 2002-02-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7741228B2 (en) | Method for fabricating semiconductor device | |

| CN1913128B (zh) | 双金属镶嵌金属布线图案的形成方法和形成的布线图案 | |

| JP3348706B2 (ja) | 半導体装置の製造方法 | |

| JPH11340332A (ja) | 信頼性を増強するための金属プラグの可変不純物添加 | |

| JP2005051247A (ja) | 金属−絶縁物−金属キャパシタおよび配線構造 | |

| JPH0864822A (ja) | 局部相互接続のオーバパス・マスク/絶縁体及びその製造方法 | |

| JP3050161B2 (ja) | 半導体装置及びその製造方法 | |

| US6137180A (en) | Low cost DRAM metallization | |

| JP3102405B2 (ja) | 半導体装置の製造方法 | |

| KR100367734B1 (ko) | 반도체 소자의 배선형성 방법 | |

| JP2005050903A (ja) | 半導体装置およびその製造方法 | |

| KR19990083188A (ko) | 반도체기판에서의 소형화된 접촉 및 이를 형성하는 방법 | |

| JP5291310B2 (ja) | 半導体装置の製造方法 | |

| JP3718458B2 (ja) | 半導体装置の製造方法 | |

| JP5036096B2 (ja) | 半導体装置の製造方法 | |

| JP4646591B2 (ja) | 半導体装置及びその製造方法 | |

| US5837608A (en) | Method of filling a contact hole in a semiconductor device using vertical growth of metal | |

| US20020106895A1 (en) | Method for forming copper interconnect and enhancing electromigration resistance | |

| JP2004311537A (ja) | 半導体装置 | |

| JP3534589B2 (ja) | 多層配線装置及びその製造方法 | |

| KR100224721B1 (ko) | 반도체장치의 금속배선 형성방법 | |

| JP2009016619A (ja) | 半導体装置及びその製造方法 | |

| JPH1041386A (ja) | 半導体装置の製造方法 | |

| KR100571407B1 (ko) | 반도체 소자의 배선 제조 방법 | |

| JP2004356315A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20060123 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070806 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070806 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20071101 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090917 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100519 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110712 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110906 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120306 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120413 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120626 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120703 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150713 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |