JP5014194B2 - ボルテージレギュレータ - Google Patents

ボルテージレギュレータ Download PDFInfo

- Publication number

- JP5014194B2 JP5014194B2 JP2008042592A JP2008042592A JP5014194B2 JP 5014194 B2 JP5014194 B2 JP 5014194B2 JP 2008042592 A JP2008042592 A JP 2008042592A JP 2008042592 A JP2008042592 A JP 2008042592A JP 5014194 B2 JP5014194 B2 JP 5014194B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- output

- circuit

- voltage

- differential amplifier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000001514 detection method Methods 0.000 claims description 24

- 230000007704 transition Effects 0.000 claims description 9

- 239000003990 capacitor Substances 0.000 description 14

- 238000010586 diagram Methods 0.000 description 13

- 230000008859 change Effects 0.000 description 9

- 230000004044 response Effects 0.000 description 9

- 230000001052 transient effect Effects 0.000 description 9

- 230000000694 effects Effects 0.000 description 6

- 230000003993 interaction Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000033228 biological regulation Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000000034 method Methods 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 238000013459 approach Methods 0.000 description 1

- 230000001276 controlling effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is dc

- G05F3/10—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics being semiconductor devices

- G05F3/20—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations

- G05F3/26—Current mirrors

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is dc

- G05F1/56—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices

- G05F1/575—Regulating voltage or current wherein the variable actually regulated by the final control device is dc using semiconductor devices in series with the load as final control devices characterised by the feedback circuit

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is dc

- G05F3/10—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is dc using uncontrolled devices with non-linear characteristics being semiconductor devices

Description

(1)式において、Vinはボルテージレギュレータへの入力電圧、Voutはボルテージレギュレータからの出力電圧、Ioutはボルテージレギュレータから負荷に接続している機器へ供給される出力電流、Issはボルテージレギュレータ自体が動作するために必要な消費電流である。

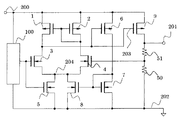

101 ・・・・定電流回路101

102 ・・・・差動増幅回路

103 ・・・・出力ドライバ

104 ・・・・分圧回路

105 ・・・・出力電流検出回路

106,406 ・・・・電流ミラー回路

107 ・・・・差電圧検出回路

205 ・・・・動作選択端子

Claims (4)

- 出力トランジスタの出力する電圧を分圧した参照電圧と基準電圧の差を増幅して出力し、前記出力トランジスタのゲートを制御する差動増幅回路を備えたボルテージレギュレータであって、

前記差動増幅回路の動作電流を供給する電流源と、

前記出力トランジスタに流れる電流に基づいた電流を出力する出力電流検出回路と、

前記出力電流検出回路の出力電流に基づいて、前記差動増幅回路の動作電流を変化させる電流ミラー回路を有し、

前記電流ミラー回路は、前記参照電圧と前記基準電圧の差の絶対値が一定値以上になったことを検出すると、所定の遅延時間を経て前記差動増幅回路の動作電流を変化させることを特徴とするボルテージレギュレータ。 - 出力トランジスタの出力する電圧を分圧した参照電圧と基準電圧の差を増幅して出力し、前記出力トランジスタのゲートを制御する差動増幅回路を備え、通常動作状態と、低消費で動作する待機動作状態を有するボルテージレギュレータであって、

前記出力トランジスタに流れる電流に基づいた電流を出力する出力電流検出回路と、

前記出力電流検出回路の出力電流に基づいて、前記差動増幅回路の動作電流を変化させる電流ミラー回路を有し、

前記電流ミラー回路は、前記待機動作状態から前記通常動作状態への状態遷移を検出すると、所定の遅延時間を経て前記差動増幅回路の動作電流を変化させることを特徴とするボルテージレギュレータ。 - 前記電流ミラー回路は、スイッチトカレント回路を備えたことを特徴とする請求項1または2に記載のボルテージレギュレータ。

- 前記電流ミラー回路の前記遅延は、前記出力電流の単位時間当たりの変動率に対して、前記差動増幅回路の動作電流の単位時間当たりの変動率を小さくすることで実現することを特徴とする請求項1または2に記載のボルテージレギュレータ。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008042592A JP5014194B2 (ja) | 2008-02-25 | 2008-02-25 | ボルテージレギュレータ |

| TW098104512A TWI437404B (zh) | 2008-02-25 | 2009-02-12 | Voltage regulator |

| KR20090015135A KR101508391B1 (ko) | 2008-02-25 | 2009-02-24 | 전압 레귤레이터 |

| US12/380,145 US8026708B2 (en) | 2008-02-25 | 2009-02-24 | Voltage regulator |

| CN2009101182129A CN101520668B (zh) | 2008-02-25 | 2009-02-25 | 稳压器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008042592A JP5014194B2 (ja) | 2008-02-25 | 2008-02-25 | ボルテージレギュレータ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009199501A JP2009199501A (ja) | 2009-09-03 |

| JP2009199501A5 JP2009199501A5 (ja) | 2011-01-27 |

| JP5014194B2 true JP5014194B2 (ja) | 2012-08-29 |

Family

ID=41052937

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008042592A Expired - Fee Related JP5014194B2 (ja) | 2008-02-25 | 2008-02-25 | ボルテージレギュレータ |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US8026708B2 (ja) |

| JP (1) | JP5014194B2 (ja) |

| KR (1) | KR101508391B1 (ja) |

| CN (1) | CN101520668B (ja) |

| TW (1) | TWI437404B (ja) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5361614B2 (ja) | 2009-08-28 | 2013-12-04 | ルネサスエレクトロニクス株式会社 | 降圧回路 |

| JP2012195326A (ja) * | 2011-03-14 | 2012-10-11 | Ricoh Co Ltd | 半導体装置 |

| JP2012203673A (ja) * | 2011-03-25 | 2012-10-22 | Seiko Instruments Inc | ボルテージレギュレータ |

| CN102915061B (zh) * | 2011-08-05 | 2015-05-06 | 深圳市汇春科技有限公司 | 极低静态电流的低压降稳压器 |

| CN102393780B (zh) * | 2011-11-30 | 2013-12-25 | 中国科学院微电子研究所 | 稳压电路 |

| US20130221940A1 (en) * | 2012-02-24 | 2013-08-29 | Shouli Yan | Linear regulator |

| JP6130112B2 (ja) | 2012-09-07 | 2017-05-17 | エスアイアイ・セミコンダクタ株式会社 | ボルテージレギュレータ |

| JP6168864B2 (ja) * | 2012-09-07 | 2017-07-26 | エスアイアイ・セミコンダクタ株式会社 | ボルテージレギュレータ |

| JP5989482B2 (ja) * | 2012-09-24 | 2016-09-07 | エスアイアイ・セミコンダクタ株式会社 | 電源切替え回路 |

| JP2014139743A (ja) * | 2013-01-21 | 2014-07-31 | Toshiba Corp | レギュレータ回路 |

| JP6250418B2 (ja) * | 2013-05-23 | 2017-12-20 | エスアイアイ・セミコンダクタ株式会社 | ボルテージレギュレータ |

| EP2816438B1 (en) * | 2013-06-20 | 2017-11-15 | Dialog Semiconductor GmbH | Active clamps for multi-stage amplifiers in over/under-voltage condition |

| CN104104228B (zh) * | 2014-08-04 | 2017-06-06 | 南京矽力杰半导体技术有限公司 | 同步整流电路和应用其的充电电路 |

| CN105446403A (zh) * | 2014-08-14 | 2016-03-30 | 登丰微电子股份有限公司 | 低压差线性稳压器 |

| KR102245472B1 (ko) * | 2014-08-18 | 2021-04-29 | 삼성디스플레이 주식회사 | Dc-dc 컨버터 및 이를 포함하는 유기 발광 표시 장치 |

| CN107272795B (zh) * | 2016-04-07 | 2019-03-15 | 瑞昱半导体股份有限公司 | 稳压器 |

| US9906221B1 (en) * | 2016-12-30 | 2018-02-27 | Delta Electronics, Inc. | Driving circuit of a power circuit |

| KR101984400B1 (ko) | 2017-10-20 | 2019-05-30 | 동아대학교 산학협력단 | 항산화 및 항피로 효능을 갖는 매실식초의 제조방법 |

| JP2021033472A (ja) * | 2019-08-20 | 2021-03-01 | ローム株式会社 | リニア電源 |

| CN114008555B (zh) * | 2020-03-18 | 2022-11-22 | 日清纺微电子有限公司 | 电源装置以及电子设备 |

| CN114242020B (zh) * | 2022-02-22 | 2022-06-10 | 深圳通锐微电子技术有限公司 | 一种瞬态恢复电路 |

| CN116880656B (zh) * | 2023-07-25 | 2024-03-22 | 深圳市迪浦电子有限公司 | 一种带定电流反馈的jfet高压稳压电路 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100364428B1 (ko) * | 2000-12-30 | 2002-12-11 | 주식회사 하이닉스반도체 | 고전압 레귤레이션 회로 |

| JP4156863B2 (ja) * | 2002-05-14 | 2008-09-24 | 株式会社ルネサステクノロジ | 半導体集積回路およびicカード |

| JP2003338744A (ja) * | 2002-05-21 | 2003-11-28 | New Japan Radio Co Ltd | 定電流スイッチング回路 |

| JP4527592B2 (ja) * | 2005-04-18 | 2010-08-18 | 株式会社リコー | 定電圧電源回路 |

| JP2006331235A (ja) * | 2005-05-27 | 2006-12-07 | Sharp Corp | 電圧変換回路および電子機器 |

| JP4774247B2 (ja) * | 2005-07-21 | 2011-09-14 | Okiセミコンダクタ株式会社 | 電圧レギュレータ |

| US7710090B1 (en) * | 2009-02-17 | 2010-05-04 | Freescale Semiconductor, Inc. | Series regulator with fold-back over current protection circuit |

-

2008

- 2008-02-25 JP JP2008042592A patent/JP5014194B2/ja not_active Expired - Fee Related

-

2009

- 2009-02-12 TW TW098104512A patent/TWI437404B/zh not_active IP Right Cessation

- 2009-02-24 US US12/380,145 patent/US8026708B2/en not_active Expired - Fee Related

- 2009-02-24 KR KR20090015135A patent/KR101508391B1/ko active IP Right Grant

- 2009-02-25 CN CN2009101182129A patent/CN101520668B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW200941179A (en) | 2009-10-01 |

| JP2009199501A (ja) | 2009-09-03 |

| CN101520668B (zh) | 2013-07-24 |

| CN101520668A (zh) | 2009-09-02 |

| US8026708B2 (en) | 2011-09-27 |

| US20090224740A1 (en) | 2009-09-10 |

| TWI437404B (zh) | 2014-05-11 |

| KR101508391B1 (ko) | 2015-04-06 |

| KR20090091665A (ko) | 2009-08-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5014194B2 (ja) | ボルテージレギュレータ | |

| US8242760B2 (en) | Constant-voltage circuit device | |

| TWI516892B (zh) | 低壓降穩壓器及運算系統 | |

| US8129966B2 (en) | Voltage regulator circuit and control method therefor | |

| US8810219B2 (en) | Voltage regulator with transient response | |

| US7199566B2 (en) | Voltage regulator | |

| JP4889398B2 (ja) | 定電圧電源回路 | |

| US20130193939A1 (en) | Voltage regulator | |

| CN113110694B (zh) | 一种具有电流浪涌抑制的低压差线性稳压器电路 | |

| US20060113978A1 (en) | Voltage regulator | |

| EP2894537A1 (en) | Voltage regulator | |

| KR102470562B1 (ko) | 향상된 슬루율을 갖는 레귤레이터 | |

| US9063558B2 (en) | Current limiting circuit configured to limit output current of driver circuit | |

| KR102225712B1 (ko) | 볼티지 레귤레이터 | |

| CN108021177B (zh) | 基于nmos的电压调节器 | |

| US10761549B2 (en) | Voltage sensing mechanism to minimize short-to-ground current for low drop-out and bypass mode regulators | |

| CN111367340B (zh) | 一种低压差线性稳压电路 | |

| CN107967019B (zh) | 一种cmos ldo及改善其负载响应特性的系统 | |

| US11442480B2 (en) | Power supply circuit alternately switching between normal operation and sleep operation | |

| KR101869565B1 (ko) | 볼티지 레귤레이터 | |

| JP4908019B2 (ja) | スイッチングレギュレータ | |

| CN106980336B (zh) | 稳压器 | |

| JP2019164800A (ja) | ボルテージレギュレータ | |

| KR20150072791A (ko) | 로우 드롭 출력 타입의 전압 레귤레이터 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091108 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091113 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20091117 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101208 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101208 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120523 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120529 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120605 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150615 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5014194 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |