JP4994112B2 - 半導体集積回路装置およびメモリ制御方法 - Google Patents

半導体集積回路装置およびメモリ制御方法 Download PDFInfo

- Publication number

- JP4994112B2 JP4994112B2 JP2007135791A JP2007135791A JP4994112B2 JP 4994112 B2 JP4994112 B2 JP 4994112B2 JP 2007135791 A JP2007135791 A JP 2007135791A JP 2007135791 A JP2007135791 A JP 2007135791A JP 4994112 B2 JP4994112 B2 JP 4994112B2

- Authority

- JP

- Japan

- Prior art keywords

- data

- flash memory

- verify

- flash

- writing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/08—Error detection or correction by redundancy in data representation, e.g. by using checking codes

- G06F11/10—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's

- G06F11/1008—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices

- G06F11/1068—Adding special bits or symbols to the coded information, e.g. parity check, casting out 9's or 11's in individual solid state devices in sector programmable memories, e.g. flash disk

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/0796—Safety measures, i.e. ensuring safe condition in the event of error, e.g. for controlling element

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/07—Responding to the occurrence of a fault, e.g. fault tolerance

- G06F11/14—Error detection or correction of the data by redundancy in operations

- G06F11/1402—Saving, restoring, recovering or retrying

- G06F11/1405—Saving, restoring, recovering or retrying at machine instruction level

- G06F11/141—Saving, restoring, recovering or retrying at machine instruction level for bus or memory accesses

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C2029/0409—Online test

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Quality & Reliability (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Read Only Memory (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

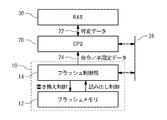

11 リセットシーケンス制御部

12 フラッシュメモリ

120 メモリセルアレイ

122 ユーザ領域

123 リダンダンシ用ブロック

124 エクストラ領域

126 アドレスデコーダ

128 セレクタ

14 フラッシュ制御部

20 CPU

22、24 バス

26 周辺バス

30 RAM

40 書き換え制御シーケンサ

42 制御レジスタ

52 アドレスポインタ

54 ライトバッファ

56 リードバッファ

62 レジスタ

64 ECCエンコーダ

66 ECCデコーダ

Claims (17)

- フラッシュメモリと、

前記フラッシュメモリに対する書き換え制御と、読み出し制御とを行うフラッシュ制御部と、

前記フラッシュメモリの書き換え動作の後にベリファイ動作を前記フラッシュ制御部に指示するプロセッサ部と

を具備し、

前記書き換え動作は前記フラッシュメモリの所定の領域を未書き込み状態にする消去動作を含み、

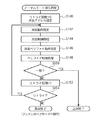

前記プロセッサ部は、動作状態として、

前記フラッシュメモリにデータを書き込んだ後の前記ベリファイ動作において不良を検出すると以降の前記フラッシュメモリの使用を停止するノーマルモードと、

前記フラッシュメモリにデータを書き込んだ後の前記ベリファイ動作において不良を検出するとエラー訂正して前記フラッシュメモリの使用を継続するフェイルセーフモードと

を備え、

前記ノーマルモードの前記消去動作後の前記ベリファイ動作において不良を検出すると、前記フェイルセーフモードに移行する

半導体集積回路装置。 - 前記フラッシュ制御部は、

前記フラッシュメモリに書き込むデータに対する誤り訂正符号を生成するECCエンコーダと、

前記フラッシュメモリから読み出された読み出しデータに基づいてエラー訂正するECCデコーダと

を備え、

前記書き込むデータは、前記誤り訂正符号とともに前記フラッシュメモリに書き込まれ、前記ECCデコーダの機能を停止して前記ベリファイ動作を行ない、

前記ノーマルモードにおいて前記書き換え動作が所定の回数を超えてリトライされたとき、書き込み不良として以降の前記フラッシュメモリの使用を停止し、

前記フェイルセーフモードにおいて前記書き換え動作が所定の回数を超えてリトライされたとき、前記ECCデコーダの機能を有効にして前記ベリファイ動作が行われる

請求項1に記載の半導体集積回路装置。 - 前記フラッシュメモリは、代替用ブロックを備え、

前記フラッシュ制御部は、前記消去動作後の前記ベリファイ動作において不良を検出すると、前記不良が検出された前記フラッシュメモリのブロックに代えて前記代替用ブロックを自動的にアクセスするように、前記フラッシュメモリのアクセスアドレスを変換する

請求項1または請求項2に記載の半導体集積回路装置。 - 前記フラッシュメモリは、

前記不良が検出された前記フラッシュメモリのブロックを示すリダンダンシ情報を格納するエクストラ領域と、

前記リダンダンシ情報に基づいて前記アクセスアドレスを変更するアドレスレジスタと

を備える

請求項3に記載の半導体集積回路装置。 - 前記フラッシュ制御部は、

前記リダンダンシ情報を格納するレジスタと、

前記プロセッサ部の初期設定が終了する前に前記エクストラ領域に格納されている前記リダンダンシ情報を読み出して前記レジスタに格納するリセットシーケンス制御部と

を備える

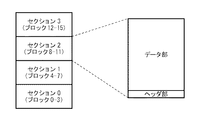

請求項4に記載の半導体集積回路装置。 - 前記フラッシュメモリは、複数のセクションに分割されて管理され、

前記複数のセクションのうちの第1セクション内にデータを書き込める領域が所定の閾値以下になると、前記第1セクション内の有効データを第2セクションにコピーし、前記第1セクションのデータを消去して未書き込み状態にして循環的に使用される

請求項1から請求項5のいずれかに記載の半導体集積装置。 - 前記複数のセクションの各々は、ヘッダ情報を備え、

ヘッダ情報に含まれる複数のフラグは、それぞれ異なるワード線で指示されるアドレス位置に格納される

請求項6に記載の半導体集積回路装置。 - フラッシュメモリと、前記フラッシュメモリに対する書き換え制御と、読み出し制御とを行うフラッシュ制御部と、前記フラッシュメモリの書き換え動作の後にベリファイ動作を前記フラッシュ制御部に指示するプロセッサ部とを具備する半導体集積回路装置のメモリ制御方法であって、

前記書き換え動作は前記フラッシュメモリの所定の領域を未書き込み状態にする消去動作を含み、

前記フラッシュメモリにデータを書き込んだ後の前記ベリファイ動作において不良を検出すると以降の前記フラッシュメモリの使用を停止するノーマルモード動作ステップと、

前記フラッシュメモリにデータを書き込んだ後の前記ベリファイ動作において不良を検出するとエラー訂正して前記フラッシュメモリの使用を継続するフェイルセーフモード動作ステップと、

前記ノーマルモード動作ステップの前記消去動作後の前記ベリファイ動作において不良を検出すると、前記フェイルセーフモードに移行する移行ステップと

を具備する

メモリ制御方法。 - 前記書き換え動作は、

書き込むデータとともに前記書き込むデータに基づいて生成される誤り訂正符号とを前記フラッシュメモリに書き込むデータ書き込みステップと、

前記フラッシュメモリの所定の領域のデータを消去して未書き込みの状態にする消去ステップと

を備え、

前記ベリファイ動作は、

前記データ書き込みステップにより書き込まれたデータを前記誤り訂正符号に基づく誤り訂正を行わずにベリファイするデータ書き込みベリファイステップと、

前記データ書き込みステップにより書き込まれたデータを前記誤り訂正符号に基づいて誤り訂正を行ってベリファイするECCベリファイステップと、

前記消去ステップにより消去された領域の消去状態を確認する消去ベリファイステップと

を備え、

前記ノーマルモード動作ステップは、前記データ書き込みステップにより書き込まれたデータを前記データ書き込みベリファイステップによりベリファイするデータ書き込みを所定の回数まで再試行可能とし、前記データ書き込みの再試行が所定の回数を超えると、書き込み不良として以降の前記フラッシュメモリの使用を停止する書き込み再試行ステップを備え、

前記フェイルセーフモード動作ステップは、前記データ書き込みステップにより書き込まれたデータを前記データ書き込みベリファイステップによりベリファイするデータ書き込みを所定の回数まで再試行可能とし、前記データ書き込みの再試行が所定の回数を超えると、前記データ書き込みステップにより書き込まれたデータを前記ECCベリファイステップによりベリファイするデータ書き込みを所定の回数まで再試行可能とするECC再試行ステップを備える

請求項8に記載のメモリ制御方法。 - 前記フラッシュメモリは、代替用ブロックを備え、

前記消去動作後の前記ベリファイ動作において不良を検出すると、前記不良が検出された前記フラッシュメモリのブロックに代えて前記代替用ブロックを自動的にアクセスするように、アクセスアドレスを変換するアドレス変換ステップを具備する

請求項8または請求項9に記載のメモリ制御方法。 - 前記フラッシュメモリは、所定の領域がエクストラ領域として確保され、

前記不良が検出されたときに前記フラッシュメモリのブロックを示すリダンダンシ情報を前記エクストラ領域に格納するリダンダンシ情報格納ステップと、

前記エクストラ領域から読み出した前記リダンダンシ情報に基づいて、前記アクセスアドレスを変換するステップと

をさらに具備する

請求項10に記載のメモリ制御方法。 - 前記プロセッサ部の初期設定が終了する前に前記エクストラ領域に格納されている前記リダンダンシ情報を読み出してレジスタに格納するリセット制御ステップを備える

請求項11に記載のメモリ制御方法。 - 前記フラッシュメモリに含まれる複数のセクションのうちの第1セクション内にデータを書き込める領域が所定の閾値以下になると、前記第1セクション内の有効データを前記複数のセクションのうちの第2セクションにコピーする有効データコピーステップと、

前記第1セクションのデータを消去して未書き込み状態にするセクション消去ステップと

を具備し、前記フラッシュメモリを循環的に使用する

請求項8から請求項12のいずれかに記載のメモリ制御方法。 - 前記複数のセクションの各々は、ヘッダ情報を備え、

ヘッダ情報に含まれる複数のフラグは、それぞれ異なるワード線で指示されるアドレス位置に格納される

請求項13に記載のメモリ制御方法。 - フラッシュメモリと、前記フラッシュメモリに対する書き換え制御と、読み出し制御とを行うフラッシュ制御部と、前記フラッシュメモリの書き換え動作の後にベリファイ動作を前記フラッシュ制御部に指示するプロセッサ部とを具備する半導体集積回路装置のプロセッサ部に前記フラッシュメモリの制御を実行させるプログラムであって、

前記フラッシュメモリにデータを書き込む第1データ書き込み手順と、

前記フラッシュメモリに書き込まれたデータをベリファイする第1データベリファイ手順と、

前記フラッシュメモリの所定の領域を未書き込み状態にする第1データ消去手順と、

前記未書き込み状態をベリファイする第1消去ベリファイ手順と

を備え、

前記第1データベリファイ手順で不良を検出すると以降の前記フラッシュメモリの使用を停止するノーマルモード動作手順と、

前記フラッシュメモリにデータを書き込む第2データ書き込み手順と、

前記フラッシュメモリに書き込まれたデータをベリファイする第2データベリファイ手順と、

前記フラッシュメモリの所定の領域を未書き込み状態にする第2データ消去手順と、

前記未書き込み状態をベリファイする第2消去ベリファイ手順と

を備え、

前記第2データベリファイ手順で不良を検出するとエラー訂正して前記フラッシュメモリの使用を継続するフェイルセーフモード手順と

を具備し、

前記第1消去ベリファイ手順において不良を検出すると、前記フェイルセーフモード手順に移行する手順をプロセッサ部に実行させるためのメモリ制御プログラム。 - 前記第2データベリファイ手順は、誤り訂正符号に基づいて誤り訂正されたデータをベリファイする手順を備える

請求項15に記載のメモリ制御プログラム。 - 前記フラッシュメモリは、代替用ブロックを備え、

前記第1および第2消去ベリファイ手順において不良を検出すると、前記不良が検出された前記フラッシュメモリのブロックに代えて前記代替用ブロックを自動的にアクセスするように、アクセスアドレスの変換を前記フラッシュ制御部に指示する手順をさらに具備する

請求項15または請求項16に記載のメモリ制御プログラム。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007135791A JP4994112B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体集積回路装置およびメモリ制御方法 |

| US12/149,915 US8055957B2 (en) | 2007-05-22 | 2008-05-09 | Semiconductor integrated circuit device having fail-safe mode and memory control method |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007135791A JP4994112B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体集積回路装置およびメモリ制御方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008293555A JP2008293555A (ja) | 2008-12-04 |

| JP4994112B2 true JP4994112B2 (ja) | 2012-08-08 |

Family

ID=40073513

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007135791A Expired - Fee Related JP4994112B2 (ja) | 2007-05-22 | 2007-05-22 | 半導体集積回路装置およびメモリ制御方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8055957B2 (ja) |

| JP (1) | JP4994112B2 (ja) |

Families Citing this family (73)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8706950B2 (en) | 2008-03-01 | 2014-04-22 | Kabushiki Kaisha Toshiba | Memory system |

| JP2010026896A (ja) * | 2008-07-23 | 2010-02-04 | Nec Electronics Corp | メモリシステム、及び、メモリエラー要因特定方法 |

| US7925939B2 (en) * | 2008-09-26 | 2011-04-12 | Macronix International Co., Ltd | Pre-code device, and pre-code system and pre-coding method thererof |

| JP2011002945A (ja) * | 2009-06-17 | 2011-01-06 | Renesas Electronics Corp | 半導体装置 |

| JP2011070346A (ja) * | 2009-09-25 | 2011-04-07 | Toshiba Corp | メモリシステム |

| JP2011198433A (ja) * | 2010-03-23 | 2011-10-06 | Toshiba Corp | メモリシステム |

| JP5815212B2 (ja) | 2010-04-19 | 2015-11-17 | スパンション エルエルシー | データ書き込み方法およびシステム |

| KR101254875B1 (ko) * | 2011-05-18 | 2013-04-15 | 삼성에스디아이 주식회사 | 배터리 팩 관리시스템 |

| JP2013068105A (ja) * | 2011-09-21 | 2013-04-18 | Hitachi Automotive Systems Ltd | 自動車用電子制御装置 |

| US8880964B2 (en) | 2012-09-19 | 2014-11-04 | Sandisk Technologies Inc. | Block and page level bad bit line and bits screening methods for program algorithm |

| US9063851B2 (en) * | 2012-11-07 | 2015-06-23 | Infineon Technologies Ag | Fail safe code functionality |

| JP2015038796A (ja) * | 2013-08-19 | 2015-02-26 | 株式会社東芝 | メモリシステムおよび制御方法 |

| US9417957B2 (en) * | 2013-10-04 | 2016-08-16 | Infineon Technologies Ag | Method of detecting bit errors, an electronic circuit for detecting bit errors, and a data storage device |

| KR20160109207A (ko) | 2015-03-10 | 2016-09-21 | 삼성전자주식회사 | 메모리의 초기화 및 펌 웨어의 업데이트를 위한 방법 및 전자 장치 |

| US10163479B2 (en) | 2015-08-14 | 2018-12-25 | Spin Transfer Technologies, Inc. | Method and apparatus for bipolar memory write-verify |

| JP6527054B2 (ja) * | 2015-08-28 | 2019-06-05 | 東芝メモリ株式会社 | メモリシステム |

| JP6115740B1 (ja) * | 2015-12-17 | 2017-04-19 | ウィンボンド エレクトロニクス コーポレーション | 半導体記憶装置 |

| US9904595B1 (en) * | 2016-08-23 | 2018-02-27 | Texas Instruments Incorporated | Error correction hardware with fault detection |

| US10437491B2 (en) | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of processing incomplete memory operations in a memory device during a power up sequence and a power down sequence using a dynamic redundancy register |

| US11151042B2 (en) | 2016-09-27 | 2021-10-19 | Integrated Silicon Solution, (Cayman) Inc. | Error cache segmentation for power reduction |

| US10628316B2 (en) * | 2016-09-27 | 2020-04-21 | Spin Memory, Inc. | Memory device with a plurality of memory banks where each memory bank is associated with a corresponding memory instruction pipeline and a dynamic redundancy register |

| US10437723B2 (en) * | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of flushing the contents of a dynamic redundancy register to a secure storage area during a power down in a memory device |

| US10192601B2 (en) | 2016-09-27 | 2019-01-29 | Spin Transfer Technologies, Inc. | Memory instruction pipeline with an additional write stage in a memory device that uses dynamic redundancy registers |

| US10546625B2 (en) | 2016-09-27 | 2020-01-28 | Spin Memory, Inc. | Method of optimizing write voltage based on error buffer occupancy |

| US11386010B2 (en) | 2016-09-27 | 2022-07-12 | Integrated Silicon Solution, (Cayman) Inc. | Circuit engine for managing memory meta-stability |

| US11048633B2 (en) * | 2016-09-27 | 2021-06-29 | Spin Memory, Inc. | Determining an inactive memory bank during an idle memory cycle to prevent error cache overflow |

| US10818331B2 (en) | 2016-09-27 | 2020-10-27 | Spin Memory, Inc. | Multi-chip module for MRAM devices with levels of dynamic redundancy registers |

| US10366774B2 (en) * | 2016-09-27 | 2019-07-30 | Spin Memory, Inc. | Device with dynamic redundancy registers |

| US10446210B2 (en) | 2016-09-27 | 2019-10-15 | Spin Memory, Inc. | Memory instruction pipeline with a pre-read stage for a write operation for reducing power consumption in a memory device that uses dynamic redundancy registers |

| US10460781B2 (en) | 2016-09-27 | 2019-10-29 | Spin Memory, Inc. | Memory device with a dual Y-multiplexer structure for performing two simultaneous operations on the same row of a memory bank |

| US10360964B2 (en) * | 2016-09-27 | 2019-07-23 | Spin Memory, Inc. | Method of writing contents in memory during a power up sequence using a dynamic redundancy register in a memory device |

| US11119936B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Error cache system with coarse and fine segments for power optimization |

| US10192602B2 (en) | 2016-09-27 | 2019-01-29 | Spin Transfer Technologies, Inc. | Smart cache design to prevent overflow for a memory device with a dynamic redundancy register |

| US11119910B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Heuristics for selecting subsegments for entry in and entry out operations in an error cache system with coarse and fine grain segments |

| US10481976B2 (en) | 2017-10-24 | 2019-11-19 | Spin Memory, Inc. | Forcing bits as bad to widen the window between the distributions of acceptable high and low resistive bits thereby lowering the margin and increasing the speed of the sense amplifiers |

| US10489245B2 (en) | 2017-10-24 | 2019-11-26 | Spin Memory, Inc. | Forcing stuck bits, waterfall bits, shunt bits and low TMR bits to short during testing and using on-the-fly bit failure detection and bit redundancy remapping techniques to correct them |

| US10529439B2 (en) | 2017-10-24 | 2020-01-07 | Spin Memory, Inc. | On-the-fly bit failure detection and bit redundancy remapping techniques to correct for fixed bit defects |

| US10656994B2 (en) | 2017-10-24 | 2020-05-19 | Spin Memory, Inc. | Over-voltage write operation of tunnel magnet-resistance (“TMR”) memory device and correcting failure bits therefrom by using on-the-fly bit failure detection and bit redundancy remapping techniques |

| WO2019133293A1 (en) * | 2017-12-27 | 2019-07-04 | Spin Transfer Technologies, Inc. | A memory device with a plurality of memory banks where each memory bank is associated with a corresponding memory instruction pipeline and a dynamic redundancy register |

| WO2019133223A1 (en) * | 2017-12-27 | 2019-07-04 | Spin Transfer Technologies, Inc. | A method of flushing the contents of a dynamic redundancy register to a secure storage area during a power down in a memory device |

| US10424726B2 (en) | 2017-12-28 | 2019-09-24 | Spin Memory, Inc. | Process for improving photoresist pillar adhesion during MRAM fabrication |

| US10395711B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Perpendicular source and bit lines for an MRAM array |

| US10360962B1 (en) | 2017-12-28 | 2019-07-23 | Spin Memory, Inc. | Memory array with individually trimmable sense amplifiers |

| US10891997B2 (en) | 2017-12-28 | 2021-01-12 | Spin Memory, Inc. | Memory array with horizontal source line and a virtual source line |

| US10811594B2 (en) | 2017-12-28 | 2020-10-20 | Spin Memory, Inc. | Process for hard mask development for MRAM pillar formation using photolithography |

| US10395712B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Memory array with horizontal source line and sacrificial bitline per virtual source |

| US10784439B2 (en) | 2017-12-29 | 2020-09-22 | Spin Memory, Inc. | Precessional spin current magnetic tunnel junction devices and methods of manufacture |

| US10840439B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Magnetic tunnel junction (MTJ) fabrication methods and systems |

| US10424723B2 (en) | 2017-12-29 | 2019-09-24 | Spin Memory, Inc. | Magnetic tunnel junction devices including an optimization layer |

| US10886330B2 (en) | 2017-12-29 | 2021-01-05 | Spin Memory, Inc. | Memory device having overlapping magnetic tunnel junctions in compliance with a reference pitch |

| US10367139B2 (en) | 2017-12-29 | 2019-07-30 | Spin Memory, Inc. | Methods of manufacturing magnetic tunnel junction devices |

| US10840436B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Perpendicular magnetic anisotropy interface tunnel junction devices and methods of manufacture |

| US10546624B2 (en) | 2017-12-29 | 2020-01-28 | Spin Memory, Inc. | Multi-port random access memory |

| US10438996B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Methods of fabricating magnetic tunnel junctions integrated with selectors |

| US10438995B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Devices including magnetic tunnel junctions integrated with selectors |

| US10446744B2 (en) | 2018-03-08 | 2019-10-15 | Spin Memory, Inc. | Magnetic tunnel junction wafer adaptor used in magnetic annealing furnace and method of using the same |

| US11107974B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Magnetic tunnel junction devices including a free magnetic trench layer and a planar reference magnetic layer |

| US11107978B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Methods of manufacturing three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US20190296223A1 (en) | 2018-03-23 | 2019-09-26 | Spin Memory, Inc. | Methods of Manufacturing Three-Dimensional Arrays with Magnetic Tunnel Junction Devices Including an Annular Free Magnetic Layer and a Planar Reference Magnetic Layer |

| US10784437B2 (en) | 2018-03-23 | 2020-09-22 | Spin Memory, Inc. | Three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US10411185B1 (en) | 2018-05-30 | 2019-09-10 | Spin Memory, Inc. | Process for creating a high density magnetic tunnel junction array test platform |

| US10559338B2 (en) | 2018-07-06 | 2020-02-11 | Spin Memory, Inc. | Multi-bit cell read-out techniques |

| US10600478B2 (en) | 2018-07-06 | 2020-03-24 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10692569B2 (en) | 2018-07-06 | 2020-06-23 | Spin Memory, Inc. | Read-out techniques for multi-bit cells |

| US10593396B2 (en) | 2018-07-06 | 2020-03-17 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10650875B2 (en) | 2018-08-21 | 2020-05-12 | Spin Memory, Inc. | System for a wide temperature range nonvolatile memory |

| US10699761B2 (en) | 2018-09-18 | 2020-06-30 | Spin Memory, Inc. | Word line decoder memory architecture |

| US11621293B2 (en) | 2018-10-01 | 2023-04-04 | Integrated Silicon Solution, (Cayman) Inc. | Multi terminal device stack systems and methods |

| US10971680B2 (en) | 2018-10-01 | 2021-04-06 | Spin Memory, Inc. | Multi terminal device stack formation methods |

| US11107979B2 (en) | 2018-12-28 | 2021-08-31 | Spin Memory, Inc. | Patterned silicide structures and methods of manufacture |

| WO2021072370A1 (en) * | 2019-10-10 | 2021-04-15 | Spin Memory, Inc. | Error cache system with coarse and fine segments for power optimization |

| JP7161583B1 (ja) | 2021-06-29 | 2022-10-26 | ウィンボンド エレクトロニクス コーポレーション | 半導体装置 |

| US12094549B2 (en) * | 2021-09-01 | 2024-09-17 | Micron Technology, Inc. | Defect detection during erase operations |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3941149B2 (ja) * | 1996-12-03 | 2007-07-04 | ソニー株式会社 | 半導体不揮発性記憶装置 |

| JPH09204367A (ja) * | 1996-01-25 | 1997-08-05 | Mitsubishi Electric Corp | フラッシュディスクカードにおけるフラッシュメモリデータのリフレッシュ方法 |

| US5978952A (en) * | 1996-12-31 | 1999-11-02 | Intel Corporation | Time-distributed ECC scrubbing to correct memory errors |

| JP2000173289A (ja) * | 1998-12-10 | 2000-06-23 | Toshiba Corp | エラー訂正可能なフラッシュメモリシステム |

| US6407944B1 (en) * | 1998-12-29 | 2002-06-18 | Samsung Electronics Co., Ltd. | Method for protecting an over-erasure of redundant memory cells during test for high-density nonvolatile memory semiconductor devices |

| US6587384B2 (en) * | 2001-04-21 | 2003-07-01 | Hewlett-Packard Development Company, L.P. | Multi-function serial I/O circuit |

| JP4059472B2 (ja) * | 2001-08-09 | 2008-03-12 | 株式会社ルネサステクノロジ | メモリカード及びメモリコントローラ |

| US7320100B2 (en) * | 2003-05-20 | 2008-01-15 | Cray Inc. | Apparatus and method for memory with bit swapping on the fly and testing |

| US7012835B2 (en) * | 2003-10-03 | 2006-03-14 | Sandisk Corporation | Flash memory data correction and scrub techniques |

| JP2005332436A (ja) * | 2004-05-18 | 2005-12-02 | Toshiba Corp | 半導体装置及びそのテスト方法 |

| US7009889B2 (en) * | 2004-05-28 | 2006-03-07 | Sandisk Corporation | Comprehensive erase verification for non-volatile memory |

| JP2006048783A (ja) * | 2004-08-02 | 2006-02-16 | Renesas Technology Corp | 不揮発性メモリおよびメモリカード |

| KR100622349B1 (ko) | 2004-08-04 | 2006-09-14 | 삼성전자주식회사 | 불량 블록 관리 기능을 가지는 플레시 메모리 장치 및플레시 메모리 장치의 불량 블록 관리 방법. |

| JP4261461B2 (ja) * | 2004-11-05 | 2009-04-30 | 株式会社東芝 | 半導体集積回路装置、及びそれを用いた不揮発性メモリシステム |

| US7158416B2 (en) * | 2005-03-15 | 2007-01-02 | Infineon Technologies Flash Gmbh & Co. Kg | Method for operating a flash memory device |

| US8291295B2 (en) * | 2005-09-26 | 2012-10-16 | Sandisk Il Ltd. | NAND flash memory controller exporting a NAND interface |

| US8245087B2 (en) * | 2007-03-26 | 2012-08-14 | Cray Inc. | Multi-bit memory error management |

| US8065573B2 (en) * | 2007-03-26 | 2011-11-22 | Cray Inc. | Method and apparatus for tracking, reporting and correcting single-bit memory errors |

| US7573773B2 (en) * | 2007-03-28 | 2009-08-11 | Sandisk Corporation | Flash memory with data refresh triggered by controlled scrub data reads |

-

2007

- 2007-05-22 JP JP2007135791A patent/JP4994112B2/ja not_active Expired - Fee Related

-

2008

- 2008-05-09 US US12/149,915 patent/US8055957B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US8055957B2 (en) | 2011-11-08 |

| JP2008293555A (ja) | 2008-12-04 |

| US20080294938A1 (en) | 2008-11-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4994112B2 (ja) | 半導体集積回路装置およびメモリ制御方法 | |

| JP4059472B2 (ja) | メモリカード及びメモリコントローラ | |

| JP4722839B2 (ja) | メモリ制御回路、不揮発性記憶装置及びメモリ制御方法 | |

| US7290097B2 (en) | Nonvolatile memory | |

| TWI408688B (zh) | 用於快閃記憶體的資料寫入方法及其控制器與儲存系統 | |

| US8812776B2 (en) | Data writing method, and memory controller and memory storage device using the same | |

| TWI396202B (zh) | 錯誤校正控制器及其快閃記憶體晶片系統與錯誤校正方法 | |

| EP1607865B1 (en) | Data control unit capable of correcting boot errors, and corresponding method | |

| US8756398B2 (en) | Partitioning pages of an electronic memory | |

| JP2000173289A (ja) | エラー訂正可能なフラッシュメモリシステム | |

| JPH06274409A (ja) | 一括消去型不揮発性メモリ | |

| JP2012063882A (ja) | 記憶装置、電子機器及び誤りデータの訂正方法 | |

| TWI394170B (zh) | 連結表的回復方法 | |

| TWI591482B (zh) | 資料保護方法、記憶體控制電路單元及記憶體儲存裝置 | |

| US20090100290A1 (en) | Memory controller, nonvolatile memory device, nonvolatile memory system, and data writing method | |

| JP2010500699A (ja) | メモリデバイス内のセクタごとに許容できるビットエラー | |

| JP4775969B2 (ja) | 不揮発性記憶装置 | |

| US8607123B2 (en) | Control circuit capable of identifying error data in flash memory and storage system and method thereof | |

| JPH09198884A (ja) | フラッシュメモリ管理方法 | |

| JP4158526B2 (ja) | メモリカード及びメモリへのデータ書き込み方法 | |

| JP4357305B2 (ja) | 外部記憶装置 | |

| JP5099342B2 (ja) | Plc用の部品実装基板 | |

| JP2012252557A (ja) | メモリコントローラ | |

| JP2011018371A (ja) | メモリ記憶装置 | |

| CN113094307B (zh) | 映射信息管理方法、存储器存储装置及存储器控制器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100415 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120418 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120508 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150518 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4994112 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |