JP2011002945A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2011002945A JP2011002945A JP2009144500A JP2009144500A JP2011002945A JP 2011002945 A JP2011002945 A JP 2011002945A JP 2009144500 A JP2009144500 A JP 2009144500A JP 2009144500 A JP2009144500 A JP 2009144500A JP 2011002945 A JP2011002945 A JP 2011002945A

- Authority

- JP

- Japan

- Prior art keywords

- data

- flash memory

- eeprom

- voltage

- block

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/44—Arrangements for executing specific programs

- G06F9/455—Emulation; Interpretation; Software simulation, e.g. virtualisation or emulation of application or operating system execution engines

Abstract

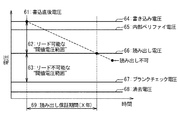

【解決手段】フラッシュメモリのEEPROM代替領域において、内部ベリファイ電圧と読み出し電圧との間にデータレベルチェック電圧を設定する。データレベルがデータレベルチェック電圧を下回った場合にブロックチェンジを行う。

【選択図】図7

Description

図7は、本発明の第1の実施形態による半導体装置の構成について説明するためのブロック図である。この半導体装置は、CPU71と、ファームウエア部72と、フラッシュメモリ部74とを具備する。ファームウエア部72は、データレベルチェックプログラム部73を具備する。フラッシュメモリ部74は、プログラム領域75と、EEPROMエミュレーション・ライブラリ76と、EEPROM代替領域78とを具備する。EEPROMエミュレーション・ライブラリ76は、データレベルチェックI/F(InterFace:インタフェース)77を具備する。

図13は、本発明の第2の実施形態における半導体装置の動作、すなわちEEPROMエミュレーション方法におけるデータレベルチェックおよびブロックチェンジについて説明するためのフローチャートである。図13(a)は、ユーザ・アプリケーションに基づくユーザ・システムについて説明するためのフローチャートである。図13(b)は、ブロックチェンジを伴うデータ保持期間スペック拡張機能について説明するためのフローチャートである。

11 フラッシュメモリ

12 CPU

13 ROM

20 半導体装置

21 CPU

22 フラッシュメモリ

23 プログラム領域

24 EEPROM代替領域

25 フラッシュコントローラ

26 RAM

27 周辺マクロ

30 フラッシュメモリ

31 データ長格納領域

32 データ格納領域

32a〜32g セクション

33 空き領域

41a、41b コントロールゲート

42a、42b 浮遊ゲート

43a、43b ソース

44a、44b ドレイン

51 コントロールゲート

52 ソース

53 ドレイン

54 電流

55 初期状態のグラフ

56 書き込み状態のグラフ

61、81 書き込み直後電圧

62、82 リード可能な閾値電圧範囲

63、83 リード不可能な閾値電圧範囲

64、84 書き込み電圧

65、85 内部ベリファイ電圧

66、86 読み出し電圧

67、87 ブランクチェック電圧

68、88 消去電圧

69、89 読み出し保証期間

71 CPU

72 ファームウエア

73 データレベルチェックプログラム

74 フラッシュメモリ

75 プログラム領域

76 EEPROMエミュレーション・ライブラリ

77 データレベルチェックI/F

78 EEPROM代替領域

80 データレベルチェック電圧

91a EEPROMエミュレーション・ライブラリ

92a 新規フラッシュアクセスI/F

93a データレベルチェックI/F

94a フラッシュメモリ操作I/F

95a 書き込みI/F

96a 消去I/F

97a 読み出しI/F

91b ファームウエア

92b 新規フラッシュアクセスプログラム

93b データレベルチェックプログラム

94b フラッシュメモリ操作プログラム

95b 書き込みプログラム

96b 消去プログラム

97b 読み出しプログラム

100 ユーザ・アプリケーション

101 EEPROMエミュレーション・ライブラリ

106 データレベルチェックI/F

108 フラッシュメモリ操作I/F

102 ファームウエア

107 データレベルチェックプログラム

109 フラッシュメモリ操作プログラム

103 フラッシュメモリ1(EEPROM代替領域)

104 フラッシュメモリ2(EEPROM代替領域)

105 フラッシュメモリ3(EEPROM代替領域)

120a〜122a、120b〜122b、120c〜122c ブロック

Claims (10)

- EEPROMエミュレーションを行うためのEEPROM代替領域を有するフラッシュメモリと、

CPUと、

前記EEPROM代替領域における任意のブロックに書き込まれたデータに対応する電圧レベルと、所定のデータレベルチェック電圧とを比較するためのデータレベルチェック回路と

を具備し、

前記CPUは、前記データに対応する電圧レベルが、前記データレベルチェック電圧を下回った場合に、前記データを前記任意のブロックから読み出して他のブロックに書き込むブロックチェンジを実行する

半導体装置。 - 請求項1に記載の半導体装置において、

前記CPUが、前記フラッシュメモリにおいて、データの書き込みおよび読出しをブロック単位で行うためのフラッシュメモリ操作プログラムと、前記CPUが、前記データレベルチェック回路を制御するためのデータレベルチェックプログラムとを有するファームウエア

をさらに具備し、

前記フラッシュメモリは、

前記CPUが実行するための所定のユーザ・アプリケーションを格納するプログラム領域と、

前記CPUが前記ファームウエアを呼び出してEEPROMエミュレーションを実行するためのEEPROMエミュレーション・ライブラリ

をさらに具備し、

前記ユーザ・アプリケーションは、前記フラッシュメモリ操作プログラムを呼び出して実行可能であり、

前記ユーザ・アプリケーションは、前記フラッシュメモリ操作プログラムとは独立した任意のタイミングで、前記ブロックチェンジを呼び出して実行可能である

半導体装置。 - 請求項2に記載の半導体装置において、

前記フラッシュメモリ操作プログラムは、

前記ブロックチェンジにおいて、前記データを前記任意のブロックから読み出した後、前記任意のブロックを消去するための消去プログラム

をさらに具備する

半導体装置。 - 請求項2または3に記載の半導体装置において、

前記データレベルチェックプログラムにおいて、前記任意のブロックに書き込まれたデータに対応する全てのビットについて、前記比較を行う

半導体装置。 - 請求項1〜4のいずれかに記載の半導体装置において、

前記フラッシュメモリは、

前記データに対応する電圧レベルが、前記フラッシュメモリに設定されたリード可能な閾値電圧範囲から外れていた場合に、前記データを書き換えるためのデフォルトデータ

をさらに具備する

半導体装置。 - (a)フラッシュメモリのEEPROM代替領域における任意のブロックに書き込まれたデータに対応する電圧レベルと、所定のデータレベルチェック電圧とを比較するステップと、

(b)前記データに対応する電圧レベルが、前記データレベルチェック電圧を下回った場合に、前記データを前記任意のブロックから読み出して他のブロックに書き込むブロックチェンジを実行するステップと

を具備する

EEPROMエミュレーション方法。 - 請求項6に記載のEEPROMエミュレーション方法において、

(c)所定のユーザ・アプリケーションを実行するステップ

をさらに具備し、

前記ステップ(c)は、

(c−1)前記EEPROM代替領域における任意のブロックにデータを書き込むステップと、

(c−2)前記任意のブロックに書き込まれた前記データを前記EEPROM代替領域から読み出すステップと、

(c−3)前記ステップ(c−1)および(c−2)とは独立した任意のタイミングにおいて、前記ステップ(a)を実行するステップ

を具備する

EEPROMエミュレーション方法。 - 請求項6または7に記載のEEPROMエミュレーション方法において、

前記ステップ(b)は、

(b−1)前記データを前記任意のブロックから読み出した後、前記任意のブロックを消去するステップ

を具備する

EEPROMエミュレーション方法。 - 請求項6〜8のいずれかに記載のEEPROMエミュレーション方法において、

前記ステップ(a)は、

(a−1)前記任意のブロックに書き込まれたデータに対応する全てのビットについて、前記比較を行うステップ

を具備する

EEPROMエミュレーション方法。 - 請求項6〜9のいずれかに記載のEEPROMエミュレーション方法において、

前記ステップ(b)は、

(b−2)前記データに対応する電圧レベルが、前記フラッシュメモリに設定されたリード可能な閾値電圧範囲から外れていた場合、前記データを所定のデフォルトデータに書き換えるステップ

を具備する

EEPROMエミュレーション方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009144500A JP2011002945A (ja) | 2009-06-17 | 2009-06-17 | 半導体装置 |

| US12/789,968 US8359427B2 (en) | 2009-06-17 | 2010-05-28 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009144500A JP2011002945A (ja) | 2009-06-17 | 2009-06-17 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2011002945A true JP2011002945A (ja) | 2011-01-06 |

| JP2011002945A5 JP2011002945A5 (ja) | 2012-03-29 |

Family

ID=43355283

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009144500A Pending JP2011002945A (ja) | 2009-06-17 | 2009-06-17 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8359427B2 (ja) |

| JP (1) | JP2011002945A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013029879A (ja) * | 2011-07-26 | 2013-02-07 | Denso Corp | フラッシュメモリの制御装置 |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20100250875A1 (en) * | 2009-03-25 | 2010-09-30 | Silicon Laboratories Inc. | Eeprom emulation using flash memory |

| US9406346B2 (en) | 2011-06-30 | 2016-08-02 | Sandisk Technologies Llc | Smart bridge for memory core |

| US9208070B2 (en) * | 2011-12-20 | 2015-12-08 | Sandisk Technologies Inc. | Wear leveling of multiple memory devices |

| US9378829B2 (en) * | 2013-02-07 | 2016-06-28 | Cypress Semiconductor Corporation | Non-volatile memory device with an EPLI comparator |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000228094A (ja) * | 1999-02-04 | 2000-08-15 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2005092659A (ja) * | 2003-09-19 | 2005-04-07 | Nec Electronics Corp | データ書込・読出制御装置、及びデータ書込・読出制御方法 |

| JP2006260468A (ja) * | 2005-03-18 | 2006-09-28 | Nec Electronics Corp | 半導体装置 |

| JP2008059745A (ja) * | 2006-09-01 | 2008-03-13 | Samsung Electronics Co Ltd | フラッシュメモリ装置及びメモリシステム |

| JP2008293555A (ja) * | 2007-05-22 | 2008-12-04 | Nec Electronics Corp | 半導体集積回路装置およびメモリ制御方法 |

Family Cites Families (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1909289A1 (en) * | 2005-06-28 | 2008-04-09 | Spansion LLC | Semiconductor device and control method thereof |

-

2009

- 2009-06-17 JP JP2009144500A patent/JP2011002945A/ja active Pending

-

2010

- 2010-05-28 US US12/789,968 patent/US8359427B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000228094A (ja) * | 1999-02-04 | 2000-08-15 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2005092659A (ja) * | 2003-09-19 | 2005-04-07 | Nec Electronics Corp | データ書込・読出制御装置、及びデータ書込・読出制御方法 |

| JP2006260468A (ja) * | 2005-03-18 | 2006-09-28 | Nec Electronics Corp | 半導体装置 |

| JP2008059745A (ja) * | 2006-09-01 | 2008-03-13 | Samsung Electronics Co Ltd | フラッシュメモリ装置及びメモリシステム |

| JP2008293555A (ja) * | 2007-05-22 | 2008-12-04 | Nec Electronics Corp | 半導体集積回路装置およびメモリ制御方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013029879A (ja) * | 2011-07-26 | 2013-02-07 | Denso Corp | フラッシュメモリの制御装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100325350A1 (en) | 2010-12-23 |

| US8359427B2 (en) | 2013-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7663933B2 (en) | Memory controller | |

| US7330995B2 (en) | Nonvolatile memory apparatus which prevents destruction of write data caused by power shutdown during a writing process | |

| KR101242293B1 (ko) | 불휘발성 메모리 제어 방법 및 반도체 장치 | |

| KR100926195B1 (ko) | 불휘발성 반도체 기억 장치 | |

| KR100645044B1 (ko) | 높은 신뢰도를 갖는 불 휘발성 메모리 장치의 프로그램 방법 | |

| US7463520B2 (en) | Memory device with variable trim settings | |

| US7719900B2 (en) | Semiconductor storage device having memory cell for storing data by using difference in threshold voltage | |

| US9019770B2 (en) | Data reading method, and control circuit, memory module and memory storage apparatus and memory module using the same | |

| US9852032B2 (en) | Data storage devices and data maintenance methods | |

| KR101468099B1 (ko) | 불휘발성 메모리 장치의 프로그램 방법 | |

| JP2009140564A (ja) | Nand型フラッシュメモリおよびメモリシステム | |

| TW201411351A (zh) | 迴避由突然斷電所造成之損壞資料頁與損壞區塊的方法 | |

| JP2011002945A (ja) | 半導体装置 | |

| KR20090021508A (ko) | 멀티-비트 및 싱글-비트 방식으로 데이터를 저장하는플래시 메모리 장치 및 그것의 프로그램 방법 | |

| CN108877863B (zh) | 快闪存储器存储装置及其操作方法 | |

| US20100046293A1 (en) | Memory cell block of nonvolatile memory device and method of managing supplementary information | |

| JP5280027B2 (ja) | 半導体装置及びその制御方法 | |

| JP4433792B2 (ja) | メモリコントローラ及びメモリコントローラを備えるフラッシュメモリシステム、並びに、フラッシュメモリの制御方法 | |

| JP4818453B1 (ja) | 電子機器およびデータ読み出し方法 | |

| JP2012155788A (ja) | Nand型フラッシュメモリ | |

| JP2010079686A (ja) | データ処理装置、メモリ制御回路およびメモリ制御方法 | |

| JP2004030849A (ja) | データの一部書き換え機能を有する半導体不揮発性メモリ | |

| US20100332736A1 (en) | Method of operating nonvolatile memory device | |

| US20060155916A1 (en) | Writing uncorrupted data to electronic memory | |

| JP2008103076A (ja) | データの一部書き換え機能を有する半導体不揮発性メモリ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120214 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120214 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130523 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130618 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20140324 |