JP4851255B2 - 表示装置 - Google Patents

表示装置 Download PDFInfo

- Publication number

- JP4851255B2 JP4851255B2 JP2006193987A JP2006193987A JP4851255B2 JP 4851255 B2 JP4851255 B2 JP 4851255B2 JP 2006193987 A JP2006193987 A JP 2006193987A JP 2006193987 A JP2006193987 A JP 2006193987A JP 4851255 B2 JP4851255 B2 JP 4851255B2

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- wiring

- semiconductor chip

- bump electrode

- insulating film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Description

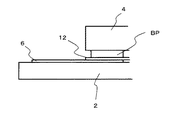

前記基板の前記周辺部に搭載された半導体チップとを有する表示装置であって、

前記半導体チップは、第1のバンプ電極を有し、

前記基板は、表示領域の配線に接続された第1の配線と、前記第1の配線に隣接して配置され表示領域の別の配線に接続された第2の配線と、前記第1の配線と前記第2の配線とを被う絶縁膜と、前記絶縁膜に形成された第1のコンタクト孔と、前記絶縁膜より上層に形成され前記第1のコンタクト孔を介して前記第1の配線と接続された第1の端子とを有し、

前記第1のバンプ電極は、前記第1の端子と接続されており、

前記第2の配線は、前記第1の端子と電気的に絶縁されており、

平面的に見た場合に、前記第1の端子は、前記絶縁膜を介して前記第2の配線と重畳して配置されている。

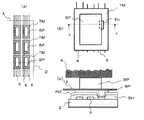

前記基板の前記周辺部に搭載された半導体チップとを有する表示装置であって、

前記半導体チップは、第1のバンプ電極を有し、

前記基板は、表示領域の配線に接続された第1の配線と、前記第1の配線に隣接して配置され表示領域の別の配線に接続された第2の配線と、前記第1の配線と前記第2の配線とを被う絶縁膜と、前記絶縁膜に形成された第1のコンタクト孔と、前記絶縁膜より上層に形成され前記第1のコンタクト孔を介して前記第1の配線と接続された第1の端子とを有し、

前記第1のバンプ電極は、前記第1の端子と接続されており、

前記第2の配線は、前記第1の端子と電気的に絶縁されており、

平面的に見た場合に、前記第1のバンプ電極は、前記絶縁膜を介して前記第2の配線と重畳して配置されている。

前記絶縁膜は、前記薄膜トランジスタのゲート絶縁膜と同材料からなる絶縁膜を含む構成としても良い。

前記基板は、前記絶縁膜より上層に形成され前記第2のバンプ電極に接続される第2の端子を有し、

前記第1の端子と前記表示部との間の距離は、前記第2の端子と前記表示部との間の距離と異なっており、

平面的に見た場合に、前記第1の端子に重畳する前記基板の配線の本数が、前記第2の端子に重畳する前記基板の配線の本数と等しい構成としても良い。

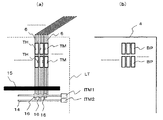

前記第1の検査端子は、前記第1のスイッチング素子を介して前記第1の配線に接続されている構成としても良い。

前記基板は、前記絶縁膜に形成された第2のコンタクト孔と、前記絶縁膜より上層に形成され前記第2のコンタクト孔を介して前記第2の配線と接続された第2の端子とを有し、

前記第2のバンプ電極は、前記第2の端子と接続されており、

前記第1の配線は、前記第2の端子と電気的に絶縁されており、

平面的に見た場合に、前記第2の端子は、前記第1の配線と重畳して配置されている構成としても良い。

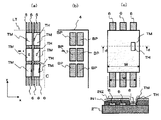

前記複数のバンプ電極は、前記半導体チップの短辺方向に2段以上に配置されており、

前記複数のバンプ電極は、第1段目のバンプ電極の前記半導体チップの長辺方向の位置が、第2段目のバンプ電極の前記半導体チップの前記長辺方向の位置に対して、シフトしていない構成としても良い。

前記複数のバンプ電極は、前記半導体チップの短辺方向に2段以上に配置されており、

前記複数のバンプ電極は、第1段目のバンプ電極の前記半導体チップの長辺方向の位置が、第2段目のバンプ電極の前記半導体チップの前記長辺方向の位置に対して、シフトしている構成としても良い。

Claims (12)

- 表示部と周辺部とを有する基板と、

前記基板の前記周辺部に搭載された半導体チップとを有する表示装置であって、

前記半導体チップは、第1のバンプ電極を有し、

前記基板は、表示領域の配線に接続された第1の配線と、前記第1の配線に隣接して配置され表示領域の別の配線に接続された第2の配線と、前記第1の配線と前記第2の配線とを被う絶縁膜と、前記絶縁膜に形成された第1のコンタクト孔と、前記絶縁膜より上層に形成され前記第1のコンタクト孔を介して前記第1の配線と接続された第1の端子とを有し、

前記第1のバンプ電極は、前記第1の端子と接続されており、

前記第2の配線は、前記第1の端子と電気的に絶縁されており、

平面的に見た場合に、前記第1の端子は、前記絶縁膜を介して前記第2の配線と重畳して配置されていることを特徴とする表示装置。 - 平面的に見た場合に、前記第1のバンプ電極は、前記絶縁膜を介して前記第2の配線と重畳して配置されていることを特徴とする請求項1に記載の表示装置。

- 表示部と周辺部とを有する基板と、

前記基板の前記周辺部に搭載された半導体チップとを有する表示装置であって、

前記半導体チップは、第1のバンプ電極を有し、

前記基板は、表示領域の配線に接続された第1の配線と、前記第1の配線に隣接して配置され表示領域の別の配線に接続された第2の配線と、前記第1の配線と前記第2の配線とを被う絶縁膜と、前記絶縁膜に形成された第1のコンタクト孔と、前記絶縁膜より上層に形成され前記第1のコンタクト孔を介して前記第1の配線と接続された第1の端子とを有し、

前記第1のバンプ電極は、前記第1の端子と接続されており、

前記第2の配線は、前記第1の端子と電気的に絶縁されており、

平面的に見た場合に、前記第1のバンプ電極は、前記絶縁膜を介して前記第2の配線と重畳して配置されていることを特徴とする表示装置。 - 前記絶縁膜は、2層以上の絶縁膜で構成されていることを特徴とする請求項1から3のいずれかに記載の表示装置。

- 前記基板は、薄膜トランジスタを有し、

前記絶縁膜は、前記薄膜トランジスタのゲート絶縁膜と同材料からなる絶縁膜を含むことを特徴とする請求項1から4のいずれかに記載の表示装置。 - 前記端子は、少なくともその表面がITO(Indium Tin Oxide)で形成されていることを特徴とする請求項1から5のいずれかに記載の表示装置。

- 前記半導体チップは、第2のバンプ電極を有し、

前記基板は、前記絶縁膜より上層に形成され前記第2のバンプ電極に接続される第2の端子を有し、

前記第1の端子と前記表示部との間の距離は、前記第2の端子と前記表示部との間の距離と異なっており、

平面的に見た場合に、前記第1の端子に重畳する前記基板の配線の本数が、前記第2の端子に重畳する前記基板の配線の本数と等しいことを特徴とする請求項1から6のいずれかに記載の表示装置。 - 前記基板の前記周辺部は、第1の検査端子と、第1のスイッチング素子とを有し、

前記第1の検査端子は、前記第1のスイッチング素子を介して前記第1の配線に接続されていることを特徴とする請求項1から7のいずれかに記載の表示装置。 - 前記半導体チップは、第2のバンプ電極を有し、

前記基板は、前記絶縁膜に形成された第2のコンタクト孔と、前記絶縁膜より上層に形成され前記第2のコンタクト孔を介して前記第2の配線と接続された第2の端子とを有し、

前記第2のバンプ電極は、前記第2の端子と接続されており、

前記第1の配線は、前記第2の端子と電気的に絶縁されており、

平面的に見た場合に、前記第2の端子は、前記第1の配線と重畳して配置されていることを特徴とする請求項1から8のいずれかに記載の表示装置。 - 前記半導体チップは、前記半導体チップの1つの長辺に、前記第1のバンプ電極を含む複数のバンプ電極を有し、

前記複数のバンプ電極は、前記半導体チップの短辺方向に2段以上に配置されており、

前記複数のバンプ電極は、第1段目のバンプ電極の前記半導体チップの長辺方向の位置が、第2段目のバンプ電極の前記半導体チップの前記長辺方向の位置に対して、シフトしていないことを特徴とする請求項1から9のいずれかに記載の表示装置。 - 前記半導体チップは、前記半導体チップの1つの長辺に、前記第1のバンプ電極を含む複数のバンプ電極を有し、

前記複数のバンプ電極は、前記半導体チップの短辺方向に2段以上に配置されており、

前記複数のバンプ電極は、第1段目のバンプ電極の前記半導体チップの長辺方向の位置が、第2段目のバンプ電極の前記半導体チップの前記長辺方向の位置に対して、シフトしていることを特徴とする請求項1から9のいずれかに記載の表示装置。 - 前記基板に対向して配置された対向基板と、前記基板と前記対向基板との間に挟持された液晶とを有することを特徴とする請求項1から11のいずれかに記載の表示装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006193987A JP4851255B2 (ja) | 2006-07-14 | 2006-07-14 | 表示装置 |

| US11/772,274 US7965368B2 (en) | 2006-07-14 | 2007-07-02 | Display device comprising a semiconductor chip including a first terminal which overlaps a first and second line, the first terminal connected to the first line and overlapping and insulated from the second line |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006193987A JP4851255B2 (ja) | 2006-07-14 | 2006-07-14 | 表示装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008020791A JP2008020791A (ja) | 2008-01-31 |

| JP2008020791A5 JP2008020791A5 (ja) | 2009-07-23 |

| JP4851255B2 true JP4851255B2 (ja) | 2012-01-11 |

Family

ID=39076741

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006193987A Active JP4851255B2 (ja) | 2006-07-14 | 2006-07-14 | 表示装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7965368B2 (ja) |

| JP (1) | JP4851255B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4448535B2 (ja) | 2007-12-18 | 2010-04-14 | 株式会社 日立ディスプレイズ | 表示装置 |

| US8629965B2 (en) | 2009-06-17 | 2014-01-14 | Hitachi Displays, Ltd. | Display device |

| JP5220692B2 (ja) * | 2009-06-17 | 2013-06-26 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| JP5730062B2 (ja) * | 2011-02-21 | 2015-06-03 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN102682664A (zh) * | 2012-05-30 | 2012-09-19 | 深圳市华星光电技术有限公司 | 一种走线结构及显示面板 |

| JP2016057616A (ja) * | 2014-09-05 | 2016-04-21 | 株式会社半導体エネルギー研究所 | 表示パネル、入出力装置、情報処理装置 |

| KR20210036437A (ko) * | 2019-09-25 | 2021-04-05 | 삼성디스플레이 주식회사 | 표시장치 및 이의 제조 방법 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| TW340192B (en) * | 1993-12-07 | 1998-09-11 | Sharp Kk | A display board having wiring with three-layered structure and a display device including the display board |

| JPH08179351A (ja) * | 1994-12-22 | 1996-07-12 | Toshiba Corp | 表示装置用アレイ基板 |

| JPH08313925A (ja) | 1995-05-18 | 1996-11-29 | Citizen Watch Co Ltd | 半導体集積回路 |

| JP3826605B2 (ja) * | 1999-03-08 | 2006-09-27 | セイコーエプソン株式会社 | 半導体装置の実装構造の製造方法、液晶装置、および電子機器 |

| KR100390456B1 (ko) * | 2000-12-13 | 2003-07-07 | 엘지.필립스 엘시디 주식회사 | 액정 디스플레이 패널 및 그 제조방법 |

| JP4006304B2 (ja) * | 2002-09-10 | 2007-11-14 | 株式会社 日立ディスプレイズ | 画像表示装置 |

| JP2005062582A (ja) * | 2003-08-18 | 2005-03-10 | Hitachi Displays Ltd | 表示装置 |

| KR101034181B1 (ko) * | 2003-08-21 | 2011-05-12 | 엘지디스플레이 주식회사 | 액정표시장치용 어레이기판 제조방법 |

| JP2005099310A (ja) | 2003-09-24 | 2005-04-14 | Seiko Epson Corp | 実装構造体、ic、電気光学装置および電子機器 |

| JP4257526B2 (ja) * | 2004-06-01 | 2009-04-22 | セイコーエプソン株式会社 | 半導体装置 |

| JP4202300B2 (ja) * | 2004-06-24 | 2008-12-24 | 三菱電機株式会社 | 液晶表示装置及び液晶表示装置の検査方法 |

-

2006

- 2006-07-14 JP JP2006193987A patent/JP4851255B2/ja active Active

-

2007

- 2007-07-02 US US11/772,274 patent/US7965368B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008020791A (ja) | 2008-01-31 |

| US7965368B2 (en) | 2011-06-21 |

| US20080049171A1 (en) | 2008-02-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10312263B2 (en) | Display panel and manufacturing method thereof | |

| KR102059785B1 (ko) | 네로우 베젤 타입 액정표시장치용 어레이 기판 | |

| JP5792817B2 (ja) | 表示装置 | |

| US8350792B2 (en) | Display device | |

| US8384870B2 (en) | Display substrate, method of manufacturing the same and display panel having the display substrate | |

| JP4851255B2 (ja) | 表示装置 | |

| JP2006209089A (ja) | 表示装置 | |

| KR20060074854A (ko) | 디스플레이 장치 | |

| KR20130122883A (ko) | 액정표시장치 및 그 제조방법 | |

| CN111625113A (zh) | 有源矩阵基板、液晶显示装置以及内嵌式触控面板 | |

| JP2008064961A (ja) | 配線構造、及び表示装置 | |

| US10928696B2 (en) | Wiring substrate and display panel | |

| JP5088687B2 (ja) | 電界駆動型装置及び電子機器 | |

| JP5443144B2 (ja) | 表示装置 | |

| JP2010008444A (ja) | 液晶表示装置 | |

| JP4092309B2 (ja) | 液晶表示装置 | |

| US10754210B1 (en) | Display device | |

| WO2018051878A1 (ja) | 実装基板及び表示パネル | |

| JP2007248903A (ja) | 液晶表示装置及び液晶表示装置の製造方法 | |

| WO2013080520A1 (ja) | 表示装置 | |

| US9651836B2 (en) | Display device | |

| JP2007271804A (ja) | 液晶パネル用アレイ基板および液晶パネル | |

| CN110262148B (zh) | 一种阵列基板、显示面板和显示装置 | |

| JP2010175700A (ja) | 液晶表示装置 | |

| JP2009069725A (ja) | 液晶パネル |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090610 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090610 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110218 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20110218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110930 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111018 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111020 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4851255 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141028 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313117 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |