JP4834992B2 - 半導体装置の製造方法 - Google Patents

半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4834992B2 JP4834992B2 JP2004373277A JP2004373277A JP4834992B2 JP 4834992 B2 JP4834992 B2 JP 4834992B2 JP 2004373277 A JP2004373277 A JP 2004373277A JP 2004373277 A JP2004373277 A JP 2004373277A JP 4834992 B2 JP4834992 B2 JP 4834992B2

- Authority

- JP

- Japan

- Prior art keywords

- fine particles

- organic semiconductor

- conductive path

- substrate

- forming

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electroluminescent Light Sources (AREA)

- Electrodes Of Semiconductors (AREA)

- Thin Film Transistor (AREA)

Description

該微粒子は、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列されていることを特徴とする。

微粒子と有機半導体分子とを結合させる前に、微粒子を、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列する、微粒子配列・充填工程を備えていることを特徴とする。

(A)支持体上に形成されたゲート電極、

(B)ゲート電極上に形成されたゲート絶縁層(基体に相当する)、

(C)ゲート絶縁層上に形成されたソース/ドレイン電極、並びに、

(D)ソース/ドレイン電極の間であってゲート絶縁層上に形成され、導電路によって構成されたチャネル形成領域、

を備えている。

(A)支持体上に形成されたゲート電極、

(B)ゲート電極上に形成されたゲート絶縁層(基体に相当する)、

(C)ゲート絶縁層上に形成され、導電路によって構成されたチャネル形成領域を含むチャネル形成領域構成層、並びに、

(D)チャネル形成領域構成層上に形成されたソース/ドレイン電極、

を備えている。

基体上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体上にチャネル形成領域を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子と有機半導体分子とを結合させる前に、微粒子を、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列することを特徴とする。

(A)基体上に形成されたソース/ドレイン電極、

(B)ソース/ドレイン電極の間の基体上に形成され、導電路によって構成されたチャネル形成領域、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

基体上にチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子と有機半導体分子とを結合させる前に、微粒子を、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列することを特徴とする。

(A)基体上に形成され、導電路によって構成されたチャネル形成領域を含むチャネル形成領域構成層、

(B)チャネル形成領域構成層上に形成されたソース/ドレイン電極、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

ゲート絶縁層を構成する基体の一方の面上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体の一方の面上にチャネル形成領域を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上に電気絶縁性の支持体を形成した後、

ゲート絶縁層を構成する基体の他方の面上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子と有機半導体分子とを結合させる前に、微粒子を、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列することを特徴とする。

(A)電気絶縁性の支持体上に形成され、導電路によって構成されたチャネル形成領域を含むチャネル形成領域構成層、

(B)チャネル形成領域構成層上に形成されたソース/ドレイン電極、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層(基体に相当する)、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

ゲート絶縁層を構成する基体の一方の面上にチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上に電気絶縁性の支持体を形成した後、

ゲート絶縁層を構成する基体の他方の面上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子と有機半導体分子とを結合させる前に、微粒子を、基体の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列することを特徴とする。

(A)電気絶縁性の支持体上に形成されたソース/ドレイン電極、

(B)ソース/ドレイン電極の間に形成され、導電路によって構成されたチャネル形成領域、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層(基体に相当する)、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

構造式(2):4,4’−ジイソシアノビフェニル

構造式(3):4,4’−ジイソシアノ−p−テルフェニル

構造式(4):2,5−ビス(5’−チオアセチル−2’−チオフェニル)チオフェン

構造式(5):4,4’−ジイソシアノフェニル

構造式(6):ベンジジン(ビフェニル−4,4'−ジアミン)

構造式(7):TCNQ(テトラシアノキノジメタン)

構造式(8):ビフェニル−4,4'−ジカルボン酸

構造式(9):1,4−ジ(4−チオフェニルアセチリニル)−2−エチルベンゼン

構造式(10):1,4−ジ(4−イソシアノフェニルアセチリニル)−2−エチルベンゼン

(A)支持体10上に形成されたゲート電極12、

(B)支持体10及びゲート電極12上に形成されたゲート絶縁層13(基体に相当する)、

(C)ゲート絶縁層13上に形成されたソース/ドレイン電極14、並びに、

(D)ソース/ドレイン電極14の間であってゲート絶縁層13上に形成され、導電路20によって構成されたチャネル形成領域15、

から構成されている。

(1)微粒子を含む溶液(例えば、微粒子コロイド溶液)を、例えばキャスト法やLB法で塗布し、塗布された微粒子コロイド溶液中の溶媒の蒸発速度を適切に制御することにより微粒子の密なる充填状態の配列を達成し、

しかも、

(2)微粒子のサイズばらつきが少ない、粒径の揃った微粒子を用いることにより、微粒子の2次元ネットワークを広い範囲において、且つ、長距離秩序を有する形態で達成する、

という2つの新しい手法を採用している。

金ナノ粒子の塗布法に関しては、金ナノ粒子を溶媒に分散させたコロイド溶液(以下、金ナノ粒子コロイド溶液と呼ぶ)を基体上に滴下して、溶媒が蒸発するときに、金ナノ粒子間に働く横毛管力による自己組織化現象を利用して2次元規則配列を達成する手法(キャスト法)が古くから採られてきた。このキャスト法は、プロセスが非常に簡便である反面、溶媒の蒸発速度が早すぎると、金ナノ粒子の自己組織化の速度を溶媒の蒸発速度が上回ってしまうため、金ナノ粒子がその場に取り残されてしまい、結果として金ナノ粒子の分布にムラができてしまうといった難点がある。

第1の手段は、基体と金ナノ粒子との相互作用を考慮した手段である。自己組織化によって金ナノ粒子の2次元様の構造を形成させる際、金ナノ粒子と基体との相互作用が重要となる。金ナノ粒子の表面状態は、主にその表面を被覆している保護膜を構成する分子の性質によって決定される。それ故、様々な保護膜を有する金ナノ粒子、例えば表面に疎水性を有する保護膜(保護膜を構成する分子が例えばアルキル基を有するもの)が形成された金ナノ粒子を用い、あるいは、表面に親水性を有する保護膜(保護膜を構成する分子が、例えばカルボキシ基、アミノ基あるいは水酸基を有するもの)が形成された金ナノ粒子を用い、更には、微粒子を含む溶液から成る薄膜を形成する前に基体の表面処理を行うことで基体の表面状態を最適化し、金ナノ粒子及び基体の振る舞いを変えることができ、キャスト法の実行に最も適した条件を得ることが可能となる(T. Teranishi, et al., Adv. Mater., 2001, 13, 1699 参照)。ここで、SiO2から成る基体の表面を親水化処理する場合、プラズマアッシング処理や、ピランハ溶液処理、酸素プラズマ処理、UV−オゾン処理による水酸基の導入を挙げることができる。一方、SiO2から成る基体の表面を疎水化処理する場合、例えば、末端に疎水基を有する処理剤(例えば、ヘキサメチルジシラザン[(CH3)3SiNHSi(CH3)3]、オクタデシルトリクロロシラン[C18H37SiCl3])による表面処理を行えばよい。

第2の手段は、微粒子を含む溶液と基体との間の濡れ性を制御することである。基体に対して溶液中の溶媒の濡れ性が良ければ溶媒は基体上を広がり、濡れ性が悪ければ溶媒は集まる。一般的に溶媒が基体に対してより広い範囲に広がった方が、基体上に微粒子を含む溶液から成る薄膜を形成した後、広い面積の薄膜の全体から溶媒が均一に蒸発する。濡れ性は、異なる溶媒を混合し、その混合比率を調整することにより、変化させることができ、これによって、基体上に金ナノ粒子を並べるのに最も適した濡れ性を得ることが可能となる。例えば、SiO2から成る基体上に金ナノ粒子のトルエン溶液をキャスト法にて塗布し、微粒子を含む溶液から成る薄膜を基体上に形成する場合、金ナノ粒子のトルエン溶液にエタノールを或る程度混合したとき、溶液が最も基体上で広がる。

サイズの揃った金ナノ粒子の作製方法は過去に数多く報告されているが、本発明においては、予め作製しておいた金ナノ粒子を改良することで得た均一な粒径を有する金ナノ粒子を用いている。実施例1においては、Leff らが提案した方法(ドデシルアミン(C12H25NH2)を保護膜とする金ナノ粒子の作製法。D. V. Leff, et al., Langmuir, 1996, 12, 4723 参照)を採用した。そして、作製した金ナノ粒子コロイド溶液に対して、Lin らの提案している方法(X. M. Lin, et al., J. Nanoparticle Res., 2000, 2, 157 参照)を改良した方法を適用することにより金ナノ粒子の粒径の均一化を行った。

金ナノ粒子の保護膜分子としてはアルカンチオール分子(例えばドデカンチオール)が良く知られているが、一般に、金(Au)と硫黄(S)の結合力は強く、有機半導体分子で金ナノ粒子間を架橋する際に、保護膜を構成する分子を有機半導体分子で置き換えるのに時間がかかると考えられている。保護膜を構成する分子が、より弱く金(Au)と結合していれば(言い換えれば、置換され易いならば)、金ナノ粒子と有機半導体分子の結合が、よりスムーズに進行すると考えられる。

先ず、支持体上にゲート電極12を形成する。具体的には、ガラス基板10の表面に形成されたSiO2から成る絶縁層11上に、ゲート電極12を形成すべき部分が除去されたレジスト層(図示せず)を、リソグラフィ技術に基づき形成する。その後、密着層としてのチタン(Ti)層(図示せず)、及び、ゲート電極12としての金(Au)層を、順次、真空蒸着法にて全面に成膜し、その後、レジスト層を除去する。こうして、所謂リフトオフ法に基づき、ゲート電極12を得ることができる。

次に、ゲート電極12を含む支持体(より具体的には絶縁層11)上にゲート絶縁層13を形成する。具体的には、SiO2から成るゲート絶縁層13を、スパッタリング法に基づきゲート電極12及び絶縁層11上に形成する。ゲート絶縁層13の成膜を行う際、ゲート電極12の一部をハードマスクで覆うことによって、ゲート電極12の取出部(図示せず)をフォトリソグラフィ・プロセス無しで形成することができる。

次に、ゲート絶縁層13の上に金(Au)層から成るソース/ドレイン電極14を形成する。具体的には、ゲート絶縁層13上に、ソース/ドレイン電極14を形成すべき部分が除去されたレジスト層をリソグラフィ技術に基づき形成する。そして、[工程−100]と同様にして、レジスト層及びゲート絶縁層13上に、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極14としての金(Au)層を、順次、真空蒸着法にて成膜し、その後、レジスト層を除去する。こうして、所謂リフトオフ法に基づき、ソース/ドレイン電極14を得ることができる(図2の(A)参照)。

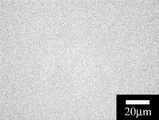

その後、微粒子21を含む溶液から成る薄膜を形成した後、薄膜に含まれる溶媒を蒸発させる。尚、薄膜に含まれる溶媒を蒸発させる工程において、蒸発速度を制御しながら薄膜に含まれる溶媒を蒸発させる。具体的には、先に説明した《粒径の均一化》によって得られたサイズの揃った微粒子21である金ナノ粒子から調製した金ナノ粒子コロイド溶液を使用して、先に説明した《微粒子の基体への塗布》を実行することによって、金(Au)から成る微粒子21を、基体(ゲート絶縁層13)の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列させる。この状態を模式的に図2の(B)に示す。尚、ドデシルアミンあるいはドデカンチオールから成る保護膜によって表面が被覆された金ナノ粒子を0.05重量%分散させ、ドデカンチオールを0.63重量%混入させた金ナノ粒子コロイド溶液(溶媒:トルエン)を使用することで、金ナノ粒子コロイド溶液における溶媒蒸発速度を遅くする。また、先に説明した[基体の表面処理]及び/又は[微粒子を含む溶液と基体との間の濡れ性の制御]といった各種を処理を行ってもよい。

次いで、先に説明した《金ナノ粒子と有機半導体分子との化学的な結合》を実行する。具体的には、4,4’−ビフェニルジチオールから成る有機半導体分子22をモル濃度数mMにてトルエンに溶解した溶液にゲート絶縁層13を含む全体を浸漬した後、トルエンで洗浄して溶液を置換し、その後、溶媒を蒸発させる。このとき、保護膜を構成するドデシルアミンが4,4’−ビフェニルジチオールから成る有機半導体分子22によって置換され、有機半導体分子22が、その末端にあるチオール基(−SH)によって金ナノ粒子から成る微粒子21の表面に化学的に結合する。1個の微粒子21の表面には、多数の有機半導体分子22が微粒子21を包み込むように結合する。そして、それらの内の一部が、もう一方の分子末端にあるチオール基によって他の微粒子21とも結合するため、有機半導体分子22によって微粒子21が2次元ネットワーク状に連結された1層目の結合体層23が形成される。この状態を、模式的に図2の(C)に示す。

次に、必要に応じて、[工程−130]及び[工程−140]を所望の回数だけ繰り返す。こうして、有機半導体分子22が両端に有する官能基によって有機半導体分子22と微粒子21とが3次元的に化学的に(交互に)結合することで、ネットワーク状の導電路20が構築され、微粒子21と有機半導体分子22との結合体の積層構造によって導電路20が構成されている構造を得ることができる。尚、図2の(D)には、[工程−140]及び[工程−150]を3回、繰り返し、微粒子21と有機半導体分子22との結合体の3層の積層構造を得た状態を示している。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例1の半導体装置を完成させる。

先ず、実施例1の[工程−100]と同様にして、支持体上にゲート電極12を形成した後、実施例1の[工程−110]と同様にして、ゲート電極12を含む支持体(より具体的には絶縁層11)上にゲート絶縁層13を形成する。

次に、実施例1の[工程−130]〜[工程−140]を実行することで、微粒子21を、基体に相当するゲート絶縁層13の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列し、次いで、微粒子21と有機半導体分子22とを化学的に結合させる。こうして、有機半導体分子22によって微粒子21が2次元ネットワーク状に連結された1層目の結合体層23から成る導電路20を形成することができ、チャネル形成領域構成層15Aを得ることができる。即ち、ソース/ドレイン電極14を形成すべきゲート絶縁層13の部分の上にチャネル形成領域15を形成することができる。この状態を、模式的に図3の(A)に示す。更に、必要に応じて、実施例1の[工程−150]と同様に、実施例1の[工程−130]及び[工程−140]を所望の回数だけ繰り返す。

その後、チャネル形成領域構成層15Aの上に、チャネル形成領域15を挟むようにソース/ドレイン電極14を形成する(図3の(B)参照)。具体的には、全面に、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極14としての金(Au)層を、順次、真空蒸着法に基づき形成する。ソース/ドレイン電極14の成膜を行う際、チャネル形成領域構成層15Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極14をフォトリソグラフィ・プロセス無しで形成することができる。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例2の半導体装置を完成させる。

(A)基体30上に形成されたソース/ドレイン電極34、

(B)ソース/ドレイン電極34の間の基体30上に形成され、導電路40によって構成されたチャネル形成領域35、

(C)ソース/ドレイン電極34及びチャネル形成領域35上に形成されたゲート絶縁層33、並びに、

(D)ゲート絶縁層33上に形成されたゲート電極32、

を備えている。

先ず、劈開した雲母から成る基体30上にソース/ドレイン電極34を形成する(図4の(A)参照)。具体的には、基体30上に、ソース/ドレイン電極34としての金(Au)層を真空蒸着法に基づき形成する。ソース/ドレイン電極34の成膜を行う際、基体30の一部をハードマスクで覆うことによって、ソース/ドレイン電極34をフォトリソグラフィ・プロセス無しで形成することができる。尚、雲母と金層との間の密着性は良好であるが故に、密着層の形成は不要である。

その後、ソース/ドレイン電極34の間の基体30上に、導電路40によって構成されたチャネル形成領域35を形成する。具体的には、実施例1の[工程−130]〜[工程−140]を実行することで、微粒子41を、基体30の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列し、次いで、微粒子41と有機半導体分子42とを化学的に結合させる。こうして、有機半導体分子42によって微粒子41が2次元ネットワーク状に連結された1層目の結合体層から成る導電路40を形成することができる。即ち、ソース/ドレイン電極34の間の基体30上にチャネル形成領域35を形成することができる。この状態を、模式的に図4の(B)に示す。更に、必要に応じて、実施例1の[工程−150]と同様に、実施例1の[工程−130]及び[工程−140]を所望の回数だけ繰り返す。

次いで、ソース/ドレイン電極34及びチャネル形成領域35上にゲート絶縁層33を形成する。具体的には、PVAをスピンコーティング法にて全面に成膜することで、ゲート絶縁層33を得ることができる。

その後、ゲート絶縁層33上にゲート電極32を形成する。具体的には、密着層としてのチタン(Ti)層(図示せず)、及び、ゲート電極32としての金(Au)層を、順次、真空蒸着法にて全面に成膜する。ゲート電極32の成膜を行う際、ゲート絶縁層33の一部をハードマスクで覆うことによって、ゲート電極32をフォトリソグラフィ・プロセス無しで形成することができる。こうして、図4の(C)に示す構造を得ることができる。

(A)基体30上に形成され、導電路40によって構成されたチャネル形成領域35を含むチャネル形成領域構成層35A、

(B)チャネル形成領域構成層35A上に形成されたソース/ドレイン電極34、

(C)ソース/ドレイン電極34及びチャネル形成領域35上に形成されたゲート絶縁層33、並びに、

(D)ゲート絶縁層33上に形成されたゲート電極32、

を備えている。

先ず、劈開した雲母から成る基体30上にチャネル形成領域35を構成するチャネル形成領域構成層35Aを形成する。具体的には、実施例1の[工程−130]〜[工程−140]を実行することで、微粒子41を、基体30の表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列し、次いで、微粒子41と有機半導体分子42とを化学的に結合させる。こうして、有機半導体分子42によって微粒子41が2次元ネットワーク状に連結された1層目の結合体層から成る導電路40を形成することができる。即ち、基体30上にチャネル形成領域35を構成するチャネル形成領域構成層35Aを形成することができる。この状態を、模式的に図5の(A)に示す。更に、必要に応じて、実施例1の[工程−150]と同様に、実施例1の[工程−130]及び[工程−140]を所望の回数だけ繰り返す。

その後、チャネル形成領域構成層35Aの上に、チャネル形成領域35を挟むようにソース/ドレイン電極34を形成する。具体的には、全面に、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極34としての金(Au)層を、順次、真空蒸着法に基づき形成する(図5の(B)参照)。ソース/ドレイン電極34の成膜を行う際、チャネル形成領域構成層35Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極34をフォトリソグラフィ・プロセス無しで形成することができる。

次いで、ソース/ドレイン電極34及びチャネル形成領域35上に、実施例3の[工程−320]と同様にして、ゲート絶縁層33を形成する。

その後、ゲート絶縁層33上にゲート電極32を形成する。具体的には、密着層としてのチタン(Ti)層(図示せず)、及び、ゲート電極32としての金(Au)層を、順次、真空蒸着法にて全面に成膜する。ゲート電極32の成膜を行う際、ゲート絶縁層33の一部をハードマスクで覆うことによって、ゲート電極32をフォトリソグラフィ・プロセス無しで形成することができる。こうして、図5の(C)に示す構造を得ることができる。

(A)電気絶縁性の支持体50上に形成され、導電路40によって構成されたチャネル形成領域55を含むチャネル形成領域構成層55A、

(B)チャネル形成領域構成層55A上に形成されたソース/ドレイン電極54、

(C)ソース/ドレイン電極54及びチャネル形成領域55上に形成されたゲート絶縁層53(基体53Aに相当する)、並びに、

(D)ゲート絶縁層53上に形成されたゲート電極52、

を備えている。

先ず、ゲート絶縁層53を構成する基体53Aの一方の面上にソース/ドレイン電極54を形成する。具体的には、劈開した雲母から成る基体53A上に、ソース/ドレイン電極54としての金(Au)層を真空蒸着法に基づき形成する。ソース/ドレイン電極54の成膜を行う際、基体53Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極54をフォトリソグラフィ・プロセス無しで形成することができる。尚、雲母と金層との間の密着性は良好であるが故に、密着層の形成は不要である。

その後、ソース/ドレイン電極54の間の基体53Aの一方の面上に、導電路40によって構成されたチャネル形成領域55を形成する。具体的には、実施例1の[工程−130]〜[工程−140]を実行することで、微粒子41を、基体53Aの表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列し、次いで、微粒子41と有機半導体分子42とを化学的に結合させる。こうして、有機半導体分子42によって微粒子41が2次元ネットワーク状に連結された1層目の結合体層から成る導電路40を形成することができる。即ち、ソース/ドレイン電極54の間の基体53A上にチャネル形成領域55を形成することができる。この状態を、模式的に図6の(A)に示す。更に、必要に応じて、実施例1の[工程−150]と同様に、実施例1の[工程−130]及び[工程−140]を所望の回数だけ繰り返す。

次いで、ソース/ドレイン電極54及びチャネル形成領域55上に電気絶縁性の支持体(パッシベーション膜)50を形成する。電気絶縁性の支持体50は、例えば、PVD法にて成膜された酸化ケイ素系材料(例えば、SiOX)や窒化ケイ素(SiNY)から構成することができる。こうして、図6の(A)に示す構造を得ることができる。尚、その後、パッシベーション膜50上に剛性の高い支持体(図示せず)を密着させることが好ましい。

その後、雲母から成る基体53Aを劈開し、あるいは、エッチングすることで、薄層化し、ゲート絶縁層53を得る(図6の(B)参照)。

次いで、ゲート絶縁層53を構成する基体53Aの他方の面上にゲート電極52を形成する。具体的には、ゲート絶縁層53を構成する基体53Aの他方の面上に、ゲート電極52としての金(Au)層を真空蒸着法に基づき形成する。ゲート電極52の成膜を行う際、ゲート絶縁層53を構成する基体53Aの他方の面の一部をハードマスクで覆うことによって、ゲート電極52をフォトリソグラフィ・プロセス無しで形成することができる。尚、雲母と金層との間の密着性は良好であるが故に、密着層の形成は不要である。

(A)電気絶縁性の支持体50上に形成されたソース/ドレイン電極54、

(B)ソース/ドレイン電極54の間に形成され、導電路40によって構成されたチャネル形成領域55、

(C)ソース/ドレイン電極54及びチャネル形成領域55上に形成されたゲート絶縁層53(基体53Aに相当する)、並びに、

(D)ゲート絶縁層53上に形成されたゲート電極52、

を備えている。

先ず、ゲート絶縁層を構成する基体53A(劈開した雲母から成る)の一方の面上に、チャネル形成領域55を構成するチャネル形成領域構成層55Aを形成する。具体的には、実施例1の[工程−130]〜[工程−140]を実行することで、微粒子41を、基体53Aの表面と略平行な面内において2次元的に規則的に、且つ、充填状態にて配列し、次いで、微粒子41と有機半導体分子42とを化学的に結合させる。こうして、有機半導体分子42によって微粒子41が2次元ネットワーク状に連結された1層目の結合体層から成る導電路40を形成することができる。即ち、基体53A上にチャネル形成領域55を構成するチャネル形成領域構成層55Aを形成することができる。更に、必要に応じて、実施例1の[工程−150]と同様に、実施例1の[工程−130]及び[工程−140]を所望の回数だけ繰り返す。

その後、チャネル形成領域構成層55Aの上に、チャネル形成領域55を挟むようにソース/ドレイン電極54を形成する。具体的には、全面に、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極54としての金(Au)層を、順次、真空蒸着法に基づき形成する。ソース/ドレイン電極54の成膜を行う際、チャネル形成領域構成層55Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極54をフォトリソグラフィ・プロセス無しで形成することができる。

次いで、ソース/ドレイン電極54及びチャネル形成領域55上に電気絶縁性の支持体(パッシベーション膜)50を形成する。電気絶縁性の支持体50は、例えば、PVD法にて成膜された酸化ケイ素系材料(例えば、SiOX)や窒化ケイ素(SiNY)から構成することができる。こうして、図7の(A)に示す構造を得ることができる。尚、その後、パッシベーション膜50上に剛性の高い支持体(図示せず)を密着させることが好ましい。

その後、雲母から成る基体53Aを劈開し、あるいは、エッチングすることで、薄層化し、ゲート絶縁層53を得る(図7の(B)参照)。

次いで、ゲート絶縁層53を構成する基体53Aの他方の面上にゲート電極52を形成する。具体的には、ゲート絶縁層53を構成する基体53Aの他方の面上に、ゲート電極52としての金(Au)層を真空蒸着法に基づき形成する。ゲート電極52の成膜を行う際、ゲート絶縁層53を構成する基体53Aの他方の面の一部をハードマスクで覆うことによって、ゲート電極52をフォトリソグラフィ・プロセス無しで形成することができる。尚、雲母と金層との間の密着性は良好であるが故に、密着層の形成は不要である。

Claims (16)

- 導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成される導電路を基体上に形成する工程を含む半導体装置の製造方法であって、

微粒子を、基体の表面と平行な面内において2次元的に規則的に、且つ、充填状態にて配列した後、有機半導体分子の溶液に微粒子を浸漬することで微粒子と有機半導体分子とを化学的に結合させ、以て、微粒子内の導電路と有機半導体分子内の分子骨格に沿った導電路とが連結したネットワーク状の導電路を形成する微粒子配列・充填・導電路形成工程を備えていることを特徴とする半導体装置の製造方法。 - 微粒子配列・充填・導電路形成工程は、微粒子を含む溶液から成る薄膜を基体上に形成した後、薄膜に含まれる溶媒を蒸発させる工程から成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 微粒子配列・充填・導電路形成工程は、微粒子を含む溶液に基づき薄膜を成膜した後、該薄膜を基体上に転写する工程から成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 微粒子配列・充填・導電路形成工程の実行後、有機半導体分子を接触させる工程を少なくとも1回行うことによって、微粒子と有機半導体分子とを結合させることを特徴とする請求項1に記載の半導体装置の製造方法。

- 微粒子の平均粒径をrAVE、微粒子の粒径の標準偏差をσとしたとき、σ/rAVE≦0.5を満足することを特徴とする請求項1に記載の半導体装置の製造方法。

- 有機半導体分子を、その末端の官能基によって、微粒子と化学的に結合させることを特徴とする請求項1に記載の半導体装置の製造方法。

- 微粒子は、導体としての金、銀、白金、銅、アルミニウム、パラジウム、クロム、ニッケル、又は、鉄から成り、あるいは、これらの金属から構成された合金から成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 微粒子は、半導体としての硫化カドミウム、セレン化カドミウム、テルル化カドミウム、ガリウム砒素、酸化チタン、又は、シリコンから成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 有機半導体分子は、共役結合を有する有機半導体分子であって、分子の両端に、チオール基(−SH)、アミノ基(−NH2)、イソシアノ基(−NC)、シアノ基(−CN)、チオアセチル基(−SCOCH3)、又は、カルボキシ基(−COOH)を有することを特徴とする請求項1に記載の半導体装置の製造方法。

- 基体は、酸化ケイ素系材料、酸化アルミニウム、又は、有機ポリマーから成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 基体は、雲母から成ることを特徴とする請求項1に記載の半導体装置の製造方法。

- 導電路の導電性を制御するための電界を生成させる制御部を形成する工程を更に含むことを特徴とする請求項1に記載の半導体装置の製造方法。

- 基体上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体上にチャネル形成領域を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子を、基体の表面と平行な面内において2次元的に規則的に、且つ、充填状態にて配列した後、微粒子と有機半導体分子とを結合させ、以て、微粒子内の導電路と有機半導体分子内の分子骨格に沿った導電路とが連結したネットワーク状の導電路を形成することを特徴とする半導体装置の製造方法。 - 基体上にチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子を、基体の表面と平行な面内において2次元的に規則的に、且つ、充填状態にて配列した後、有機半導体分子の溶液に微粒子を浸漬することで微粒子と有機半導体分子とを化学的に結合させ、以て、微粒子内の導電路と有機半導体分子内の分子骨格に沿った導電路とが連結したネットワーク状の導電路を形成することを特徴とする半導体装置の製造方法。 - ゲート絶縁層を構成する基体の一方の面上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体の一方の面上にチャネル形成領域を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上に電気絶縁性の支持体を形成した後、

ゲート絶縁層を構成する基体の他方の面上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子を、基体の表面と平行な面内において2次元的に規則的に、且つ、充填状態にて配列した後、有機半導体分子の溶液に微粒子を浸漬することで微粒子と有機半導体分子とを化学的に結合させ、以て、微粒子内の導電路と有機半導体分子内の分子骨格に沿った導電路とが連結したネットワーク状の導電路を形成することを特徴とする半導体装置の製造方法。 - ゲート絶縁層を構成する基体の一方の面上にチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、

次いで、ソース/ドレイン電極及びチャネル形成領域上に電気絶縁性の支持体を形成した後、

ゲート絶縁層を構成する基体の他方の面上にゲート電極を形成する工程から成り、

チャネル形成領域は、導電路によって構成されており、

該導電路は、導体又は半導体から成る微粒子と、該微粒子と結合した有機半導体分子とによって構成され、ゲート電極に印加される電圧によって導電性が制御され、

微粒子を、基体の表面と平行な面内において2次元的に規則的に、且つ、充填状態にて配列した後、有機半導体分子の溶液に微粒子を浸漬することで微粒子と有機半導体分子とを化学的に結合させ、以て、微粒子内の導電路と有機半導体分子内の分子骨格に沿った導電路とが連結したネットワーク状の導電路を形成することを特徴とする半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004373277A JP4834992B2 (ja) | 2003-12-26 | 2004-12-24 | 半導体装置の製造方法 |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003434349 | 2003-12-26 | ||

| JP2003434349 | 2003-12-26 | ||

| JP2004373277A JP4834992B2 (ja) | 2003-12-26 | 2004-12-24 | 半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005210107A JP2005210107A (ja) | 2005-08-04 |

| JP2005210107A5 JP2005210107A5 (ja) | 2007-09-27 |

| JP4834992B2 true JP4834992B2 (ja) | 2011-12-14 |

Family

ID=34914326

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004373277A Expired - Fee Related JP4834992B2 (ja) | 2003-12-26 | 2004-12-24 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4834992B2 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7687372B2 (en) * | 2005-04-08 | 2010-03-30 | Versatilis Llc | System and method for manufacturing thick and thin film devices using a donee layer cleaved from a crystalline donor |

| KR101223718B1 (ko) * | 2005-06-18 | 2013-01-18 | 삼성디스플레이 주식회사 | 나노 도전성 막의 패터닝 방법 |

| JP4940618B2 (ja) * | 2005-10-07 | 2012-05-30 | ソニー株式会社 | 半導体装置 |

| JP2007273949A (ja) * | 2006-03-30 | 2007-10-18 | Korea Univ Industrial & Academic Collaboration Foundation | ナノ粒子を用いたトップゲート型薄膜トランジスタおよびその製造方法 |

| JP4957735B2 (ja) * | 2006-05-18 | 2012-06-20 | ソニー株式会社 | 有機電子デバイス及びその製造方法、並びに、有機半導体分子 |

| JP4967503B2 (ja) * | 2006-07-28 | 2012-07-04 | ソニー株式会社 | 有機薄膜トランジスタ、有機薄膜トランジスタの形成方法 |

| JP2008155357A (ja) * | 2006-11-28 | 2008-07-10 | Institute Of Physical & Chemical Research | 構造体およびその製造方法 |

| JP6004092B2 (ja) * | 2013-04-18 | 2016-10-05 | 富士電機株式会社 | 積層体および積層体の製造方法 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003264326A (ja) * | 2002-03-08 | 2003-09-19 | Japan Science & Technology Corp | 分子集積回路素子及びその製造方法 |

| JP4736324B2 (ja) * | 2002-04-22 | 2011-07-27 | コニカミノルタホールディングス株式会社 | 半導体素子及びその製造方法 |

-

2004

- 2004-12-24 JP JP2004373277A patent/JP4834992B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005210107A (ja) | 2005-08-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4586334B2 (ja) | 電界効果型トランジスタ及びその製造方法 | |

| CN100440534C (zh) | 半导体装置及其制造方法 | |

| CN102024846B (zh) | 3端子电子器件和2端子电子器件 | |

| US8093109B2 (en) | Method for forming semiconductor thin film and method for manufacturing electronic device | |

| CN100590862C (zh) | 配线和有机晶体管及其制造方法 | |

| US20130056835A1 (en) | Transistor structures and methods of fabrication thereof | |

| CN101689607A (zh) | 结合界面导电簇的薄膜晶体管 | |

| US8309992B2 (en) | Switching element including carbon nanotubes and method for manufacturing the same | |

| JP4547864B2 (ja) | 電界効果型トランジスタ及びその製造方法 | |

| JP4834992B2 (ja) | 半導体装置の製造方法 | |

| JP4876520B2 (ja) | 不揮発性半導体メモリ及びその製造方法 | |

| JP2725587B2 (ja) | 電界効果型トランジスタ | |

| JP4940618B2 (ja) | 半導体装置 | |

| JP4696520B2 (ja) | 電界効果型トランジスタ及びその製造方法 | |

| JP4639703B2 (ja) | 電子装置の製造方法、並びに、半導体装置の製造方法 | |

| JP5510413B2 (ja) | 半導体装置及びその製造方法 | |

| JP5310567B2 (ja) | 薄膜トランジスタ及びその製造方法 | |

| JPWO2009096525A1 (ja) | 薄膜トランジスタ | |

| JP2006108400A (ja) | 半導体装置 | |

| Wu et al. | Organic Thin Film Transistors with Contacts Printed from Metal Nanoparticles | |

| JP2006100618A (ja) | 半導体装置及びその製造方法 | |

| JP2007214542A (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070809 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070809 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110614 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110812 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110830 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110912 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141007 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141007 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |