JP4639703B2 - 電子装置の製造方法、並びに、半導体装置の製造方法 - Google Patents

電子装置の製造方法、並びに、半導体装置の製造方法 Download PDFInfo

- Publication number

- JP4639703B2 JP4639703B2 JP2004261908A JP2004261908A JP4639703B2 JP 4639703 B2 JP4639703 B2 JP 4639703B2 JP 2004261908 A JP2004261908 A JP 2004261908A JP 2004261908 A JP2004261908 A JP 2004261908A JP 4639703 B2 JP4639703 B2 JP 4639703B2

- Authority

- JP

- Japan

- Prior art keywords

- organic semiconductor

- cluster

- fine particles

- forming

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Polymers With Sulfur, Phosphorus Or Metals In The Main Chain (AREA)

- Thin Film Transistor (AREA)

Description

導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスターを得た後、

該クラスターを2つの電極間に配置することによって、2つの電極間に導電路を形成することを特徴とする。

基体上にゲート電極を形成した後、基体及びゲート電極上にゲート絶縁層を形成し、次いで、

ゲート絶縁層上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極間に、導電路から成るチャネル形成領域を形成する工程から成り、

チャネル形成領域を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスターを得た後、該クラスターをソース/ドレイン電極の間のゲート絶縁層の部分に配置する工程から成ることを特徴とする。

(A)基体上に形成されたゲート電極、

(B)ゲート電極及び基体上に形成されたゲート絶縁層、

(C)ゲート絶縁層上に形成されたソース/ドレイン電極、並びに、

(D)ソース/ドレイン電極の間であってゲート絶縁層上に形成され、導電路によって構成されたチャネル形成領域、

を備えている。

基体上にゲート電極を形成した後、基体及びゲート電極上にゲート絶縁層を形成し、次いで、

ゲート絶縁層上に、導電路から成るチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上にソース/ドレイン電極を形成する工程から成り、

チャネル形成領域構成層を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスターを得た後、該クラスターをゲート絶縁層の上に配置する工程から成ることを特徴とする。

(A)基体上に形成されたゲート電極、

(B)ゲート電極及び基体上に形成されたゲート絶縁層、

(C)ゲート絶縁層上に形成され、導電路によって構成されたチャネル形成領域を含むチャネル形成領域構成層、並びに、

(D)チャネル形成領域構成層上に形成されたソース/ドレイン電極、

を備えている。

基体上に、導電路から成るチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、次いで、

ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域構成層を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスターを得た後、該クラスターを基体の上に配置する工程から成る特徴とする。

(A)基体上に形成され、導電路によって構成されたチャネル形成領域を含むチャネル形成領域構成層、

(B)チャネル形成領域構成層上に形成されたソース/ドレイン電極、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

基体上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体上に、導電路から成るチャネル形成領域を形成し、次いで、

ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合(反応)して成るクラスターを得た後、該クラスターをソース/ドレイン電極の間の基体の部分の上に配置する工程から成ることを特徴とする。

(A)基体上に形成されたソース/ドレイン電極、

(B)ソース/ドレイン電極の間の基体上に形成され、導電路によって構成されたチャネル形成領域、

(C)ソース/ドレイン電極及びチャネル形成領域上に形成されたゲート絶縁層、並びに、

(D)ゲート絶縁層上に形成されたゲート電極、

を備えている。

(A)基体11上に形成されたゲート電極12、

(B)ゲート電極12及び基体11上に形成されたゲート絶縁層13、

(C)ゲート絶縁層13上に形成されたソース/ドレイン電極14(電子装置における2つの電極に相当する)、並びに、

(D)ソース/ドレイン電極14の間であってゲート絶縁層13上に形成され、導電路23によって構成されたチャネル形成領域15、

を備えている。

実施例2においても、実施例1と同じ、導体から成る微粒子21を含む溶液として、金微粒子(金ナノ粒子)のトルエン溶液を用いた。また、有機半導体分子22としてBPDTを用いた。そして、実施例1と同様の方法で、金微粒子(金ナノ粒子)のトルエン溶液に粉末状のBPDTを投入して、混合することによって、有機半導体分子22が末端に有する官能基が微粒子21と化学的に結合し(より具体的には、有機半導体分子22が両端に有する官能基によって有機半導体分子22と微粒子21とが化学的に(交互に)結合することで、微粒子21と有機半導体分子22とが3次元的なネットワーク状に結合し)、クラスター20が形成された。

一方、ガラス基板の表面に形成されたSiO2から成る基体11上にゲート電極12を形成した。具体的には、基体11上に、ゲート電極12を形成すべき部分が除去されたレジスト層(図示せず)を、リソグラフィ技術に基づき形成する。その後、密着層としてのチタン(Ti)層(図示せず)、及び、ゲート電極12としての金(Au)層を、順次、真空蒸着法にて全面に成膜し、その後、レジスト層を除去する。こうして、所謂リフトオフ法に基づき、ゲート電極12を得ることができる。

次に、ゲート電極12を含む基体11上にゲート絶縁層13を形成する。具体的には、SiO2から成るゲート絶縁層13を、スパッタリング法に基づきゲート電極12及び基体11上に形成する。ゲート絶縁層13の成膜を行う際、ゲート電極12の一部をハードマスクで覆うことによって、ゲート電極12の取出部(図示せず)をフォトリソグラフィ・プロセス無しで形成することができる。

次に、ゲート絶縁層13の上に金(Au)層から成るソース/ドレイン電極14を形成する。具体的には、ゲート絶縁層13上に、ソース/ドレイン電極14を形成すべき部分が除去されたレジスト層をリソグラフィ技術に基づき形成する。そして、[工程−210]と同様にして、レジスト層及びゲート絶縁層13上に、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極14としての金(Au)層を、順次、真空蒸着法にて成膜し、その後、レジスト層を除去する。こうして、所謂リフトオフ法に基づき、ソース/ドレイン電極14を得ることができる。

その後、[工程−200]において得られたクラスター20を2つの電極間であるソース/ドレイン電極14の間に配置することによって、2つの電極間であるソース/ドレイン電極14の間に導電路23を形成する。あるいは又、ソース/ドレイン電極14間に、導電路23から成るチャネル形成領域15を形成する。具体的には、[工程−200]において得られたクラスター20を、ソース/ドレイン電極14の間のゲート絶縁層13の部分に配置する。クラスター20の配置は、クラスターと溶媒とを混合したクラスター混合溶液を2つの電極間に塗布し、次いで、クラスター混合溶液を乾燥させることで行う。より具体的には、[工程−200]において得られたクラスター20とトルエンから成る溶媒とを混合したクラスター混合溶液を準備する。尚、必要であれば、フィルタリングして所望のサイズのクラスター20を選択する。そして、このクラスター混合溶液に基体11等の全体を浸漬することで、このクラスター混合溶液を2つの電極(ソース/ドレイン電極14)間に塗布し、次いで、クラスター混合溶液を自然乾燥させる。クラスター20とクラスター20、あるいは、クラスター20と電極(ソース/ドレイン電極14)とは、クラスター20の表面に存在する有機半導体分子30によって、相互に結合される。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例2の半導体装置を完成させる。

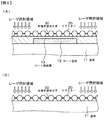

(A)基体11上に形成されたゲート電極12、

(B)ゲート電極12及び基体11上に形成されたゲート絶縁層13、

(C)ゲート絶縁層13上に形成され、導電路23によって構成されたチャネル形成領域15を含むチャネル形成領域構成層15A、並びに、

(D)チャネル形成領域構成層15A上に形成されたソース/ドレイン電極14、

を備えている。

先ず、実施例2の[工程−200]と同様にして、クラスター20を得ておく。また、実施例2の[工程−210]と同様にして、基体11上にゲート電極12を形成した後、実施例2の[工程−220]と同様にして、ゲート電極12及び基体11上にゲート絶縁層13を形成する。

次に、ゲート絶縁層13上に、導電路23から成るチャネル形成領域15を構成するチャネル形成領域構成層15Aを形成する。即ち、クラスター20をゲート絶縁層13の上に配置する。具体的には、クラスター20の配置は、クラスターと溶媒とを混合したクラスター混合溶液をゲート絶縁層13上に塗布し、次いで、クラスター混合溶液を乾燥させることで行う。より具体的には、[工程−200]において得られたクラスター20とトルエンから成る溶媒とを混合したクラスター混合溶液を準備する。尚、必要であれば、フィルタリングして所望のサイズのクラスター20を選択する。そして、このクラスター混合溶液に基体11等の全体を浸漬することで、このクラスター混合溶液をゲート絶縁層13上に塗布し、次いで、クラスター混合溶液を自然乾燥させる。クラスター20とクラスター20とは、クラスター20の表面に存在する有機半導体分子30によって、相互に結合される。

その後、チャネル形成領域構成層15Aの上に、チャネル形成領域15を挟むようにソース/ドレイン電極14を形成する(図5の(A)参照)。具体的には、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極14としての金(Au)層を、順次、真空蒸着法に基づき形成する。ソース/ドレイン電極14の成膜を行う際、チャネル形成領域構成層15Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極14をフォトリソグラフィ・プロセス無しで形成することができる。こうして、クラスター20を2つの電極間であるソース/ドレイン電極14の間に配置することによって、2つの電極間であるソース/ドレイン電極14の間に導電路23を形成することができる。あるいは又、ソース/ドレイン電極14間に、導電路23から成るチャネル形成領域15を形成することができる。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例3の半導体装置を完成させる。

(A)基体11上に形成され、導電路23によって構成されたチャネル形成領域15を含むチャネル形成領域構成層15A、

(B)チャネル形成領域構成層15A上に形成されたソース/ドレイン電極14、

(C)ソース/ドレイン電極14及びチャネル形成領域15上に形成されたゲート絶縁層13、並びに、

(D)ゲート絶縁層13上に形成されたゲート電極12、

を備えている。

先ず、実施例2の[工程−200]と同様にして、クラスター20を得ておく。

一方、ガラス基板の表面に形成されたSiO2から成る基体11上に、導電路23から成るチャネル形成領域15を構成するチャネル形成領域構成層15Aを形成する。即ち、クラスター20を基体11の上に配置する。具体的には、クラスター20の配置は、クラスターと溶媒とを混合したクラスター混合溶液を基体11上に塗布し、次いで、クラスター混合溶液を乾燥させることで行う。より具体的には、[工程−200]において得られたクラスター20とトルエンから成る溶媒とを混合したクラスター混合溶液を準備する。尚、必要であれば、フィルタリングして所望のサイズのクラスター20を選択する。そして、このクラスター混合溶液に基体11の全体を浸漬することで、このクラスター混合溶液を基体11上に塗布し、次いで、クラスター混合溶液を自然乾燥させる。クラスター20とクラスター20とは、クラスター20の表面に存在する有機半導体分子30によって、相互に結合される。

次いで、チャネル形成領域構成層15A上に、チャネル形成領域15を挟むようにソース/ドレイン電極14を形成する。具体的には、密着層としてのチタン(Ti)層(図示せず)、及び、ソース/ドレイン電極14としての金(Au)層を、順次、真空蒸着法に基づき形成する。ソース/ドレイン電極14の成膜を行う際、チャネル形成領域構成層15Aの一部をハードマスクで覆うことによって、ソース/ドレイン電極14をフォトリソグラフィ・プロセス無しで形成することができる。

次いで、ソース/ドレイン電極14及びチャネル形成領域15上に、ゲート絶縁層13を形成する。具体的には、PVAをスピンコーティング法にて全面に成膜することで、ゲート絶縁層13を得ることができる。

その後、ゲート絶縁層13上にゲート電極12を形成する。具体的には、密着層としてのチタン(Ti)層(図示せず)、及び、ゲート電極12としての金(Au)層を、順次、真空蒸着法にて成膜する。ゲート電極12の成膜を行う際、ゲート絶縁層13の一部をハードマスクで覆うことによって、ゲート電極12をフォトリソグラフィ・プロセス無しで形成することができる。こうして、図5の(B)に示す構造を得ることができる。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例4の半導体装置を完成させる。

(A)基体11上に形成されたソース/ドレイン電極14、

(B)ソース/ドレイン電極14の間の基体11上に形成され、導電路23によって構成されたチャネル形成領域15、

(C)ソース/ドレイン電極14及びチャネル形成領域15上に形成されたゲート絶縁層13、並びに、

(D)ゲート絶縁層13上に形成されたゲート電極12、

を備えている。

先ず、実施例2の[工程−200]と同様にして、クラスター20を得ておく。

一方、ガラス基板の表面に形成されたSiO2から成る基体11上に、ソース/ドレイン電極を形成する。具体的には、基体11上に、密着層としてのチタン(Ti)層(図示せず)、ソース/ドレイン電極14としての金(Au)層を真空蒸着法に基づき形成する。ソース/ドレイン電極14の成膜を行う際、基体11の一部をハードマスクで覆うことによって、ソース/ドレイン電極14をフォトリソグラフィ・プロセス無しで形成することができる。

その後、ソース/ドレイン電極14の間の基体11上に、導電路23から成るチャネル形成領域15を形成する。即ち、クラスター20をソース/ドレイン電極14の間の基体11の部分の上に配置する。具体的には、クラスター20の配置は、クラスターと溶媒とを混合したクラスター混合溶液を基体11上に塗布し、次いで、クラスター混合溶液を乾燥させることで行う。より具体的には、[工程−200]において得られたクラスター20とトルエンから成る溶媒とを混合したクラスター混合溶液を準備する。尚、必要であれば、フィルタリングして所望のサイズのクラスター20を選択する。そして、このクラスター混合溶液に基体11等の全体を浸漬することで、このクラスター混合溶液をソース/ドレイン電極14の間の基体11の部分の上に塗布し、次いで、クラスター混合溶液を自然乾燥させる。クラスター20とクラスター20、あるいは、クラスター20と電極(ソース/ドレイン電極14)とは、クラスター20の表面に存在する有機半導体分子30によって、相互に結合される。

次に、ソース/ドレイン電極14及びチャネル形成領域15上に、実施例4の[工程−430]と同様にして、ゲート絶縁層13を形成する。

その後、実施例4の[工程−440]と同様にして、ゲート絶縁層13上にゲート電極12を形成する。こうして、図5の(C)に示す構造を得ることができる。

最後に、全面にパッシベーション膜(図示せず)を形成することで、実施例5の半導体装置を完成させる。

Claims (9)

- 導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合して成るクラスターを得た後、

該クラスターを2つの電極間に配置し、その後、有機半導体分子を溶解した有機半導体分子溶液を2つの電極間に配置されたクラスターに塗布し、次いで、有機半導体分子溶液を乾燥させることによって、2つの電極間に導電路を形成し、

有機半導体分子が両端に有する官能基によって有機半導体分子と微粒子とが化学的に結合することで、微粒子と有機半導体分子とが3次元的なネットワーク状に結合し、以て、クラスターが形成され、

ゲート電極、ゲート絶縁層、チャネル形成領域、及び、ソース/ドレイン電極を有する電界効果型トランジスタから成り、

ソース/ドレイン電極が2つの電極に相当し、

導電路によってチャネル形成領域が構成される電子装置の製造方法。 - 導電路の導電性は、導電路に加えられる電界によって制御される請求項1に記載の電子装置の製造方法。

- 有機半導体分子は、共役結合を有する有機半導体分子であって、分子の両端に、チオール基(−SH)、アミノ基(−NH2)、イソシアノ基(−NC)、シアノ基(−CN)、チオアセチル基(−SCOCH3)、又は、カルボキシ基(−COOH)を有することを特徴とする請求項1に記載の電子装置の製造方法。

- 微粒子は、導体としての金、銀、白金、銅、アルミニウム、パラジウム、クロム、ニッケル、又は、鉄から成り、あるいは、これらの金属から構成された合金から成ることを特徴とする請求項1に記載の電子装置の製造方法。

- 微粒子は、半導体としての硫化カドミウム、セレン化カドミウム、テルル化カドミウム、ガリウム砒素、酸化チタン、又は、シリコンから成ることを特徴とする請求項1に記載の電子装置の製造方法。

- 基体上にゲート電極を形成した後、基体及びゲート電極上にゲート絶縁層を形成し、次いで、

ゲート絶縁層上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極間に、導電路から成るチャネル形成領域を形成する工程から成り、

チャネル形成領域を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合して成るクラスターを得た後、該クラスターをソース/ドレイン電極の間のゲート絶縁層の部分に配置し、その後、有機半導体分子を溶解した有機半導体分子溶液をソース/ドレイン電極の間のゲート絶縁層の部分に配置されたクラスターに塗布し、次いで、有機半導体分子溶液を乾燥させる工程から成り、

有機半導体分子が両端に有する官能基によって有機半導体分子と微粒子とが化学的に結合することで、微粒子と有機半導体分子とが3次元的なネットワーク状に結合し、以て、クラスターが形成される半導体装置の製造方法。 - 基体上にゲート電極を形成した後、基体及びゲート電極上にゲート絶縁層を形成し、次いで、

ゲート絶縁層上に、導電路から成るチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上にソース/ドレイン電極を形成する工程から成り、

チャネル形成領域構成層を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合して成るクラスターを得た後、該クラスターをゲート絶縁層の上に配置し、その後、有機半導体分子を溶解した有機半導体分子溶液をゲート絶縁層の上に配置されたクラスターに塗布し、次いで、有機半導体分子溶液を乾燥させる工程から成り、

有機半導体分子が両端に有する官能基によって有機半導体分子と微粒子とが化学的に結合することで、微粒子と有機半導体分子とが3次元的なネットワーク状に結合し、以て、クラスターが形成される半導体装置の製造方法。 - 基体上に、導電路から成るチャネル形成領域を構成するチャネル形成領域構成層を形成した後、

チャネル形成領域構成層上に、チャネル形成領域を挟むようにソース/ドレイン電極を形成し、次いで、

ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域構成層を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合して成るクラスターを得た後、該クラスターを基体の上に配置し、その後、有機半導体分子を溶解した有機半導体分子溶液を基体の上に配置されたクラスターに塗布し、次いで、有機半導体分子溶液を乾燥させる工程から成り、

有機半導体分子が両端に有する官能基によって有機半導体分子と微粒子とが化学的に結合することで、微粒子と有機半導体分子とが3次元的なネットワーク状に結合し、以て、クラスターが形成される半導体装置の製造方法。 - 基体上にソース/ドレイン電極を形成した後、

ソース/ドレイン電極の間の基体上に、導電路から成るチャネル形成領域を形成し、次いで、

ソース/ドレイン電極及びチャネル形成領域上にゲート絶縁層を形成した後、

ゲート絶縁層上にゲート電極を形成する工程から成り、

チャネル形成領域を形成する工程は、導体又は半導体から成る微粒子を含む溶液と有機半導体分子とを混合することによって、微粒子と有機半導体分子とが結合して成るクラスターを得た後、該クラスターをソース/ドレイン電極の間の基体の部分の上に配置し、その後、有機半導体分子を溶解した有機半導体分子溶液をソース/ドレイン電極の間の基体の部分の上に配置されたクラスターに塗布し、次いで、有機半導体分子溶液を乾燥させる工程から成り、

有機半導体分子が両端に有する官能基によって有機半導体分子と微粒子とが化学的に結合することで、微粒子と有機半導体分子とが3次元的なネットワーク状に結合し、以て、クラスターが形成される半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004261908A JP4639703B2 (ja) | 2004-09-09 | 2004-09-09 | 電子装置の製造方法、並びに、半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2004261908A JP4639703B2 (ja) | 2004-09-09 | 2004-09-09 | 電子装置の製造方法、並びに、半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2006080257A JP2006080257A (ja) | 2006-03-23 |

| JP2006080257A5 JP2006080257A5 (ja) | 2007-08-02 |

| JP4639703B2 true JP4639703B2 (ja) | 2011-02-23 |

Family

ID=36159477

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004261908A Expired - Fee Related JP4639703B2 (ja) | 2004-09-09 | 2004-09-09 | 電子装置の製造方法、並びに、半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4639703B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8085578B2 (en) | 2009-03-13 | 2011-12-27 | Paul Scherrer Institut | Method and system for coding and read out of information in a microscopic cluster comprising coupled functional islands |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2003089515A1 (fr) * | 2002-04-22 | 2003-10-30 | Konica Minolta Holdings, Inc. | Composition de semi-conducteur organique, element semi-conducteur organique et procede pour les produire |

| JP2004088090A (ja) * | 2002-07-02 | 2004-03-18 | Sony Corp | 半導体装置及びその製造方法 |

-

2004

- 2004-09-09 JP JP2004261908A patent/JP4639703B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2003089515A1 (fr) * | 2002-04-22 | 2003-10-30 | Konica Minolta Holdings, Inc. | Composition de semi-conducteur organique, element semi-conducteur organique et procede pour les produire |

| JP2004088090A (ja) * | 2002-07-02 | 2004-03-18 | Sony Corp | 半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006080257A (ja) | 2006-03-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| Cao et al. | Current trends in shrinking the channel length of organic transistors down to the nanoscale | |

| US8288764B2 (en) | Organic electronic device, method for production thereof, and organic semiconductor molecule | |

| KR101413208B1 (ko) | 전극 피복 재료, 전극 구조체 및 반도체 장치 | |

| US9520572B2 (en) | Electronic device and method of manufacturing semiconductor device | |

| US7626197B2 (en) | Semiconductor device including conductive network of protective film molecules and fine particles | |

| US8120018B2 (en) | Semiconductor device comprising semiconductor molecules and a conductor formed of fine particles and linker molecules | |

| JP4547864B2 (ja) | 電界効果型トランジスタ及びその製造方法 | |

| Gupta et al. | Covalent assembly of gold nanoparticles: an application toward transistor memory | |

| Metzger | Monolayer rectifiers | |

| Metzger | Unimolecular rectifiers and prospects for other unimolecular electronic devices | |

| JP4834992B2 (ja) | 半導体装置の製造方法 | |

| Vuillaume | Nanometer-scale organic thin film transistors from self-assembled monolayers | |

| JP4639703B2 (ja) | 電子装置の製造方法、並びに、半導体装置の製造方法 | |

| JP4940618B2 (ja) | 半導体装置 | |

| JP5510523B2 (ja) | 電極被覆材料、電極構造体、及び、半導体装置 | |

| JP4696520B2 (ja) | 電界効果型トランジスタ及びその製造方法 | |

| Metzger | Six unimolecular rectifiers and what lies ahead | |

| JP2004356538A (ja) | 有機半導体トランジスタ | |

| Metzger | Unimolecular rectifiers and what lies ahead | |

| JP4957735B2 (ja) | 有機電子デバイス及びその製造方法、並びに、有機半導体分子 | |

| JP2007335827A (ja) | 微粒子層構造体及びその形成方法、半導体装置、並びに、分離領域 | |

| JP2007214542A (ja) | 半導体装置および半導体装置の製造方法 | |

| Jeong | Analyses of device characteristics in low voltage p-, new material n-, and dual-channel organic field-effect transistors | |

| JP2006080257A5 (ja) |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070618 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070618 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100805 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100924 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101102 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101115 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131210 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |