JP4763206B2 - 多相フィルタ - Google Patents

多相フィルタ Download PDFInfo

- Publication number

- JP4763206B2 JP4763206B2 JP2001548523A JP2001548523A JP4763206B2 JP 4763206 B2 JP4763206 B2 JP 4763206B2 JP 2001548523 A JP2001548523 A JP 2001548523A JP 2001548523 A JP2001548523 A JP 2001548523A JP 4763206 B2 JP4763206 B2 JP 4763206B2

- Authority

- JP

- Japan

- Prior art keywords

- filter

- capacitive

- channel

- current source

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/16—Networks for phase shifting

- H03H11/22—Networks for phase shifting providing two or more phase shifted output signals, e.g. n-phase output

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H11/08—Frequency selective two-port networks using gyrators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H11/12—Frequency selective two-port networks using amplifiers with feedback

- H03H11/126—Frequency selective two-port networks using amplifiers with feedback using a single operational amplifier

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03H—IMPEDANCE NETWORKS, e.g. RESONANT CIRCUITS; RESONATORS

- H03H11/00—Networks using active elements

- H03H11/02—Multiple-port networks

- H03H11/04—Frequency selective two-port networks

- H03H2011/0494—Complex filters

Landscapes

- Networks Using Active Elements (AREA)

- Filters And Equalizers (AREA)

- Filters That Use Time-Delay Elements (AREA)

- Power Conversion In General (AREA)

- Nonmetallic Welding Materials (AREA)

- Iron Core Of Rotating Electric Machines (AREA)

- Glass Compositions (AREA)

Description

本発明は、一般的に、多相バンドパス・フィルタに関する。

【0002】

このようなフィルタは、それ自体、例えば米国特許第4、914、408号により知られており、また例えば無線応用、テレビジョン応用又は電話応用の受信機回路に適用することが例えば可能である。このようなフィルタは、更に、異なる応用も知られているが、ここでは、このようなフィルタの可能な応用を受信機回路の背景においてより詳細に説明する。

【0003】

米国特許第4、914、408号に説明されているフィルタの大きな欠点は、2フィルタ・チャネル間の結合が抵抗により影響されることである。従って、本発明の重要な目的は、このようなカップリング抵抗を除去した多相バンドパス・フィルタを提供することである。

【0004】

図面を参照して、本発明による多相バンドパス・フィルタの好ましい実施例の下記説明によって、これらと共にその他の構成、特徴及び効果を更に詳細に説明する。図面において、同一参照番号は、同一又は同様の部分を表している。

【0005】

図1は、既知の受信機回路1を概要的に示しており、アンテナ2から来る受信機信号Sは、第1の混合段3において、ローカル発振器5から供給される信号φと混合され、かつ受信機信号Sは、第2の混合段4において、ローカル発振器5から供給され、第1の信号φに対して90°シフトされている第2の信号と混合される。同様に、位相同相信号によって示される第1の混合段3の出力信号は、フィルタ10の第1の入力11に供給され、同様に、直角位相信号によって示される第2の混合段4の出力信号は、フィルタ10の第2の入力12に供給される。フィルタ10は、それぞれ実質的に同一方法により、第1の入力11の同相信号及び第2の入力12の直角信号をそれぞれ処理する2フィルタ・チャネル13及び14を有し、また、同相出力信号及び直角出力信号をそれぞれ供給する出力15及び16をそれぞれ有する。第2の出力の直角出力信号は、第1の出力の同相出力信号に対して90°シフトされている。フィルタ・チャネル13及び14は、互いに同一のフィルタ特性、例えば帯域通過特性を有する。

【0006】

以下において、ローカル発振器信号の周波数は、f1により示される。受信機信号Sには、多くの周波数が存在する。以下において、受信回路1が同調すべき同調周波数は、f2により表される。この周波数は、ローカル周波数f1より高いものと、即ちf2=f1+Δfと仮定する。

【0007】

一般的に、異なる周波数f1及びf2を有する2信号が混合されると、信号成分は、異なる周波数Δf=f2−f1を発生する。しかしながら、受信機信号Sには、更にf3=f1−Δfを満足させる周波数f3も存在する。更に、この成分は、究極的に混合信号に、即ち異なる周波数f3−f1=−Δfを有する仮想ミラー信号成分を発生させることに、寄与している。フィルタ10は、このようなミラー信号成分を抑圧することが望まれている。

【0008】

更に、中心周波数ωcに対してほぼ対称となる帯域通過特性を有することが望まれている。

【0009】

周波数特性が中心周波数ωc>0に対して対称であり、かつミラー信号成分を効果的に抑圧するバンドパス・フィルタを設計する既知の方法は、特性が設計しようとするバンドパス・フィルタの所望特性に対応するローパス・フィルタから開始する。

【0010】

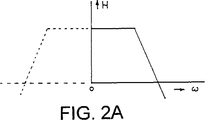

図2Aは、ローパス・フィルタの伝達特性を概要的に示す。周波数ωは水平軸上に示され、また伝達関数Hは垂直軸上に示される。実際には、周波数が0より高い信号のみが発生し、この部分の周波数特性を実線により示す。しかしながら、周波数特性は、周波数の符号に関係なく、図2Aに点線により示すように、ω=0に対して対称となることを意味する。

【0011】

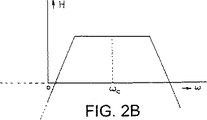

ローパス・フィルタは、前記ローパス・フィルタの設計によって、所望の特性、例えば1次、2次、又は更に高次、ベッセル形、バターワース形等を有することができる。所望の特性を有するローパス・フィルタから開始すると、フィルタ特性を高い周波数へ変換即ちシフトすることにより、帯域フィルタを導き出すことができる。図2Bは、距離ωcだけ高い周波数へシフトした図2Aの特性を示す。この帯域フィルタの同調周波数HBDF(ω)は、次式を満足する。

【0012】

【数1】

【0013】

フィルタ特性の所望シフトは、想像軸上の互いに同一距離で全ての極及び全てのゼロのシフトに対応する。周波数に依存したインピーダンスを有する部品が専らコンデンサであるフィルタ設計では、前記容量性フィルタ部品に対して並列の複素部品Xをスイッチングすることにより、これを達成可能であり、そのアドミッタンスYXは、次式により、一定の複素数となる。

【0014】

【数2】

【0015】

図2Cは、コンデンサCとこのような複素部品Xとの並列接続を概要的に示す。容量値Cを有する周波数に依存したコンデンサの従属アドミッタンスYCに対して、次式は、理想コンデンサの場合に成立する。

【0016】

【数3】

【0017】

図2Cの並列接続の周波数に依存したアドミッタンスYに対して、以下は有効である。

【数4】

【0018】

従って、周波数ωを有する信号の場合に、この並列回路の動作は、周波数ω−ωCにおけるコンデンサCの動作と同一である。従って、フィルタの全ての容量性フィルタ部品をこのような並列回路によって置換することにより、周波数ωにおける総合的なフィルタの動作は、周波数ω−ωCにおける元のフィルタの動作と同一となる。

【0019】

以上の演繹は、単一フィルタに既に適用している。そこで、このようにして帯域フィルタを実現するときの問題は、アドミッタンス(又は逆に:インピーダンス)が一定の複素数となる部品を得ることの問題に移行する。これは、それ自体可能であるが、多相フィルタでは、信号が互いに同一であるが、信号が互いに90°シフトされている、互いに同一の2つのフィルタ・チャネルが存在するという、都合のよい方法に使用することができる。そこで、このようなフィルタでは、各チャネルにおいて、アドミッタンスが実数であるが、その入力で他のチャネルから90°シフトされて受信する部品を使用することにより、複素部品Xの動作を獲得できる。

【0020】

多相帯域フィルタを構築するこのような解決方法は、米国特許第4、914、408号において既に説明されていた。そこでは、2つのフィルタ・チャネル間の実結合が図2Dに示すように、抵抗により実施される。その場合、各抵抗は、抵抗値R=ωc・Cを有する。

【0021】

しかしながら、既知の解決方法は、チップ上にフィルタを実現するときに得に問題となるいくつかの難点がある。プロセスのばらつきを原因として、フィルタの抵抗及びコンデンサは、比較的に大きな許容誤差を示す。従って、コンデンサ及び抵抗は、製造後、設定可能でなければならない。しかしながら、これは実現するのが困難である。

【0022】

本発明の概要的な目的は、前述の欠点を克服することである。

【0023】

特に、本発明の目的は、所望の周波数シフトを達成するために必要とする2つのフィルタ・チャネル間の結合を抵抗なしで実現する多相帯域フィルタを提供することである。

【0024】

本発明の重要な構成によれば、2フィルタ・チャネル間の結合は、電圧制御電流源により、実施される。本発明によるこの原理を図3Aに示す。図3Aにおいて、多相フィルタは、参照番号20により概括的に示す。フィルタ20は、互いに区別するために、それぞれI及びQにより示す互いに同一の2つのフィルタ・チャネル30を有する。各フィルタ・チャネル30I、30Qは、1入力及び1出力を有する。フィルタ・チャネル30I、30Qの設計は、適当とする任意の設計が可能であると同時に、フィルタ・チャネルに関する種々の構造それ自体が公知なので、図3Aに、フィルタ・チャネル30の完全な設計は、示していない。

【0025】

以下の説明のために、図3Aには、同相フィルタ・チャネル30Iの1容量性フィルタ部品CIを示し、かつ対応する直交フィルタ・チャネル30Qの容量性フィルタ部品CQを示す。2つの容量性フィルタ部品CI及びCQは、逆並列に接続された2つの電流源結合40QI及び40IQにより互いに接続されている。第1の電流源結合40QIは第1の電圧制御電流源41Iを備え、その出力は、同相フィルタ・チャネル30Iにおける容量性フィルタ部品CIに並列に接続され、一方、第2の電流源結合40IQは第2の電圧制御電流源41Qを備え、その出力は、直交フィルタ・チャネル30Qにおける容量性フィルタ部品CQに並列に接続されている。

【0026】

第1の電圧制御電流源41Iは、第1の電圧検出器42Qの出力信号により制御されており、その入力は、容量性フィルタ部品CQと並列に接続されている。同様に、第2の電圧制御電流源41Qは、第2の電圧検出器42Iにより制御されており、その入力は、容量性フィルタ部品CIと並列に接続されている。

【0027】

従って、第1の電圧制御電流源41Iは、値が第2のフィルタ・チャネル30Qにおける容量性フィルタ部品CQ上の電圧に従った電流を第1のフィルタ・チャネル30Iに加算し、一方、第2の電圧制御電流源41Qは、値が第1のフィルタ・チャネル30Iにおける容量性フィルタ部品CI上の電圧に従った電流を第2のフィルタ・チャネル30Qに加算する。

【0028】

2つの第1の電流源結合40QI及び40IQは、必須ではないが、互いに同一である。重要なことは、両電流源結合40QI及び40IQに関して、電圧検出器42により検出された電圧と電流源41により発生した電流との間の比例係数が互いに同一ということだけである。換言すれば、重要なことは、2つの電流源結合40QI及び40IQが互いに同一の伝達関数を有することだけである。これは、各電流源結合40QI及び40IQがそれぞれ電圧制御電流源41I及び41Qがそれぞれ電流I41、I及びI41、Qを発生するように設計されることを意味し、その電流値は、それぞれ次式に従ってそれぞれ電圧検出器42Q及び42Iによりそれぞれ検出された電圧VCO及びVCIに従う。

【0029】

【数5】

【0030】

ただし、Cはそれぞれ容量性フィルタ部品CI及びCQの容量値であり、またωCは、帯域フィルタの所望中心周波数である。

【0031】

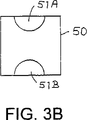

以下において、逆並列に接続された2つの電流源結合は、位相「ジャイレータ」により表され、また図3Bに示すシンボル50により表される。ジャイレータ50は、2つの端子51A及び51Bを有する。51Aから51Bへ接続する場合、ジャイレータ50は、図3Bに示していない第1の電流源結合を備え、その端子51Aは電圧入力であり、またその端子51Bは電流出力である。51Bから51Aへ接続する場合、ジャイレータ50は、図3Bに示していない第2の電流源結合を備え、その端子51Bは電圧入力であり、またその端子51Aは電流出力である。2つの電流源結合は、入力電圧により分流された出力電流として定義された比例係数GAB及びGBAをそれぞれ有する。両比例係数が互いに等しいとき、又は少なくとも同一特性を有するときは、ジャイレータを対称ジャイレータとして示す。両電流源結合が同一であれば、これを達成することができるが、必須ではない。

【0032】

図4は、本発明による多相フィルタ100の実施例を示す。多相フィルタ100は、同相チャネル101I及び直交チャネル101Qを備えており、これらは互にほぼ同一である。チャネル101I及び101Qは、同相入力信号ψI及び直交入力信号ψQを受け取る入力102I、102Qをそれぞれ有する。チャネル101I及び101Qは、更に同相出力信号ΨI及び直交出力信号ΨQを出力する出力103I、103Qをそれぞれ有する。入力102I、102Qは、電流入力である。即ち、入力信号ψI及びψQは電流信号である。フィルタ100が電圧信号を受け取りたいときは、入力102I、102Qの前の電圧・電流変換器を切り換えることができる。これには、それ自体公知の電圧・電流変換器を使用することができるので、ここで、これらをこれ以上説明しない。出力103I及び103Qは、電圧出力である。即ち、出力信号ΨI及びΨQは、電圧信号である。フィルタ100が電流信号を出力したいときは、出力103I、103Qの後の電圧・電流変換器を切り換えることができる。これには、それ自体公知の電圧・電流変換器を使用することができるので、ここでも、これらをこれ以上説明しない。

【0033】

チャネル101I及び101Qは、複数のNコンデンサC1I、C2I、C3I、…CNI、及びC1Q、C2Q、C3Q、…CNQをそれぞれ備えている。ただし、N≧2。

【0034】

同相チャネル101Iにおいて、連続する2つのコンデンサCiI及びC[i+1]Iは、ジャイレータ105iIにより常に接続されている。同様に、直交チャネル101Qにおいて、連続する2つのコンデンサCiQ及びC[i+1]Qは、ジャイレータ105iQにより常に接続されている。対応するジャイレータ105il及び105iQは、互いに同一である。ここで、「順方向」比例係数G(i→i+1)及び「逆方向」比例係数G(i+1→i)は、互いに同一である必要性はない。

【0035】

対応するコンデンサCiI及びCiQは、常に、互いに同一容量値Ciを有する。異なる値のiの場合、容量値Ciは異なっていてもよい。対応するコンデンサCiI及びCiQは、常に、対称ジャイレータ106iにより相互に接続されている。各ジャイレータ106iの比例係数GiIQ及びGiQIは、常に1/(ωc・Ci)に等しい。

【0036】

従って、本発明は、I−入力信号φI及びQ−入力信号φQをそれぞれ処理するフィルタ・チャネル30I、30Q;101I、101Qを有する多相フィルタ20、100を提供する。このフィルタは、2つのフィルタ・チャネル30I、30Q;101I、101Qにおいて互いに対応する少なくとも2つの容量性フィルタ部品CI、CQ;CiI、CiQを有し、これら2つの容量性フィルタ部品CI、CQ;CiI、CiQの容量値C;Ciは、互いにほぼ等しい。前記2つの容量性フィルタ部品CI、CQ;CiI、CiQは、逆並列にスイッチングされるほぼ等しい特性を有する2つの電流源結合40QI、40IQ;106iにより互いに接続されている。従って、更に高い周波数方向へ距離ωcだけフィルタ特性を遷移させることが達成される。

【0037】

本発明の範囲が以上で説明した例に限定されることないことは、当該技術分野に習熟する者にとって、明らかである。

【図面の簡単な説明】

【図1】 既知の受信機回路を概要的に示す。

【図2A】 ローパス・フィルタの伝送特性を概要的に示す。

【図2B】 図2Aの伝送特性から導き出したバンドパス・フィルタの伝送特性を概要的に示す。

【図2C】 コンデンサ及び複素部品の並列接続を概要的に示す。

【図2D】 2つのフィルタ・チャネルを結合する既知の方法を概要的に示す。

【図3A】 本発明によるカップリング原理を示す。

【図3B】 図3Aのカップリング・スケジュールの置換表示を示す。

【図4】 本発明による多相フィルタの一実施例の基本スケジュールである。

Claims (6)

- 所望のフィルタ特性を有するとともに、第1と第2の入力端子を有し、かつ、I入力信号(ΦI)を受け取る入力(31I、102I)、及び第1と第2の出力端子を有し、かつ、I出力信号(ΨI)を供給する出力(32I、103I)を有する第1のフィルタ・チャネル(30I;101I)と、

前記第1のフィルタ・チャネル(30I;101I)とほぼ同一であり、第3と第4の入力端子を有し、かつ、I入力信号(ΦI)に対して90°シフトされているQ入力信号(ΦQ)を受け取る入力(31Q;102Q)、及び第3と第4の出力端子を有し、かつ、I出力信号(ΨI)に対して90°シフトされているQ出力信号(ΨQ)を供給する出力(32Q、103Q)を有する第2のフィルタ・チャネル(30Q;101Q)と

を備えた多相フィルタ(20;100)であって、

前記第1のフィルタ・チャネル(30I;101 I)において、前記第1の入力端子及び前記第1の出力端子とが一方と接続され、前記第2の入力端子及び前記第2の出力端子とが他方と接続された第1容量性フィルタ部品(CI、CiI)と、

前記第2のフィルタ・チャネル(30Q;101Q)において、前記第3の入力端子及び前記第3の出力端子とが一方と接続され、前記第4の入力端子及び前記第4の出力端子とが他方と接続され、前記第1容量性フィルタ部の容量値とほぼ等しい容量値を有する第2容量性フィルタ部品(CQ、CiQ)と、

前記第1のフィルタ・チャネル(30 I ;101 I )において前記第1容量性フィルタ部品(C I 、Ci I )と並列に接続され、電流を出力する第1電圧制御電流源(41 I )と、前記第2のフィルタ・チャネル(30 Q ;101 Q )において前記第2容量性フィルタ部品(C Q 、Ci Q )と並列に接続され、かつ、検出した電圧を該第1電圧制御電流源(41 I )に出力する第1電圧検出器(42 Q )とを有する第1電流源結合(40 QI )と、

前記第2のフィルタ・チャネル(30 Q ;101 Q )において前記第2容量性フィルタ部品(C Q 、Ci Q )と並列に接続され、電流を出力する第2電圧制御電流源(41 Q )と、前記第1のフィルタ・チャネル(30 I ;101 I )において前記第1容量性フィルタ部品(C I 、Ci I )と並列に接続され、かつ、検出した電圧を該第2電圧制御電流源(41 Q )に出力する第2電圧検出器(42 I )とを有する第2電流源結合(40 IQ )と、をさらに備え、

前記第1電圧検出器(42 Q )は、前記第2電圧制御電流源(41 Q )と並列に接続され、

前記第2電圧検出器(42 I )は、前記第1電圧制御電流源(41 I )と並列に接続され、

前記第1電流源結合(40 QI )は、第1電圧検出器(42 Q )によって出力された電圧を入力として、前記第1のフィルタ・チャネル(30I;101 I)に電流を出力し、

前記第2電流源結合(40 IQ )は、第2電圧検出器(42 I )によって出力された電圧を入力として、前記第2のフィルタ・チャネル(30Q;101Q)に電流を出力する

ことを特徴とする多相フィルタ。 - 前記第1及び第2電圧制御電流源(41I、41Q)は、電流値が

I41,I=VCQ/(ωC・C)、I41,Q=VCI/(ωC・C)

をそれぞれ満足する電流(I41,I、I41,Q)を提供するように適応されていることを特徴とする請求項1に記載の多相フィルタ。 - 前記第1及び第2のフィルタ・チャネル(101I、101Q)は、前記第1電流源結合(40QI)及び前記第2電流源結合(40IQ)を含むジャイレータ(105iI、105iQ)と、該ジャイレータの入力及び出力に接続された前記第1容量性フィルタ部品及び前記第2容量性フィルタ部品(CiI及びC[i+1]I、CiQ及びC[i+1]Q)の組合わせを少なくとも1つ備えていることを特徴とする請求項1又は2に記載の多相フィルタ。

- 前記組合わせにおいて、

前記第1のフィルタ・チャネル(101I)の1つ目の前記第1容量性フィルタ部品(C[i+1]I)と、対応する前記第2のフィルタ・チャネル(101Q)の1つ目の前記第2容量性フィルタ部品(C[i+1]Q)とは、比例係数(GiIQ及びGiQI)が常に1/(ωc・Ci)に等しい対称的なジャイレータ(106I)に接続され、

前記第1のフィルタ・チャネル(101I)の2つ目の前記第1容量性フィルタ部品(CiI)と、対応する第2のフィルタ・チャネル(101Q)の2つ目の前記第2容量性フィルタ部品(CiQ)とは、比例係数(G[i+1]IQ及びG[i+1]QI)が常に1/(ωc・C[i+1])に等しい対称的なジャイレータ(106[i+1])に接続されていることを特徴とする請求項3に記載の多相フィルタ。 - 前記第1のフィルタ・チャネル(30I;101I)は、複数の前記第1容量性フィルタ部品(CiI)を有し、

前記第2のフィルタ・チャネル(30Q;101Q)は、複数の前記第2容量性フィルタ部品(CiQ)を有し、

前記第1容量性フィルタ部品と対応する前記第2容量性フィルタ部品の組合わせごとに、前記第1電流結合(40QI)と前記第2電流結合(40IQ)とが設けられることを特徴とする請求項1乃至4の何れか1項に記載の多相フィルタ。 - 個々のフィルタ・チャネル(30I、30Q;101I、101Q)は、それぞれローパス・フィルタ特性を有し、前記多相フィルタ(20;100)は、前記第1及び第2電流源結合(40QI、40IQ;106i)により発生されるバンドパス・フィルタ特性を有する請求項1乃至5の何れか1項に記載の多相フィルタ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| NL1013951 | 1999-12-24 | ||

| NL1013951A NL1013951C2 (nl) | 1999-12-24 | 1999-12-24 | Polyfase filter. |

| PCT/IB2000/001975 WO2001048918A2 (en) | 1999-12-24 | 2000-12-22 | Polyphase filter |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003518863A JP2003518863A (ja) | 2003-06-10 |

| JP2003518863A5 JP2003518863A5 (ja) | 2008-02-28 |

| JP4763206B2 true JP4763206B2 (ja) | 2011-08-31 |

Family

ID=19770510

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001548523A Expired - Fee Related JP4763206B2 (ja) | 1999-12-24 | 2000-12-22 | 多相フィルタ |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US6346850B2 (ja) |

| EP (1) | EP1247339B1 (ja) |

| JP (1) | JP4763206B2 (ja) |

| CN (1) | CN1183672C (ja) |

| AT (1) | ATE250824T1 (ja) |

| AU (1) | AU2019901A (ja) |

| DE (1) | DE60005561T2 (ja) |

| MY (1) | MY121473A (ja) |

| NL (1) | NL1013951C2 (ja) |

| WO (1) | WO2001048918A2 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20030128068A1 (en) * | 2001-08-16 | 2003-07-10 | Farbod Behbahani | Low noise image-reject gm-c filter |

| JP2005522906A (ja) * | 2002-04-11 | 2005-07-28 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 積分器付きポリフェーズフィルタ |

| CN1628411B (zh) * | 2002-06-03 | 2010-05-26 | 艾利森电话股份有限公司 | 放大器电路、回转器电路、滤波器装置和放大信号的方法 |

| CN100426670C (zh) * | 2002-08-15 | 2008-10-15 | 联发科技股份有限公司 | 多相滤波器电路 |

| US7098731B1 (en) | 2004-01-13 | 2006-08-29 | Wyszynski Adam S | Synthesis method for an active polyphase filter |

| DE102004030229A1 (de) * | 2004-06-23 | 2006-01-19 | Infineon Technologies Ag | Funkabfragbarer Datenträger |

| US7689189B2 (en) * | 2005-04-06 | 2010-03-30 | Silicon Laboratories Inc. | Circuit and method for signal reception using a low intermediate frequency reception |

| US7196574B1 (en) * | 2005-06-22 | 2007-03-27 | Vishinsky Adam S | Active polyphase ladder filters with transmission zeros and their synthesis method |

| US7973861B2 (en) * | 2007-04-19 | 2011-07-05 | Newport Media, Inc. | Universal tuner for mobile TV |

| US8412141B2 (en) * | 2009-10-19 | 2013-04-02 | Qualcomm Incorporated | LR polyphase filter |

| DE102010031535A1 (de) | 2010-07-19 | 2012-01-19 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Bildaufnahmevorrichtung und Verfahren zum Aufnehmen eines Bildes |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1070482A (ja) * | 1996-03-19 | 1998-03-10 | Philips Electron Nv | 受信機 |

| WO1999016179A2 (en) * | 1997-09-25 | 1999-04-01 | Koninklijke Philips Electronics N.V. | Improvements in or relating to phasing receivers |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| NL8801412A (nl) | 1988-06-02 | 1990-01-02 | Philips Nv | Asymmetrisch polyfase filter. |

| JP4148992B2 (ja) * | 1995-04-03 | 2008-09-10 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | 直角位相信号変換装置 |

-

1999

- 1999-12-24 NL NL1013951A patent/NL1013951C2/nl not_active IP Right Cessation

-

2000

- 2000-12-21 US US09/741,014 patent/US6346850B2/en not_active Expired - Lifetime

- 2000-12-22 DE DE60005561T patent/DE60005561T2/de not_active Expired - Lifetime

- 2000-12-22 JP JP2001548523A patent/JP4763206B2/ja not_active Expired - Fee Related

- 2000-12-22 EP EP00983445A patent/EP1247339B1/en not_active Expired - Lifetime

- 2000-12-22 CN CN00817695.7A patent/CN1183672C/zh not_active Expired - Fee Related

- 2000-12-22 WO PCT/IB2000/001975 patent/WO2001048918A2/en active Search and Examination

- 2000-12-22 AT AT00983445T patent/ATE250824T1/de not_active IP Right Cessation

- 2000-12-22 AU AU20199/01A patent/AU2019901A/en not_active Abandoned

- 2000-12-22 MY MYPI20006104A patent/MY121473A/en unknown

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1070482A (ja) * | 1996-03-19 | 1998-03-10 | Philips Electron Nv | 受信機 |

| WO1999016179A2 (en) * | 1997-09-25 | 1999-04-01 | Koninklijke Philips Electronics N.V. | Improvements in or relating to phasing receivers |

Also Published As

| Publication number | Publication date |

|---|---|

| DE60005561T2 (de) | 2004-04-29 |

| AU2019901A (en) | 2001-07-09 |

| JP2003518863A (ja) | 2003-06-10 |

| CN1413379A (zh) | 2003-04-23 |

| US6346850B2 (en) | 2002-02-12 |

| ATE250824T1 (de) | 2003-10-15 |

| EP1247339B1 (en) | 2003-09-24 |

| EP1247339A2 (en) | 2002-10-09 |

| WO2001048918A3 (en) | 2002-03-07 |

| MY121473A (en) | 2006-01-28 |

| NL1013951C2 (nl) | 2001-07-02 |

| WO2001048918A2 (en) | 2001-07-05 |

| US20010013807A1 (en) | 2001-08-16 |

| CN1183672C (zh) | 2005-01-05 |

| DE60005561D1 (en) | 2003-10-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100341231B1 (ko) | 이상기 | |

| Crols et al. | Low-IF topologies for high-performance analog front ends of fully integrated receivers | |

| EP0185416B1 (en) | Radio receiver/transmitter filters | |

| KR100466471B1 (ko) | 집적수신기 | |

| JP3948533B2 (ja) | 多相フィルタからなる受信機及びフィルタ配置 | |

| US5434541A (en) | Frequency translated filter for a micro-miniature radio receiver | |

| JP2002512471A (ja) | ダイレクト変換受信機 | |

| JP4763206B2 (ja) | 多相フィルタ | |

| US5877643A (en) | Phase shift amplifier and its applications to a recombining circuit | |

| JP2001358537A (ja) | 映像周波数を強固に排除する低ノイズ周波数コンバータ | |

| CN110545077B (zh) | 对阻挠者具有高免疫的降频转换器及其方法 | |

| KR20040043190A (ko) | 이미지 주파수 제거기능을 갖는 믹서 회로, 특히, 영 또는낮은 중간 주파수를 갖는 고주파 수신기 | |

| US20050157826A1 (en) | Filtering signals | |

| JP2008067090A (ja) | 周波数変換器 | |

| EP1064720B1 (en) | Demodulator circuits | |

| CN100426670C (zh) | 多相滤波器电路 | |

| Hintea et al. | On the design of a reconfigurable OTA-C filter for software radio | |

| US6714602B1 (en) | Demodulator and receiver | |

| JPWO2005064787A1 (ja) | 周波数変換器 | |

| KR20010021467A (ko) | 이상기 및 이를 이용한 복조기 | |

| JPS62292005A (ja) | Fm復調回路 | |

| JP2001069182A (ja) | Am復調方式 | |

| JPH01282909A (ja) | 周波数変換器 | |

| JP2002076795A (ja) | 増幅回路及びそれを用いた衛星放送受信装置 | |

| JPH07115329A (ja) | 乗算回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20060411 |

|

| RD05 | Notification of revocation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7425 Effective date: 20060629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071217 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20071217 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100709 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101008 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110124 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110415 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110603 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110609 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140617 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 Ref document number: 4763206 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |