JP4700160B2 - Semiconductor device - Google Patents

Semiconductor device Download PDFInfo

- Publication number

- JP4700160B2 JP4700160B2 JP2000069563A JP2000069563A JP4700160B2 JP 4700160 B2 JP4700160 B2 JP 4700160B2 JP 2000069563 A JP2000069563 A JP 2000069563A JP 2000069563 A JP2000069563 A JP 2000069563A JP 4700160 B2 JP4700160 B2 JP 4700160B2

- Authority

- JP

- Japan

- Prior art keywords

- film

- conductive

- substrate

- insulating film

- line side

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 221

- 239000010408 film Substances 0.000 claims description 529

- 239000000758 substrate Substances 0.000 claims description 176

- 239000010410 layer Substances 0.000 claims description 161

- 239000004973 liquid crystal related substance Substances 0.000 claims description 58

- 239000000463 material Substances 0.000 claims description 34

- 239000011159 matrix material Substances 0.000 claims description 20

- 239000002245 particle Substances 0.000 claims description 14

- 239000010409 thin film Substances 0.000 claims description 14

- 239000013078 crystal Substances 0.000 claims description 12

- 238000013461 design Methods 0.000 claims description 9

- 239000012528 membrane Substances 0.000 claims 4

- 238000000034 method Methods 0.000 description 165

- 239000012535 impurity Substances 0.000 description 73

- 230000008569 process Effects 0.000 description 61

- 238000004519 manufacturing process Methods 0.000 description 56

- 238000005530 etching Methods 0.000 description 52

- 230000015572 biosynthetic process Effects 0.000 description 36

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 31

- 229910052710 silicon Inorganic materials 0.000 description 31

- 238000004544 sputter deposition Methods 0.000 description 31

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 30

- 239000010703 silicon Substances 0.000 description 30

- 238000010438 heat treatment Methods 0.000 description 28

- 239000010936 titanium Substances 0.000 description 28

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N silicon dioxide Inorganic materials O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 27

- 239000011521 glass Substances 0.000 description 26

- 239000003990 capacitor Substances 0.000 description 25

- 229910021417 amorphous silicon Inorganic materials 0.000 description 24

- 239000004020 conductor Substances 0.000 description 24

- 229910052698 phosphorus Inorganic materials 0.000 description 24

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 23

- 239000011574 phosphorus Substances 0.000 description 23

- 238000002425 crystallisation Methods 0.000 description 21

- 238000006243 chemical reaction Methods 0.000 description 20

- 238000012545 processing Methods 0.000 description 19

- 229910052814 silicon oxide Inorganic materials 0.000 description 18

- 239000012298 atmosphere Substances 0.000 description 16

- 230000003197 catalytic effect Effects 0.000 description 16

- 239000007789 gas Substances 0.000 description 16

- 230000008025 crystallization Effects 0.000 description 15

- 238000010586 diagram Methods 0.000 description 15

- 239000003054 catalyst Substances 0.000 description 13

- 229910052751 metal Inorganic materials 0.000 description 13

- 239000002184 metal Substances 0.000 description 13

- 238000000206 photolithography Methods 0.000 description 13

- 238000003860 storage Methods 0.000 description 13

- 229910052719 titanium Inorganic materials 0.000 description 13

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- 239000000956 alloy Substances 0.000 description 11

- 229910052739 hydrogen Inorganic materials 0.000 description 11

- 239000011347 resin Substances 0.000 description 11

- 229920005989 resin Polymers 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- XYFCBTPGUUZFHI-UHFFFAOYSA-N Phosphine Chemical compound P XYFCBTPGUUZFHI-UHFFFAOYSA-N 0.000 description 10

- 229910045601 alloy Inorganic materials 0.000 description 10

- 239000001257 hydrogen Substances 0.000 description 10

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 9

- 125000004429 atom Chemical group 0.000 description 9

- 230000007547 defect Effects 0.000 description 9

- 239000010453 quartz Substances 0.000 description 9

- 229910052782 aluminium Inorganic materials 0.000 description 8

- 230000004888 barrier function Effects 0.000 description 8

- 239000011651 chromium Substances 0.000 description 8

- 239000010949 copper Substances 0.000 description 8

- 230000005611 electricity Effects 0.000 description 8

- 230000003068 static effect Effects 0.000 description 8

- 229910052715 tantalum Inorganic materials 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 7

- 239000000460 chlorine Substances 0.000 description 7

- 239000011810 insulating material Substances 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 7

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 6

- 230000001133 acceleration Effects 0.000 description 6

- 238000000137 annealing Methods 0.000 description 6

- 229910052804 chromium Inorganic materials 0.000 description 6

- 238000001312 dry etching Methods 0.000 description 6

- 239000010931 gold Substances 0.000 description 6

- 229910021424 microcrystalline silicon Inorganic materials 0.000 description 6

- 239000012495 reaction gas Substances 0.000 description 6

- 239000002356 single layer Substances 0.000 description 6

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 6

- XLOMVQKBTHCTTD-UHFFFAOYSA-N zinc oxide Inorganic materials [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 230000015556 catabolic process Effects 0.000 description 5

- 229910052802 copper Inorganic materials 0.000 description 5

- 229910021419 crystalline silicon Inorganic materials 0.000 description 5

- 229910052736 halogen Inorganic materials 0.000 description 5

- 150000002367 halogens Chemical class 0.000 description 5

- 150000002500 ions Chemical class 0.000 description 5

- 239000012299 nitrogen atmosphere Substances 0.000 description 5

- 229910000073 phosphorus hydride Inorganic materials 0.000 description 5

- 230000035882 stress Effects 0.000 description 5

- 238000002230 thermal chemical vapour deposition Methods 0.000 description 5

- 238000001039 wet etching Methods 0.000 description 5

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 4

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 4

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 4

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 4

- BOTDANWDWHJENH-UHFFFAOYSA-N Tetraethyl orthosilicate Chemical compound CCO[Si](OCC)(OCC)OCC BOTDANWDWHJENH-UHFFFAOYSA-N 0.000 description 4

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 4

- 239000005407 aluminoborosilicate glass Substances 0.000 description 4

- 229910052788 barium Inorganic materials 0.000 description 4

- DSAJWYNOEDNPEQ-UHFFFAOYSA-N barium atom Chemical compound [Ba] DSAJWYNOEDNPEQ-UHFFFAOYSA-N 0.000 description 4

- 230000000903 blocking effect Effects 0.000 description 4

- 239000005388 borosilicate glass Substances 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 238000005247 gettering Methods 0.000 description 4

- 238000005499 laser crystallization Methods 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 238000002156 mixing Methods 0.000 description 4

- 229910052750 molybdenum Inorganic materials 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 229920001721 polyimide Polymers 0.000 description 4

- 230000001681 protective effect Effects 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 239000000243 solution Substances 0.000 description 4

- 229910052721 tungsten Inorganic materials 0.000 description 4

- ZAMOUSCENKQFHK-UHFFFAOYSA-N Chlorine atom Chemical compound [Cl] ZAMOUSCENKQFHK-UHFFFAOYSA-N 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 3

- 229910052779 Neodymium Inorganic materials 0.000 description 3

- 239000004642 Polyimide Substances 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 229910052801 chlorine Inorganic materials 0.000 description 3

- 238000011109 contamination Methods 0.000 description 3

- 230000006866 deterioration Effects 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 3

- 238000009616 inductively coupled plasma Methods 0.000 description 3

- 238000010030 laminating Methods 0.000 description 3

- 239000007769 metal material Substances 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- 150000004767 nitrides Chemical class 0.000 description 3

- 229910052757 nitrogen Inorganic materials 0.000 description 3

- 230000010355 oscillation Effects 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 3

- 238000007650 screen-printing Methods 0.000 description 3

- 229910021332 silicide Inorganic materials 0.000 description 3

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 3

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 3

- 238000009751 slip forming Methods 0.000 description 3

- 125000006850 spacer group Chemical group 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 238000001771 vacuum deposition Methods 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 239000004988 Nematic liquid crystal Substances 0.000 description 2

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 2

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 2

- 239000004990 Smectic liquid crystal Substances 0.000 description 2

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 2

- NIXOWILDQLNWCW-UHFFFAOYSA-N acrylic acid group Chemical group C(C=C)(=O)O NIXOWILDQLNWCW-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 239000000853 adhesive Substances 0.000 description 2

- 230000001070 adhesive effect Effects 0.000 description 2

- 239000003513 alkali Substances 0.000 description 2

- 229910052786 argon Inorganic materials 0.000 description 2

- 229910052785 arsenic Inorganic materials 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- IVHJCRXBQPGLOV-UHFFFAOYSA-N azanylidynetungsten Chemical compound [W]#N IVHJCRXBQPGLOV-UHFFFAOYSA-N 0.000 description 2

- 239000002585 base Substances 0.000 description 2

- UMIVXZPTRXBADB-UHFFFAOYSA-N benzocyclobutene Chemical compound C1=CC=C2CCC2=C1 UMIVXZPTRXBADB-UHFFFAOYSA-N 0.000 description 2

- 238000009125 cardiac resynchronization therapy Methods 0.000 description 2

- 239000003795 chemical substances by application Substances 0.000 description 2

- 150000001875 compounds Chemical class 0.000 description 2

- 238000006356 dehydrogenation reaction Methods 0.000 description 2

- 238000007599 discharging Methods 0.000 description 2

- 238000007687 exposure technique Methods 0.000 description 2

- 230000002349 favourable effect Effects 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 238000005984 hydrogenation reaction Methods 0.000 description 2

- 230000001771 impaired effect Effects 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- LQJIDIOGYJAQMF-UHFFFAOYSA-N lambda2-silanylidenetin Chemical compound [Si].[Sn] LQJIDIOGYJAQMF-UHFFFAOYSA-N 0.000 description 2

- 238000003475 lamination Methods 0.000 description 2

- 238000005224 laser annealing Methods 0.000 description 2

- WABPQHHGFIMREM-UHFFFAOYSA-N lead(0) Chemical compound [Pb] WABPQHHGFIMREM-UHFFFAOYSA-N 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 238000002161 passivation Methods 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229910000077 silane Inorganic materials 0.000 description 2

- 238000004528 spin coating Methods 0.000 description 2

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 238000007740 vapor deposition Methods 0.000 description 2

- OYQCBJZGELKKPM-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O-2].[Zn+2].[O-2].[In+3] OYQCBJZGELKKPM-UHFFFAOYSA-N 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 1

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- XEEYBQQBJWHFJM-UHFFFAOYSA-N Iron Chemical compound [Fe] XEEYBQQBJWHFJM-UHFFFAOYSA-N 0.000 description 1

- 229910021578 Iron(III) chloride Inorganic materials 0.000 description 1

- GRYLNZFGIOXLOG-UHFFFAOYSA-N Nitric acid Chemical compound O[N+]([O-])=O GRYLNZFGIOXLOG-UHFFFAOYSA-N 0.000 description 1

- 239000004952 Polyamide Substances 0.000 description 1

- 238000001069 Raman spectroscopy Methods 0.000 description 1

- 229910006404 SnO 2 Inorganic materials 0.000 description 1

- 230000003213 activating effect Effects 0.000 description 1

- 229910052783 alkali metal Inorganic materials 0.000 description 1

- 150000001340 alkali metals Chemical class 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 238000000149 argon plasma sintering Methods 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000000919 ceramic Substances 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 239000011248 coating agent Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000011889 copper foil Substances 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 238000001723 curing Methods 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 238000007872 degassing Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 239000010432 diamond Substances 0.000 description 1

- 229910003460 diamond Inorganic materials 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000001035 drying Methods 0.000 description 1

- 239000007772 electrode material Substances 0.000 description 1

- 238000007772 electroless plating Methods 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000010574 gas phase reaction Methods 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 230000006872 improvement Effects 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- RBTARNINKXHZNM-UHFFFAOYSA-K iron trichloride Chemical compound Cl[Fe](Cl)Cl RBTARNINKXHZNM-UHFFFAOYSA-K 0.000 description 1

- 239000003550 marker Substances 0.000 description 1

- 239000011259 mixed solution Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 1

- 229910017604 nitric acid Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000003647 oxidation Effects 0.000 description 1

- 238000007254 oxidation reaction Methods 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 230000003071 parasitic effect Effects 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 238000000016 photochemical curing Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 229920002647 polyamide Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 239000009719 polyimide resin Substances 0.000 description 1

- 238000007639 printing Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 238000004151 rapid thermal annealing Methods 0.000 description 1

- 230000003014 reinforcing effect Effects 0.000 description 1

- 229910052706 scandium Inorganic materials 0.000 description 1

- SIXSYDAISGFNSX-UHFFFAOYSA-N scandium atom Chemical compound [Sc] SIXSYDAISGFNSX-UHFFFAOYSA-N 0.000 description 1

- 238000007789 sealing Methods 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 239000010935 stainless steel Substances 0.000 description 1

- 229910001220 stainless steel Inorganic materials 0.000 description 1

- 230000008646 thermal stress Effects 0.000 description 1

- 229910021341 titanium silicide Inorganic materials 0.000 description 1

- 238000002834 transmittance Methods 0.000 description 1

- WQJQOUPTWCFRMM-UHFFFAOYSA-N tungsten disilicide Chemical compound [Si]#[W]#[Si] WQJQOUPTWCFRMM-UHFFFAOYSA-N 0.000 description 1

- NXHILIPIEUBEPD-UHFFFAOYSA-H tungsten hexafluoride Chemical compound F[W](F)(F)(F)(F)F NXHILIPIEUBEPD-UHFFFAOYSA-H 0.000 description 1

- 229910021342 tungsten silicide Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/1333—Constructional arrangements; Manufacturing methods

- G02F1/1345—Conductors connecting electrodes to cell terminals

- G02F1/13452—Conductors connecting driver circuitry and terminals of panels

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1237—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a different composition, shape, layout or thickness of the gate insulator in different devices

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/124—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs with a particular composition, shape or layout of the wiring layers specially adapted to the circuit arrangement, e.g. scanning lines in LCD pixel circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1255—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs integrated with passive devices, e.g. auxiliary capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1214—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having at least one potential-jump barrier or surface barrier; including integrated passive circuit elements with at least one potential-jump barrier or surface barrier the substrate being other than a semiconductor body, e.g. an insulating body comprising a plurality of TFTs formed on a non-semiconducting substrate, e.g. driving circuits for AMLCDs

- H01L27/1259—Multistep manufacturing methods

- H01L27/1288—Multistep manufacturing methods employing particular masking sequences or specially adapted masks, e.g. half-tone mask

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66757—Lateral single gate single channel transistors with non-inverted structure, i.e. the channel layer is formed before the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66409—Unipolar field-effect transistors

- H01L29/66477—Unipolar field-effect transistors with an insulated gate, i.e. MISFET

- H01L29/66742—Thin film unipolar transistors

- H01L29/6675—Amorphous silicon or polysilicon transistors

- H01L29/66765—Lateral single gate single channel transistors with inverted structure, i.e. the channel layer is formed after the gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78675—Polycrystalline or microcrystalline silicon transistor with normal-type structure, e.g. with top gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/7866—Non-monocrystalline silicon transistors

- H01L29/78672—Polycrystalline or microcrystalline silicon transistor

- H01L29/78678—Polycrystalline or microcrystalline silicon transistor with inverted-type structure, e.g. with bottom gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78606—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device

- H01L29/78618—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure

- H01L29/78621—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile

- H01L2029/7863—Thin film transistors, i.e. transistors with a channel being at least partly a thin film with supplementary region or layer in the thin film or in the insulated bulk substrate supporting it for controlling or increasing the safety of the device characterised by the drain or the source properties, e.g. the doping structure, the composition, the sectional shape or the contact structure with LDD structure or an extension or an offset region or characterised by the doping profile with an LDD consisting of more than one lightly doped zone or having a non-homogeneous dopant distribution, e.g. graded LDD

Description

【0001】

【発明の属する技術分野】

本願発明は薄膜トランジスタ(以下、TFTという)で構成された回路を有する半導体装置およびその作製方法に関する。特に、表示部を形成する画素領域における各画素の構成と、該画素に信号伝達する駆動回路の構成に関する。例えば、液晶表示パネルに代表される電気光学装置およびその様な電気光学装置を部品として搭載した電子機器に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器をその範疇に含むものとする。

【0003】

【従来の技術】

画像表示装置として液晶表示装置が知られている。パッシブ型の液晶表示装置に比べ高精細な画像が得られることからアクティブマトリクス型の液晶表示装置が多く用いられるようになっている。アクティブマトリクス型の液晶表示装置においては、マトリクス状に配置された画素に電圧を印加することにより液晶の配向を制御して、画面上に画像情報を表示する仕組みになっている。

【0004】

このようなアクティブマトリクス型液晶表示装置は、ノート型パーソナルコンピュータ(ノートパソコン)やモバイルコンピュータ、携帯電話などの携帯型情報端末をはじめ、液晶テレビなどの様々な電子機器に利用され広く普及している。このような表示装置はCRTと比較して軽量薄型化が可能であり、用途によっては画面の大面積化や画素数の高密度化が要求されている。

【0005】

非晶質シリコンに代表される非晶質半導体膜でTFTのチャネル形成領域などを形成する技術は生産性に優れている。非晶質半導体膜は、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどの比較的安価で大面積の基板に形成できる特徴を有している。しかしながら、非晶質シリコン膜でチャネル形成領域を形成したTFTの電界効果移動度は、大きくとも1cm2/Vsec程度しか得ることができない。そのため、画素領域に設けるスイッチング用のTFT(画素TFT)としては利用できるが、駆動回路を形成して所望の動作をさせることはできなかった。従って、画素に印加する電圧を信号に応じて制御する駆動回路は、単結晶シリコン基板で作製したICチップ(ドライバIC)を用い、画素領域の周辺にTAB(Tape Automated bonding)方式やCOG(Chip on Glass)方式で実装されている。

【0006】

TAB方式は可撓性の絶縁基板上に銅箔などで配線を形成し、その上にICチップを直接装着したものであり、可撓性基板の一方の端が表示装置の入力端子に接続して実装する方法である。一方、COG方式はICチップを表示装置の基板上に形成した配線のパターンに合わせて直接貼り合わせて接続する方式である。

【0007】

また、駆動回路を実装するその他の方法として、特開平7−014880号公報や特開平11−160734号公報にはガラスや石英などの基板上に非単結晶半導体材料で作製したTFTで駆動回路を形成し、短冊状に分割して(以下、このように短冊状に切り出された駆動回路を有する基板をスティックドライバという)、表示装置の基板上に実装する技術が開示されている。

【0008】

いずれにしても、画素領域が形成された基板に駆動回路を実装する領域は可能な限り小さい方が好ましく、駆動回路の実装方法には配線のレイアウトなどを含め様々な工夫が凝らされている。

【0009】

【発明が解決しようとする課題】

テレビやパーソナルコンピュータのモニタとして、これまではCRTが最も使用されてきた。しかし、省スペースや低消費電力化の観点から、それが液晶表示装置に置き換えられていくにつれ、液晶表示装置に対しては画面の大面積化や高精細化が推進される一方で製造コストの削減が求められてきた。

【0010】

アクティブマトリクス型の表示装置は、画素TFTの作製に写真蝕刻(フォトリソグラフィー)技術を用い、少なくとも5枚のフォトマスクを使用している。フォトマスクはフォトリソグラフィーの技術において、エッチング工程のマスクとするフォトレジストパターンを基板上に形成するために用いている。このフォトマスクを1枚使用することによって、レジスト塗布、プレベーク、露光、現像、ポストベークなどの工程と、その前後の工程において、被膜の成膜およびエッチングなどの工程、さらにレジスト剥離、洗浄や乾燥工程などが付加され、製造に係わる作業は煩雑なものとなり問題となっていた。

【0011】

生産性を向上させ歩留まりを向上させるためには、工程数を削減することが有効な手段として考えられる。しかし、フォトマスクの数を減らさない限りは、製造コストの削減にも限界があった。

【0012】

また、基板が絶縁体であるために製造工程中における摩擦などによって静電気が発生していた。この静電気が発生すると基板上に設けられた配線の交差部でショートしたり、静電気によってTFTが劣化または破壊されて電気光学装置に表示欠陥や画質の劣化が生じていた。特に、製造工程で行われる液晶配向処理のラビング時に静電気が発生し問題となっていた。

【0013】

その他に、画素数が増加すると実装するICチップの数も必然的に多くなる。RGBフルカラー表示のXGAパネルでは、画素領域のソース線側の端子数だけで約3000個となり、それがUXGAでは4800個必要となる。ICチップのサイズは製造プロセスにおけるウエハーサイズで限定され、実用的なサイズとして長辺が20mm程度のものが限度となる。このICチップは出力端子のピッチを50μmとしても、1個のICチップで400個の接続端子しか賄うことができない。上述のXGAパネルではソース線側だけでICチップが8個程度、UXGAパネルでは12個が必要となる。

【0014】

長尺のICチップを作製する方法も考えられるが、短冊状のICチップは円形のシリコンウエハーから取り出すことのできる数が必然的に減ってしまい実用に即さない。さらに、シリコンウエハー自体が脆い性質なので、あまり長尺のものを作製すると破損してしまう確率が増大する。また、ICチップの実装には位置合わせの精度や、端子部のコンタクト抵抗を低くする必要がある。1枚のパネルに貼り付けるICチップの数が増えると、不良の発生率が増え、その工程における歩留まりを低下させる懸念がある。その他にも、ICチップの基体となっているシリコンと画素領域が形成されているガラス基板との温度係数か異なるため、貼り合わせた後にたわみなどが発生し、コンタクト抵抗の増大といった直接的な不良の他に、発生する応力によって素子の信頼性が低下する要因になる。

【0015】

一方、スティックドライバは画素領域と同等の長さの駆動回路を形成することも可能であり、一つのスティックドライバで駆動回路を形成して実装することもできる。しかしながら、回路部の面積が増えると、一つの点欠陥で不良となってしまうスティックドライバの数が増加するので、1枚の基板から取り出すことのできる数が減少し、工程歩留まりが低下を招いてしまう。

【0016】

生産性の観点からは、大面積のガラス基板や石英基板上に結晶質半導体膜から作製するTFTで多数のスティックドライバを形成する方法は優れていると考えられる。しかし、走査線側とソース線側では回路の駆動周波数が異なり、また、印加する駆動電圧の値も異なっている。具体的には、走査線側のスティックドライバのTFTには30V程度の耐圧が要求されるものの、駆動周波数は100kHz以下であり高速性は要求されない。ソース線側のスティックドライバのTFTの耐圧は12V程度あれば十分であるが、駆動周波数は3Vにて65MHz程度であり高速動作が要求される。このように、要求される仕様の違いによりスティックドライバおよび該ドライバ内のTFTの構造を適切に作り分ける必要がある。

【0017】

このような背景を基にして、本発明は液晶表示装置の画素TFTを作製する工程数を削減して製造コストの低減および歩留まりの向上を実現することを第1の課題とする。また、各回路が要求する特性を満たすTFTで形成した駆動回路をガラス基板などの大面積基板に一括に形成する方法と、そのような駆動回路を実装した表示装置を提供し、信頼性と生産性を向上させる技術を提供することを第2の課題とする。

【0018】

【課題を解決するための手段】

上記課題を解決するための第1の手段は、画素領域に形成する画素TFTをチャネルエッチ型の逆スタガ型TFTで形成し、ソース領域及びドレイン領域のパターニングと画素電極のパターニングを同じフォトマスクで行うことを特徴とする。

【0019】

本発明の画素TFTの作製方法を図1を参照して簡略に説明する。まず、第1のマスク(フォトマスク1枚目)でゲート配線102と容量配線103のパターンを形成する。次いで、絶縁膜(ゲート絶縁膜)、第1の半導体膜、一導電型の第2の半導体膜、第1の導電膜を順次積層形成する。

【0020】

第2のマスク(フォトマスク2枚目)で第1の導電膜、一導電型の第2の半導体膜、第1の半導体膜を所定の形状にエッチングして、画素TFTのチャネル形成領域やソースまたはドレイン領域を確定すると共に、ソース配線やドレイン電極のパターンを形成する。その後、画素電極を形成するための第2の導電膜を形成する。

【0021】

第3のマスク(フォトマスク3枚目)で第2の導電膜をエッチングして画素電極119を形成する。さらに、画素TFTのチャネル形成領域上に残存する第1の導電膜と一導電型の第2の半導体膜をエッチングして除去する。このエッチング処理では、エッチングの選択比が大きくとれないので第1の半導体膜も一部がエッチングされる。

【0022】

このような工程により、画素TFTの作製に必要なフォトマスクの数を3枚とすることができる。画素TFT上に保護絶縁膜を形成する場合には、画素電極に開口を設ける必要から、もう1枚フォトマスクが必要となる。ソース配線は画素電極と同じ材料である第2の導電膜で覆い、基板全体を外部の静電気等から保護する構造とすることもできる。また、この第2の導電膜を用いて画素TFT部以外の領域に保護回路を形成する構造としてもよい。このような構成とすることで、製造工程において製造装置と絶縁体基板との摩擦による静電気の発生を防止することができる。特に、製造工程で行われる液晶配向処理のラビング時に発生する静電気からTFT等を保護することができる。

【0023】

反射型の液晶表示装置では、明るい表示を得るために画素電極の表面を凹凸化して、最適な反射特性を有する画素電極を形成する方法がある。本発明はこのような反射型の液晶表示装置にも適用し得るものであり、そのためにフォトマスクを増やすことを必要としない。画素電極の表面を凹凸化する方法として、ゲート配線を形成するときに、画素電極の下方の領域に島状に分離されたパターンを形成しておく手法を用いる。そのパターン上にはゲート絶縁膜と画素電極の層が形成されるのみであるので、パターンに対応した凹凸形状を画素電極の表面に形成することができる。

【0024】

上記課題を解決するための第2の手段は、画素領域が形成された第1の基板と、対向電極が形成された第2の基板とを有する表示装置において、結晶質半導体層を有するTFTを用いて形成される駆動回路と該駆動回路に従属する入出力端子を一つのユニットとしたものを、第3の基板上に複数個形成し、その後第3の基板を個々のユニット毎に分割して得られるスティックドライバを、第1の基板に実装することを特徴とする。

【0025】

スティックドライバの各回路の構成は、走査線側とソース線側で異なるものとし、要求される回路特性に応じてTFTのゲート絶縁膜の厚さやチャネル長などを異ならせたものとする。例えば、シフトレジスタ回路、レベルシフタ回路、バッファ回路から構成する走査線のスティックドライバでは、30Vの耐圧が要求されるバッファ回路のTFTはシフトレジスタ回路のTFTよりもゲート絶縁膜を厚く形成する。また、シフトレジスタ回路、ラッチ回路、レベルシフタ回路、D/A変換回路から構成されるソース線側のスティックドライバは、高周波数で駆動するためにシフトレジスタ回路やラッチ回路のゲート絶縁膜の厚さを薄くし、チャネル長も他のTFTよりも短く形成する。

【0026】

また、高い周波数の入力デジタル信号を必要とするソース線側には信号分割回路を設け、スティックドライバに入力するデータ信号の周波数を落とす手段を設ける。これにより、スティックドライバのTFTの負担を軽減し、駆動回路の信頼性を向上させる。信号分割回路は、n個の入力部とm×n個の出力部とを備え、n個の入力部のそれぞれより入力信号の供給を受け、入力デジタル信号のパルスの長さを時間伸長した修正デジタル信号を、m×n個ある出力部より送り出すことにより、入力デジタル信号の周波数を落としている。修正デジタル信号は、入力デジタル信号のパルスの長さを何倍に時間伸長したものであっても良い。

【0027】

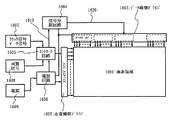

本発明の基本的な概念を図32に示す。表示領域3202が形成された第1の基板3201と、第3の基板3206上に複数の駆動回路を形成し、第3の基板3206を各駆動回路毎に、短冊状または矩形状に分断することによって取り出されるスティックドライバを第1の基板に貼り合わせる。駆動回路の構成は走査線側とソース線側で異なるが、いずれにしてもそれぞれの側で複数個のスティックドライバを実装する。図32では、走査線駆動回路が形成されたスティックドライバ3203、3204及びソース線駆動回路が形成されたスティックドライバ3207、3208が実装される形態を示している。

【0028】

スティックドライバは大面積の第3の基板上に複数個作り込むことが生産性を向上させる観点から適している。例えば、300×400mmや550×650mmの大面積の基板上に駆動回路部と入出力端子を一つのユニットとする回路パターンを複数個形成し、最後に分割して取り出すと良い。スティックドライバの短辺の長さは1〜6mm、長辺の長さは15〜80mmとする。このようなサイズで分割するには、ダイヤモンド片などを利用してガラス基板の表面に罫書き線を形成し、外力を作用させて罫書き線に沿って分断する方法で行うことができる。この加工を行う機械はガラススクライバーとも呼ばれるが、分断加工するのに必要な刃の加工幅は100μmを下らず、100〜500μmは余裕を見込む必要があった。また、基板上に形成したマーカーとの位置合わせ精度も±100μmの誤差がある。従って、ガラススクライバーで短辺が2mmのスティックドライバを切り出すには切りしろを1〜5mm見込む必要があり、そのために1枚の基板からの取り数が制限されてしまう。一方、シリコンウェハーを個々のダイに切断するブレートダイシング法を用いたダイシング装置は、ブレード(刃)の幅が0.02〜0.05mmであり、位置合わせ精度を考慮しても100μm以下の精度で基板を分割することができる。

【0029】

従って、1枚の基板からスティックドライバを効率的に取出す方法は、加工精度の低いガラススクライバーで分断する加工領域と、加工精度の高いダイシング装置で分断する加工領域とを分けて配置する。具体的には、一辺が100〜200mmの領域から成る群を作り、その群の中に短辺の長さ1〜6mmのスティックドライバを複数個配置する。そして、群と群との分割はガラススクライバーで行い、分割された群からスティックドライバを取り出すにはダイシング装置で行う。

【0030】

また、ソース線側のスティックドライバは、チャネル長を0.3〜1μmとし、さらに上記のような限られた面積内に必要な回路を形成するために、走査線側のスティックドライバよりもデザインルールを縮小して形成する。その好ましい方法として、ステッパ方式を用いた露光技術を採用する。

【0031】

【発明の実施の形態】

[実施形態1]

本願発明の液晶表示装置における画素領域の画素の構成について説明する。図1はその平面図の一例であり、ここでは簡略化のため、マトリクス状に配置された複数の画素の1つの画素構成を示している。また、図2及び図3は作製工程を示す図である。

【0032】

図1に示すように、画素領域は互いに平行に配置された複数のゲート配線と、各ゲート配線と交差するソース配線を複数有している。ゲート配線とソース配線とで囲まれた領域には画素電極119が設けられている。また、この画素電極119と重ならないように、画素電極と同じ材料からなる配線120がソース配線117と重なっている。ゲート配線102とソース配線117の交差部近傍にはスイッチング素子としてのTFTが設けられている。このTFTは非晶質構造を有する半導体膜(以下、第1の半導体膜と呼ぶ)で形成されたチャネル形成領域を有する逆スタガ型(若しくはボトムゲート型ともいう)のTFTである。

【0033】

さらに、画素電極119の下方で隣り合う2本のゲート配線の間には、ゲート配線102と平行に容量配線103が配置されている。この容量配線103は全画素に設けられており、画素電極119との間に存在する絶縁膜104bを誘電体として保持容量を形成している。

【0034】

本発明の逆スタガ型TFTは、絶縁性基板上に順次、ゲート電極(ゲート配線102と同じ層で一体形成され、ゲート配線に接続する電極)と、ゲート絶縁膜と、第1の半導体膜膜と、一導電型(通常はn型を用いる)の不純物元素を含む第2の半導体膜からなるソース領域及びドレイン領域と、ソース電極(ソース配線117と一体形成された)及び電極118(以下、ドレイン電極とも呼ぶ)とが積層形成されている。

【0035】

ソース配線(ソース電極含む)及びドレイン電極118の下方には、絶縁性基板上に順次、ゲート絶縁膜と、第1の半導体膜と、n型を付与する不純物元素を含む第2の半導体膜とが積層形成されている。

【0036】

第1の半導体膜のうち、ソース領域と接する領域とドレイン領域との間の領域は、他の領域と比べ膜厚が薄くなっている。膜厚が薄くなったのは、n型を付与する不純物元素を含む第2の半導体膜をエッチングにより分離してソース領域とドレイン領域とを形成する際、第1の半導体膜の一部が除去されたためである。また、このエッチングによって画素電極の端面、ドレイン電極の端面、及びドレイン領域の端面が一致している。このような逆スタガ型のTFTはチャネルエッチ型と呼ばれている。また、本発明における逆スタガ型TFTの特徴は、ソース電極を覆う配線120の端面、ソース領域の端面、及びソース配線の端面が一致している。

【0037】

[実施形態2]

図6は本発明の表示装置の構成を示す図である。基板651上には画素領域652が形成されている。その画素領域652が形成された領域上には対向電極が形成された第2の基板660が液晶層(図示せず)を介して貼り合わされている。第1の基板と第2の基板との間隔、即ち液晶層の厚さはスペーサによって決定付けられるが、ネマチック液晶の場合には3〜8μm、スメチック液晶の場合には1〜4μmとする。第1及び第2の基板にはアルミノホウケイ酸ガラスやバリウムホウケイ酸ガラスなどの無アルカリガラスを用いることが好ましく、その厚さは0.3〜1.1mm(代表的には0.7mm)が用いられるので、相対的に液晶層の厚さは外観上無視できるものである。

【0038】

画素領域652は走査線(ゲート配線に対応する)群658とソース線群659が交差してマトリクスを形成し、各交差部に対応してTFTが配置されている。ここで配置されるTFTは実施形態1で説明した逆スタガ型のTFTを用いる。非晶質シリコン層はプラズマCVD法で300℃以下の温度で形成することが可能であり、例えば、外寸550×650mmの無アルカリガラス基板であっても、TFTを形成するのに必要な膜厚を数十秒で形成することができる。このような製造技術の特徴は、大画面の表示装置を作製する上で非常に有用に活用することができる。

【0039】

画素領域652の外側の領域には、駆動回路が形成されたスティックドライバ653、654が実装されている。653はソース線側の駆動回路であり、654は走査線側の駆動回路であるが、いずれも複数個に分割して実装する。RGBフルカラーに対応した画素領域を形成するためには、XGAクラスでソース線の本数が3072本であり走査線側が768本必要となる。また、UXGAではそれぞれ4800本と1200本が必要となる。このような数で形成されたソース線及び走査線は画素領域652の端部で数ブロック毎に区分して引出線657を形成し、スティックドライバ653、654の出力端子のピッチに合わせて集められている。

【0040】

一方、基板651の端部には外部入力端子655が形成され、この部分で外部回路と接続するFPC(フレキシブルプリント配線板:Flexible Printed Circuit)を貼り合わせる。そして、外部入力端子655とスティックドライバとの間は基板651上に形成した接続配線656によって結ばれ、最終的にはスティックドライバの入力端子のピッチに合わせて集められる。

【0041】

スティックドライバの回路構成は、走査線側とソース線側とで異なっている。図7はその一例を示し、図6と同様に画素領域670の外側に走査線側のスティックドライバ671と、ソース線側のスティックドライバ672が設けられる様子を示している。スティックドライバは画素密度にもよるが、走査線側で1〜2個、データ線側で2〜10個程度が実装される。走査線側のスティックドライバ671の構成は、シフトレジスタ回路673、レベルシフタ回路674、バッファ回路675から成っている。この内、バッファ回路675は30V程度の耐圧が要求されるものの、動作周波数は100kHz程度であるので、特にこの回路を形成するTFTはゲート絶縁膜の厚さは150〜250nm、チャネル長は1〜2μmで形成する。一方、ソース線側のスティックドライバは、シフトレジスタ回路676、ラッチ回路677、レベルシフタ回路678、D/A変換回路679から構成される。シフトレジスタ回路676やラッチ回路677は駆動電圧3Vで周波数50MHz以上(例えば65MHz)で駆動するために、特にこの回路を形成するTFTはゲート絶縁膜の厚さは20〜70nm、チャネル長は0.3〜1μmで形成する。

【0042】

このような駆動回路が形成されたスティックドライバは図8(A)に示すように、第3の基板811上に形成され、TFTで形成された回路部812、入力端子813、出力端子814が設けられている。駆動回路部812のTFTのチャネル形成領域やソース及びドレイン領域は結晶質半導体膜で形成する。結晶質半導体膜には非晶質半導体膜をレーザー結晶化法や熱結晶化法で結晶化させた膜を適用することが可能であり、その他のもSOI技術を用いて形成された単結晶半導体層で形成することも可能である。

【0043】

図8(B)はスティックドライバの上面図であり、図8(A)の断面図はA−A'線に対応している。画素領域のソース線または走査線に接続する出力端子のピッチは40〜100μmで複数個形成する。また、同様に入力端子813も必要な数に応じて形成する。これらの入力端子813及び出力端子814は一辺の長さを30〜100μmとした正方形または長方形状に形成する。図6で示したように、スティックドライバは画素領域の一辺の長さに合わせて形成するものではなく、長辺が15〜80mm、短辺が1〜6mmの矩形状または短冊状に形成する。画素領域のサイズ、即ち画面サイズが大型化すると、その一例として、20型では画面の一方の辺の長さは443mmとなる。勿論、この長さに対応してスティックドライバを形成することは可能であるが、基板の強度を確保するには実用的な形状とはなり得ない。むしろ、15〜80mmの長さとして複数個にスティックドライバを分割する方が取り扱いが容易となり、製造上の歩留まりも向上する。

【0044】

スティックドライバのICチップに対する外形寸法の優位性はこの長辺の長にあり、ICチップを15〜80mmという長さで形成することは生産性の観点から適していない。不可能ではないにしろ、円形のシリコンウエハーから取出すICチップの取り数を減少させるので現実的な選択とはなり得ない。一方、スティックドライバの駆動回路はガラス基板上に形成するものであり、母体として用いる基板の形状に限定されないので生産性を損なうことがない。このように、長辺が15〜80mmで形成されたスティックドライバを用いることにより、画素領域に対応して実装するのに必要な数がICチップを用いる場合よりも少なくて済むので、製造上の歩留まりを向上させることができる。

【0045】

第3の基板を用いて作製されたスティックドライバを第1の基板上に実装する方法はCOG方式と同様なものであり、異方性導電材を用いた接続方法やワイヤボンディング方式などを採用することができる。図9にその一例を示す。図9(A)は第1の基板201にスティックドライバ208が異方性導電材を用いて実装する例を示している。第1の基板210上には画素領域202、引出線206、接続配線及び入出力端子207が設けられている。第2の基板はシール材204で第1の基板201と接着されており、その間に液晶層205が設けられている。また、接続配線及び入出力端子207の一方の端にはFPC212が異方性導電材で接着されている。異方性導電材は樹脂215と表面にAuなどがメッキされた数十〜数百μm径の導電性粒子214から成り、導電性粒子214により接続配線及び入出力端子207とFPC212に形成された配線213とが電気的に接続されている。スティックドライバ208も同様に異方性導電材で第1の基板に接着され、樹脂211中に混入された導電性粒子210により、スティックドライバ208に設けられた入出力端子209と引出線206または接続配線及び入出力端子207と電気的に接続されている。

【0046】

図10(A)はこの方式によるスティックドライバ224の実装方法を詳細に説明する部分断面図である。スティックドライバ224には入出力端子225が設けられ、その周辺部には保護絶縁膜226が形成されていることが望ましい。第1の基板220には第1の導電層221と第2の導電層223、及び絶縁層222が図で示すように形成され、ここでは第1の導電層221と第2の導電層223とで引出線または接続配線を形成している。第1の基板に形成されるこれらの導電層及び絶縁層は画素領域の画素TFTと同じ工程で形成されるものである。例えば、画素TFTが逆スタガ型で形成される場合、第1の導電層221はゲート電極と同じ層に形成され、Ta、Cr、Ti、Alなどの材料で形成される。通常ゲート電極上にはゲート絶縁膜が形成され、絶縁層222はこれと同じ層で形成されるものである。第1の導電層221上に重ねて設ける第2の導電層223は画素電極と同じ透明導電膜で形成されるものであり、導電性粒子227との接触を良好なものとするために設られている。樹脂228中に混入させる導電性粒子227の大きさと密度を適したものとすることにより、このような形態でスティックドライバと第1の基板とは電気的接続構造を形成することができる。

【0047】

図10(B)は樹脂の収縮力を用いたCOG方式の例であり、スティックドライバ側にTaやTiなどでバリア層229を形成し、その上に無電解メッキ法などによりAuを約20μm形成しバンプ230とする。そして、スティックドライバと第1の基板との間に光硬化性絶縁樹脂231を介在させ、光硬化して固まる樹脂の収縮力を利用して電極間を圧接して電気的な接続を形成する。

【0048】

また、図9(B)で示すように第1の基板にスティックドライバを接着材216で固定して、Auワイヤ217によりスティックドライバの入出力端子と引出線または接続配線とを接続しても良い。そして樹脂218で封止する。

【0049】

スティックドライバの実装方法は図9及び図10を基にした方法に限定されるものではなく、ここで説明した以外にも公知のCOG方法やワイヤボンディング方法、或いはTAB方法を用いることが可能である。

【0050】

スティックドライバの厚さは、対向電極が形成された第2の基板と同じ厚さとすることにより、この両者の間の高さはほぼ同じものとなり、表示装置全体としての薄型化に寄与することができる。また、それぞれの基板を同じ材質のもので作製することにより、この液晶表示装置に温度変化が生じても熱応力が発生することなく、TFTで作製された回路の特性を損なうことはない。その他にも、本実施形態で示すようにICチップよりも長尺のスティックドライバで駆動回路を実装することにより、一つの画素領域に対して必要な数を減らすことができる。

【0051】

【実施例】

[実施例1]

本実施例は液晶表示装置の作製方法を示し、基板上に画素部のTFTを逆スタガ型で形成し、該TFTに接続する保持容量を作製する方法について図1〜図5を用い工程に従って詳細に説明する。また、同図には該基板の端部に設けられ、他の基板に設けた回路の配線と電気的に接続するための端子部の作製工程を同時に示す。

【0052】

図2(A)において、基板100にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いる。その他に、石英基板、プラスチック基板などの基板を使用することができる。

【0053】

この基板100上に導電層を全面に形成した後、第1のフォトマスクを用いるフォトリソ工程を行い、エッチング処理をしてゲート電極102'及びゲート配線(図示せず)、容量配線103、端子101を形成する。このとき少なくともゲート電極102'の端部にテーパー部が形成されるようにエッチングする。また、この段階での上面図を図4に示す。

【0054】

ゲート電極102及びゲート配線と容量配線103、端子部の端子101は、アルミニウム(Al)や銅(Cu)などの低抵抗導電性材料で形成することが望ましいが、Al単体では耐熱性が劣り、また腐蝕しやすい等の問題点があるので耐熱性導電性材料と組み合わせて形成する。また、低抵抗導電性材料としてAgPdCu合金を用いてもよい。耐熱性導電性材料としては、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)から選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜、または前記元素を成分とする窒化物で形成する。例えば、TiとCuの積層、TaNとCuとの積層が挙げられる。また、Ti、Si、Cr、Nd等の耐熱性導電性材料と組み合わせて形成した場合、平坦性が向上するため好ましい。その他に、耐熱性導電性材料の単層やMoとW、或いはMoとTaの合金を用いても良い。

【0055】

液晶表示装置を作製するには、ゲート電極およびゲート配線は耐熱性導電性材料と低抵抗導電性材料とを組み合わせて形成することが望ましい。画面サイズが4型程度までなら耐熱性導電性材料の窒化物から成る導電層(A)と耐熱性導電性材料から成る導電層(B)とを積層したニ層構造とする。導電層(B)はAl、Cu、Ta、Ti、W、Nd、Crから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜で形成すれば良く、導電層(A)は窒化タンタル(TaN)膜、窒化タングステン(WN)膜、窒化チタン(TiN)膜などで形成する。例えば、導電層(A)としてCr、導電層(B)としてNdを含有するAlとを積層したニ層構造とすることが好ましい。導電層(A)は10〜100nm(好ましくは20〜50nm)とし、導電層(B)は200〜400nm(好ましくは250〜350nm)とする。

【0056】

一方、4型クラス以上の大画面に適用するには耐熱性導電性材料から成る導電層(A)と低抵抗導電性材料から成る導電層(B)と耐熱性導電性材料から成る導電層(C)とを積層した三層構造とすることが好ましい。低抵抗導電性材料から成る導電層(B)は、アルミニウム(Al)を成分とする材料で形成し、純Alの他に、0.01〜5atomic%のスカンジウム(Sc)、Ti、Nd、シリコン(Si)等を含有するAlを使用する。導電層(C)は導電層(B)のAlにヒロックが発生するのを防ぐ効果がある。導電層(A)は10〜100nm(好ましくは20〜50nm)とし、導電層(B)は200〜400nm(好ましくは250〜350nm)とし、導電層(C)は10〜100nm(好ましくは20〜50nm)とする。本実施例では、Tiをターゲットとしたスパッタ法により導電層(A)をTi膜で50nmの厚さに形成し、Alをターゲットとしたスパッタ法により導電層(B)をAl膜で200nmの厚さに形成し、Tiをターゲットとしたスパッタ法により導電層(C)をTi膜で50nmの厚さに形成する。

【0057】

次いで、絶縁膜104aを全面に成膜する。絶縁膜104aはスパッタ法を用い、膜厚を50〜200nmとする。例えば、絶縁膜104aとして窒化シリコン膜を用い、150nmの厚さで形成する。勿論、ゲート絶縁膜はこのような窒化シリコン膜に限定されるものでなく、酸化シリコン膜、酸化窒化シリコン膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。例えば、下層を窒化シリコン膜とし、上層を酸化シリコン膜とする積層構造としても良い。

【0058】

絶縁膜104a上に50〜200nm(好ましくは100〜150nm)の厚さで第1の半導体膜105を、プラズマCVD法やスパッタ法などの公知の方法で全面に形成する。例えば、シリコンのターゲットを用いたスパッタ法で非晶質シリコン(a−Si)膜を150nmの厚さに形成する。その他、この第1の半導体膜には、微結晶半導体膜、非晶質シリコンゲルマニウム膜(SiXGe(1-X)、(0<X<1))、非晶質シリコンカーバイト(SiXCY)などの非晶質構造を有する化合物半導体膜を適用することも可能である。

【0059】

次に、一導電型(n型またはp型の不純物元素を含有する)の第2の半導体膜を20〜80nmの厚さで形成する。一導電型の第2の半導体膜は、プラズマCVD法やスパッタ法などの公知の方法で全面に形成する。本実施例では、リン(P)が添加されたシリコンターゲットを用いて一導電型の第2の半導体膜106を形成する。或いは、シリコンターゲットを用い、リンを含む雰囲気中でスパッタリングを行い成膜してもよい。その他にも、第2の半導体膜を水素化微結晶シリコン膜(μc−Si:H)で形成しても良い。

【0060】

金属材料からなる第1の導電膜107はスパッタ法や真空蒸着法で形成する。第1の導電膜107の材料としては、第2の半導体膜106とオーミックコンタクトのとれる金属材料であれば特に限定されず、Al、Cr、Ta、Tiから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜等が挙げられる。本実施例ではスパッタ法を用い、第1の導電膜107として、50〜150nmの厚さのTi膜と、そのTi膜上に重ねてアルミニウム(Al)を300〜400nmの厚さで形成し、さらにその上にTi膜を100〜150nmの厚さで形成する3層構造で形成する(図2(A))。

【0061】

絶縁膜104a、第1の半導体膜105、一導電型の第2の半導体膜106、及び第1の導電膜107はいずれも公知の方法で作製するものであり、プラズマCVD法やスパッタ法で作製することができる。本実施例では、これらの膜(104a、105、106、107)をスパッタ法で、ターゲット及びスパッタガスを適宣切り替えることにより連続的に形成した。この時、スパッタ装置において、同一の反応室または複数の反応室を用い、これらの膜を大気に晒すことなく連続して積層させることが好ましい。このように、大気に曝さないことで不純物の混入を防止することができる。

【0062】

そして、第2のフォトマスクを用い、フォトリソグラフィー工程を行い、レジストマスク108を形成し、エッチングにより不要な部分を除去して配線(後の工程によりソース配線及びドレイン電極)111を形成する。この際のエッチング方法としてウエットエッチングまたはドライエッチングを用いる。この時、第1の導電膜107、一導電型の第2の半導体膜106、及び第1の半導体膜105が順次、レジストマスク108のパターンに従ってエッチングとなする。この工程では配線の形成のみならず、TFTを形成する半導体層のパターンまでも同時に形成する。TFTの形成部においては、第1の導電膜からなる配線111、n型を付与する不純物元素を含む第2の半導体膜110、及び第1の半導体膜109がそれぞれ形成される。本実施例では、SiCl4とCl2とBCl3の混合ガスを反応ガスとしたドライエッチングにより、Ti膜とAl膜とTi膜を順次積層した第1の導電膜107をエッチングし、反応ガスをCF4とO2の混合ガスに代えて第1の半導体膜105及びn型を付与する不純物元素を含む第2の半導体膜106を選択的に除去する(図2(B))。また、容量部においては容量配線103と絶縁膜104aを残し、同様に端子部においても、端子101と絶縁膜104aが残る。この状態の上面図を図5に示す。但し、簡略化のため図5では全面に成膜された第2の導電膜112は図示していない。

【0063】

次に、レジストマスク108を除去した後、スクリーン印刷で画素領域の全面を覆うマスクを形成し、端子部のパッド部分を覆っている絶縁膜104aを選択的に除去する。この処理は高い位置合わせ精度を要求しないので、スクリーン印刷やシャドーマスクを用いて行うことができる。こうして絶縁膜104bを形成する(図2(C))。

【0064】

そして、全面に透明導電膜からなる第2の導電膜112を成膜する(図2(D))。この第2の導電膜112の材料は、酸化インジウム(In2O3)や酸化インジウム酸化スズ合金(In2O3―SnO2、ITOと略記する)などをスパッタ法や真空蒸着法などを用いて形成する。このような材料のエッチング処理は塩酸系の溶液により行う。しかし、特にITOのエッチングは残渣が発生しやすいので、エッチング加工性を改善するために酸化インジウム酸化亜鉛合金(In2O3―ZnO)を用いても良い。酸化インジウム酸化亜鉛合金は表面平滑性に優れ、ITOと比較して熱安定性にも優れているので、第2の導電膜112と接触する配線111をAl膜で形成しても腐蝕反応をすることを防止できる。同様に、酸化亜鉛(ZnO)も適した材料であり、さらに可視光の透過率や導電率を高めるためにガリウム(Ga)を添加した酸化亜鉛(ZnO:Ga)などを用いることができる。

【0065】

次に、第3のフォトマスクを用い、フォトリソグラフィー工程によりレジストマスク113a〜113cを形成する。そして、エッチングにより不要な部分を除去して第1の半導体膜114、ソース領域115及びドレイン領域116、ソース電極117及びドレイン電極118、画素電極119を形成する(図3(A))。このフォトリソグラフィー工程は、第2の導電膜112をパターニングすると同時に配線111と、一導電型の第2の半導体膜110と第1の半導体膜109の一部をエッチングにより除去して開孔を形成する。本実施例では、まず、ITOからなる第2の導電膜112を硝酸と塩酸の混合溶液または塩化系第2鉄系の溶液を用いたウエットエッチングにより選択的に除去し、ウエットエッチングにより配線111を選択的に除去した後、ドライエッチングによりn型を付与する不純物元素を含む第2の半導体膜110と第1の半導体膜109の一部をエッチングした。なお、本実施例では、ウエットエッチングとドライエッチングとを用いたが、実施者が反応ガスを適宜選択してドライエッチングのみで行ってもよいし、実施者が反応溶液を適宜選択してウエットエッチングのみで行ってもよい。

【0066】

また、開孔の底部は第1の半導体膜に達しており、凹部を有する第1の半導体膜114が形成される。この開孔によって配線111はソース配線117とドレイン電極118に分離され、一導電型の第2の半導体膜110はソース領域115とドレイン領域116に分離される。また、ソース配線と接する第2の導電膜120は、ソース配線を覆い、後の製造工程、特にラビング処理で生じる静電気を防止する役目を果たす。本実施例では、ソース配線上に第2の導電膜120を形成した例を示したが、第2の導電膜120を除去してもよい。また、このフォトリソグラフィー工程において、容量部における絶縁膜104bを誘電体として、容量配線103と画素電極119とで保持容量が形成される。その他に、このフォトリソグラフィー工程において、レジストマスク113cで覆い端子部に形成された透明導電膜からなる第2の導電膜を残す。

【0067】

次に、レジストマスク113a〜113cを除去した。この状態の断面図を図3(B)に示す。尚、図1は1つの画素の上面図であり、A−A'線 及びB−B'線に沿った断面図がそれぞれ図3(B)に相当する。

【0068】

また、図11(A)は、この状態のゲート配線端子部501、及びソース配線端子部502の上面図をそれぞれ図示している。なお、図1〜図3と対応する箇所には同じ符号を用いている。また、図11(B)は図11(A)中のE−E'線 及びF−F'線に沿った断面図に相当する。図11(A)において、透明導電膜からなる503は入力端子として機能する接続用の電極である。また、図11(B)において、504は絶縁膜(104bから延在する)、505は第1の非晶質半導体膜(114から延在する)、506はn型を付与する不純物元素を含む第2の非晶質半導体膜(115から延在する)である。

【0069】

こうして3枚のフォトマスクを使用して、3回のフォトリソグラフィー工程により、逆スタガ型のnチャネル型TFT201を有する画素TFT、保持容量202を完成させることができる。これらを個々の画素に対応してマトリクス状に配置して画素部を構成することによりアクティブマトリクス型の電気光学装置を作製するための一方の基板とすることができる。本明細書では便宜上このような基板をアクティブマトリクス基板と呼ぶ。

【0070】

次に、アクティブマトリクス基板の画素部のみに配向膜121を選択的に形成する。配向膜121を選択的に形成する方法としては、スクリーン印刷法を用いてもよいし、配向膜を塗布後、シャドーマスクを用いてレジストマスクを形成して除去する方法を用いてもよい。通常、液晶表示素子の配向膜にはポリイミド樹脂が多く用いられている。そして、配向膜121にラビング処理を施して液晶分子がある一定のプレチルト角を持って配向するようにする。

【0071】

次いで、アクティブマトリクス基板と、対向電極122と配向膜123とが設けられた対向基板124とをスペーサで基板間隔を保持しながらシール剤により貼り合わせた後、アクティブマトリクス基板と対向基板の間に液晶材料125を注入する。液晶材料125は公知のものを適用すれば良く代表的にはTN液晶を用いる。液晶材料を注入した後、注入口は樹脂材料で封止する(図3(C))。

【0072】

端子部には、実施形態2で示すように駆動回路が形成されたスティックドライバを取り付ける。スティックドライバは走査線側とソース線側で異なる駆動回路が用いられる。こうして、画素領域を3枚のフォトマスクで作製したアクティブマトリクス型液晶表示装置を完成させることができる。

【0073】

[実施例2]

本実施例では、実施例1で作製した画素TFT上に保護膜を形成した例を図12に示す。なお、本実施例は、実施例1の図3(B)の状態まで同一であるので異なる点について以下に説明する。また、図3(B)に対応する箇所は同一の符号を用いている。

【0074】

まず、実施例1に従って図3(B)の状態を得た後、薄い無機絶縁膜を全面に形成する。この薄い無機絶縁膜としては、酸化シリコン膜、窒化シリコン膜、酸化窒化シリコン膜、酸化タンタル膜などの無機絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。

【0075】

次いで、第4のフォトマスクを用い、フォトリソグラフィー工程を行い、レジストマスクを形成し、エッチングにより不要な部分を除去して、画素TFT部においては絶縁膜402、端子部においては無機絶縁膜401をそれぞれ形成する。この無機絶縁膜401、402は、パッシベーション膜として機能する。また、端子部においては、第4のフォトリソグラフィー工程により薄い無機絶縁膜401を除去して、端子部の端子101上に形成された透明導電膜からなる第2の導電膜を露呈させる。

【0076】

こうして本実施例では、4枚のフォトマスクを使用して、4回のフォトリソグラフィー工程により、無機絶縁膜で保護された逆スタガ型のnチャネル型TFT、保持容量を完成させることができる。そして、これらを個々の画素に対応してマトリクス状に配置し、画素部を構成することによりアクティブマトリクス型の電気光学装置を作製するための一方の基板とすることができる。なお、本実施例は、実施例1の構成と組み合わせることが可能である。

【0077】

[実施例3]

実施例1では、絶縁膜、第1の非晶質半導体膜、一導電型の第2の非晶質半導体膜及び第1の導電膜をスパッタ法で形成する例を中心として示しが、本実施例ではプラズマCVD法を用いる例を示す。具体的には、絶縁膜、第1の非晶質半導体膜、及び一導電型の第2の半導体膜をプラズマCVD法で形成する。

【0078】

本実施例においては絶縁膜として酸化窒化シリコン膜を用い、プラズマCVD法により150nmの厚さで形成する。この時、プラズマCVD装置において、電源周波数を13〜70MHz、好ましくは27〜60MHzで行う。特に、電源周波数27〜60MHzを使うことにより緻密な絶縁膜を形成することができ、ゲート絶縁膜としての耐圧を高めることができる。また、SiH4とNH3にN2Oを添加させて作製された酸化窒化シリコン膜は、膜の内部応力が緩和されるので、この用途に対して好ましい材料となる。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、酸化シリコン膜、窒化シリコン膜、酸化タンタル膜などの他の絶縁膜を用い、これらの材料から成る単層または積層構造として形成しても良い。も良い。その一例を示せば、下層を窒化シリコン膜とし、上層を酸化シリコン膜とする積層構造はゲート絶縁膜として好ましい形態である。

【0079】

酸化シリコン膜を用いる場合には、プラズマCVD法で、オルトケイ酸テトラエチル(Tetraethyl Orthosilicate:TEOS)とO2とを混合し、反応圧力40Pa、基板温度250〜350℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製された酸化シリコン膜は、その後300〜400℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0080】

第1の半導体膜として、代表的には、プラズマCVD法で水素化非晶質シリコン(a−Si:H)膜を100nmの厚さに形成する。この時、プラズマCVD装置において、電源周波数13〜70MHz、好ましくは27〜60MHzで行えばよい。電源周波数27〜60MHzを使うことにより成膜速度を向上することが可能となり、成膜された膜は、欠陥密度の少ないa−Si膜となるため好ましい。その他、この第1の非晶質半導体膜には、非晶質シリコンゲルマニウム膜などの非晶質構造を有する化合物半導体膜を適用することも可能である。非晶質半導体膜のプラズマCVD法による成膜において、100〜100kHzのパルス変調放電を行えば、プラズマCVD法の気相反応によるパーティクルの発生を防ぐことができ、成膜においてピンホールの発生を防ぐことができるため好ましい。

【0081】

また、本実施例では、一導電型の不純物元素を含有する半導体膜として、一導電型の第2の非晶質半導体膜を20〜80nmの厚さで形成する。例えば、n型の不純物元素を含有するa−Si:H膜を形成すれば良く、そのためにシラン(SiH4)に対して0.1〜5%の濃度でフォスフィン(PH3)を添加する。或いは、n型を付与する不純物元素を含む第2の非晶質半導体膜106に代えて水素化微結晶シリコン膜(μc−Si:H)を用いても良い。

【0082】

これらの膜は、反応ガスを適宣切り替えることにより、連続的に形成することができる。また、プラズマCVD装置において、同一の反応室または複数の反応室を用い、これらの膜を大気に晒すことなく連続して積層させることもできる。このように、大気に曝さないで連続成膜することで特に、第1の半導体膜への不純物の混入を防止することができる。

【0083】

[実施例4]

図2において示すように、絶縁膜、第1の非晶質半導体膜、一導電型の第2の非晶質半導体膜、第1の導電膜を順次、連続的に積層する工程では、スパッタ装置やプラズマCVD装置の一つの形態として、複数の反応室を備えたマルチチャンバー型の装置が適用できる。

【0084】

図13はマルチチャンバー型の装置(連続成膜システム)の上面からみた概要を示す。装置の構成は、ロード・アンロード室10、15、皮膜を形成するチャンバー11〜14が備えられ、各チャンバーは共通室20に連結されている。ロード・アンロード室、共通室及び各チャンバーには、真空排気ポンプ、ガス導入系が配置されている。

【0085】

ロード・アンロード室10、15は、処理基板30をチャンバーに搬入するためのロードロック室である。第1のチャンバー11は絶縁膜104を成膜するための反応室である。第2のチャンバー12は第1の非晶質半導体膜105を成膜するための反応室である。第3のチャンバー13は一導電型の非晶質半導体膜106を成膜するための反応室である。第4のチャンバー14は第1の導電膜107を成膜するための反応室である。

【0086】

このようなマルチチャンバー型の装置の動作の一例を示す。最初、全てのチャンバーは、一度高真空状態に真空引きされた後、窒素またはアルゴンなどのガスを流し、チャンバー内を0.01〜5Pa程度の圧力に保持することにより、排気口からの逆拡散やチャンバー内壁からの脱ガスによる汚染を防いでいる。

【0087】

処理基板は多数枚が収納されたカセット28ごとロード・アンロード室10にセットされる。処理基板はゲート弁22を開けてカセットから取り出し、ロボットアーム21によって共通室20に移される。この際、共通室において位置合わせが行われる。なお、この基板30は実施例1に従って得られた配線101、102、103が形成されたものを用いた。

【0088】

ここでゲート弁22を閉鎖し、次いでゲート弁23を開ける。そして第1のチャンバー11へ処理基板30を移送する。第1のチャンバー内では150℃から300℃の温度で成膜処理を行い、絶縁膜104を得る。なお、絶縁膜としては、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、またはこれらの積層膜等を使用することができる。本実施例では単層の窒化珪素膜を採用しているが、二層または三層以上の積層構造としてもよい。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0089】

絶縁膜の成膜終了後、処理基板はロボットアームによって共通室に引き出され、第2のチャンバー12に移送される。第2のチャンバー内では第1のチャンバーと同様に150℃〜300℃の温度で成膜処理を行い、プラズマCVD法で第1の半導体膜105を得る。なお、第1の非晶質半導体膜としては、微結晶半導体膜、非晶質ゲルマニウム膜、非晶質シリコン・ゲルマニウム膜、またはこれらの積層膜等を使用することができる。また、第1の半導体膜の形成温度を350℃〜500℃として水素濃度を低減するための熱処理を省略してもよい。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0090】

第1の半導体膜の成膜終了後、処理基板は共通室に引き出され、第3のチャンバー13に移送される。第3のチャンバー内では第2のチャンバーと同様に150℃〜300℃の温度で成膜処理を行い、プラズマCVD法でn型を付与する不純物元素(PまたはAs)を含む一導電型の第2の半導体膜106を得る。なお、ここではプラズマCVD法が可能なチャンバーを用いたが、ターゲットを用いたスパッタ法が可能なチャンバーを用いても良い。

【0091】

一導電型の第2の半導体膜の成膜終了後、処理基板は共通室に引き出され、第4のチャンバー14に移送される。第4のチャンバー内では金属ターゲットを用いたスパッタ法で第1の導電膜107を得る。

【0092】

このようにして四層が連続的に成膜された被処理基板はロボットアームによってロードロック室15に移送されカセット29に収納される。

【0093】

[実施例5]

実施例4では、複数のチャンバーを用いて連続的に積層する例を示したが、本実施例では図14に示す装置を用いて一つのチャンバー内で高真空を保ったまま連続的に積層する方法を採用することもできる。

【0094】

本実施例では図14に示した装置システムを用いた。図14において、40は処理基板、50は共通室、44、46はロードロック室、45はチャンバー、42、43はカセットである。本実施例では基板搬送時に生じる汚染を防ぐために同一チャンバーで積層形成した。

【0095】

図14で示す装置を実施例1に適用する場合には、チャンバー45に複数のターゲットを用意し、順次、反応ガスを入れ替えて絶縁膜104、第1の半導体膜105、一導電型の第2の半導体膜106、第1の導電膜107を積層形成すればよい。

【0096】

また、実施例4に適用する場合には、順次、反応ガスを入れ替えて絶縁膜104、第1の非晶質半導体膜105、一導電型の第2の半導体膜106を積層形成すればよい。

【0097】

[実施例6]

実施例4で示すように、プラズマCVD法を用いるTFTの作製工程では、一導電型の第2の半導体膜を微結晶半導体膜で形成することができる。成膜時の基板加熱温度を80〜300℃、好ましくは140〜200℃とし、水素で希釈したシランガス(SiH4:H2=1:10〜100)とフォスフィン(PH3)との混合ガスを反応ガスとし、ガス圧を0.1〜10Torr、放電電力を10〜300mW/cm2とすることで微結晶シリコン膜を得ることができる。また、この微結晶珪素膜成膜後にリン(P)をプラズマドーピングして形成してもよい。一導電型の第2の半導体膜を微結晶半導体膜で形成することで、ソース及びドレイン領域の低抵抗化が図られ、TFTの特性を向上させることができる。

【0098】

[実施例7]

実施例1〜3では透過型の液晶表示装置に対応するアクティブマトリクス基板の作製方法を示したが、本実施例では図15、16を用いて、反射型の液晶表示装置に適用する例について示す。図15は断面図、図16は上面図を示し、図16中の鎖線G―G’で切断した面での断面構造とH−H’で切断した面に対応する断面構造を図15に示している。

【0099】

まず、絶縁表面を有する基板を用意する。本実施例は、基板としてガラス基板、石英基板、プラスチック基板のような透光性を有する基板の他に、反射型であるため、半導体基板、ステンレス基板、セラミック基板などに絶縁膜を形成したものでもよい。

【0100】

次いで、基板上に金属材料からなる導電膜を形成した後、第1のフォトマスクを用いレジストパターンを形成した後、エッチング処理でゲート配線750及びを凸部751形成する。この凸部は、ゲート配線とソース配線とで囲まれた領域、即ち画素電極が形成されて表示領域となる領域に配置する。なお、凸部751の形状は特に限定されず、径方向の断面が多角形であってもよいし、左右対称でない形状であってもよい。例えば、凸部751の形状は円柱状や角柱状であってもよいし、円錐状や角錐状であってもよい。また、凸部751を規則的に配置しても不規則に配置してもよい。本実施例ではゲート配線がテーパー形状であることが望ましいため、凸部751もテーパー形状を有する角錐形状となる。テーパー部の角度は5〜45度、好ましくは5〜25度とする。

【0101】

次いで、絶縁膜(ゲート絶縁膜)752、第1の半導体膜、一導電型の第2の半導体膜及び第1の導電膜を順次積層形成する。尚、第1の半導体膜は非晶質半導体、微結晶半導体のいずれを適用しても良い。一導電型の第2の半導体膜も実施例6で示すように微結晶半導体を用いてもよい。さらに、これらの膜はスパッタ法やプラズマCVD法を用いて複数のチャンバー内または同一チャンバー内で連続的に大気に曝すことなく形成することができる。大気に曝さないようにすることで不純物の混入を防止できる。上記絶縁膜752は、凸部751が形成された基板上に形成され、表面に凸凹を有している。

【0102】

次いで、第2のフォトマスクを用いレジストパターンを形成した後、エッチング処理で上記第1の導電膜、第2の半導体膜、第1の半導体膜をエッチングする。こうしてソース配線608及び電極(ドレイン電極)609を形成し、第1の半導体膜605を形成する。このエッチング処理により、ソース配線、ドレイン電極、TFTを形成する半導体層が所定のパターンに形成される。

【0103】

その後、全面に第2の導電膜を成膜する。なお、第2の導電膜としては、反射性を有する導電膜を用いる。このような導電膜としてAlやAgなどを適用することが望ましいが、耐熱性が劣るため下層に対するバリアメタル層としてTi、Taなどの層を形成しておいても良い。

【0104】

次いで、第3のフォトマスクを用い、レジストパターンを形成した後、エッチング処理をして、第2の導電膜からなる画素電極604を形成する。こうして、凸部601上に形成された絶縁膜の表面は凸凹を有し、この凸凹を表面に有する絶縁膜602上に画素電極604が形成されるので、画素電極604の表面に凹凸を持たせて光散乱性を図ることができる。

【0105】

また、本実施例の構成とすることで、画素TFT部の作製する際、フォトリソグラフィー技術で使用するフォトマスクの数を3枚とすることができる。従来では、凸凹部を形成する工程を増やす必要があったが、本実施例はゲート配線と同時に凸部を作製するため、全く工程を増やすことなく画素電極に凸凹部を形成することができる。

【0106】

[実施例8]

本実施形態では主に走査線側のスティックドライバに適したTFTの作製方法について説明する。走査線側のスティックドライバには、シフトレジスタ回路やバッファ回路などを形成する。ここでは、シフトレジスタ回路は3〜5V駆動とし、バッファ回路は33V駆動を前提とする。バッファ回路を構成するTFTは高耐圧が要求されるため、他の回路のTFTよりもゲート絶縁膜の膜厚を厚くする必要がある。その作製方法を図17と図18を用いて説明する。

【0107】

図17(A)において、基板301にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板などを用いる。このようなガラス基板は加熱温度により僅かながら収縮するので、ガラス歪み点よりも500〜650℃のい温度で熱処理を施したものを用いると基板の収縮率を低減させることができる。

【0108】

ブロッキング層302は基板301に微量に含まれるアルカリ金属などが半導体層に拡散するのを防ぐために設け、酸化シリコン膜や窒化シリコン膜、または酸化窒化シリコン膜などの絶縁膜で形成する。また、TFTのしきい値電圧(Vth)を安定化させるために、ブロッキング層の応力を引張り応力とすることが望ましい。応力の制御は上記絶縁膜の作製条件により制御する。その目的のために、ブロッキング層は単層に限らず、組成の異なる複数の絶縁膜を積層して形成しても良い。例えば、プラズマCVD法でSiH4、NH3、N2Oから作製される酸化窒化シリコン膜を10〜200nm(好ましくは50〜100nm)形成し、同様にSiH4、N2Oから作製される酸化窒化シリコン膜を50〜200nm(好ましくは100〜150nm)の厚さに積層形成してブロッキング層とすることができる。

【0109】

非晶質構造を有する半導体膜303は、25〜100nmの膜厚で形成する。非晶質構造を有する半導体膜の代表例としては非晶質シリコン(a−Si)膜、非晶質シリコン・ゲルマニウム(a−SiGe)膜、非晶質炭化シリコン(a−SiC)膜、非晶質シリコン・スズ(a−SiSn)膜などがあり、そのいずれでも適用できる。これらの非晶質構造を有する半導体膜はプラズマCVD法やスパッタ法、或いは減圧CVD法などにより形成されるもので、膜中に水素を0.1〜40atomic%程度含有するようにして形成する。好適な一例は、プラズマCVD法でSiH4またはSiH4とH2から作製される非晶質シリコン膜であり、膜厚は55nmとする。尚、SiH4の代わりにSi2H6を使用しても良い。

【0110】

そして、非晶質半導体膜の結晶化温度を低温化することのできる触媒元素を添加する。触媒元素は非晶質半導体膜中に直接注入する方法も可能であるが、スピンコート法、印刷法、スプレー法、バーコーター法、スパッタ法または真空蒸着法によって触媒元素が含有する層304を1〜5nmの厚さに形成しても良い。このような触媒元素の一例は、非晶質シリコンに対してニッケル(Ni)、ゲルマニウム(Ge)、鉄(Fe)、パラジウム(Pd)、スズ(Sn)、鉛(Pb)、コバルト(Co)、白金(Pt)、銅(Cu)、金(Au)が有効であることが知られている。スピンコート法で触媒元素を含有する層304を形成するには、重量換算で1〜100ppm(好ましくは10ppm)の触媒元素を含む水溶液をスピナーで基板を回転させて塗布する。

【0111】

図17(B)で示す結晶化の工程では、まず400〜500℃で1時間程度の熱処理を行い、非晶質シリコン膜の含有水素量を5atom%以下にする。そして、ファーネスアニール炉を用い、窒素雰囲気中において550〜600℃で1〜8時間の熱処理を行う。好適には、550℃で4時間の熱処理を行う。こうして結晶質半導体膜305を得ることができる。このような熱結晶化法により、非晶質シリコン膜からは結晶構造を有する結晶質シリコン膜が形成される。

【0112】

しかし、この熱結晶化法によって作製された結晶質半導体膜305は、局所的に非晶質領域が残存していることがある。このような場合、ラマン分光法では480cm-1にブロードなピークを持つ非晶質成分の存在を確認することができる。レーザー結晶化法はこのように残存する非晶質領域を結晶化させる目的において適した方法である。

【0113】

レーザー結晶化法において用いるレーザー光源にはエキシマレーザー、YAGレーザー、YVO4レーザー、YAlO3レーザー、YLFレーザーなどを用いることができる。エキシマレーザーでは400nm以下の波長の光を高出力で放射させることができるので半導体膜の結晶化に好適に用いることができる。一方、YAGレーザー、YVO4レーザー、YAlO3レーザー、YLFレーザーなどの固体レーザーではその第2高調波(532nm)、第3高調波(355nm)、第4高調波(266nm)を用いる。光の侵入長により、第2高調波(532nm)を用いる場合には半導体膜の表面及び内部から、第3高調波(355nm)や第4高調波(266nm)の場合にはエキシマレーザーと同様に半導体膜の表面から加熱して結晶化を行うことができる。

【0114】

図17(C)はその様子を示すものであり、例えば、Nd:YAGレーザーを用い、そのパルス発振周波数を1〜10kHzとし、レーザーエネルギー密度を100〜500mJ/cm2(代表的には100〜400mJ/cm2)として、シリンドリカルレンズなどを含む光学系にて形成した線状レーザー光306をその長手方向に対し垂直な方向に走査して(或いは、相対的に基板を移動させて)する。線状レーザー光306の線幅は100〜1000μm、例えば400μmとする。このようにして熱結晶化法とレーザー結晶化法を併用することにより、結晶性の高い結晶質半導体膜307を形成することができる。

【0115】

以上のようにして形成される結晶質半導体膜307は、TFTの能動層としてチャネル形成領域をはじめ、ソース領域、ドレイン領域、LDD領域などを形成するのに適している。ニッケルなどの触媒元素を用いた熱結晶化法で作製される結晶質シリコン膜は、微視的に見れば複数の針状または棒状の結晶が集合した構造を有している。しかし、隣接する結晶粒の連続性が高く不対結合手(ダングリングボンド)が殆ど形成されないことが見込まれている。また、その結晶粒の大部分は<110>に配向している。その理由の一つとして、ニッケルなどの触媒元素を用いた場合の結晶成長過程は、触媒元素のシリサイド化物が関与しているものと考えられ、半導体膜の膜厚が25〜100nmと薄いのでその初期核のうち(111)面が基板表面とほぼ垂直なものが優先的に成長するため実質的に<110>の配向性が高くなると考えられる。

【0116】

その後、結晶質半導体膜307はエッチング処理により島状の半導体層308〜311を形成する。図17(D)では便宜上4つの半導体層を示している。以降の説明は、半導体層308、309にはシフトレジスタ回路など低電圧で駆動する回路のTFTを、半導体層310、311にはバッファ回路など高電圧で駆動する回路のTFTをそれぞれ作製することを前提として説明する。

【0117】

半導体層上に形成するゲート絶縁膜は、回路の駆動電圧を考慮して、同一基板上に形成するTFTであってもその膜厚を異ならせて形成する。そのために2段階の成膜プロセスを必要とする。最初に、ゲート絶縁膜第1層目312を40〜200nm(好ましくは70〜90nm)の厚さで形成する。そして、半導体層308、309上のゲート絶縁膜第1層目を選択的にエッチングして除去することにより図17(E)の様な状態を形成する。

【0118】

続いて、図17(F)に示すようにゲート絶縁膜第2層目313を同様に形成する。その結果、ゲート絶縁膜第1層目312とゲート絶縁膜第2層目313とをそれぞれ80nmの厚さで成膜した場合には、半導体層308、309上のゲート絶縁膜の厚さは80nmとなり、半導体層310、311のゲート絶縁膜の厚さは160nmとすることができる。

【0119】

ゲート絶縁膜はプラズマCVD法またはスパッタ法を用いシリコンを含む絶縁膜で形成する。プラズマCVD法でSiH4とN2Oの混合ガスから作製される酸化窒化シリコン膜はゲート絶縁膜として適した材料である。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜をで形成しても良い。酸化シリコン膜を適用する場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化シリコン膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0120】

こうして作製されたゲート絶縁膜上にゲート電極を形成するための導電膜を形成する。本実施形態で示すTFTのゲート電極はドライエッチング法で選択比が5〜20(好ましくは、10〜13)以上の2種類の導電性材料を積層して形成する。例えば、窒化物導電性材料から成る第1の導電膜と、400〜650℃の熱処理に耐え得る耐熱性導電性材料から成る第2の導電膜とから形成する。その具体的な一例として、第1の導電膜を窒化タンタル(TaN)、窒化チタン(TiN)、窒化タングステン(WN)から選ばれた材料で形成し、第2の導電膜をタンタル(Ta)、チタン(Ti)、タングステン(W)、モリブデン(Mo)から選ばれた一種または複数種からなる合金材料で形成する。勿論、適用可能なゲート電極材料はここで記載した材料に限定されるものではなく、上記仕様を満たす導電性材料の組み合わせであれば、他の導電性材料を選択することも可能である。尚、ここでいう選択比とは、第1の導電膜に対する第2の導電膜のエッチング速度の割合をいう。

【0121】

本実施形態では、図示はしないが、第1の導電膜をTaN膜で50〜100nmの厚さに形成し、第2の導電膜をW膜で100〜400nmの厚さに形成する。TaN膜はスパッタ法でTaのターゲットを用い、Arと窒素の混合ガスでスパッタして形成する。W膜はWをターゲットとしたスパッタ法で形成する。その他に6フッ化タングステン(WF6)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要がある。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。Wのターゲットには純度99.9999%のものを用い、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9〜20μΩcmを実現することができる。

【0122】

ゲート電極は2段階のエッチング処理により形成する。図18(A)に示すようにレジストによるマスク314を形成し、第1のエッチング処理を行う。エッチング方法に限定はないが、好適にはICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング装置を用い、エッチング用ガスにCF4とCl2を用い、0.5〜2Pa、好ましくは1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF4とCl2を混合した場合にはW膜及びTa膜とも同程度の速度でエッチングすることがでできる。

【0123】

第1のエッチング処理では、第1の導電膜及び第2の導電膜の端部がテーパー形状となるように加工する。テーパー部の角度は15〜45°とする。しかし、ゲート絶縁膜上に残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させるオーバーエッチング処理をすると良い。W膜に対する酸化窒化シリコン膜の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされる。こうして、第1のエッチング処理により第1の導電膜と第2の導電膜から成る第1の形状の導電層315〜318(第1の導電層315a〜318aと第2の導電層315b〜318b)を形成する。

【0124】