JP4699089B2 - チップオンフィルム半導体装置 - Google Patents

チップオンフィルム半導体装置 Download PDFInfo

- Publication number

- JP4699089B2 JP4699089B2 JP2005156276A JP2005156276A JP4699089B2 JP 4699089 B2 JP4699089 B2 JP 4699089B2 JP 2005156276 A JP2005156276 A JP 2005156276A JP 2005156276 A JP2005156276 A JP 2005156276A JP 4699089 B2 JP4699089 B2 JP 4699089B2

- Authority

- JP

- Japan

- Prior art keywords

- dummy

- chip

- lead terminal

- electrodes

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/17—Structure, shape, material or disposition of the bump connectors after the connecting process of a plurality of bump connectors

Description

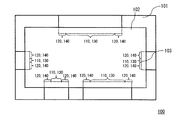

101 バンプ電極

102 フレキシブル配線基板

103 リード端子

104 ダミーリード端子

105 バンプ電極

106 ダミーバンプ電極

110 リード端子群

120 ダミーリード端子群

130 バンプ電極群

140 ダミーバンプ電極群

Claims (5)

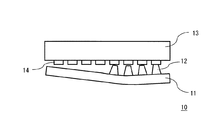

- 互いに近接して配列された複数の電極から構成される複数の電極群を有する半導体チップと、

前記半導体チップが接着剤によってその上に固着され、前記電極群を構成する各電極に対向すると共に接続する複数のリード端子から構成される複数のリード端子群を有するフレキシブル配線基板と、

を備えるチップオンフィルム半導体装置であって、

前記フレキシブル配線基板は、全ての前記リード端子群の両端のそれぞれに、4以上のダミーリード端子を備え、

前記半導体チップは、全ての前記電極群の両端のそれぞれに、前記各ダミーリード端子に対向する4以上のダミー電極を備えている、チップオンフィルム半導体装置。 - 前記接着剤は、導電粒子を含有しない熱硬化性の接着シートである、

請求項1に記載のチップオンフィルム半導体装置。 - 1つの前記リード端子群に対応する前記4以上のダミーリード端子及び前記複数のリード端子のそれぞれは、同一ピッチで配置されており、

1つの前記電極群に対応する前記4以上のダミー電極及び前記複数の電極のそれぞれは、同一ピッチで配置されている、

請求項1または2に記載のチップオンフィルム半導体装置。 - 1つの前記リード端子群に対応する前記4以上のダミーリード端子及び前記複数のリード端子のそれぞれは、同一形状であり、

1つの前記電極群に対応する前記4以上のダミー電極及び前記複数の電極のそれぞれは、同一形状である、

請求項1、2または3に記載のチップオンフィルム半導体装置。 - 1つの前記リード端子群に対応する前記4以上のダミーリード端子及び前記複数のリード端子のそれぞれは、同一の材料で形成されており、

1つの前記電極群に対応する前記4以上のダミー電極及び前記複数の電極のそれぞれは、同一の材料で形成されている、

請求項1、2、3または4に記載のチップオンフィルム半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005156276A JP4699089B2 (ja) | 2005-05-27 | 2005-05-27 | チップオンフィルム半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005156276A JP4699089B2 (ja) | 2005-05-27 | 2005-05-27 | チップオンフィルム半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006332465A JP2006332465A (ja) | 2006-12-07 |

| JP4699089B2 true JP4699089B2 (ja) | 2011-06-08 |

Family

ID=37553814

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005156276A Expired - Fee Related JP4699089B2 (ja) | 2005-05-27 | 2005-05-27 | チップオンフィルム半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4699089B2 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2014026042A (ja) * | 2012-07-25 | 2014-02-06 | Japan Display Inc | 表示装置 |

| KR102103792B1 (ko) | 2012-11-08 | 2020-04-24 | 삼성디스플레이 주식회사 | 회로 기판의 접속 구조 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05235089A (ja) * | 1992-02-26 | 1993-09-10 | Fujitsu Ltd | フェイスダウン実装用半導体チップ |

| JPH10308413A (ja) * | 1997-05-07 | 1998-11-17 | Casio Comput Co Ltd | 電子部品及び電子部品搭載モジュール |

| JP2003100999A (ja) * | 2001-09-19 | 2003-04-04 | Sony Corp | 固体撮像装置 |

| JP2003338524A (ja) * | 2002-05-21 | 2003-11-28 | Matsushita Electric Ind Co Ltd | 電子部品および電子部品実装体 |

-

2005

- 2005-05-27 JP JP2005156276A patent/JP4699089B2/ja not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05235089A (ja) * | 1992-02-26 | 1993-09-10 | Fujitsu Ltd | フェイスダウン実装用半導体チップ |

| JPH10308413A (ja) * | 1997-05-07 | 1998-11-17 | Casio Comput Co Ltd | 電子部品及び電子部品搭載モジュール |

| JP2003100999A (ja) * | 2001-09-19 | 2003-04-04 | Sony Corp | 固体撮像装置 |

| JP2003338524A (ja) * | 2002-05-21 | 2003-11-28 | Matsushita Electric Ind Co Ltd | 電子部品および電子部品実装体 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2006332465A (ja) | 2006-12-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3967133B2 (ja) | 半導体装置及び電子機器の製造方法 | |

| KR100757345B1 (ko) | 플립 칩 패키지 및 그의 제조 방법 | |

| JP4828164B2 (ja) | インタポーザおよび半導体装置 | |

| US6846699B2 (en) | Semiconductor device and method of manufacture thereof, circuit board, and electronic instrument | |

| JP2003133518A (ja) | 半導体モジュール | |

| JP2009278064A (ja) | 半導体装置とその製造方法 | |

| US10692832B2 (en) | Manufacturing method of semiconductor structure | |

| EP1096565B1 (en) | Sealed-by-resin type semiconductor device and liquid crystal display module including the same | |

| JP2009105209A (ja) | 電子装置及びその製造方法 | |

| JP2000277649A (ja) | 半導体装置及びその製造方法 | |

| JP4699089B2 (ja) | チップオンフィルム半導体装置 | |

| JP3695458B2 (ja) | 半導体装置、回路基板並びに電子機器 | |

| JP2008218758A (ja) | 電子回路実装構造体 | |

| JP2007103614A (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2005340393A (ja) | 小型実装モジュール及びその製造方法 | |

| JP2910731B2 (ja) | 半導体装置 | |

| JP2004134653A (ja) | 基板接続構造およびその基板接続構造を有する電子部品の製造方法 | |

| JP4324773B2 (ja) | 半導体装置の製造方法 | |

| JP2002289735A (ja) | 半導体装置 | |

| US20230044345A1 (en) | Layout structure of flexible circuit board | |

| JPH11163054A (ja) | 半導体装置の構造及びその製造方法 | |

| JP2012227320A (ja) | 半導体装置 | |

| JP7454345B2 (ja) | 半導体装置及びその製造方法、ならびに電子機器 | |

| JP2009194058A (ja) | 電気接続装置 | |

| JP2000353424A (ja) | 異方性導電接着剤及び導電接続構造並びに導電接続方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080522 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101027 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101102 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101224 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110222 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110302 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4699089 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140311 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140311 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313115 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |