JP4644696B2 - 裏面照射型撮像素子及びその製造方法 - Google Patents

裏面照射型撮像素子及びその製造方法 Download PDFInfo

- Publication number

- JP4644696B2 JP4644696B2 JP2007143804A JP2007143804A JP4644696B2 JP 4644696 B2 JP4644696 B2 JP 4644696B2 JP 2007143804 A JP2007143804 A JP 2007143804A JP 2007143804 A JP2007143804 A JP 2007143804A JP 4644696 B2 JP4644696 B2 JP 4644696B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor substrate

- side element

- substrate

- constituent layer

- support substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 239000000758 substrate Substances 0.000 claims description 271

- 239000004065 semiconductor Substances 0.000 claims description 98

- 239000000470 constituent Substances 0.000 claims description 70

- 125000006850 spacer group Chemical group 0.000 claims description 48

- 238000003384 imaging method Methods 0.000 claims description 40

- 239000000853 adhesive Substances 0.000 claims description 37

- 230000001070 adhesive effect Effects 0.000 claims description 37

- 238000005286 illumination Methods 0.000 claims description 22

- 239000000463 material Substances 0.000 claims description 18

- 238000005530 etching Methods 0.000 claims description 12

- 238000000206 photolithography Methods 0.000 claims description 11

- 230000004044 response Effects 0.000 claims description 10

- 238000000059 patterning Methods 0.000 claims description 7

- 238000009740 moulding (composite fabrication) Methods 0.000 claims 1

- 239000010410 layer Substances 0.000 description 87

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 48

- 229910052710 silicon Inorganic materials 0.000 description 48

- 239000010703 silicon Substances 0.000 description 48

- 238000000034 method Methods 0.000 description 29

- 238000010586 diagram Methods 0.000 description 15

- 230000008569 process Effects 0.000 description 8

- 239000007769 metal material Substances 0.000 description 6

- 238000002156 mixing Methods 0.000 description 5

- 239000011368 organic material Substances 0.000 description 5

- 238000003860 storage Methods 0.000 description 5

- 239000003822 epoxy resin Substances 0.000 description 4

- 230000006872 improvement Effects 0.000 description 4

- 229920000647 polyepoxide Polymers 0.000 description 4

- 239000011241 protective layer Substances 0.000 description 4

- 239000011521 glass Substances 0.000 description 3

- 238000003825 pressing Methods 0.000 description 3

- 238000009825 accumulation Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 239000011810 insulating material Substances 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 238000012546 transfer Methods 0.000 description 2

- 239000012790 adhesive layer Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 230000006866 deterioration Effects 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14643—Photodiode arrays; MOS imagers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/1464—Back illuminated imager structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/14—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components sensitive to infrared radiation, light, electromagnetic radiation of shorter wavelength or corpuscular radiation and specially adapted either for the conversion of the energy of such radiation into electrical energy or for the control of electrical energy by such radiation

- H01L27/144—Devices controlled by radiation

- H01L27/146—Imager structures

- H01L27/14601—Structural or functional details thereof

- H01L27/14618—Containers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Electromagnetism (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Solid State Image Pick-Up Elements (AREA)

Description

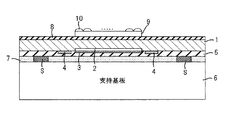

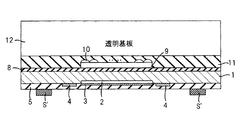

図1〜図7は、本発明の第一実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図である。

本実施形態の裏面照射型撮像素子の概略構成は、図7に示すような構成であり、半導体基板の一例であるシリコン基板1の表面側には、シリコン基板1で発生した電荷を蓄積するための多数の電荷蓄積領域や各電荷蓄積領域に蓄積された電荷を転送するCCDを構成する転送チャネル等の素子構造物2、転送チャネルを駆動する駆動電極や各種配線等の素子構造物3、電極パッド4、及びこれらを保護する保護層や平坦化層として機能する絶縁層5等を含む表面側素子構成層が形成されている。又、シリコン基板1の裏面側には、平坦化層8、各電荷蓄積領域に入射させる光を分光するカラーフィルタ9、及び各電荷蓄積領域に光を集光するためのマイクロレンズ10等を含む裏面側素子構成層が形成されている。表面側素子構成層にはスペーサSの一端が接触し、スペーサSの他端には支持基板6が接触している。そして、表面側素子構成層と支持基板6との間の空間には接着材7が充填されており、これによってシリコン基板1と支持基板6とが貼りあわされている。

まず、図1に示すように、シリコン基板1表面を上にして固定し、表面内に素子構造物2を形成し、表面上に素子構造物3や電極パッド4を公知のプロセスによって形成する。次に、図2に示すように、シリコン基板1表面上に絶縁材料を成膜後、これを平坦化して絶縁層5を形成する。

図10(a)に示すように、裏面照射型撮像素子を形成すべき領域であるチップ領域Cの中央に表面側素子構成層16を形成した場合には、それを取り囲むように面15を形成しておき、支持基板6には、図10(b)に示すように、面15に対応する位置にスペーサSを形成しておく。そして、図10(a)に示したシリコン基板1と図10(b)に示した支持基板6とを貼り合わせて接着することで、シリコン基板1と支持基板6とを平行にすることができる。

図11〜図15は、本発明の第二実施形態である裏面照射型撮像素子の製造工程の各工程における断面模式図である。

まず、第一実施形態で説明した方法と同様の方法で図2に示した状態の素子を形成する。次に、図11に示すように、絶縁層5上の特定の位置にフォトリソグラフィ及びエッチングによってスペーサS’(凸部のパターン)を形成する。つまり、絶縁層5上に絶縁層5とは異なる材料(例えば金属材料)をCVDやPVD法等の膜厚均一性のよい成膜方法で成膜し、金属材料膜上に露光及び現像工程によってレジストのマスクパターンを形成し、このマスクパターンを介して金属材料膜をエッチングすることで、スペーサS’を形成する。

2,3,4,5 表面側素子構成層

6 支持基板

7 接着材

8,9,10 裏面側素子構成層

S スペーサ

Claims (6)

- 半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子であって、

前記半導体基板の裏面上に形成された前記裏面側の素子を構成する裏面側素子構成層と、

前記半導体基板の表面上に形成された前記表面側の素子を構成する表面側素子構成層と、

前記表面側素子構成層上方に形成された支持基板と、

前記半導体基板と前記支持基板との間隔を均一にするためのスペーサであって、前記表面側素子構成層に一端が接触し、前記支持基板に他端が接触する複数のスペーサと、

前記複数のスペーサによって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に充填された接着材とを備え、

前記複数のスペーサは、前記表面側素子構成層上又は前記支持基板上に成膜された材料をフォトリソグラフィ及びエッチングによってパターニングして形成されたものであり、

前記表面側素子構成層表面には、前記複数のスペーサの各々と対応する位置に前記半導体基板の表面からの距離が均一な底面を有する複数の凹部が形成され、

前記スペーサの一端が当該スペーサに対応する位置の前記凹部の底面に接触している裏面照射型撮像素子。 - 請求項1記載の裏面照射型撮像素子であって、

前記支持基板が前記裏面照射型撮像素子の実装基体である裏面照射型撮像素子。 - 半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

前記半導体基板の表面上に、前記表面側の素子を構成する表面側素子構成層を形成する表面側素子構成層形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記支持基板上の特定の位置に複数の凸部を形成する凸部形成工程と、

前記複数の凸部を前記表面側素子構成層に接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備え、

前記表面側素子構成層形成工程では、前記表面側素子構成層表面の前記特定の位置と対応する位置に、前記半導体基板の表面からの距離が均一な底面を有する凹部を形成し、

前記貼り合わせ工程では、前記凸部を前記凹部の底面に接触させた状態で接着材の充填を行う裏面照射型撮像素子の製造方法。 - 半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって、表面の特定の位置に、前記半導体基板の表面からの距離が均一な底面を有する複数の凹部を有する表面側素子構成層を形成する表面側素子構成層形成工程と、

前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして、前記表面側素子構成層の前記複数の凹部の各々の底面上に凸部を形成する凸部形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程とを備える裏面照射型撮像素子の製造方法。 - 請求項4記載の裏面照射型撮像素子の製造方法であって、

前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、 前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備える裏面照射型撮像素子の製造方法。 - 半導体基板の裏面側から光を照射し、前記光に応じて前記半導体基板内で発生した電荷を、前記半導体基板の表面側から読み出して撮像を行う裏面照射型撮像素子の製造方法であって、

前記半導体基板の表面上に前記表面側の素子を構成する表面側素子構成層であって表面が平坦な表面側素子構成層を形成する表面側素子構成層形成工程と、

前記表面側素子構成層上に材料を成膜し、成膜した材料をフォトリソグラフィ及びエッチングによってパターニングして前記表面側素子構成層上に複数の凸部を形成する凸部形成工程と、

前記半導体基板を支持するための支持基板を用意し、前記支持基板に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記支持基板との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記支持基板を貼り合わせる貼り合わせ工程と、

前記支持基板と前記半導体基板を貼り合わせた状態で、前記半導体基板の裏面上に前記裏面側の素子を構成する裏面側素子構成層を形成する裏面側素子構成層形成工程と、

前記裏面側素子構成層形成工程の後、前記支持基板を前記接着材と共に前記表面側素子構成層から剥離する支持基板剥離工程と、 前記裏面照射型撮像素子の実装基体を用意し、前記実装基体に前記複数の凸部を接触させた状態で、前記複数の凸部によって形成された前記表面側素子構成層と前記実装基体との間の空間の少なくとも一部に接着材を充填して、前記半導体基板と前記実装基体を接着する工程とを備える裏面照射型撮像素子の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007143804A JP4644696B2 (ja) | 2007-05-30 | 2007-05-30 | 裏面照射型撮像素子及びその製造方法 |

| US12/126,592 US7893516B2 (en) | 2007-05-30 | 2008-05-23 | Backside-illuminated imaging device and manufacturing method of the same |

| US13/007,482 US8158452B2 (en) | 2007-05-30 | 2011-01-14 | Backside-illuminated imaging device and manufacturing method of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007143804A JP4644696B2 (ja) | 2007-05-30 | 2007-05-30 | 裏面照射型撮像素子及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008300551A JP2008300551A (ja) | 2008-12-11 |

| JP2008300551A5 JP2008300551A5 (ja) | 2010-08-26 |

| JP4644696B2 true JP4644696B2 (ja) | 2011-03-02 |

Family

ID=40087184

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007143804A Expired - Fee Related JP4644696B2 (ja) | 2007-05-30 | 2007-05-30 | 裏面照射型撮像素子及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US7893516B2 (ja) |

| JP (1) | JP4644696B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5644096B2 (ja) | 2009-11-30 | 2014-12-24 | ソニー株式会社 | 接合基板の製造方法及び固体撮像装置の製造方法 |

| JP2013175540A (ja) * | 2012-02-24 | 2013-09-05 | Nikon Corp | 固体撮像装置および固体撮像装置の製造方法 |

| JP6328025B2 (ja) * | 2014-10-10 | 2018-05-23 | キヤノン株式会社 | シリコン基板の加工方法、液体吐出ヘッド用基板の製造方法、および液体吐出ヘッドの製造方法 |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1167823A (ja) * | 1997-08-08 | 1999-03-09 | Hitachi Chem Co Ltd | バンプ付き配線基板及び半導体パッケ−ジの製造法 |

| WO2000062344A1 (fr) * | 1999-04-13 | 2000-10-19 | Hamamatsu Photonics K.K. | Dispositif à semiconducteur |

| JP2001308092A (ja) * | 2000-04-18 | 2001-11-02 | Toyo Kohan Co Ltd | 半導体ウェハ上の配線形成に用いる金属積層板、および半導体ウェハ上への配線形成方法 |

| JP2004296825A (ja) * | 2003-03-27 | 2004-10-21 | Hamamatsu Photonics Kk | ホトダイオードアレイおよびその製造方法並びに放射線検出器 |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06350068A (ja) | 1993-06-03 | 1994-12-22 | Hamamatsu Photonics Kk | 半導体エネルギー線検出器の製造方法 |

| WO2003096427A1 (en) | 2002-05-10 | 2003-11-20 | Hamamatsu Photonics K.K. | Rear surface irradiation photodiode array and method for producing the same |

| JP4389626B2 (ja) * | 2004-03-29 | 2009-12-24 | ソニー株式会社 | 固体撮像素子の製造方法 |

| JP4720120B2 (ja) | 2004-07-14 | 2011-07-13 | ソニー株式会社 | 半導体イメージセンサ・モジュール |

-

2007

- 2007-05-30 JP JP2007143804A patent/JP4644696B2/ja not_active Expired - Fee Related

-

2008

- 2008-05-23 US US12/126,592 patent/US7893516B2/en not_active Expired - Fee Related

-

2011

- 2011-01-14 US US13/007,482 patent/US8158452B2/en not_active Expired - Fee Related

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1167823A (ja) * | 1997-08-08 | 1999-03-09 | Hitachi Chem Co Ltd | バンプ付き配線基板及び半導体パッケ−ジの製造法 |

| WO2000062344A1 (fr) * | 1999-04-13 | 2000-10-19 | Hamamatsu Photonics K.K. | Dispositif à semiconducteur |

| JP2001308092A (ja) * | 2000-04-18 | 2001-11-02 | Toyo Kohan Co Ltd | 半導体ウェハ上の配線形成に用いる金属積層板、および半導体ウェハ上への配線形成方法 |

| JP2004296825A (ja) * | 2003-03-27 | 2004-10-21 | Hamamatsu Photonics Kk | ホトダイオードアレイおよびその製造方法並びに放射線検出器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8158452B2 (en) | 2012-04-17 |

| US20110111547A1 (en) | 2011-05-12 |

| US20080296720A1 (en) | 2008-12-04 |

| JP2008300551A (ja) | 2008-12-11 |

| US7893516B2 (en) | 2011-02-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4501130B2 (ja) | 撮像装置およびその製造方法 | |

| TWI488499B (zh) | 光敏感器件的透鏡校準之方法,裝置及實施其之系統 | |

| TWI463645B (zh) | 影像感測器中之彩色濾光片陣列對準標記形成 | |

| JP5317586B2 (ja) | カメラモジュール及びその製造方法 | |

| JP3778817B2 (ja) | 固体撮像装置およびその製造方法 | |

| TWI721378B (zh) | 影像感測器封裝及其製造方法 | |

| JP2006228837A (ja) | 半導体装置及びその製造方法 | |

| JP5721370B2 (ja) | 光センサの製造方法、光センサ及びカメラ | |

| US8193025B2 (en) | Photomask, image sensor, and method of manufacturing the image sensor | |

| US8048768B2 (en) | Joined wafer, fabrication method thereof, and fabrication method of semiconductor devices | |

| US20170062504A1 (en) | Semiconductor device with surface integrated focusing element and method of producing a semiconductor device with focusing element | |

| JP2008052004A (ja) | レンズアレイ及び固体撮像素子の製造方法 | |

| JP5342838B2 (ja) | カメラモジュール及びその製造方法 | |

| JP2004063751A (ja) | 固体撮像素子およびその製造方法 | |

| JP4174247B2 (ja) | 固体撮像素子の製造方法 | |

| JP4644696B2 (ja) | 裏面照射型撮像素子及びその製造方法 | |

| JP2009176949A (ja) | 裏面照射型固体撮像装置及びその製造方法 | |

| JP2004063782A (ja) | 固体撮像装置およびその製造方法 | |

| JP2011009389A (ja) | 固体撮像装置およびその製造方法 | |

| JP5564751B2 (ja) | イメージセンサーの製造方法 | |

| JP2006190944A (ja) | 画像センサ・ダイ | |

| CN111009542B (zh) | 一种封装方法及封装结构 | |

| JP2012099639A (ja) | イメージセンサ及びイメージセンサの製造方法 | |

| JP2001358320A (ja) | 固体撮像素子及びその製造方法、並びにオンチップレンズ金型の製造方法 | |

| JP5047077B2 (ja) | 固体撮像装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100212 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100712 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100712 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100730 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100810 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100921 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101109 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101206 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4644696 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131210 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |