JP4585147B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4585147B2 JP4585147B2 JP2001179974A JP2001179974A JP4585147B2 JP 4585147 B2 JP4585147 B2 JP 4585147B2 JP 2001179974 A JP2001179974 A JP 2001179974A JP 2001179974 A JP2001179974 A JP 2001179974A JP 4585147 B2 JP4585147 B2 JP 4585147B2

- Authority

- JP

- Japan

- Prior art keywords

- heat spreader

- spreader plate

- semiconductor device

- semiconductor element

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H10W72/30—

-

- H10W70/682—

-

- H10W70/685—

-

- H10W72/01308—

-

- H10W72/07311—

-

- H10W72/07353—

-

- H10W72/334—

-

- H10W72/884—

-

- H10W72/931—

-

- H10W90/754—

-

- H10W90/756—

Landscapes

- Cooling Or The Like Of Semiconductors Or Solid State Devices (AREA)

- Die Bonding (AREA)

Description

【発明の属する技術分野】

本発明は半導体装置に係り、特にヒートスプレッダー板に直接半導体素子を接着剤で接着して搭載し、樹脂により半導体素子をモールドした半導体装置に関する。

【0002】

【従来の技術】

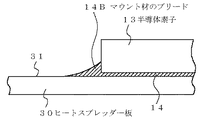

図5は従来技術のヒートスプレッダー板30を示す図であり、(A)は平面図、(B)は(A)のB−B部の断面図である。ヒートスプレッダー板30の半導体素子搭載面31は平坦面になっている。

【0003】

尚、ヒートスプレッダー板とは、搭載した半導体素子に発生した熱を拡散して外部に放出する銅系、アルミ系、Fe系等の金属板またはアルミナ、SiC等のセラミック板のことであり、このようなヒートスプレッダー板は、例えば特開平11−74417号公報あるいは特開2000−323610号公報等に開示されている。

【0004】

このように従来技術のヒートスプレッダー板30の半導体素子搭載面31は平坦面になっているから、図6に示すように、半導体素子13を半導体素子搭載面31にマウント材14により被着搭載した場合、搭載時にはみ出したマウント材14がヒートスプレッダー板上に塗れ広がり、すなわちマウント材の露出部であるブリード(にじみ出し)14Bが広くなる。

【0005】

そしてこの後で形成される封止樹脂はマウント材と密着性が悪いから、このようにマウント材の露出部14Bが広く設けられてしまうと封止樹脂の剥離等の不都合を生じる。

【0006】

このように、図5に示すようなヒートスプレッダーを備えたモールドパッケージの半導体装置では、樹脂封止後にマウント材が塗れ広がった箇所から封止樹脂が剥離し、この剥離がリフロー時にヒートスプレッダー板全面に拡大するというパッケージ信頼性上の問題があった。

【0007】

【発明が解決しようとする課題】

以上説明したように従来技術のヒートスプレッダー板の半導体素子搭載部は平滑な平面であるため、半導体素子搭載時にはみ出したマウント材がヒートスプレッダー板上に塗れ広がり、封止樹脂との密着性が悪いマウント材の露出部が広い面積で発生し、マウント材が塗れ広がった箇所から封止樹脂が剥離し、この剥離がリフロー時にヒートスプレッダー板全面に進行するというPKG信頼性上の問題があった。

したがって本発明の目的は、半導体素子搭載時におけるマウント材のはみ出し(ブリード)を抑制することができるヒートスプレッダー板を有する半導体装置を提供することである。

【0008】

【課題を解決するための手段】

本発明によれば、

ヒートスプレッダー板と、

前記ヒートスプレッダー板に設けられたリードフレームと、

前記ヒートスプレッダー板にマウント材で接着して直接搭載されており、樹脂により封止された半導体素子と、を備え、

前記ヒートスプレッダー板の前記半導体素子を搭載する面に、上面視において、少なくとも前記半導体素子の外側に同心四角形状に複数の凹凸が形成されている、半導体装置が提供される。

【0009】

また、本発明によれば、

ヒートスプレッダー板と、

前記ヒートスプレッダー板に設けられたインターポーザーと、

前記ヒートスプレッダー板にマウント材で接着して直接搭載されており、樹脂により封止された半導体素子と、を備え、

前記ヒートスプレッダー板の前記半導体素子を搭載する面に、上面視において、少なくとも前記半導体素子の外側に同心四角形状に複数の凹凸が形成されている、半導体装置が提供される。

【0010】

このように上記それぞれの半導体装置では、ヒートスプレッダー板の半導体素子を搭載する面に凹凸が形成されているから、素子搭載時のマウント材の広がり(ブリード)を抑制することが可能となり、これにより封止樹脂の剥離を阻止して信頼性の高い半導体装置を得ることができる。

【0011】

さらにこの凹凸は互いに同心的に配置した複数の直角四角形状で形成されている。したがって、直角四角形状の半導体素子(半導体チップ)の各辺からの状態が一様となって広がりの制御が容易になる。

【0012】

すなわち、半導体素子の中心を同心四角形状の凹凸の中心と一致するように半導体素子を接着すれば、半導体素子の各周辺箇所からの広がりを一様に最小限に止めることができる。ここで、凹部を同心的に形成しないで、例えば放射状またはそれに類似の形状に形成するとマウント材の広がりを促進することになり逆効果となる。

【0013】

ここで、塗れ広がりを小さくするためにはピッチを細かくした方が好ましいが、ピッチを細かくし過ぎると刻印パンチ加工が困難となり、ヒートスプレッダー板のゆがみが大きくなる懸念が生じるから、凹凸のピッチは0.3mm以上であることが好ましい。

【0014】

一方、ピッチが大き過ぎると半導体素子(半導体チップ)のサイズによっては、塗れ広がりを防止する機能がはたせなくなる。したがって、凹凸のピッチは1.0mm以下であることが好ましい。

【0015】

また、凹の深さ(凸部上面から凹部底面までの寸法)が浅いと本発明の溝としての機能が無くなるから、5.0μm以上の深さであることが好ましい。

【0016】

一方、深さが深すぎるとヒートスプレッダー板がゆがみが問題となる懸念が生じるから、20.0μm以下の深さであることが好ましい。

【0017】

【発明の実施の形態】

以下図面を参照して本発明を説明する。図2は本発明の実施の形態におけるヒートスプレッダー板を示す図であり、(A)は平面図、(B)は(A)のB−B部の断面図である。図1は図2のヒートスプレッダー板を用いた場合の半導体素子搭載時を示す断面図である。

【0018】

先ず図2を参照して、銅板からなり表裏側面にニッケルメッキ等の防錆処理が施されたヒートスプレッダー板10の半導体素子を搭載する素子搭載面11の全面に、同心的に複数の直角四角形状に複数の凹部12,凸部11Aが形成されている。

【0019】

すなわち、凹部12に対応する断面楔型であり図2(A)の凹部12と同様な平面形状の複数の同心直角四角形状の鋼鉄製のプレス治具を銅板表面に加圧することにより、複数の同心四角形状の凹部12を形成し、その間の素子搭載面11の箇所が凸部11Aとなっている。

【0020】

全面にニッケルメッキを施された銅板表面に、このようなプレス加工を行ないヒートスプレッダー板10となる。

【0021】

次に、図1を参照して、ヒートスプレッダー板10の半導体素子を搭載する素子搭載面11の全面に形成された凹凸のピッチp、すなわち凹部12となるプレス刻印12のピッチpは0.3mm以上、10.0mm以下となっている。

【0022】

また、凸部11Aとなる素子搭載面11の箇所11Aから凹部(刻印)12の底まで、すなわち凹部(刻印)12の深さtは5.0μm以上、20.0μm以下となっている。

【0023】

この同心的に配列の複数の凹凸形状12、11Aの中心と半導体素子13の中心とを一致させて、半導体素子13を銀ペーストあるいは絶縁ペースト等のマウント材14でヒートスプレッダー板10の素子搭載面11に直接接着して搭載されている。尚、絶縁ペーストは例えばエポキシ系接着材にガラスフィラーやセラミックフィラーを充填したペーストである。

【0024】

このように本発明では、ヒートスプレッダー板の半導体素子搭載面側に、プレス加工により0.3mm〜1.0mmピッチで同心四角形の刻印12が施こされているから、図1に示すように、半導体素子搭載時にはみ出したマウント材14の塗れ広がり量(投影面積)14A、すなわちマウント材のブリード(塗れ広がり、にじみ出し)14Aが狭くなり、これによりこの後の工程で形成される封止樹脂との密着性が悪いマウント材の露出部の面積が減少し、PKG信頼性が向上する。

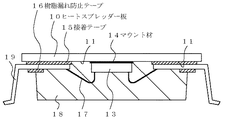

図3は図1および図2に示すヒートスプレッダー板10をQFPまたはSOPのモールドパッケージの半導体装置に適用した一例を示す断面図である。

【0025】

ヒートスプレッダー板10の凹凸を全面に形成した素子搭載面11に、同心的に配列の複数の凹凸形状12、11Aの中心と半導体素子13の中心とを一致させて、半導体素子13を銀ペーストあるいは絶縁ペースト等のマウント材14で直接接着している。

【0026】

また、リードフレーム19のインナーリードを素子搭載面11に、例えば、ポリイミドテープ基材の両面に熱硬化性接着材や熱可塑性接着材を塗布した接着テープ15により接着している。

【0027】

半導体素子の電極とインナーリードの先端をボンディングワイヤー17で接続し、接着テープ15と反対側のモールド部分の外側に位置するリードフレームの箇所に樹脂漏れ防止テープ16を張り付け、半導体素子13、インナーリード、ボンディングワイヤー17等を封止樹脂18でモールドされている。

【0028】

このような半導体装置では、刻印により形成された同心矩形状の凹凸によりクサビ効果が得られるためマウント材14のブリードが狭くなり、これにより封止樹脂18の剥離が防止できるだけではなく、同心矩形状の凹凸12、11Aによるクサビ効果により接着テープ15、マウント材14および封止樹脂18とヒートスプレッダー板10との界面の密着性も向上する。

【0029】

図4は図1および図2に示すヒートスプレッダー板10をプリント基板またはTABテープのインターポーザーを有し、モールド型のBGAパッケージの半導体装置に適用した一例を示す断面図である。

【0030】

ヒートスプレッダー板10の凹凸を全面に形成した素子搭載面11に、同心的に配列の複数の凹凸形状12、11Aの中心と半導体素子13の中心とを一致させて、半導体素子13を銀ペーストあるいは絶縁ペースト等のマウント材14で直接接着している。

【0031】

また、プリント基板またはTABテープ等のインターポーザー21を素子搭載面11に、例えば、ポリイミドテープ基材の両面に熱硬化性接着材や熱可塑性接着材を塗布した接着テープ15により接着している。

【0032】

そして、インターポーザー21の他方の面(図で下面)には複数の半田ボール29の電極が設けられ、インターポーザー11の配線の先端と半導体素子の電極とをボンディングワイヤー17で接続し、半導体素子13、インターポーザー21の半導体素子側の部分、ボンディングワイヤー17等を封止樹脂18でモールドされている。

【0033】

このような半導体装置では、図3と同様に、刻印により形成された同心矩形状の凹凸によりクサビ効果が得られるためマウント材14のブリードが狭くなり、これにより封止樹脂18との密着性が向上して封止樹脂18の剥離を防止することができるだけではなく、同心矩形状の凹凸12、11Aによるクサビ効果により接着テープ15、マウント材14および封止樹脂18とヒートスプレッダー板10との界面の密着性も向上する。

【0034】

【発明の効果】

以上説明したように本発明によれば、同心矩形状に刻印された凹凸により、半導体素子搭載時にはみ出したマウント材の塗れ広がり量(投影面積)が減少するため、封止樹脂との密着性が悪いマウント材の露出部の面積が減少し、PKG信頼性が向上する。

【0035】

また、ヒートスプレッダー板に同心矩形状に凹凸が形成されているので、ヒートスプレッダー板とマウント材の界面でクサビ効果が得られ、ヒートスプレッダー板界面とマウント材界面の密着性が向上する。

【0036】

また、ヒートスプレッダー板に同心矩形状に凹凸が形成されているので、ヒートスプレッダー板と封止樹脂材の界面でクサビ効果が得られ、ヒートスプレッダー板界面と封止樹脂材界面の密着性が向上する。

【0037】

さらに、ヒートスプレッダー板に同心矩形状に凹凸が形成されているので、ヒートスプレッダー板と接着テープの界面でクサビ効果が得られ、ヒートスプレッダー板界面と接着テープ界面の密着性が向上する。

【図面の簡単な説明】

【図1】本発明の実施の形態におけるヒートスプレッダー板を用いた場合の半導体素子搭載時を示す断面図である。

【図2】本発明の実施の形態におけるヒートスプレッダー板を示す図であり、(A)は平面図、(B)は(A)のB−B部の断面図である。

【図3】本発明の実施の形態のヒートスプレッダー板を用いた半導体装置を示す断面図である。

【図4】本発明の実施の形態のヒートスプレッダー板を用いた他の半導体装置を示す断面図である。

【図5】従来技術のヒートスプレッダー板を示す図であり、(A)は平面図、(B)は(A)のB−B部の断面図である。

【図6】図5のヒートスプレッダー板を用いた場合の半導体素子搭載時を示す断面図である。

【符号の説明】

10 ヒートスプレッダー板

11 素子搭載面

11A 凸部(刻印)

12 凹部

13 半導体素子

14 マウント材

14A 本発明のヒートスプレッダー板によるマウント材のブリード

14B 従来技術のヒートスプレッダー板によるマウント材のブリード

15 接着テープ

16 樹脂漏れ防止テープ

17 ボンディングワイヤー

18 封止樹脂

21 インターポーザー

29 半田ボール

30 ヒートスプレッダー板

31 半導体素子搭載面

Claims (8)

- ヒートスプレッダー板と、

前記ヒートスプレッダー板に設けられたリードフレームと、

前記ヒートスプレッダー板にマウント材で接着して直接搭載されており、樹脂により封止された半導体素子と、を備え、

前記ヒートスプレッダー板の前記半導体素子を搭載する面に、上面視において、少なくとも前記半導体素子の外側に同心四角形状に複数の凹凸が形成されている、半導体装置。 - 前記半導体装置のパッケージはQFPまたはSOPのモールドパッケージであることを特徴とする請求項1記載の半導体装置。

- ヒートスプレッダー板と、

前記ヒートスプレッダー板に設けられたインターポーザーと、

前記ヒートスプレッダー板にマウント材で接着して直接搭載されており、樹脂により封止された半導体素子と、を備え、

前記ヒートスプレッダー板の前記半導体素子を搭載する面に、上面視において、少なくとも前記半導体素子の外側に同心四角形状に複数の凹凸が形成されている、半導体装置。 - 前記インターポーザーはプリント基板またはTABテープであり、前記半導体装置のパッケージはBGAのモールドパッケージであることを特徴とする請求項3記載の半導体装置。

- 前記マウント材は銀ペーストまたは絶縁ペーストであることを特徴とする請求項1乃至請求項4のいずれか一項に記載の半導体装置。

- 前記凹凸はピッチ0.3mm以下、1.0mm以上でプレス刻印したものであることを特徴とする請求項1乃至請求項5のいずれか一項に記載の半導体装置。

- 前記凸からの前記凹の深さは5.0μm以上、20.0μm以下であることを特徴とする請求項1乃至請求項6のいずれか一項に記載の半導体装置。

- 平面視において、前記半導体素子の中心と同心四角形状の複数の前記凹凸の中心とが一致している、請求項1から7のいずれか1項に記載の半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001179974A JP4585147B2 (ja) | 2001-06-14 | 2001-06-14 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001179974A JP4585147B2 (ja) | 2001-06-14 | 2001-06-14 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2002373956A JP2002373956A (ja) | 2002-12-26 |

| JP4585147B2 true JP4585147B2 (ja) | 2010-11-24 |

Family

ID=19020460

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001179974A Expired - Fee Related JP4585147B2 (ja) | 2001-06-14 | 2001-06-14 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4585147B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5428542B2 (ja) * | 2009-06-03 | 2014-02-26 | 三菱電機株式会社 | 半導体装置とその製造方法 |

| WO2017018212A1 (ja) * | 2015-07-28 | 2017-02-02 | 京セラ株式会社 | 配線基板および電子装置 |

| JP6758151B2 (ja) * | 2016-10-19 | 2020-09-23 | 三菱電機株式会社 | ダイパッド、半導体装置、および、半導体装置の製造方法 |

| JP6644196B1 (ja) * | 2019-02-01 | 2020-02-12 | 三菱電機株式会社 | 半導体装置およびその製造方法ならびに電力変換装置 |

| CN113314486B (zh) * | 2021-06-28 | 2025-03-25 | 甬矽电子(宁波)股份有限公司 | 封装散热板和散热封装器件 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01270254A (ja) * | 1988-04-22 | 1989-10-27 | Hitachi Ltd | 樹脂封止型半導体装置 |

| JPH11340385A (ja) * | 1998-05-27 | 1999-12-10 | Furukawa Electric Co Ltd:The | 樹脂封止型半導体装置 |

-

2001

- 2001-06-14 JP JP2001179974A patent/JP4585147B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002373956A (ja) | 2002-12-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101204107B1 (ko) | 보편적 풋프린트를 포함하는 반도체 다이 패키지 및 그제조방법 | |

| US5729051A (en) | Tape automated bonding type semiconductor device | |

| JP2002329829A (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2003068931A (ja) | 半導体パッケージ及びその製造方法 | |

| JP2000332055A (ja) | フリップチップ実装構造及び実装方法 | |

| US6501160B1 (en) | Semiconductor device and a method of manufacturing the same and a mount structure | |

| JP3072291B1 (ja) | リ―ドフレ―ムとそれを用いた樹脂封止型半導体装置およびその製造方法 | |

| TWI311352B (en) | Fabricating process of leadframe-based bga packages and leadless leadframe utilized in the process | |

| JP4585147B2 (ja) | 半導体装置 | |

| JPH1174312A (ja) | 半導体装置およびはんだバンプの形成方法 | |

| JPH04199664A (ja) | 半導体装置 | |

| JPH05109786A (ja) | 半導体チツプの実装構造 | |

| CN2567768Y (zh) | 基板在晶片上的封装结构 | |

| JP2001024133A (ja) | リードフレームとそれを用いた樹脂封止型半導体装置およびその製造方法 | |

| JPH04361552A (ja) | テープキャリアのアウタボンディングツール | |

| JP7603620B2 (ja) | 電子装置および電子装置の製造方法 | |

| JPH06140466A (ja) | 半導体装置 | |

| JPH08306721A (ja) | 半導体装置及びその製造方法 | |

| JP2012084795A (ja) | 実装部品仮固定用接着剤の供給方法、半導体装置の製造方法、部品実装用基板および半導体装置 | |

| JPH11238828A (ja) | Bga型パッケージの半導体装置およびその製造方法、実装装置 | |

| JPH03257854A (ja) | 半導体装置 | |

| JP4065180B2 (ja) | 樹脂封止金型 | |

| JP2001291729A (ja) | 半導体素子の孔版印刷樹脂封止方法、及び該方法に用いる孔版及びスキージ | |

| JP2000228457A (ja) | 半導体装置、その製造方法及びテープキャリア | |

| JP3707639B2 (ja) | エリアアレイパッケージ型半導体装置の構造 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20070705 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080415 |

|

| RD01 | Notification of change of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7421 Effective date: 20100426 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100610 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100615 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100809 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100831 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100903 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130910 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |