JP4550288B2 - 共鳴トンネルダイオードブリッジを用いたアナログ信号量子化装置 - Google Patents

共鳴トンネルダイオードブリッジを用いたアナログ信号量子化装置 Download PDFInfo

- Publication number

- JP4550288B2 JP4550288B2 JP2000592945A JP2000592945A JP4550288B2 JP 4550288 B2 JP4550288 B2 JP 4550288B2 JP 2000592945 A JP2000592945 A JP 2000592945A JP 2000592945 A JP2000592945 A JP 2000592945A JP 4550288 B2 JP4550288 B2 JP 4550288B2

- Authority

- JP

- Japan

- Prior art keywords

- terminal

- clock

- bridge

- negative resistance

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/06—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M1/0617—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence

- H03M1/0675—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence using redundancy

- H03M1/0678—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence using redundancy using additional components or elements, e.g. dummy components

- H03M1/068—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence using redundancy using additional components or elements, e.g. dummy components the original and additional components or elements being complementary to each other, e.g. CMOS

- H03M1/0682—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by the use of methods or means not specific to a particular type of detrimental influence using redundancy using additional components or elements, e.g. dummy components the original and additional components or elements being complementary to each other, e.g. CMOS using a differential network structure, i.e. symmetrical with respect to ground

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Nanotechnology (AREA)

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Crystallography & Structural Chemistry (AREA)

- Amplifiers (AREA)

- Analogue/Digital Conversion (AREA)

- Radar Systems Or Details Thereof (AREA)

- Digital Transmission Methods That Use Modulated Carrier Waves (AREA)

- Arrangements For Transmission Of Measured Signals (AREA)

Description

発明の技術分野

本発明は、概して、電子的量子化に関し、特に、共鳴トンネルダイオードブリッジを用いたアナログ信号の量子化装置に関する。

【0002】

発明の背景

アナログ−デジタル変換器は様々な設計によって作られてきた。従来、これらの設計はトランジスタを用いて実施されている。例えば、一般的な実施の1つでは、交差結合した一組のトランジスタが含まれる。しかしながら、アナログ−デジタル変換器にトランジスタを用いて実施するのに関連したいくつかの欠点がある。

【0003】

第一に、デジタル回路に用いられる装置はどんどん小さくなっている。これらの装置は、サイズが小さくなることによって量子力学的効果が現れはじめる。量子力学的効果により、従来のトランジスタの電気的特性は容認できなくなる。第二に、トランジスタ利用アナログ−デジタル変換器は、トランジスタのスイッチング速度によって限界となり、いくつかの適用においては遅すぎる。最後に、従来のトランジスタは二安定状態に限定されている。したがって、トランジスタを用いた装置は、一般的にはアナログ信号をバイナリデジタル信号にただ変換するだけで、多値論理に用いるのを難しくしている。

【0004】

発明の開示

本発明により、共鳴トンネルダイオードブリッジを用いてアナログ信号を量子化する装置を提供して、今まで発展してきた量子化装置に伴う欠点や問題点を実質上除去しまたは減少するものある。

【0005】

本発明の1つの実施形態においては、共鳴トンネルダイオードブリッジを用いてアナログ信号を量子化する装置を提供するが、装置は、第1の負性抵抗素子を含んでいる。第1の負性抵抗素子は、クロック信号を受けるために結合される第1の端子と、第1の入力信号を受けるために結合される第2の端子を有する。第2の負性抵抗素子は、クロック信号を受けるために結合される第1の端子と、第2の入力信号を受けるために結合される第2の端子を有する。第3の負性抵抗素子は、第1の入力信号を受けるために結合される第1の端子と、反転クロック信号を受けるために結合される第2の端子を有する。第4の負性抵抗素子は、第2の入力信号を受けるために結合される第1の端子と、反転クロック信号を受けるために結合される第2の端子を有する。出力端子は、第1の負性抵抗素子の第2の端子、及び第3の負性抵抗素子の第1の端子に結合している。出力端子は出力信号を出力する。反転出力端子は、第2の負性抵抗素子の第2の端子、及び第4の負性抵抗の第1の端子に結合している。反転出力端子は反転出力信号を出力する。

【0006】

本発明の技術的長所は、アナログ信号の量子化のために改良した装置の提供を含んでいる。特に、共鳴トンネルダイオードのような負性抵抗素子が、アナログ−デジタル変換器の一部として含まれている。したがって、トランジスタに依拠することが避けられる。その結果として、不利益な量子力学的効果は、最小限になるか又は存在せずに、スイッチング速度は上昇し、そして多値論理を用いることが可能となる。

【0007】

本発明における他の技術的長所は、以下の図面、説明、及び請求項から、この分野の専門家にあっては、容易に理解することができるであろう。

ここで、本発明およびその長所のより完全な理解のために、添付の図と関連して、以下の説明が参照される。

【0008】

発明の詳細な説明

本発明の好ましい実施の形態及び効果は、図1から図10を参照して詳細に理解されるが、ここに同じ番号が同じ部材を示す。

【0009】

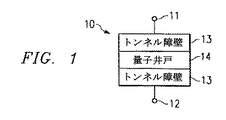

図1は、本発明の教示に基づいて、負性抵抗素子として使用される共鳴トンネルダイオード(RTD)10の模式図である。RTD10は、入力信号を受け取る入力端子11と、出力信号を出す出力端子12と、2つのトンネル障壁層13と、量子井戸層14と、から構成されている。

【0010】

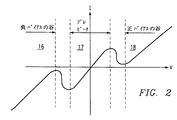

図2は、RTD10のような負性抵抗素子の、電圧に対する電流の関係を示すグラフである。このI−V曲線の形状は、トンネル障壁層13と量子井戸層14の厚さを非常に薄くした場合に現れる量子効果に依存する。層13及び14の厚さは、大体、10〜20原子厚みである。

【0011】

微小振幅の電圧が入力端子11に印加されると、電子は2つのトンネル障壁層13をトンネリングしない。これは、無視できる程度の電流しか流れないこと、及びRTD10のスイッチが切れているためである。電圧を大きくしていくと、入力端子11で受け取る電子のエネルギーも増加し、これら電子の波長は減少する。入力端子11が特定の電圧レベルに達すると、電子の波長の特定の値が量子井戸層14の内部に適合(fit)するようになる。この点で、一つのトンネル障壁層13をトンネリングする電子が量子井戸層14の中に留まり、共鳴状態となる。これにより、電子は第2のトンネル障壁層13をトンネリングして出力端子12に到達することが可能となる。このようにして、入力端子11から出力端子12への電流の流れが完成し、RTD10のスイッチが入る。しかし、電圧レベルが増加し続けると、終には、電子はトンネル障壁層13をトンネリングするに必要な波長を持つことができず、RTD10のスイッチが切れる。RTD10のような負性抵抗素子のこのような特性、すなわち、電圧を増加させた時、オン状態とオフ状態との間を交互にスイッチングする特性は、図2に示した3つの安定状態の中の一つの状態で動作するように電圧を印加することを可能にする。これらの3つの安定状態とは、負バイアスの谷領域16、プレピーク領域17、そして正バイアスの谷領域18である。

【0012】

RTD10のトンネル障壁層13と量子井戸層14とを非常に薄くした場合に現れる別の特性は、スイッチング速度に関するものである。これらの層13と14は、10〜20原子厚み程度であるので、電子は、入力端子11から出力端子12まで約0.01μを移動するだけで良い。この短い距離により、RTD10は非常に速い速度でスイッチのオンとオフとを行うことができる。

【0013】

図3と図4は、本発明に基づいてアナログ信号を量子化する装置20と40を示す回路図である。装置20と40は、第1の共鳴トンネルダイオード22と、第2の共鳴トンネルダイオード24とで構成されている。装置20と40は、また、アナログ入力信号を受ける入力端子26と、クロック信号を受けるクロック端子28と、反転クロック信号を受け取る反転クロック端子30と、量子化された出力信号を出す出力端子32と、から構成されている。

【0014】

本発明の一実施の形態によれば、入力端子26で受けた入力は、電流可変信号からなり、一方、出力端子32での出力は電圧可変信号からなる。装置20と40の一つの実施において、入力信号はXバンド領域(10GHz以上)で変化する。図3の装置20において、RTD22と24は、クロック端子28に対して同じ方向にバイアスされている。図4の装置40において、RTD22と24は、それぞれ、並列に接続され、互いに逆方向にバイアスされた対から成る。

【0015】

本発明によれば、出力端子32は、入力信号が第1の閾値よりも大きい時は+1の電圧信号を出力し、入力信号が第2の閾値よりも小さい時は−1の電圧信号を出力し、入力信号が第1と第2の閾値の間にある時はゼロの電圧信号を出力する。

【0016】

図3に示した実施の形態において、装置20は1個のRTD22と1個のRTD24とから成る。この実施の形態は、よりコンパクトな配置を提供するものであり、図4に示した実施の形態、すなわち、RTD22と24がそれぞれ対で構成されているものよりも高速で動作する。しかし、図4に示した実施の形態は、より対称的な配置を提供し、図3に示した実施の形態に存在する可能性のある偶数次高調波を減少させることができる。

【0017】

図5,6,7は、本発明に基づいてアナログ信号を量子化するブリッジ50,70,80を示す回路図である。ブリッジ50,70,80は、第1の共鳴トンネルダイオード52と、第2の共鳴トンネルダイオード54と、第3の共鳴トンネルダイオード56と、第4の共鳴トンネルダイオード58と、から成る。ブリッジ50,70,80は、また、入力信号を受け取る入力端子60と、反転入力信号を受け取る反転入力端子62と、クロック信号を受け取るクロック端子64と、反転クロック信号を受け取る反転クロック端子66と、から成る。別の実施の形態では、反転入力信号を受け取る反転入力端子62に、基準信号を受け取る基準端子を用いることができる。

【0018】

図5に示した実施の形態において、RTD52,54,56,58は、それぞれ、クロック端子64に対し、同じ方向にバイアスされている。図6に示した実施の形態では、RTD52,54,56,58は、それぞれ、並列に接続され、互いに逆方向にバイアスされた一対のダイオードから構成されている。図7に示した装置80は、第5の共鳴トンネルダイオード82を含んでいる。この実施の形態では、RTD52,54,56,58,82は、それぞれ、クロック端子64に対し、同じ方向にバイアスされている。しかし、別の形態として、RTD52,54,56,58,82は、それぞれ、並列に接続され、互いに逆方向にバイアスされた一対のRTDから構成されても良い。

【0019】

ブリッジ50,70では、RTD52,54,56,58は、入力電流がゼロの時、プレピーク領域17で動作する(図2参照)。これにより、ゼロの出力信号が出力される。しかし、入力電流が特定のレベルに達すると、非対称性により−1又は+1の出力信号が出力される。

【0020】

クロック信号のレベルが増加する時に、出力信号が−1又は+1のいずれになるかの決定がなされる。この場合、ブリッジ50,70は、正電位にバイアスされ、RTD52,54,56,58の内の2つは、負バイアスの谷領域16で−1Vの出力信号を出力するか、あるいは、正バイアスの谷領域18で+1Vの出力信号を出力するように動作する。もし入力電流レベルによりRTD52が切換わると、RTD58も切換わる。しかし、もし入力電流レベルによりRTD54が切換わると、RTD56は2番目に切換わる。もしRTD52,58が切換わると、出力信号は+1Vになり、RTD54,56が切換わると、出力信号は−1Vになる。

【0021】

クロック信号のレベルが減少する時に、出力信号が−1又は+1のいずれになるかの決定がなされる。この場合、ブリッジ50,70は、負電位にバイアスされ、RTD52,54,56,58の内の2つは、クロック信号の増加に関係して説明したように、負バイアスの谷領域16、図2を参照、又は正バイアスの谷領域18のいずれかの状態に強いられる。前述のように、RTD52,58あるいはRTD54,56のいずれかが切換わる。しかし、この場合、もしRTD52,58が切換わると、出力信号は−1であり、もしRTD54,56が切換わると、出力信号は+1である。

【0022】

ブリッジ80では、第5のRTD82は非対称性を作り出す。すなわち、RTDの対である、52と58、又は54と56のいずれか一方が、負バイアスの谷領域16又は正バイアスの谷領域18の状態をとるように強いられる。この配置では、出力信号ゼロをもたらすような入力信号は実質的に有り得ない。そのため、ブリッジ80が第5のRTDを含むような実施の形態においては、出力信号は3値の代わりに2値になる。

【0023】

ブリッジ50と70の場合のように、ブリッジ80は、クロックが増加した時とクロックが減少した時の両方の出力信号の値を決定する。したがって、ブリッジ50,70,80は、各クロックサイクルに対し、2つの出力を行う。例えば、1秒当り25ギガのサンプリングを行うには、12.5GHzのクロックで十分である。

【0024】

図5および7に示す実施形態では、シングルRTD52、54、56、58と、図7のRTD82とがブリッジを備えており、これらは図6に示される実施形態よりも小型の設計であり、より高速で作用する。しかしながら、図6の実施形態はより対称で、図5および7に示される実施形態に存在し得る偶数次高調波を減少させる。

【0025】

図8は、直結動作モードにおけるアナログ信号を量子化するための装置90を示す回路図である。装置90は、図5、6または7に示される実施形態の1つによって構成されたブリッジ100を有する。このように、ブリッジ100は、アナログ入力信号を受けるための入力端子60と、反転入力信号を受けるための反転入力端子62と、クロック信号を受けるためのクロック端子64と、反転クロック信号を受けるための反転クロック端子66とを有する。あるいは他の実施形態では、反転入力信号を受けるための反転入力端子62は、基準信号を受けるための基準端子であってもよい。

【0026】

図8に示す実施形態によると、入力は、装置入力端子102で受けた電圧可変信号を有する。反転入力信号は装置入力端子104で受信される。入力増幅器106は、入力端子60と反転入力端子62とにそれぞれ接続された出力を有し、入力信号および反転入力信号は、入力増幅器106の入力端子60および反転入力端子62にそれぞれ印加される。同様に、クロック信号はクロック入力端子108で受けて、反転クロック信号はクロック入力端子110で受ける。クロック信号および反転クロック信号は、クロック増幅器112に付与され、クロック増幅器112は、クロック端子64に付与される第1の出力と、クロック端子66に付与される第2の出力とをそれぞれ有している。

【0027】

装置90からの出力信号は装置出力端子114で与えられ、反転装置出力は反転装置出力端子116で与えられる。一つの実施形態では、出力は、電流が可変する信号を有する。装置出力端子114は、ブリッジ100の入力端子60に結合されており、反転装置出力端子116は、ブリッジ100の反転入力端子62に結合されている。

【0028】

ブリッジ100が図5または図6に従って構成される場合には、出力信号は、−1、0、および+1で表される3つのレベルを有する。本発明によると、入力増幅器106は、入力信号および反転入力信号を増幅し、クロック増幅器112は、クロック信号を増幅する。この増幅によって、第1の閾値よりも入力信号が大きい場合に、出力信号に+1が形成され、第2の閾値よりも入力信号が小さい場合に、出力信号に−1が形成され、第1の閾値と第2の閾値との間に入力信号がある場合に、出力信号に0が形成される。

【0029】

図7に従ってブリッジ100が構成された場合、出力信号は−1および+1によって表される2つのレベルのうちの1つを有する。本発明によると、入力増幅器106は、入力信号および反転入力信号を増幅させ、クロック増幅器112はクロック信号および反転クロック信号を増幅させる。この増幅によって、第1の閾値よりも入力信号が大きい場合に、出力信号に+1が形成され、第2の閾値よりも入力信号が小さい場合に、出力信号に−1が形成される。

【0030】

図9は、容量結合動作モードでアナログ信号を量子化するための装置120の回路図である。装置120は、図5、図6または図7に示された実施形態のうちの1つに従って構成されたブリッジ100を有する。このように、ブリッジ100は、アナログ入力信号を受けるための入力端子60と、反転入力信号を受けるための反転入力端子62と、クロック信号を受けるためのクロック端子と、反転クロック信号を受けるための反転クロック端子66とを有する。あるいは、他の実施形態によると、反転入力信号を受けるための反転入力端子62は、基準信号を受けるための基準端子であってもよい。

【0031】

図9に示される実施形態によると、入力は、装置入力端子102で受けた電流可変信号を有する。反転入力信号は、装置入力端子104で受ける。入力信号および反転入力信号は、それぞれ、入力増幅器106の入力端子60および反転入力端子62に与えられ、入力増幅器106は、入力端子60に接続された出力と、反転入力端子62に接続された出力とを、それぞれ、有する。これと同様に、クロック信号はクロック入力端子108で受けて、反転クロック信号はクロック入力端子110で受ける。クロック信号と反転クロック信号とはそれぞれ、抵抗器124とキャパシタ126に印加され、次に、クロック端子64および反転クロック端子66に、それぞれ、接続される。

【0032】

出力信号は、装置出力端子114で装置120から与えられ、反転出力信号は、反転装置出力端子116で与えられる。出力は、電圧可変信号を含む。装置出力端子114は、入力端子60でブリッジ100に結合され、反転装置出力端子116は、反転入力端子62でブリッジ100に結合される。

【0033】

図9に示される容量結合動作モードにおいて、ブリッジ100が、図5、図6または図7に示される実施形態に従って構成されるか否かに拘わらず、出力は−1と+1とで表される2つのレベルのうちの1つを有する。本発明によると、入力増幅器106は、入力信号および反転入力信号を増幅させる。装置120に対して、入力信号が第1の閾値よりも大きい場合、装置出力114における出力信号は+1であり、入力信号が第2の閾値よりも小さい場合、−1である。

【0034】

図10は、本発明に係る連続−時間変調器130を示す回路図である。

変調器130は、図5、図6及び図7に示す実施形態の1つであるブリッジ100を備える。そして、ブリッジ100は、アナログ入力信号を受け取るための入力端子60と、反転入力信号を受けるための反転入力端子62と、クロック信号を受け取るためのクロック端子64と、反転クロック信号を受け取るための反転クロック端子66とを備える。他の実施形態では、反転入力信号を受け取るための反転入力端子62は、リファレンス信号を受け取るためのリファレンス端子であっても良い。

【0035】

図10に示した変調器の場合、入力には電流の変化する信号が含まれ、その入力はシステム入力端子132に入力される。反転入力信号は、システム入力端子133によって受け取られる。入力信号と、反転された入力信号は、入力増幅器134に送られる。入力増幅器134は、接続配線136及び138の各々に出力を有する。配線136及び138は、各々、ブリッジ増幅器144の端子140及び142に接続している。ブリッジ増幅器144は、146及び148に接続する配線に出力している。接続配線146及び148は、各々、入力端子60と反転入力端子62に接続している。また、入力端子60及び反転入力端子には、接続配線150及び152が接続している。これらの接続配線は、端子60及び62における信号をフィードバック増幅器154に送り、フィードバック増幅器154は、接続配線156及び158に出力している。接続配線156及び158は、各々、端子140及び142につながれており、これによってブリッジ信号をブリッジ増幅器144にフィードバックする。キャパシタ160は、接続配線136と138の間を容量性結合にしている。

【0036】

クロック信号は、クロック入力端子162に入力され、反転されたクロック信号は、反転クロック入力端子164で入力される。クロック信号と反転クロック信号は、クロック増幅器166に送られる。クロック増幅器166は、接続配線168及び170に出力している。接続配線168及び170は、各々、クロック端子64及び反転クロック端子66に接続されている。

【0037】

また、変調器130は、出力信号用の出力端子172と、反転出力信号用の反転出力端子174を備える。出力には、電圧の変化する信号が含まれる。出力端子172は、入力端子60においてブリッジ100に接続されている。反転出力端子174は、反転入力端子62においてブリッジ100に接続されている。

【0038】

ブリッジ100が、図5及び6の態様に従って構成されている場合、出力信号は、−1、0、+1で表される3つのレベルのいずれかを有する。本発明によれば、入力増幅器134は、入力信号と反転入力信号とを増幅し、ブリッジ増幅器144は、端子140及び142において受けた信号の増幅を行い、フィードバック増幅器154は、接続配線150及び152上に受信された信号の増幅を行い、クロック増幅器166は、クロック信号と反転クロック信号を増幅する。変調器130については、端子172における出力信号は、入力信号が第1のしきい値よりも大きければ+1であり、入力信号が第2のしきい値よりも小さければ−1であり、入力信号が第1のしきい値と第2のしきい値の間にあれば0である。

【0039】

ブリッジ100が、図7の態様に従って構成されている場合、出力信号は、−1と+1で表される2つのレベルの一方を有する。入力増幅器134は、そこに送られた信号を増幅し、ブリッジ増幅器144は、受信した信号を増幅し、フィードバック増幅器154は、それへの入力を増幅し、クロック増幅器166は、クロック信号を増幅する。出力端子172では、入力信号が第1のしきい値よりも大きければ+1であり、入力信号が第2のしきい値よりも小さければ−1である。

【0040】

クロック増幅器166による増幅度は、ブリッジ増幅器144による増幅度よりも、4倍から10倍大きい。このことは、デジタル信号の出力を高めており、その結果アナログフィードバックが相対的に減少している。また、このことは、出力抵抗を下げ、スピードと感度の両方を増加させる。

【0041】

本発明を、種々の実施形態について説明したが、この分野の専門家であれば種々の変形が可能である。本発明は、そうした変形もクレームの技術的範囲に属するものとして包含することを意図したものである。

【図面の簡単な説明】

【図1】 本発明の説明に従った負性抵抗素子として用いるための共鳴トンネルダイオード(RTD)の概略図である。

【図2】 図1に示した負性抵抗素子の、電圧に対する電流のグラフである。

【図3】 本発明の第一実施例にしたがって、アナログ信号を量子化する装置を示した回路図である。

【図4】 本発明の第二実施例によるアナログ信号量子化装置を示した回路図である。

【図5】 本発明のさらなる実施例にしたがって、アナログ信号を量子化するためのブリッジを示した回路図である。

【図6】 本発明のさらなる実施例にしたがって、アナログ信号量子化のためのブリッジを示した回路図である。

【図7】 本発明のさらなる実施例によるアナログ信号量子化のためのブリッジを示した回路図である。

【図8】 直結動作モードにある図5、6及び7のブリッジを示した回路図である。

【図9】 容量結合型動作モードにある図5、6及び7のブリッジを示した回路図である。

【図10】 本発明の他の実施例にしたがって構成された連続時間変調器の回路図である。

Claims (37)

- クロック信号を受けるために接続した第1の端子と、第1の入力信号を受けるために接続した第2の端子と、を有する第1の負性抵抗素子と、

クロック信号を受けるために接続した第1の端子と、第2の入力信号を受けるために接続した第2の端子とを、有する第2の負性抵抗素子と、

第1の入力信号を受けるために接続された第1の端子と、反転クロック信号を受けるために接続された第2の端子と、を有する第3の負性抵抗素子と、

第2の入力信号を受けるために接続された第1の端子と、反転クロック信号を受けるために接続された第2の端子と、を有する第4の負性抵抗素子と、

第1の負性抵抗素子の第2の端子と第3の負性抵抗素子の第1の端子とに接続されて出力信号を出す出力端子と、

第2の負性抵抗素子の第2の端子と第4の負性抵抗素子の第1の端子と接続されて反転出力信号を出す反転出力端子と、

を含むアナログ信号量子化ブリッジ装置。 - 第1、第2、第3及び第4の負性抵抗素子が各々、共鳴トンネルダイオードである請求項1の装置。

- さらに、第1、第2、第3及び第4の負性抵抗素子をクロック信号に対して同じ方向にバイアスする手段を含む請求項1の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列の第1と第2のトンネルダイオードとを含み、第1のトンネルダイオードが、第2のトンネルダイオードに対して反対方向にバイアスされている請求項1の装置。

- 第1及び第2の入力信号が、可変電流を含む請求項1の装置。

- 出力信号が可変電圧を含む請求項1の装置。

- 出力信号が、−1、0、+1で表せる3水準の1つである請求項1の装置。

- 第1の入力信号が、Xバンド領域の信号である請求項1の装置。

- さらに、クロック信号を受ける第1の端子と、反転クロック信号を受ける第2の端子と、を有する第5の負性抵抗素子を含む請求項1の装置。

- 第1、第2、第3、第4及び第5の負性抵抗素子が各々、共鳴トンネルダイオードを含む請求項9の装置。

- さらに、第1、第2、第3、第4及び第5の負性抵抗素子をクロック端子に対して同じ方向にバイアスする手段を含む請求項9の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列な第1の共鳴トンネルダイオードと第2の共鳴トンネルダイオードを含み、第1の共鳴トンネルダイオードが、第2の共鳴トンネルダイオードとは反対方向にバイアスされている請求項9の装置。

- 第1及び第2の入力信号が、可変電流を含む請求項9の装置。

- 出力信号が、可変電圧を含む請求項9の装置。

- 出力信号が、−1、0、+1で表せる3水準の1つである請求項9の装置。

- さらに、第1の入力端子と第2の入力端子と第1の出力端子と第2の出力端子とを有するクロック増幅器と、

クロック信号をクロック増幅器の第1の入力端子に接続する手段と、

反転クロック信号をクロック増幅器の第2の入力端子に接続する手段と、

クロック増幅器の第1の出力端子を第1の負性抵抗素子の第1の端子及び第2の負性抵抗素子の第1の端子に接続する手段と、

クロック増幅器の第2の出力端子を第3の負性抵抗素子の第2の端子及び第4の負性抵抗素子の第2の端子に接続する手段と、

を含む請求項1の装置。 - さらに、クロック信号をクロック端子に接続するキャパシタと、反転クロック信号を反転クロック端子に接続するキャパシタとを含む請求項1の装置。

- 負性抵抗素子を有する量子化ブリッジであって、ブリッジ入力端子、反転ブリッジ入力端子、クロック端子及び反転クロック端子を有し、さらに、

クロック端子と接続した第1の端子と、ブリッジ入力端子と接続した第2の端子と、を有する第1の負性抵抗素子と、

クロック端子と接続した第1の端子と、反転ブリッジ入力端子と接続した第2の端子と、を有する第2の負性抵抗素子と、

ブリッジ入力端子に接続した第1の端子と、反転クロック端子と接続した第2の端子と、を有する第3の負性抵抗素子と、

反転ブリッジ入力端子と接続した第1の端子と、反転クロック端子と接続した第2の端子と、を有する第4の負性抵抗素子と、を含む量子化ブリッジと、

第1の入力信号と第2の入力信号とを受けて増幅して出力をブリッジに供給する入力増幅器と、

クロック信号と反転クロック信号とを受けて増幅し、出力を受けるブリッジと接続されたクロック増幅器と、

ブリッジ入力端子に接続されて出力信号を出す出力端子と、

反転ブリッジ入力端子に接続されて反転出力信号を出す反転出力端子と、

を含むアナログ信号量子化装置。 - 負性抵抗素子を有する量子化ブリッジであって、ブリッジ入力端子、反転ブリッジ入力端子、クロック端子及び反転クロック端子を有し、さらに、

クロック端子と接続した第1の端子と、ブリッジ入力端子と接続した第2の端子と、を有する第1の負性抵抗素子と、

クロック端子と接続した第1の端子と、反転ブリッジ入力端子と接続した第2の端子とを有する第2の負性抵抗素子と、

ブリッジ入力端子に接続した第1の端子と、反転クロック端子と接続した第2の端子と、を有する第3の負性抵抗素子と、

反転ブリッジ入力端子と接続した第1の端子と、反転クロック端子と接続した第2の端子と、を有する第4の負性抵抗素子と、を含む量子化ブリッジと、

第1の入力信号と第2の入力信号とを受けて増幅して出力をブリッジに供給する入力増幅器と、

クロック信号を受ける第1の結合素子であって、その出力をブリッジが受けるように接続された当該第1の結合素子と、

反転クロック信号を受ける第2の結合素子であって、その出力をブリッジが受けるように接続された当該第2の結合素子と、

ブリッジ入力端子に接続されて出力信号を出す出力端子と、

反転ブリッジ入力端子に接続されて反転出力信号を出す反転出力端子と、

を含むアナログ信号量子化装置。 - 第1の結合素子と第2の結合素子とが各々、キャパシタと直列に接続した抵抗とを含む請求項19の装置。

- 負性抵抗素子を有する変調器ブリッジであって、ブリッジ入力端子、反転ブリッジ入力端子、クロック端子及び反転クロック端子を有し、さらにクロック端子に接続された第1の端子及びブリッジ入力端子に接続された第2の端子を有する第1の負性抵抗素子、

クロック端子に接続された第1の端子及び反転ブリッジ入力端子に接続された第2の端子を有する第2の負性抵抗素子、

ブリッジ入力端子に接続された第1の端子及び反転クロック端子に接続された第2の端子を有する第3の負性抵抗素子、及び

反転ブリッジ入力端子に接続された第1の端子及び反転クロック端子に接続された第2の端子を有する第4の負性抵抗素子を含む変調器ブリッジと、

増幅のために入力信号及び反転入力信号を受ける入力増幅器と、

ブリッジに適合した出力を有し、入力増幅器から増幅された信号を受けるために接続されたブリッジ増幅器と、

ブリッジ増幅器に適合した出力を有し、ブリッジからの出力を受けるために接続されたフィードバック増幅器と、

増幅のためにクロック信号及び反転クロック信号を受けるクロック増幅器と、

クロック増幅器からの出力を受けるために接続されたブリッジと、

ブリッジ入力端子に接続した、出力信号を出す出力端子と、

反転ブリッジ入力端子に接続した、反転出力信号を出す反転出力端子と、を含む連続−時間変調器。 - ブリッジ増幅器がさらに第1の入力端子及び第2の入力端子を含み、第1の入力端子に接続された第1の端子及び第2の入力端子に接続された第2の端子を有するキャパシタをさらに含む請求項21の装置。

- クロック増幅器がブリッジ増幅器の増幅定数よりも約4〜10倍の増幅定数を有する請求項21の装置。

- 第1、第2、第3及び第4の負性抵抗素子がクロック端子に対して同じ方向にバイアスされている請求項21の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列な第1の共鳴トンネルダイオードと第2の共鳴トンネルダイオードを含み、第1の共鳴トンネルダイオードが、第2の共鳴トンネルダイオードとは反対方向にバイアスされている請求項21の装置。

- 第5の負性抵抗素子がクロック端子に接続された第1の端子及び反転クロック端子に接続された第2の端子をさらに含む請求項21の装置。

- 第1、第2、第3、第4及び第5の負性抵抗素子が各々、共鳴トンネルダイオードを含む請求項26の装置。

- 第1、第2、第3、第4及び第5の負性抵抗素子がクロック端子に対し同じ方向にバイアスされている請求項26の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列な第1の共鳴トンネルダイオードと第2の共鳴トンネルダイオードを含み、第1の共鳴トンネルダイオードが、第2の共鳴トンネルダイオードとは反対方向にバイアスされている請求項26の装置。

- 負性抵抗素子を有する変調器ブリッジであって、ブリッジ入力端子、反転ブリッジ入力端子、クロック信号を受けるクロック端子及び反転クロック信号を受ける反転クロック端子を有し、さらにクロック端子に接続された第1の端子及びブリッジ入力端子に接続された第2の端子を有する第1の負性抵抗素子、

クロック端子に接続された第1の端子及び反転ブリッジ入力端子に接続された第2の端子を有する第2の負性抵抗素子、

ブリッジ入力端子に接続された第1の端子及び反転クロック端子に接続された第2の端子を有する第3の負性抵抗素子、及び

反転ブリッジ入力端子に接続された第1の端子及び反転クロック端子に接続された第2の端子を有する第4の負性抵抗素子を含む変調器ブリッジと、

それ自身の増幅のために入力信号及び反転入力信号を受ける増幅器と、

増幅器に適合した出力を有し、ブリッジからの出力を受けるために接続されたフィードバック増幅器と、

ブリッジ入力端子に接続した、出力信号を出す出力端子と、

反転ブリッジ入力端子に接続した、反転出力信号を出す反転出力端子と、を含む連続−時間変調器。 - 増幅器がさらに第1の入力端子及び第2の入力端子を含み、上記第1の入力端子に接続された第1の端子及び上記第2の入力端子に接続された第2の端子を有するキャパシタをさらに含む請求項30の装置。

- 第1、第2、第3及び第4の負性抵抗素子がクロック端子に対し同じ方向にバイアスされている請求項30の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列な第1の共鳴トンネルダイオードと第2の共鳴トンネルダイオードを含み、第1の共鳴トンネルダイオードが、第2の共鳴トンネルダイオードとは反対方向にバイアスされている請求項30の装置。

- 反転クロック端子に接続された第2の端子及びクロック端子に接続された第1の端子を有する第5の負性抵抗素子をさらに含む請求項30の装置。

- 第1、第2、第3、第4及び第5の負性抵抗素子が各々、共鳴トンネルダイオードを含む請求項34の装置。

- 第1、第2、第3、第4及び第5の負性抵抗素子が各々、クロック端子に対して同じ方向にバイアスされている請求項34の装置。

- 第1、第2、第3及び第4の負性抵抗素子が各々、並列な第1の共鳴トンネルダイオードと第2の共鳴トンネルダイオードを含み、第1の共鳴トンネルダイオードが、第2の共鳴トンネルダイオードとは反対方向にバイアスされている請求項34の装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11512999P | 1999-01-06 | 1999-01-06 | |

| US60/115,129 | 1999-01-06 | ||

| PCT/US2000/000173 WO2000041310A2 (en) | 1999-01-06 | 2000-01-05 | System for quantizing an analog signal utilizing a resonant tunneling diode bridge |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002534890A JP2002534890A (ja) | 2002-10-15 |

| JP2002534890A5 JP2002534890A5 (ja) | 2007-06-07 |

| JP4550288B2 true JP4550288B2 (ja) | 2010-09-22 |

Family

ID=22359460

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000592945A Expired - Fee Related JP4550288B2 (ja) | 1999-01-06 | 2000-01-05 | 共鳴トンネルダイオードブリッジを用いたアナログ信号量子化装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (1) | US6292118B1 (ja) |

| EP (1) | EP1142125B1 (ja) |

| JP (1) | JP4550288B2 (ja) |

| AT (1) | ATE327592T1 (ja) |

| AU (1) | AU2719600A (ja) |

| DE (1) | DE60028182T2 (ja) |

| WO (1) | WO2000041310A2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6288617B1 (en) * | 2000-01-18 | 2001-09-11 | Raytheon Company | System and method for phase-locking a bridge with an optical pulse |

| US6323737B1 (en) | 2000-01-18 | 2001-11-27 | Raytheon Company | System and method for generating a multi-phase signal with a ring oscillator |

| JP2002261615A (ja) * | 2001-02-28 | 2002-09-13 | Nagoya Industrial Science Research Inst | Δ−σ型モジュレータおよびδ−σ型アナログ−デジタル変換回路 |

| US6509859B1 (en) | 2001-08-22 | 2003-01-21 | Raytheon Company | Method and system for quantizing an analog signal |

| US6490193B1 (en) | 2001-08-22 | 2002-12-03 | Raytheon Company | Forming and storing data in a memory cell |

| US6864816B1 (en) * | 2004-01-21 | 2005-03-08 | Raytheon Company | Method and apparatus for high-speed quantization using resonant tunneling technology |

| US9912253B2 (en) | 2015-12-03 | 2018-03-06 | Motorola Mobility Llc | Full bridge tunnel diode inverter |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3569733A (en) | 1967-12-28 | 1971-03-09 | Gen Electric | Reversible counter circuit utilizing tunnel diodes |

| CH484562A (de) * | 1968-06-20 | 1970-01-15 | Ibm | Analog-Digital-Wandler |

| US3815124A (en) | 1973-01-16 | 1974-06-04 | Westinghouse Electric Corp | Analog to digital converter |

| US3889134A (en) | 1974-05-16 | 1975-06-10 | Trw Inc | Tunnel diode digital data sample, decision and hold circuit |

| DE2755228A1 (de) | 1977-12-10 | 1979-06-13 | Wandel & Goltermann | Schaltungsanordnung zur traegereinspeisung fuer modulatoren |

| SU1370758A1 (ru) * | 1986-08-28 | 1988-01-30 | Институт Проблем Управления (Автоматики И Телемеханики) | Компаратор тока |

| JPH0499966A (ja) * | 1990-08-20 | 1992-03-31 | Yokogawa Electric Corp | サンプリング装置 |

| US5272480A (en) | 1992-08-17 | 1993-12-21 | Hewlett-Packard Company | Track and hold circuit with continuously suppressed Josephson effect |

| JP3429821B2 (ja) * | 1992-11-04 | 2003-07-28 | テキサス インスツルメンツ インコーポレイテツド | 多機能共鳴トンネリング論理ゲート |

| JPH0730130A (ja) * | 1993-07-14 | 1995-01-31 | Nec Corp | 微分負性抵抗ダイオードとスタティックメモリー |

| JPH08307396A (ja) * | 1995-04-28 | 1996-11-22 | Victor Co Of Japan Ltd | Ss方式無線装置 |

| JP3472973B2 (ja) * | 1995-05-22 | 2003-12-02 | 日本電信電話株式会社 | 多値論理回路 |

| US5698997A (en) | 1995-09-28 | 1997-12-16 | Mayo Foundation For Medical Education And Research | Resonant tunneling diode structures for functionally complete low power logic |

| JPH10285037A (ja) | 1997-04-10 | 1998-10-23 | Mitsubishi Electric Corp | アナログ−デジタル変換回路 |

| JPH10308669A (ja) * | 1997-05-09 | 1998-11-17 | Nippon Telegr & Teleph Corp <Ntt> | アナログ・デジタル変換装置 |

| US6037819A (en) * | 1997-08-01 | 2000-03-14 | Texas Instruments Incorporated | High frequency clock signal generator |

| DE10112938A1 (de) | 2001-03-12 | 2002-10-02 | Volkswagen Ag | Verfahren zur Steuerung eines Warmlaufs eines Katalysatorsystems |

-

2000

- 2000-01-05 US US09/478,041 patent/US6292118B1/en not_active Expired - Lifetime

- 2000-01-05 AT AT00905537T patent/ATE327592T1/de not_active IP Right Cessation

- 2000-01-05 AU AU27196/00A patent/AU2719600A/en not_active Abandoned

- 2000-01-05 WO PCT/US2000/000173 patent/WO2000041310A2/en active IP Right Grant

- 2000-01-05 JP JP2000592945A patent/JP4550288B2/ja not_active Expired - Fee Related

- 2000-01-05 DE DE60028182T patent/DE60028182T2/de not_active Expired - Lifetime

- 2000-01-05 EP EP00905537A patent/EP1142125B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| DE60028182D1 (de) | 2006-06-29 |

| WO2000041310A3 (en) | 2000-09-28 |

| WO2000041310A2 (en) | 2000-07-13 |

| US6292118B1 (en) | 2001-09-18 |

| AU2719600A (en) | 2000-07-24 |

| ATE327592T1 (de) | 2006-06-15 |

| DE60028182T2 (de) | 2007-03-29 |

| EP1142125A2 (en) | 2001-10-10 |

| EP1142125B1 (en) | 2006-05-24 |

| JP2002534890A (ja) | 2002-10-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4422914B2 (ja) | クロック共鳴トンネルダイオードペアを用いたアナログ信号量子化方法とその装置 | |

| US3984703A (en) | CMOS Schmitt trigger | |

| Inokawa et al. | A multiple-valued logic with merged single-electron and MOS transistors | |

| KR101063872B1 (ko) | 아날로그 디지털 변환기용 저전력 저역입력 잡음 비교기 회로 | |

| FR2536607A1 (fr) | Circuit d'interface | |

| CA1215138A (en) | Latching circuits | |

| JPH05252035A (ja) | 差動増幅器,比較器およびa/d変換器 | |

| JP4550288B2 (ja) | 共鳴トンネルダイオードブリッジを用いたアナログ信号量子化装置 | |

| US6597303B2 (en) | Comparator with very fast regeneration time constant | |

| JP2701546B2 (ja) | 信号電荷検出回路を有する電荷転送装置 | |

| JPS61120518A (ja) | クロツクド比較器 | |

| US6509859B1 (en) | Method and system for quantizing an analog signal | |

| JPH01202930A (ja) | 信号積分器 | |

| EP0720300B1 (en) | Digital/analog (D/A) converting device with unit current generating circuit having differential switching and reference voltage generating circuits | |

| US6229468B1 (en) | System for quantizing an analog signal utilizing a resonant tunneling diode differential ternary quantizer | |

| JPS58502176A (ja) | ラツチ可能高速設定d−a変換器ビツトスイツチ | |

| CA1262476A (en) | A modified cascode amplifier | |

| US6366229B2 (en) | System for continuous-time modulation | |

| JPH0555900A (ja) | レベル変換回路 | |

| US6208277B1 (en) | High speed analog to digital conversion circuitry using quantum mechanical tunneling structures | |

| EP0289818A2 (en) | A non-inverting repeater circuit for use in semiconductor circuit interconnections | |

| US5153461A (en) | Logic circuit using element having negative differential conductance | |

| US6864816B1 (en) | Method and apparatus for high-speed quantization using resonant tunneling technology | |

| JP3338355B2 (ja) | 半導体回路 | |

| JP2570050B2 (ja) | ディジタル回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070105 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070411 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090709 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090728 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20091027 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20091104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091127 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100112 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100409 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100416 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100512 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100622 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100708 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130716 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |