JP4430175B2 - デジタル制御出力ドライバ及びインピーダンス整合方法 - Google Patents

デジタル制御出力ドライバ及びインピーダンス整合方法 Download PDFInfo

- Publication number

- JP4430175B2 JP4430175B2 JP31364199A JP31364199A JP4430175B2 JP 4430175 B2 JP4430175 B2 JP 4430175B2 JP 31364199 A JP31364199 A JP 31364199A JP 31364199 A JP31364199 A JP 31364199A JP 4430175 B2 JP4430175 B2 JP 4430175B2

- Authority

- JP

- Japan

- Prior art keywords

- output

- pull

- fets

- driver

- pfets

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0005—Modifications of input or output impedance

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/003—Modifications for increasing the reliability for protection

- H03K19/00369—Modifications for compensating variations of temperature, supply voltage or other physical parameters

- H03K19/00384—Modifications for compensating variations of temperature, supply voltage or other physical parameters in field effect transistor circuits

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Logic Circuits (AREA)

Description

【発明の属する技術分野】

本発明は、一般に、高速半導体素子のためのドライバ回路に関するものであり、とりわけ、可変出力インピーダンスを備える高速半導体素子のためのドライバ回路に関するものである。

【0002】

【従来の技術】

最近の集積回路は、一般に、チップの形をとるようになっている。チップ内の集積回路は、信号パッドとして知られるチップの外側のメタライズ層を介して、チップの外界と通信を行う。チップ内から外界への通信の場合、「ドライバ回路」は、チップの外部の信号パッドを介して信号またはデータを駆動する。各種チップの信号パッドは、信号ラインによって互いに接続され、これによって、異なるチップ間の通信が可能になる。

【0003】

チップの信号パッドは、さらに、チップのパッケージに接続され、そのパッケージは、さらに、別の集積回路チップまたは他の同様のデバイスまで延びるプリント回路基板の信号トレースに接続される。信号パッドからチップのパッケージを介して伝送ラインに至る電気的接続には、信号パッドからの信号の伝送を妨害する寄生抵抗、インダクタンス、及びキャパシタンスが含まれる。プリント回路基板の信号トレース自体にも、やはり、信号パッドからの信号送信機の質をそこなう抵抗、キャパシタンス、及びインダクタンスを含む、伝送ライン特性が含まれる。以上の全てが、ドライバ回路によって駆動されなければならない負荷に追加されることになる。

【0004】

チップ間の信号相互接続に存在する寄生抵抗、インダクタンス、及びキャパシタンスのため、それらの信号相互接続を駆動するドライバ回路は、スイッチングが生じる場合(とりわけ、高速または低電力I/Oの場合)、過剰な電圧の変動を回避するように設計することが望ましい。過剰な電圧の変動は、リンギング(ringing)として知られている。リンギングは、回避しなければならないが、それにもかかわらず、最近の集積回路の高速要件を満たすため、スイッチングは、できるだけ速くしなければならない。

【0005】

これまで、CMOSドライバは、NMOS(及び/またはPMOS)FETを利用し、信号パッドをドライバの入力に対するクロック動作入力または静的入力に基づく電圧レベルまで駆動した。駆動NMOS FETは、駆動される伝送ラインの状態に関係なく、チップ内からの入力に基づいてオン/オフされ、その状態に留まった。

【0006】

集積回路の製造プロセスにおける固有のプロセス変動により、同じ機能の実施を意図した異なる集積回路を、「低速」、「公称」、または「高速」と分類することができる。集積回路の製造プロセス中に、いくつかのパラメータに変動が生じる。例えば、ドーピングレベル、FETのチャネル長、トランジスタのゲート酸化物の厚さ、拡散抵抗、及び集積回路の他の特性が、製造プロセス中に変動する。換言すれば、2つの同一であると想定される集積回路は、それらの特性の全てにおいて変化する可能性がある。それらの特性が高速の場合に近づくにつれて、チップ内の多くの構成要素の抵抗は小さくなる。正反対の場合、それらの特性が、理想の場合からますます逸脱するにつれて、チップの性能が劣化し、とりわけ、チップ内の多くの構成要素の抵抗が増大することになるが、その状況は、低速の場合と呼ばれる。

【0007】

また、電圧及び温度が変動すると、単一のチップが高速または低速であるかのような挙動を生じる可能性がある。例えば、集積回路の温度がその最高動作温度に近づくと、集積回路におけるFETの抵抗が増大する。集積回路が高速であるか、低速であるかに関係なく、有効に動作し、さらに、過剰な電圧の変動を回避することが可能な単一のドライバ回路を備えること望ましい。

【0008】

従来のシステムでは、プロセスのパラメータによって、NMOS FET自体のインピーダンスが最小になり、相互接続インピーダンスが最大になる場合、過剰な電圧のオーバシュート及びアンダーシュートを最小限に抑えるため、信号の相互接続を駆動するFETのサイズは、制限された。しかし、このアプローチでは、プロセスのパラメータの変動によって、これらのインピーダンスが正反対の場合に移行した際、スイッチング速度が制限された。

【0009】

このアプローチによって、システムタイミングにさらなる問題が生じた。それによって、スイッチングの遷移の時間的位置の不確実性が増大した。このため、システムの周波数が制限され、性能の劣化が生じた。

【0010】

この問題に取り組む従来技術において既知のアプローチの1つは、CMOS出力ドライバに設定可能な出力駆動段を設けることである。図1には、こうした回路の1つが例示されている。この図には、設定可能な電流源21(FET12及び13のインピーダンスを制御する働きをする)と、2つの出力駆動段22が示されている。CMOS出力段(出力駆動段)22は、容量的に終端された伝送ライン17を駆動する。伝送ラインは、Zoの特性インピーダンスを備えている。設定可能な電流源21によって、CMOS出力駆動段の合成信号源インピーダンスが決まる。その合成信号源インピーダンスは、値Rsc(充電中の信号源抵抗)と値Rsd(放電中の信号源抵抗)に分割することが可能である。概して言えば、Rsc及びRsdが、互いに異なり、及び伝送ライン17の特性インピーダンスZoと異なることが必要な特殊な状況が存在すると想像できるが、Rsc及びRsdが互いに等しく、伝送ライン17の特性インピーダンスZoと等しいことが望ましい。

【0011】

伝送ライン17のもう一方の端部における容量性負荷18に留意されたい。システムは、伝送ライン17の終端における無効(及び無電力損失)不連続部(容量性負荷18)からの反射電力を利用して、出力電圧を2倍にする周知の技法を用いることが可能である。完全に2倍にすることが望ましいが、ただし、出力駆動段22及び23の信号源インピーダンスに関して余分な関心を引くことになる、オーバシュートの付加(低すぎるZoにプラスして多重反射の害)または過剰な立ち上がり時間(高すぎるZo及び付随する多重反射)を伴わなければという条件がつく。負荷がリアクタンスをもつ場合、Rscを介した充電によって放出される電力が、Zoを介して送り出され、反射されて(及び、負荷における電圧が2倍になり)、Zoを介して戻され、さらに、依然としてオンのRscによる放電によって、再反射を生じることなく、吸収されるという点に留意されたい。同様のシーケンスの事象が、Rsdが関与する放電の場合にも生じる。(もちろん、全て、Rsc=Zo=Rsdと仮定した場合である)。反射を伴わない、負荷に対する真の電力伝達を予測した終端抵抗が存在する状況であっても、出力駆動段の信号源インピーダンスの制御は、やはり重要である。

【0012】

CMOSデバイスの動作を理解するため、図示のように接続された4つのCMOSデバイス12、13、14、及び15を含む出力駆動段22について考察する。デバイス14及び15は、そのZoがRsc(プルアップ中)及びRsd(プルダウン中)によって整合させられる、伝送ライン17を駆動する出力端子16において、それぞれ、プルアップ(DVDDまで充電)及びプルダウン(DGndまで放電)するためのスイッチの働きをする。もちろん、スイッチングデバイス(CMOSデバイス)14及び15は、所望の出力波形に従って、適切な交番でオン/オフに駆動され、デバイス14及び15の両方をトライステート出力端子16に対してオフにすることができるが、両方のデバイスが同時にオンになることはない。これに関して、ドライバ回路32及び34は、スイッチングデバイス14及び15をON/OFFするために設けられている。一般に、既知のように、一方のドライバ回路32は、出力信号を低値から高値に駆動するように、FET14を制御する働きをし、もう一方のドライバ回路34は、出力信号を高値から低値に駆動するように、FET15を制御する働きをする。

【0013】

デバイス13は、デバイス14の極めて低いオン抵抗との組み合わせによって、Rscを生じる設定可能な値の抵抗の働きをする。同様に、デバイス12は、デバイス15の比較的低いオン抵抗との組み合わせによって、Rsdを生じる設定可能な値の抵抗の働きをする。デバイス13の抵抗は、電圧PGate20の値によって制御され、同様に、デバイス12の抵抗は、電圧NGate19の値によって決まる。次に、P形デバイス13及びN形デバイス12が、ほぼ等しい相互コンダクタンスを備えているものと仮定すると、信号NGate19及びPGate20は、(1)外部から変化させて、プロセス変動にもかかわらず、Zoの適正な広い範囲にわたってRsc及びRsdを調整できるように、(2)共に変化して、NGateがDGndからDVDDへと上昇するにつれて、PGAETが、相応じて、DVDDからDGndへと低下するように、(3)自動調整で、温度の影響を補償するように制御される。本発明の譲受人に譲渡された米国特許第5,581,197号には、これらの目的を実現するための1つの方法及び回路についての記載があり、参照によって、そっくりそのまま本明細書に組み込まれている。上述の回路要素は、プロセス及び温度の変動に対して、出力インピーダンスを有効に変化させるが、回路の性能は、比較的わずかな量のノイズによってさえ、かなりの(悪)影響を受ける可能性のあることが明らかになった。

【0014】

【発明が解決しようとする課題】

従って、プロセス、電圧、及び温度(PVT)に対して出力駆動段の出力インピーダンスを有効に変化させ、ノイズの悪影響をより受けにくい、改良された出力駆動段を提供することが望まれる。とりわけ、その出力インピーダンスが、プロセス、温度、及び電圧に対して変化する際、基板のトレースインピーダンスに正確に整合するように、前記出力インピーダンスを有効に変化させることが可能な、改良された出力駆動段を提供することが望まれる。

【0015】

【課題を解決するための手段】

本発明のいくつかの目的、利点、及び新規な特徴については、後続の説明において部分的に記述されている。当該技術者であれば、下記説明を検討することによって明らかになり、または本発明を実施することによって知ることになるであろう。本発明の目的及び利点は、特許請求の範囲に詳細に示された手段及び組み合わせによって実現し、得ることが可能である。

【0016】

前記利点及び新規な特徴を実現するため、本発明は、一般に、半導体素子の信号パッドを介して信号を駆動するための可変インピーダンス出力ドライバを目指している。本発明の態様の1つによれば、出力ドライバには、電気的に並列に接続された複数のpチャネル電界効果トランジスタ(PFET)が含まれる。複数のPFETのそれぞれのソースノードは、電気的に互いに接続され、複数のPFETのそれぞれのドレインノードは、電気的に互いに接続される。ドライバには、さらに、電気的に並列に接続された複数のnチャネル電界効果トランジスタ(NFET)も含まれる。複数のNFETのそれぞれのソースノードは、電気的に互いに接続され、複数のNFETのそれぞれのドレインノードは、電気的に互いに接続される。さらに、複数のPFETのドレインノードは、複数のNFETのそれぞれのソースノードと電気的に接続され、さらに、信号パッドと(好適には、ESD抵抗器を介して)電気的に結合される。複数のPFETの第1のPFETは、プルアッププリドライバ回路の出力によって駆動されるゲートノードを備えており、複数のNFETの第1のNFETは、プルダウンプリドライバ回路の出力によって駆動されるゲートノードを備える。しかし、残りのPFET及びNFETには、制御回路から出力される較正ワードによって制御されるに従って、プルアッププリドライバ回路及びプルダウンプリドライバ回路によって駆動されるゲートノードを備える。

【0017】

本発明の新規の態様によれば、PFET及びNFETは、PFET及びNFETのうちの選択された互いに異なるそれぞれを選択的にオン/オフして、ドライバ回路の有効出力インピーダンスを制御可能に変化させるように制御される。この機能を容易にするため、複数のPFETのチャネル幅は、サイズが可変である。チャネル幅のサイズは、幅寸法が漸進的に1/2に変化するのが望ましい。好適には全部で8つのPFET及び8つのNFETが設けられているので(他の数のPFET及びNFETを用いることも可能であるが)、単一のデジタル制御バイトを用いて、回路の出力インピーダンスを制御することが可能である。PFET及びNFETは、出力インピーダンスが、広範囲のプロセス、電圧、及び温度(PVT)条件にわたってほぼ一定になるように制御されるのが望ましい。

【0018】

本発明のもう1つの態様によれば、半導体素子の信号パッドを介して信号を駆動するため、可変インピーダンス出力ドライバが設けられる。ドライバには、信号パッドに対する出力信号を低状態から高状態に駆動するように構成されたプルアッププリドライバ回路と、信号パッドに対する出力信号を高状態から低状態に駆動するように構成されたプルダウンプリドライバ回路が含まれる。さらに、ドライバ回路には、信号パッドと、プルアッププリドライバ回路及びプルダウンプリドライバ回路の両方との間に挿入された電界効果トランジスタ(FET)回路網も含まれる。最後に、ドライバ回路には、FET回路網に入力される複数の出力信号を有するインピーダンス制御回路が含まれ、それによってインピーダンス制御回路の出力信号が、出力ドライバの出力インピーダンスを制御可能に変化させる働きをする。

【0019】

本発明のさらにもう1つの態様によれば、半導体素子の信号パッドを介して信号を駆動するように構成された出力ドライバ回路の出力インピーダンスを制御可能に変化させるための方法が提供される。この態様によれば、この方法には、プルアップFETの出力の両端に電気的に並列に接続された複数のpチャネル電界効果トランジスタ(PFET)を設けるステップと、プルダウンFETの出力の両端に電気的に並列に接続された複数のnチャネル電界効果トランジスタ(NFET)を設けるステップが含まれており、プルアップFETのドレインノードは、プルダウンFETのソースノードに電気的に接続され、プルダウンFETのソースノードは、信号パッドに電気的に結合される。この方法には、さらに、複数のPFET及びNFETのゲートノードに対して複数の電気信号を加えて、複数の電気信号の集合的状態によって、出力ドライバの出力インピーダンスを制御可能に変化させるステップも含まれる。

【0020】

本発明には、多くの利点があるが、本発明の主要な利点は、広いPVT範囲にわたって、ほぼ一定した、正確な出力抵抗が提供されるという点にある。本発明の他の特徴及び利点については、下記の図面及び詳細な説明を検討すれば、当該技術者には明らかになるであろう。こうしたその他の特徴及び利点のすべては、本発明の範囲内に含まれるものと意図されている。

【0021】

【発明の実施の形態】

以上で本発明の概要を述べたが、次に、図面によって示されるような本発明の説明について詳細に言及することにする。本発明の説明は、これらの図面に関連して行われるが、それによって開示される実施態様に制限することを意図したものではない。それどころか、特許請求の範囲によって定義されるように本発明の思想及び範囲内に含まれる全ての代替案、修正案、及び等価物を包含するように意図されている。

【0022】

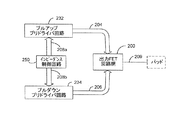

次に、図面を参照して、図2に言及する。図2は制御可能な可変出力インピーダンスを備えたドライバ回路を示すブロック図であり、図1に示す従来技術によるものに改良を加えている。すなわち、ドライバ回路には、プルアッププリドライバ回路132と、プルダウンプリドライバ回路134が含まれる。既知のように、プルアッププリドライバ回路要素は、出力値を低状態から高状態に(例えば、論理0から論理1に)駆動する働きをし、プルダウンプリドライバ回路要素134は、出力値を高状態から低状態に駆動する働きをする。NFET114及び115は、それぞれ、プルアッププリドライバ回路132及びプルダウンプリドライバ回路134の出力によって駆動される。ドライバ回路の出力は、NFET114のドレインノードとNFET115のソースノードとの間における電気的接続点である、ライン102において認められる値である。図3に関連してさらに後述するように、FET回路網100は、信号ライン102とドライバパッドの間に挿入される。FET回路網100によって、ドライバ回路の出力インピーダンスを変化させて、基板のトレースインピーダンスと整合させる働きをする、制御可能な可変インピーダンスが与えられる。FET回路網100によって与えられるインピーダンスは、制御回路(制御ブロック)110によって制御される。FET回路網の出力は、導体104を介してドライバパッドに経路指定される。

【0023】

FET回路網100の構成及び動作についてさらに詳述するため、次に、この回路要素をより詳細に示した図3を参照する。特に、FET回路網100は、信号ライン102、104、及び制御回路110に関連して示されている。FET回路網には、電気的に並列に接続された複数のNFETデバイス111、112、113、114、115、及び116が含まれる。NFET111〜116は、それぞれ、NFETデバイスのコンダクタンス(従って、抵抗)を決めるチャネル幅によって形成される。オンになると、各NFETは、ライン102からライン104に電圧を伝える。NFETデバイス111〜116の2つ以上がオンになると、抵抗器のような働きをして、並列に結合し、より小さい抵抗を提供する。こうして、ドライバ回路の出力インピーダンスが変化する。NFETデバイス111〜116は、チャネル幅が漸減するように、とりわけ、チャネル幅が1/2に減少するように設計されることが望ましい。従って、例えば、NFET111のチャネル幅をある値Xとし、NFET112のチャネル幅を約1/2Xとし、NFET113のチャネル幅を約1/4Xとし、...以下同様にすることが可能である。従って、制御ブロック110の集合的出力は、NFETデバイス111〜116のうち選択されたデバイスをオンにすることにより、ドライバ回路の出力インピーダンスを正確に制御するデジタル制御ワードの働きをすることが可能である。制御ブロック110の回路要素または論理回路が、プロセス、電圧、及び温度(PVT)によって決まるのは明らかであるが、ここで説明を行う必要はない。FET回路網100は、少なくとも1つの経路が、必ずオンになり、信号が、信号ライン102から信号ライン104、従って、信号経路に通るのを可能にするように設計されている。

【0024】

図2及び図3の回路要素によって、ドライバ回路の出力インピーダンスを制御可能に変化させるための有効な手段が提供されるが、それにもかかわらず、いくつかの欠点がある。第1に、回路要素の適正な動作は、ドライバの供給電圧が、NFETのターンオン電圧の少なくとも2倍になるものと想定している。そうでなければ、適正な動作は行われない。さらに、コア論理レベルがドライバ供給電圧(DVDD)に等しい環境では、ライン102(図2)における信号値は、実際には、FETデバイス114及び115の両端におけるターンオン電圧の合計に等しい電圧降下のため、高の論理出力より低くなる。従って、代替の解決策が所望される。

【0025】

次に、本発明のドライバ回路を例示したブロック図である図4を参照する。従来技術によるシステムの回路と同様、本発明のドライバ回路は、プルアッププリドライバ回路232及びプルダウンプリドライバ回路234を備えたドライバ回路環境において動作する。これらの回路は、ドライバに対して(または、トライステートに対して)それぞれ、出力信号を低状態から高状態に、及び高状態から低状態に駆動する働きをする。回路232及び234の出力204及び206は、本発明に従って構成された出力FET回路網200に送られる。図4に示すように、出力FET回路網200の出力209は、信号パッドに送られる。また、インピーダンス制御回路250は、較正ワードの形をとる制御信号208a及び208bを発生する。後述する態様において、その制御信号208a及び208bを用いて、出力FET回路網200の動作を制御する。

【0026】

本発明に従って構成された出力ドライバ回路の一般的な回路ブロックについて列挙したが、次に、本発明に従って構成された出力FET回路網200の好適な実施態様を詳細に例示した図5を参照する。要するに、FET回路網200には、各PFETのソースノードが他のソースノードと電気的に接続され、各PFETのドレインノードが他のドレインノードと電気的に接続されるように、電気的に並列に接続されたPFETのアレイ210が含まれる。回路網200には、さらに、ソースノードが、互いに電気的に接続され、さらにPFETアレイ210のドレインノードと電気的に接続され、ドレインノードが、互いに電気的に接続されるように、電気的に接続されたNチャネル電界効果トランジスタ(NFET)のアレイ220も含まれる。

【0027】

好適な実施態様によれば、PFETアレイ210には、9つのPFETデバイス211、212、213、214、215、216、217、218、及び219が含まれる。これら各PFETデバイスのソースノードは、電位がDVDDの共通信号ライン201によって互いに電気的に接続される。同様に、NFETデバイスアレイ220には、9つのNFETデバイス221、222、223、224、225、226、227、228、及び229が含まれる。さらに、駆動されていない出力を軽くプルダウンして、浮動しないようにするため(CMOSデバイスにおいて、フローチング入力は望ましくないので)、出力にNFETデバイス230を設けることが可能である。複数のNFETデバイスのそれぞれのドレインノードは、電位がDGndのライン203によって互いに電気的に接続される。

【0028】

PFETアレイ210には、プルアッププリドライバ回路232の出力204によって直接駆動される第1のPFET211が含まれる。同様に、NFETアレイ220には、プルダウンプリドライバ回路234の出力206によって駆動される第1のNFETデバイス221が含まれる。2つのアレイにおけるPFET及びNFETの残りは、ラベルPU[7:0]及びPD[7:0]によって表示された、バス208a及び208bで供給される制御信号によって駆動される。図6に関連して例示され、説明されるように、ライン208a及びライン208bで供給される制御信号によって、アレイ210及び220の個々のPFET及びNFETデバイスを選択的にオン/オフして、ドライバ回路の出力インピーダンスを有効に変化させるために用いられる、デジタル制御ワードが生成される。

【0029】

好適な実施態様によれば、2つのアレイにおけるPFET及びNFETのそれぞれのチャネル幅は、その値の有効な2進数重み付けを提供するため、漸進的に1/2に減少するように設計されている。従って、例えば、PFET212のチャネル幅がXで、PFET212のコンダクタンスがGの場合、PFET213のチャネル幅が、1/2Xになると、PFET213のコンダクタンスは0.5Gになる。

【0030】

従って、本発明の好適な実施態様に従って、図5に例示されたそれぞれのトランジスタの物理的サイズ(図示の通りの)を指定する表1が、以下で示されている。しかし、当然明らかなように、本発明は表に記載の値に制限されるものではなく、この表は、本発明の望ましい実施態様を十分に開示するためだけに作成されたものである。

【0031】

【表1】

【0032】

本発明の概念及び教示に一致するように、さまざまな方法で制御回路要素250(図4)を実施することが可能である。本発明の概念の目的にとって重要なのは、制御回路250が、FETアレイ200内の個々のPFET及びNFETの状態を制御して、ドライバ回路の出力インピーダンスを変化させる。それにより出力抵抗がプロセス、電圧、及び温度の全範囲にわたってほぼ一定に留まるようにすることである。この一般的な目的を達成するため、さまざまな構成及び回路を実施することが可能であるが、図6には、こうした回路が1つだけしか示されていない。

【0033】

次に図6を参照すると、出力ドライバのインピーダンスのグループが外部抵抗と整合するように、または外部抵抗のある倍数になるように設定するために用いることが可能な、2組の制御信号(1つはプルアップトランジスタ用で、1つはプルダウントランジスタ用)が生じる。通常動作中、較正ドライバのPFETアレイ210には、電流が流れる。PFETアレイ210の各トランジスタは、公称では、デジタル式に制御される出力ドライバのプルアップPFETアレイにおける各トランジスタのサイズに同等である。電流は、正の電源DVDD(クリーンである、または汚れている可能性がある)から、PFETアレイ210を通り、静電放電(ESD)保護抵抗器242を通り、パッド241から出て、外部抵抗器(不図示)を通り、アースに流れる。

【0034】

PFETアレイ210及びESD保護抵抗器242のインピーダンスは、外部抵抗器と共に分圧器を形成し、パッド241のノードにおける正の供給電圧を分圧する。このノードは、アナログ比較器260の反転端子に対する入力である。アナログ比較器260の非反転入力は、抵抗器262及び264によって形成される分圧器に接続される。抵抗器262及び264は、オンチップ抵抗器とすることが可能であり、正の電源と負の電源の間に直列に接続される。正の電源と負の電源の間にある中間のノードが、アナログ比較器260の非反転入力に接続される。実施態様の1つでは、抵抗器262及び264が、同じ値であり、従って、アナログ比較器260の非反転入力における電圧はVDD/2になる。アナログ比較器260の出力は、デジタルアップ/ダウンカウンタ266のDIR入力に接続されて、アップ/ダウンカウンタ266がカウントする方向を制御する。アップ/ダウンカウンタ266は、その最高出力からその最低出力に、及びその最低出力から最高出力にぐるりと一回転することがないように、飽和カウンタとすることが可能である。アップ/ダウンカウンタ266は、クロック入力CLKのストローブ時に、DIRの状態に従ってその出力の2進値をインクリメントまたはデクリメントする。アップ/ダウンカウンタ266の出力は、信号PU[7:0]を発生し、そのそれぞれが、プリドライバ回路を制御し/イネーブルにして、PFETアレイ210のトランジスタの1つのゲートを駆動するために用いられる。好適な実施態様の場合、前述のように、PFETアレイ210における各トランジスタのサイズは、そのゲートに接続されたPU[7:0]のビットの重要度に対応するようにスケーリングが施される。例えば、P[N]が、コンダクタンスがGのFETを制御する場合、P[N+1]は、コンダクタンスが2GのFETを制御することになる。

【0035】

比較器260の反転入力が、アナログ比較器260の非反転入力より高い場合、アップ/ダウンカウンタ266は、カウントダウンする。これによって、PFETアレイ210のトランジスタのより多くがオフになり、PFETアレイ210のインピーダンスが増大する。比較器260の反転入力が、アナログ比較器260の非反転入力より低い場合、アップ/ダウンカウンタ266は、カウントアップし、PFETアレイ210のトランジスタのより多くがオンになり、PFETアレイ210のインピーダンスが減少する。PFETアレイ210及びESD保護抵抗器242のインピーダンスが、外部抵抗器の抵抗値にほぼ整合すると、このフィードバックシステムは、安定化する。

【0036】

アナログ比較器274に対する入力は、比較器260の入力と同様に発生する。アナログ比較器274の出力は、アップ/ダウンカウンタ286のDIR入力に接続される。アップ/ダウンカウンタ286の出力信号は、信号PD[7:0]に接続される。これらの信号は、プリドライバ回路を制御し/イネーブルにして、NFETアレイ220のトランジスタのゲートを駆動するために用いられる。比較器274の反転入力が、アナログ比較器274の非反転入力より低い場合、アップ/ダウンカウンタ286は、カウントダウンし、NFETアレイ220のトランジスタのより多くがオフになり、NFETアレイ220のインピーダンスが増大する。比較器274の反転入力が、アナログ比較器274の非反転入力より高い場合、アップ/ダウンカウンタ286は、カウントアップし、NFETアレイ220のトランジスタのより多くがオンになり、NFETアレイ130のインピーダンスが減少する。

【0037】

やはり、前述のように、図6の回路は、ただ単に、FETアレイ200の制御入力をいかに発生することが可能かを例証するものとして示されているだけである。これらの信号の特定の発生方法は、本発明に対する制限をなすものではなく、従って、本明細書でこれ以上詳述する必要はない。しかし、図6の回路によって、該システムが、較正制御ワードを、従って、出力ドライバの出力インピーダンスを絶えず更新する(比較器及びアップ/ダウンカウンタを介して)ことが可能になるのは明らかである。

【0038】

より一般的には、図6の較正回路要素は、外部精密抵抗器のインピーダンスまたはその倍数と整合するために、全ての出力ドライバのPFETインピーダンスを設定するように設計される。通常の動作中、データまたはクロック出力ドライバと同等のサイズのPFETアレイには、電流が流れる。電流は、基板上のI/Oパッド241を通って、GNDに接続された外部抵抗器に流れる。この電流経路によって、分圧器が形成されるが、この場合、2つの抵抗はドライバの出力抵抗と外部抵抗器である。パッドは、差動増幅器260の端子に対する入力203の働きをする。増幅器260のもう一方の端子は、VDD/2である。差動増幅器に対する入力電圧間の差は、ドライバの出力抵抗と外部抵抗器の間で抵抗の不整合として感知される。デルタ電圧によって、差動増幅器の出力が、アップ/ダウンカウンタ266にその出力をインクリメント/デクリメントするように設定する。クロックエッジを受信すると、アップ/ダウンカウンタは、新たな2進カウントPU[n:0](nビットカウンタの場合)を駆動する。この較正ワードは、較正回路要素のプルアップドライバによって利用され、他のドライバに分配される。PU[n:0]における増分2進変化によって、較正ドライバに増分の抵抗変化が生じる。較正ドライバは、新たな較正ワードを備えているので、新たな出力抵抗を備えている。較正プロセスが継続され、通常のチップ動作にとって透過的であるのは明らかである。

【0039】

図6の較正回路要素は、さらに、外部精密抵抗器のインピーダンスまたはその倍数と整合するために全ての出力ドライバのNFETインピーダンスを、設定するように設計される。通常の動作中、データまたはクロック出力ドライバと同等のサイズのNFETアレイには、電流が流れる。電流は、基板上のI/Oパッド241を通って、VDDに接続された外部抵抗器に流れる。この電流経路によって、ドライバの出力抵抗と外部抵抗器の間に分圧器が形成される。パッドは、差動増幅器274の端子に対する入力201の働きをする。増幅器274のもう一方の端子は、VDD/2である。差動増幅器に対する入力電圧間の差は、ドライバの出力抵抗と外部抵抗器の間で抵抗の不整合として感知される。デルタ電圧によって、差動増幅器の出力が、アップ/ダウンカウンタ286にその出力をインクリメント/デクリメントするように設定する。クロックエッジを受信すると、アップ/ダウンカウンタは、新たな2進カウントPD[n:0]を駆動する。この較正ワードは、較正回路要素のプルダウンドライバによって利用され、他のドライバに分配される。PD[n:0]における増分2進変化によって、較正ドライバに増分の抵抗変化が生じる。較正ドライバは、新たな較正ワードを備えているので、新たな出力抵抗を備えている。較正プロセスが継続され、通常のチップ動作にとって透過的である。

【0040】

以上の説明は、例証及び解説を目的として提示されたものである。本発明を余すところなく説明しようとか、開示の形態そのままに制限しようとするものではない。以上の教示に鑑みて、明白な修正または変更が可能である。例えば、較正ワード208a及び208b(本明細書では、8ビットワードとして例示されている)は、さまざまなサイズが可能であり、8ビット未満とすることも、または、8ビットを超えることも可能であることが理解されよう。

【0041】

論述した実施態様は、本発明の原理、及びその実際の応用例の最良な例証を提示することによって、当該技術者が、企図される特定の用途に適するように、さまざまな実施態様において、さまざまな修正を施して、本発明を利用できるようにするために、選択され解説された。こうした全ての修正及び変更は、公正かつ合法的に権利を与えられる範囲に従って解釈される場合、特許請求の範囲によって決まる本発明の範囲内に含まれる。

【0042】

以下においては、本発明の種々の構成用件の組み合わせからなる例示的な実施態様を示す。

1.半導体素子の信号パッド(241)を介して信号を駆動する可変インピーダンス出力ドライバ(200)であって、

電気的に並列に接続された複数のpチャネル電界効果トランジスタ(PFET)(210)であって、該複数のPFET(211〜219)のそれぞれのソースノードが互いに電気的に接続され、前記複数のPFET(211〜219)のそれぞれのドレインノードが互いに電気的に接続される、前記複数のpチャネル電界効果トランジスタ(PFET)(210)と、

電気的に並列に接続された複数のnチャネル電界効果トランジスタ(NFET)(220)であって、該複数のNFET(221〜229)のそれぞれのソースノードが互いに電気的に接続され、前記複数のNFET(221〜229)のそれぞれのドレインノードが電気的に接続されており、前記複数のPFET(211〜219)のそれぞれのドレインノードが、前記複数のNFET(221〜229)のそれぞれのソースノードに電気的に接続されて、更に信号パッド(241)に電気的に接続されている、前記複数のnチャネル電界効果トランジスタ(NFET)(220)とが含まれており、

前記複数のPFET(211〜219)の第1のPFET(211)が、プルアッププリドライバ回路(232)の出力によって駆動されるゲートノードを備えており、前記複数のNFET(221〜229)の第1のNFET(221)が、プルダウンプリドライバ回路(234)の出力によって駆動されるゲートノードを備えており、残りのPFET及びNFETが、それぞれ、制御回路(250)によって生成される較正ワードによって制御されるに従って、前記プルアップ及びプルダウンプリドライバ回路(232,234)によって駆動されるゲートノードを備えている、

ドライバ。

2.前記複数のPFET(211〜219)のサイズが可変である、上記1のドライバ。

3.前記複数のPFET(211〜219)のサイズは、前記第1のPFET(211)を除いて幅寸法が漸進的に小さくなるようになっている、上記2のドライバ。

4.前記複数のPFET(211〜219)のサイズは、前記第1のPFET(211)を除いて幅寸法が漸進的に1/2に変化する、上記2のドライバ。

5.前記複数のNFET(221〜229)のサイズが可変である、上記1のドライバ。

6.前記複数のNFET(221〜229)のサイズは、前記第1のNFET(221)を除いて幅寸法が漸進的に小さくなるようになっている、上記5のドライバ。

7.前記複数のNFET(221〜229)のサイズは、前記第1のNFET(221)を除いて幅寸法が漸進的に1/2に変化する、上記6のドライバ。

8.前記信号パッドと、前記複数のPFET(211〜219)のドレインノード及び前記複数のNFET(221〜229)のソースノードの共通接続部との間に、電気的に直列に配置された抵抗器(242)を更に含む、上記1のドライバ。

9.半導体素子の信号パッド(241)を介して信号を駆動する可変インピーダンス出力ドライバ(200)であって、

前記信号パッド(241)に対する出力信号を低状態から高状態に駆動するように構成されたプルアッププリドライバ回路(232)と、

前記信号パッド(241)に対する出力信号を高状態から低状態に駆動するように構成されたプルダウンプリドライバ回路(234)と、

前記信号パッド(241)と、前記プルアッププリドライバ回路(232)及び前記プルダウンプリドライバ回路(234)の両方との間に挿入された電界効果トランジスタ(FET)回路網と、

前記FET回路網に入力される複数の出力信号(208a,208b)を有するインピーダンス制御回路(250)とが含まれており、それによって前記インピーダンス制御回路の出力信号(208a,208b)が、前記出力ドライバ(200)の出力インピーダンスを制御可能に変化させる働きをする、

ドライバ。

10.前記FET回路網に、電気的に並列に接続された複数のpチャネル電界効果トランジスタ(FET)(210)が含まれており、前記複数のPFET(211〜219)のそれぞれのソースノードが、互いに電気的に接続され、前記複数のPFET(211〜219)のそれぞれのドレインノードが、互いに電気的に接続されている、上記9のドライバ。

【0043】

【発明の効果】

本発明により、プロセス、電圧、及び温度(PVT)に対して出力駆動段の出力インピーダンスを有効に変化させ、ノイズの悪影響を受けにくい、改良された出力駆動段が提供される。特に、その出力インピーダンスが、プロセス、電圧、及び温度に対して変化する際、基板のトレースインピーダンスに正確に整合するように、前記出力インピーダンスを有効に変化させることが可能な、改良された出力駆動段が提供される。

【図面の簡単な説明】

【図1】従来技術において既知の可変出力インピーダンスを備えたドライバ回路の概略図である。

【図2】デジタル式に制御される可変出力インピーダンスを備えたドライバ回路の実施態様の1つを例示するブロック図である。

【図3】図2のブロック図の一部に関する概略図である。

【図4】本発明に従って構成された、デジタル式に制御される可変出力インピーダンスを備えたドライバ回路を例示するブロック図である。

【図5】図4のブロック図のFET回路網の部分に関する概略図である。

【図6】図4のブロック図に例示された、考えられるインピーダンス制御回路の一部に関する概略図である。

【符号の説明】

200 出力FET回路網

208a、208b 出力信号

210 PFETのアレイ

211〜219 PFET

220 NFETのアレイ

221〜229 NFET

232 プルアッププリドライバ回路

234 プルダウンプリドライバ回路

241 信号パッド

250 制御回路

Claims (10)

- 半導体素子の信号パッド(241)を介して信号を駆動する可変インピーダンス出力ドライバ(200)であって、

該出力ドライバ(200)が、

前記信号パッド(241)に対する出力信号を低状態から高状態に駆動するように構成されたプルアッププリドライバ回路(232)と、

前記信号パッド(241)に対する出力信号を高状態から低状態に駆動するように構成されたプルダウンプリドライバ回路(234)と、

前記信号パッド(241)と前記プルアッププリドライバ回路(232)との間に、各々が互いに電気的に並列に配置された第1の複数の電界効果トランジスタ(FET)と、前記信号パッド(241)と前記プルダウンプリドライバ回路(234)との間に、各々が互いに電気的に並列に配置された第2の複数の電界効果トランジスタ(FET)とからなる電界効果トランジスタ(FET)回路網と、

前記出力ドライバ(200)の出力インピーダンスを制御するための2組の2進カウント値(208a、208b)を生成し、一方の組の2進カウント値(208a)を前記プルアッププリドライバ回路(232)に、他方の組の2進カウント値(208b)を前記プルダウンプリドライバ回路(234)に送るインピーダンス制御回路(250)

を備え、

前記第1の複数のFETの各々は互いに幅寸法が異なり、前記第2の複数のFETの各々は互いに幅寸法が異なり、

前記第1の組の2進カウント値(208a)は前記プルアッププリドライバ回路(232)を介して前記第1の複数の電界効果トランジスタ(FET)に送られ、前記第2の組の2進カウント値(208b)は前記プルダウンプリドライバ回路(234)を介して前記第2の複数の電界効果トランジスタ(FET)に送られ、

前記第1の複数のFETのうちの少なくとも2以上のFETの各々が前記第1の組の2進カウント値のそれぞれのビット位置に対応付けられており、前記第2の複数のFETのうちの少なくとも2以上のFETの各々が、前記第2の組の2進カウント値のそれぞれのビット位置に対応付けられており、これらの対応付けは、前記第1及び第2の組の2進カウント値の各組について、各組を構成するビット列の上位ビット位置から下位ビット位置に向かうにしたがって、各ビット位置に対応付けられた前記第1及び第2の複数のFETの各FETの幅寸法が漸進的に小さくなるようにされており、

前記インピーダンス制御回路(250)が、

前記信号パッド(241)上の電圧と第1の電圧とを比較する第1の差動増幅器(260)と、

前記信号パッド(241)上の電圧と第2の電圧とを比較する第2の差動増幅器(274)と、

前記第1の差動増幅器(260)の比較結果にしたがって、前記第1の組の2進カウント値のカウントアップ及びカウントダウンを行う第1のデジタルアップ/ダウンカウンタ(266)と、

前記第2の差動増幅器(274)の比較結果にしたがって、前記第2の組の2進カウント値のカウントアップ及びカウントダウンを行う第2のデジタルアップ/ダウンカウンタ(286)

を備え、

前記第1及び第2の組の2進カウント値のそれぞれのビット位置に対応付けられた前記FETの各々は、前記第1及び第2の組の2進カウント値のうちの対応するビット位置のビットが前記第1及び第2のデジタルアップ/ダウンカウンタ(266、286)の前記カウントアップまたはカウントダウンによって1または0に設定されるのに応じてオンまたはオフにされる、可変インピーダンス出力ドライバ。 - 前記第1の複数のFETの各々がpチャネル電界効果トランジスタ(PFET)(211-219)であり、この複数のPFET(211-219)のそれぞれのソースノードが互いに電気的に接続され、該複数のPFET(211〜219)のそれぞれのドレインノードが互いに電気的に接続される、請求項1の可変インピーダンス出力ドライバ。

- 前記第2の複数のFETの各々がnチャネル電界効果トランジスタ(NFET)(221〜229)であり、この複数のNFET(221〜229)のそれぞれのソースノードが互いに電気的に接続され、該複数のNFET(221〜229)のそれぞれのドレインノードが互いに電気的に接続され、前記複数のPFET(211〜219)のそれぞれのドレインノードが、前記複数のNFET(221〜229)のそれぞれのソースノードに電気的に接続されると共に、前記信号パッド(241)にも電気的に接続され、

前記複数のPFET(211〜219)の第1のPFET(211)が、前記プルアッププリドライバ回路(232)の出力によって駆動され、前記複数のNFET(221〜229)の第1のNFET(221)が、前記プルダウンプリドライバ回路(234)の出力によって駆動され、残りのPFETとNFETが、前記第1の組と第2の組の2進カウント値によってそれぞれ制御される、請求項2の可変インピーダンス出力ドライバ。 - 前記複数のPFET(211〜219)のサイズが可変である請求項3の可変インピーダンス出力ドライバ。

- 前記複数のPFET(211〜219)のサイズは、前記第1のPFET(211)を除いて幅寸法が漸進的に小さくなるようになっている請求項3または4の可変インピーダンス出力ドライバ。

- 前記複数のPFET(211〜219)のサイズは、前記第1のPFET(211)を除いて幅寸法が漸進的に1/2に変化する請求項3乃至5のいずれかの可変インピーダンス出力ドライバ。

- 前記複数のNFET(221〜229)のサイズが可変である請求項3乃至6のいずれかの可変インピーダンス出力ドライバ。

- 前記複数のNFET(221〜229)のサイズは、前記第1のNFET(221)を除いて幅寸法が漸進的に小さくなるようになっている請求項3乃至7のいずれかの可変インピーダンス出力ドライバ。

- 前記複数のNFET(221〜229)のサイズは、前記第1のNFET(221)を除いて幅寸法が漸進的に1/2に変化する請求項3乃至8のいずれかの可変インピーダンス出力ドライバ。

- 前記信号パッドと、前記複数のPFET(211〜219)のドレインノード及び前記複数のNFET(221〜229)のソースノードの共通接続部との間に、電気的に直列に配置された抵抗器(242)を更に含む請求項3乃至9のいずれかの可変インピーダンス出力ドライバ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US186006 | 1998-11-04 | ||

| US09/186,006 US6118310A (en) | 1998-11-04 | 1998-11-04 | Digitally controlled output driver and method for impedance matching |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000151384A JP2000151384A (ja) | 2000-05-30 |

| JP2000151384A5 JP2000151384A5 (ja) | 2007-01-25 |

| JP4430175B2 true JP4430175B2 (ja) | 2010-03-10 |

Family

ID=22683282

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP31364199A Expired - Fee Related JP4430175B2 (ja) | 1998-11-04 | 1999-11-04 | デジタル制御出力ドライバ及びインピーダンス整合方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6118310A (ja) |

| EP (1) | EP0999643A1 (ja) |

| JP (1) | JP4430175B2 (ja) |

Families Citing this family (98)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6366129B1 (en) * | 1998-11-10 | 2002-04-02 | Intel Corporation | Method and apparatus for buffering an input-output node of an integrated circuit |

| US6204683B1 (en) * | 1999-05-18 | 2001-03-20 | Intel Corporation | Apparatus and method for reducing crosstalk in an integrated circuit which includes a signal bus |

| US6278306B1 (en) | 1999-06-07 | 2001-08-21 | Sun Microsystems, Inc. | Method for an output driver with improved slew rate control |

| US6339351B1 (en) | 1999-06-07 | 2002-01-15 | Sun Microsystems, Inc. | Output driver with improved impedance control |

| US6281729B1 (en) | 1999-06-07 | 2001-08-28 | Sun Microsystems, Inc. | Output driver with improved slew rate control |

| US6366139B1 (en) | 1999-06-07 | 2002-04-02 | Sun Microsystems, Inc. | Method for an output driver with improved impedance control |

| US6316957B1 (en) * | 1999-09-20 | 2001-11-13 | Sun Microsystems, Inc. | Method for a dynamic termination logic driver with improved impedance control |

| US6294924B1 (en) | 1999-09-20 | 2001-09-25 | Sun Microsystems, Inc. | Dynamic termination logic driver with improved slew rate control |

| US6420913B1 (en) | 1999-09-20 | 2002-07-16 | Sun Microsystems, Inc. | Dynamic termination logic driver with improved impedance control |

| US6297677B1 (en) | 1999-09-20 | 2001-10-02 | Sun Microsystems, Inc. | Method for a dynamic termination logic driver with improved slew rate control |

| US6316956B1 (en) * | 1999-10-22 | 2001-11-13 | Motorola, Inc. | Multiple redundant reliability enhancement method for integrated circuits and transistors |

| US6300789B1 (en) * | 1999-12-22 | 2001-10-09 | Intel Corporation | Dynamic termination for non-symmetric transmission line network topologies |

| US6347850B1 (en) * | 1999-12-23 | 2002-02-19 | Intel Corporation | Programmable buffer circuit |

| US6356105B1 (en) * | 2000-06-28 | 2002-03-12 | Intel Corporation | Impedance control system for a center tapped termination bus |

| US6864706B1 (en) * | 2000-07-20 | 2005-03-08 | Silicon Graphics, Inc. | GTL+Driver |

| US7222208B1 (en) | 2000-08-23 | 2007-05-22 | Intel Corporation | Simultaneous bidirectional port with synchronization circuit to synchronize the port with another port |

| US6424175B1 (en) * | 2000-09-11 | 2002-07-23 | Intel Corporation | Biased control loop circuit for setting impedance of output driver |

| US6693450B1 (en) * | 2000-09-29 | 2004-02-17 | Intel Corporation | Dynamic swing voltage adjustment |

| KR100391150B1 (ko) * | 2000-11-15 | 2003-07-16 | 삼성전자주식회사 | 다단의 상위 코드 선택기를 갖는 반도체 장치의 임피던스콘트롤 출력회로 및 그의 동작방법 |

| KR100410536B1 (ko) * | 2001-02-05 | 2003-12-18 | 삼성전자주식회사 | 터미네이션 회로의 임피던스 업데이트 장치 및 방법 |

| WO2002065641A1 (de) * | 2001-02-15 | 2002-08-22 | Infineon Technologies Ag | Hochgeschwindigkeitsausgangstreiber |

| US6437610B1 (en) | 2001-02-15 | 2002-08-20 | Infineon Technologies Ag | High-speed output driver |

| US6522185B2 (en) | 2001-02-28 | 2003-02-18 | Agilent Technologies, Inc. | Variable delay CMOS circuit with PVT control |

| US6559690B2 (en) * | 2001-03-15 | 2003-05-06 | Micron Technology, Inc. | Programmable dual drive strength output buffer with a shared boot circuit |

| US20020135406A1 (en) * | 2001-03-20 | 2002-09-26 | Hossain Km Mozammel | Controlled impedance driver receiving a combination binary and thermometer code |

| US6448811B1 (en) | 2001-04-02 | 2002-09-10 | Intel Corporation | Integrated circuit current reference |

| US6522174B2 (en) * | 2001-04-16 | 2003-02-18 | Intel Corporation | Differential cascode current mode driver |

| US6741095B2 (en) | 2001-05-21 | 2004-05-25 | Aucid Corporation, Limited | Data transmission system, circuit and method |

| JP2002359548A (ja) * | 2001-05-31 | 2002-12-13 | Hitachi Ltd | 半導体集積回路 |

| US6791356B2 (en) * | 2001-06-28 | 2004-09-14 | Intel Corporation | Bidirectional port with clock channel used for synchronization |

| US6636821B2 (en) * | 2001-07-03 | 2003-10-21 | International Business Machines Corporation | Output driver impedance calibration circuit |

| US6509757B1 (en) | 2001-08-02 | 2003-01-21 | Agilent Technologies, Inc. | Binary weighted thermometer code for PVT controlled output drivers |

| US6798237B1 (en) | 2001-08-29 | 2004-09-28 | Altera Corporation | On-chip impedance matching circuit |

| US6529037B1 (en) | 2001-09-13 | 2003-03-04 | Intel Corporation | Voltage mode bidirectional port with data channel used for synchronization |

| KR100427037B1 (ko) | 2001-09-24 | 2004-04-14 | 주식회사 하이닉스반도체 | 적응적 출력 드라이버를 갖는 반도체 기억장치 |

| US6836144B1 (en) | 2001-12-10 | 2004-12-28 | Altera Corporation | Programmable series on-chip termination impedance and impedance matching |

| US7109744B1 (en) | 2001-12-11 | 2006-09-19 | Altera Corporation | Programmable termination with DC voltage level control |

| US6812734B1 (en) * | 2001-12-11 | 2004-11-02 | Altera Corporation | Programmable termination with DC voltage level control |

| US6781416B1 (en) * | 2001-12-19 | 2004-08-24 | Rambus Inc. | Push-pull output driver |

| JP3626452B2 (ja) * | 2001-12-27 | 2005-03-09 | 株式会社東芝 | 半導体装置 |

| GB0208014D0 (en) * | 2002-04-05 | 2002-05-15 | Acuid Corp Ltd | Line termination incorporating compensation for device and package parasites |

| KR100481854B1 (ko) * | 2002-07-29 | 2005-04-11 | 삼성전자주식회사 | 온칩 터미네이션기능을 가진 집적회로장치 |

| US7239170B2 (en) * | 2003-07-08 | 2007-07-03 | Lsi Corporation | Apparatus and methods for improved input/output cells |

| US6894529B1 (en) | 2003-07-09 | 2005-05-17 | Integrated Device Technology, Inc. | Impedance-matched output driver circuits having linear characteristics and enhanced coarse and fine tuning control |

| US6888369B1 (en) | 2003-07-17 | 2005-05-03 | Altera Corporation | Programmable on-chip differential termination impedance |

| DE10338077A1 (de) * | 2003-08-19 | 2005-03-17 | Infineon Technologies Ag | Verfahren und Schaltungsanordnung zum schrittweisen Abgleich der Treiberimpedanz in integrierten Halbleiterschaltungschips |

| US6859064B1 (en) | 2003-08-20 | 2005-02-22 | Altera Corporation | Techniques for reducing leakage current in on-chip impedance termination circuits |

| US6888370B1 (en) | 2003-08-20 | 2005-05-03 | Altera Corporation | Dynamically adjustable termination impedance control techniques |

| US6912165B2 (en) * | 2003-08-22 | 2005-06-28 | International Business Machines Corporation | Method for transparent updates of output driver impedance |

| KR100543197B1 (ko) * | 2003-08-25 | 2006-01-20 | 주식회사 하이닉스반도체 | 데이터 출력드라이버 |

| KR100500921B1 (ko) * | 2003-08-25 | 2005-07-14 | 주식회사 하이닉스반도체 | 데이터 출력드라이버의 임피던스를 조정할 수 있는 반도체메모리 장치 |

| TW594187B (en) * | 2003-10-21 | 2004-06-21 | Au Optronics Corp | Mechanism for preventing ESD damages and LCD panel applying the same |

| JP4086757B2 (ja) | 2003-10-23 | 2008-05-14 | Necエレクトロニクス株式会社 | 半導体集積回路の入出力インターフェース回路 |

| US7057415B2 (en) * | 2003-12-10 | 2006-06-06 | Hewlett-Packard Development Company, L.P. | Output buffer compensation control |

| US6967501B1 (en) | 2003-12-18 | 2005-11-22 | Integrated Device Technology, Inc. | Impedance-matched output driver circuits having enhanced predriver control |

| US7248636B2 (en) * | 2004-04-20 | 2007-07-24 | Hewlett-Packard Development Company, L.P. | Systems and methods for adjusting an output driver |

| US7088129B2 (en) | 2004-04-30 | 2006-08-08 | Avago Technologies General Ip (Singapore) Pte. Ltd. | Hybrid binary/thermometer code for controlled-voltage integrated circuit output drivers |

| US7005886B2 (en) | 2004-04-30 | 2006-02-28 | Agilent Technologies, Inc. | Tristateable CMOS driver with controlled slew rate for integrated circuit I/O pads |

| KR100699828B1 (ko) * | 2004-10-11 | 2007-03-27 | 삼성전자주식회사 | 임피던스 교정 회로와 이를 포함하는 집적 회로 및 이를이용한 출력 드라이버의 임피던스 조절 방법 |

| KR100670672B1 (ko) * | 2004-11-02 | 2007-01-17 | 주식회사 하이닉스반도체 | 반도체메모리소자 |

| US7218155B1 (en) | 2005-01-20 | 2007-05-15 | Altera Corporation | Techniques for controlling on-chip termination resistance using voltage range detection |

| US7221193B1 (en) | 2005-01-20 | 2007-05-22 | Altera Corporation | On-chip termination with calibrated driver strength |

| US7327167B2 (en) * | 2005-04-28 | 2008-02-05 | Silicon Graphics, Inc. | Anticipatory programmable interface pre-driver |

| KR100702838B1 (ko) * | 2005-05-09 | 2007-04-03 | 삼성전자주식회사 | 반도체 장치에서의 임피던스 콘트롤러블 출력 구동회로 및그에 따른 임피던스 콘트롤 방법 |

| KR100655083B1 (ko) * | 2005-05-11 | 2006-12-08 | 삼성전자주식회사 | 반도체 장치에서의 임피던스 콘트롤 회로 및 임피던스콘트롤 방법 |

| JP2006352272A (ja) * | 2005-06-13 | 2006-12-28 | Renesas Technology Corp | 半導体集積回路装置 |

| US7679397B1 (en) | 2005-08-05 | 2010-03-16 | Altera Corporation | Techniques for precision biasing output driver for a calibrated on-chip termination circuit |

| CN1980057B (zh) * | 2005-12-01 | 2011-10-26 | 瑞昱半导体股份有限公司 | 输出驱动电路的阻抗匹配装置 |

| TWI323467B (en) * | 2005-12-27 | 2010-04-11 | Hynix Semiconductor Inc | On-die termination circuit for semiconductor memory apparatus |

| US7391229B1 (en) | 2006-02-18 | 2008-06-24 | Altera Corporation | Techniques for serially transmitting on-chip termination control signals |

| US7420386B2 (en) | 2006-04-06 | 2008-09-02 | Altera Corporation | Techniques for providing flexible on-chip termination control on integrated circuits |

| RU2296363C1 (ru) * | 2006-04-27 | 2007-03-27 | Общество с ограниченной ответственностью "АСТРОМА" | Способ и средство защиты программного обеспечения от несанкционированного использования |

| JP4996880B2 (ja) * | 2006-06-08 | 2012-08-08 | 日本オプネクスト株式会社 | 双方向通信システムおよび校正器 |

| US7417452B1 (en) | 2006-08-05 | 2008-08-26 | Altera Corporation | Techniques for providing adjustable on-chip termination impedance |

| US7423450B2 (en) * | 2006-08-22 | 2008-09-09 | Altera Corporation | Techniques for providing calibrated on-chip termination impedance |

| US7656209B2 (en) * | 2006-11-03 | 2010-02-02 | Micron Technology, Inc. | Output slew rate control |

| US7902875B2 (en) | 2006-11-03 | 2011-03-08 | Micron Technology, Inc. | Output slew rate control |

| US7646229B2 (en) * | 2006-11-03 | 2010-01-12 | Micron Technology, Inc. | Method of output slew rate control |

| US7372295B1 (en) | 2006-12-22 | 2008-05-13 | Altera Corporation | Techniques for calibrating on-chip termination impedances |

| US7443193B1 (en) | 2006-12-30 | 2008-10-28 | Altera Corporation | Techniques for providing calibrated parallel on-chip termination impedance |

| TW200910373A (en) * | 2007-06-08 | 2009-03-01 | Mosaid Technologies Inc | Dynamic impedance control for input/output buffers |

| KR100878310B1 (ko) * | 2007-06-11 | 2009-01-14 | 주식회사 하이닉스반도체 | 데이터 출력 드라이버 회로 |

| TW200912591A (en) * | 2007-09-07 | 2009-03-16 | Realtek Semiconductor Corp | Calibration device and method for chip output current |

| US7586325B1 (en) * | 2007-12-03 | 2009-09-08 | Lattice Semiconductor Corporation | Integrated circuit having independent voltage and process/temperature control |

| US20090175378A1 (en) * | 2008-01-08 | 2009-07-09 | Robert Bogdan Staszewski | System and Method for Impedance Mismatch Compensation in Digital Communications Systems |

| US20090184395A1 (en) * | 2008-01-23 | 2009-07-23 | Che-Yuan Jao | Input/output (i/o) buffer |

| JP2009231891A (ja) * | 2008-03-19 | 2009-10-08 | Nec Electronics Corp | 半導体装置 |

| US7443194B1 (en) | 2008-04-24 | 2008-10-28 | International Business Machines Corporation | I/O driver for integrated circuit with output impedance control |

| US20110019760A1 (en) * | 2009-07-21 | 2011-01-27 | Rambus Inc. | Methods and Systems for Reducing Supply and Termination Noise |

| US8471602B2 (en) | 2010-04-30 | 2013-06-25 | SK Hynix Inc. | Output driver and semiconductor apparatus having the same |

| US8766663B2 (en) | 2012-06-18 | 2014-07-01 | International Business Machines Corporation | Implementing linearly weighted thermal coded I/O driver output stage calibration |

| US8957715B2 (en) | 2012-10-17 | 2015-02-17 | Allegro Microsystems, Llc | Output driver having improved electromagnetic compatibility (EMC) and associated methods |

| US9484916B1 (en) | 2015-03-16 | 2016-11-01 | Altera Corporation | Adaptive on-chip termination circuitry |

| KR20160148112A (ko) * | 2015-06-15 | 2016-12-26 | 에스케이하이닉스 주식회사 | 출력 드라이버 및 이를 이용하는 반도체 장치 및 시스템 |

| US9928194B2 (en) | 2015-11-30 | 2018-03-27 | Allegro Microsystems, Llc | Non-linear transmit biasing for a serial bus transmitter |

| US9621140B1 (en) | 2016-01-15 | 2017-04-11 | Allegro Microsystems, Llc | Electronic circuit for driving an output current signal and method of driving the output current signal from the electronic circuit to achieve an altered transition of the output current signal |

| US9793888B2 (en) * | 2016-03-14 | 2017-10-17 | Altera Corporation | Techniques for enabling and disabling transistor legs in an output driver circuit |

| WO2023250313A2 (en) * | 2022-06-22 | 2023-12-28 | Rambus Inc. | A high-speed, low-power, and area-efficient transmitter |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4719369A (en) * | 1985-08-14 | 1988-01-12 | Hitachi, Ltd. | Output circuit having transistor monitor for matching output impedance to load impedance |

| US5134311A (en) * | 1990-06-07 | 1992-07-28 | International Business Machines Corporation | Self-adjusting impedance matching driver |

| US5162672A (en) * | 1990-12-24 | 1992-11-10 | Motorola, Inc. | Data processor having an output terminal with selectable output impedances |

| US5306965A (en) * | 1992-07-01 | 1994-04-26 | Hewlett-Packard Co. | Process compensating variable impedence I/O driver with feedback |

| FR2709217B1 (fr) * | 1993-08-19 | 1995-09-15 | Bull Sa | Procédé et dispositif d'adaptation d'impédance pour un émetteur et/ou récepteur, circuit intégré et système de transmission les mettant en Óoeuvre. |

| US5602494A (en) * | 1995-03-09 | 1997-02-11 | Honeywell Inc. | Bi-directional programmable I/O cell |

| US5581197A (en) * | 1995-05-31 | 1996-12-03 | Hewlett-Packard Co. | Method of programming a desired source resistance for a driver stage |

-

1998

- 1998-11-04 US US09/186,006 patent/US6118310A/en not_active Expired - Lifetime

-

1999

- 1999-09-14 EP EP99118261A patent/EP0999643A1/en not_active Withdrawn

- 1999-11-04 JP JP31364199A patent/JP4430175B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000151384A (ja) | 2000-05-30 |

| US6118310A (en) | 2000-09-12 |

| EP0999643A1 (en) | 2000-05-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4430175B2 (ja) | デジタル制御出力ドライバ及びインピーダンス整合方法 | |

| JP4127743B2 (ja) | ドライバ回路の出力インピーダンス校正回路 | |

| JP3509097B2 (ja) | バスの電流源回路 | |

| US6133749A (en) | Variable impedance output driver circuit using analog biases to match driver output impedance to load input impedance | |

| US6509757B1 (en) | Binary weighted thermometer code for PVT controlled output drivers | |

| US6937055B2 (en) | Programmable I/O buffer | |

| US5214320A (en) | System and method for reducing ground bounce in integrated circuit output buffers | |

| US6593795B2 (en) | Level adjustment circuit and data output circuit thereof | |

| US8120381B2 (en) | Impedance adjusting device | |

| US7863927B2 (en) | Semiconductor device | |

| US7573289B2 (en) | Impedance matching circuit and semiconductor memory device with the same | |

| JP2002325019A (ja) | 出力ドライバおよび高周波補償方法 | |

| US7400272B2 (en) | Hybrid binary/thermometer code for controlled-voltage integrated circuit output drivers | |

| US6483354B1 (en) | PCI-X driver control | |

| US6184703B1 (en) | Method and circuit for reducing output ground and power bounce noise | |

| US10063232B1 (en) | Digitally controlled impedance calibration for a driver using an on-die reference resistor | |

| US6157215A (en) | Method and apparatus for controlling impedance | |

| WO2007070768A2 (en) | Temperature independent, linear on-chip termination resistance | |

| US6509765B1 (en) | Selectable resistor and/or driver for an integrated circuit with a linear resistance | |

| EP1286469A1 (en) | An output driver for integrated circuits and a method for controlling the output impedance of an integrated circuit | |

| US6359465B1 (en) | CMOS small signal switchable adjustable impedence terminator network | |

| US6268750B1 (en) | Flattened resistance response for an electrical output driver | |

| US6373276B1 (en) | CMOS small signal switchable impedence and voltage adjustable terminator with hysteresis receiver network | |

| US6864706B1 (en) | GTL+Driver | |

| JPH10105307A (ja) | ドライバおよびレシーバ回路の構造 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20060629 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061106 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061106 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061201 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20090424 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090428 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090721 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090901 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091113 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20091215 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20091217 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121225 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121225 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131225 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |