JP4242995B2 - 補助ドライバ - Google Patents

補助ドライバ Download PDFInfo

- Publication number

- JP4242995B2 JP4242995B2 JP2000064756A JP2000064756A JP4242995B2 JP 4242995 B2 JP4242995 B2 JP 4242995B2 JP 2000064756 A JP2000064756 A JP 2000064756A JP 2000064756 A JP2000064756 A JP 2000064756A JP 4242995 B2 JP4242995 B2 JP 4242995B2

- Authority

- JP

- Japan

- Prior art keywords

- node

- transistor

- terminal

- net

- signal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/01—Modifications for accelerating switching

- H03K19/017—Modifications for accelerating switching in field-effect transistor circuits

- H03K19/01707—Modifications for accelerating switching in field-effect transistor circuits in asynchronous circuits

- H03K19/01721—Modifications for accelerating switching in field-effect transistor circuits in asynchronous circuits by means of a pull-up or down element

Landscapes

- Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Mathematical Physics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Logic Circuits (AREA)

- Dc Digital Transmission (AREA)

Description

【発明の属する技術分野】

本発明は、広く、データ伝達の分野に関し、特に、集積回路内の信号経路における信号の伝送速度を増加するための装置および方法に関する。

【0002】

【従来の技術】

信号の伝送遅延時間は、ネットワーク内の信号経路の長さが長くなるのに従って増加する。伝送遅延時間は、「負荷の大きな」ネットワーク(すなわち、容量性負荷の大きなネットワークやネット)上を伝送される信号の場合に比較的長くなる。これは、容量性負荷が大きいと、伝送信号のRC遅延時間が長くなるからである。ここで、負荷の大きなネットとは、例えば、SRAMのワード線である。

【0003】

構成の規模が減少するにつれて、集積回路内の金属層における抵抗値は増加する。抵抗値が高くなると、金属層内に形成されたネット上を伝送される信号のRC遅延が大きくなる。

マイクロプロセッサの周期は、マイクロプロセッサで処理された信号の伝送遅延時間が増加すれば、長くなる。しかも、クリティカルなネット上の信号の伝送遅延時間が長くなると、「クリティカルなネット(クリティカルパス:critical path)」におけるタイミング要件が満たされなくなるかも知れない。

【0004】

【発明が解決しようとする課題】

従来の手法によれば、通常、インバータで形成される中継器を長いネットに挿入して、信号の伝送速度を上げるようにしている。中継器は、長いネットを多数の短いネットへ分割し、そこで、各中継器で1つの短いネットを駆動する。多くの場合、所望の信号タイミング(或いは、最適なタイミング)は、インバータを奇数個挿入することで達成される。しかしながら、インバータを奇数個挿入することによって、伝送信号の極性が反転する(電圧が変動する)。伝送信号の元来の極性を取り戻すために、別のインバータをネットに追加してインバータの個数を偶数にする。しかしながら、別のインバータを追加すると、遅延が増大し、その結果、ネットに対する所望の信号タイミングの制約(或いは、最適なタイミング値)が満足されなくなるかも知れない。

【0005】

従来の手法には「近接効果 (neighbor effect)」の問題もある。近接効果は、近接するネット(近接ネット)を伝送する信号が反対側に方向を替える時に生じる。近接効果は、有効切り替え静電容量の増加を引き起し、信号の伝送遅延時間の増加を招く。

従って、集積回路内のネット上での信号の伝送速度を上げることができ、上記の従来の手法における課題を解決することのできる方法および装置が要望される。

【0006】

RC遅延の問題が深刻なのは、例えば、ネットに接続された多数のドライバの中のどれか1つによって駆動されるネットである。中継器は一方向性のものなので、ドライバはネットの全部の部分に信号を送ることができず、そのため、ネットに中継器を使用することができない。この種のネットは、例えば、多機能ユニットのリザルトバス (result bus) である。このような具体例における伝送遅延を改善するための方法および装置が望まれる。これを解決する従来の手法では、双方向性の中継器を使用している。しかしながら、双方向性の中継器は、速度が遅く信号の流れの方向を決定するための制御回路を必要とする。この制御回路は、対面積経費が嵩むだけでなく、その制御回路自体による速度の問題を引き起こすことになる。

【0007】

【課題を解決するための手段】

本発明によれば、ドライバが信号を駆動するネットに含まれるノードに接続され、前記ドライバによる前記信号の駆動を補助する補助ドライバにおいて、電源に接続されたソース端子と、前記ノードに接続されたドレイン端子と、プリチャージクロック信号が入力されるゲート端子を有する第1のトランジスタと、接地されたソース端子と、前記ノードに接続されたドレイン端子と、ゲート端子を有する第2のトランジスタと、電源に接続されたソース端子と、ドレイン端子と、前記プリチャージクロック信号の反転信号が入力されるゲート端子を有する第3のトランジスタと、前記第3のトランジスタのドレイン端子に接続されたソース端子と、前記第2のトランジスタのゲート端子に接続されたドレイン端子と、前記ノードに接続されたゲート端子を有する第4のトランジスタと、接地されたソース端子と、前記第4のトランジスタのドレイン端子に接続されたドレイン端子と、前記プリチャージクロック信号の反転信号が入力されるゲート端子を有する第5のトランジスタと、接地されたソース端子と、前記第2のトランジスタのゲート端子に接続されたドレイン端子と、前記第2のトランジスタのドレイン端子または接地端子に配線により選択的に接続されるゲート端子を有する第6のトランジスタを備えることを特徴とする補助ドライバが提供される。

本発明は、集積回路内に設けられた多数のドライバ中のどれか1つによって駆動されるネット上で高速の信号伝送を達成するための装置を提供する。この装置は、ネットを介して信号を駆動するための第1のドライバを備えている。第1の状態変化アシストドライバ(TAD:transition assist driver) は、信号が第1のノードに接近するにつれて第1のノードの電圧レベルが閾値に到達するのに応えて、ネット内の第1のノードの電圧レベルを変化させる。第1のノードがプリチャージされて論理レベル『1』になっている場合、第1のTADは、第1のノードの電圧レベルを論理レベル『0』へ変化させる。第1のノードがプリチャージされて論理レベル『0』になっている場合、第1のTADは、第1のノードの電圧レベルを論理レベル『1』へ変化させる。第1のTADが、第1のノードの電圧レベルを変化させると、ネットにおける信号の伝送速度が上がる。

【0008】

本発明の他の形態によれば、第2のTADが第2のノードでネットに接続される。第2のTADは、信号が第2のノードに接近するにつれて、第2のノードの電圧レベルを変化させる。第2のノードの電圧レベルを変化させることによって、信号の伝送速度がさらに上がる。さらなるTADを追加してネット上の別のノードに接続することによって、ネットにおける信号の伝送速度をさらに上げられるかも知れない。

【0009】

本発明のさらに他の形態によれば、切り替え速度或いはTADのノイズ不活性 (noise immunity) が上がるように本発明に係るTADをプログラムすることによって、上記の閾値を調整することができる。

従来の手法では、中継器(インバータ)を用いてネットにおける信号の伝送速度を増加させている。しかしながら、中継器を奇数個設けることによって、伝送信号の極性が反転する(電圧が変動する)。本発明によれば、ネットにおける信号の伝送速度を上げるために中継器を使用することを回避できるので好都合である。加えて、本発明に係るTADは、伝送信号の極性を反転しない。

【0010】

本発明の別の形態によれば、近接するネット(近接ネット)をプリチャージし、その電圧を特定の電圧レベルにしておくというプリチャージ法が採用される。このプリチャージ法によれば、従来の手法の「近接効果」の問題を回避することができる。ここで、近接効果は、近接ネットを伝わる信号が反対方向に切り替わるときに生じる。近接効果の問題は、有効切り替え静電容量の増加を引き起し、信号の伝送遅延時間の増加を招く。本発明のプリチャージ法によれば、近接ネット上の信号が反対方向に切り替わることはない。1つのネット上の信号がある方向に切り替わるとき、近接ネット上の他の信号は、同一方向に切り替わるか、或いは、現在の極性を維持する。

【0011】

第2のドライバをネットに接続して、第1のドライバによって駆動される信号の方向と反対の方向に伝送するように信号を駆動するようにしてもよい。この場合、本発明に係る信号伝送システムにおいて双方向信号伝送が達成される。他のドライバをネット上の別の地点に追加すれば、ネットにおける双方向信号伝送が可能になる。

【0012】

本発明に係るTADは、ネットにおける信号の伝送方向に関わらずネット上の対応するノードの電圧レベルを変化させる。TADは、ネット上を伝送する信号によって生じる対応するノードの電圧レベルの変化を自動的に検出し、その対応するノードの電圧レベルを変化させて信号の伝送速度を上げる。

【0013】

【発明の実施の形態】

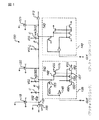

図1は本発明の第1実施例に係る信号伝送システム100を示す。図1に示されるように、信号伝送システム100は、信号102の伝送速度を上げることができ、集積回路(図示しない)に適用可能である。例えば、信号伝送システム100は、マイクロプロセッサ(図示しない)内で信号を送信するのに使用される。ドライバ105は、ネット(信号経路)110を介して信号102を駆動する。レシーバ112は信号102を受信する。信号伝送システム100に一方向の信号伝送機能を発揮させる場合、ドライバ115、120および125は不活性化されるか省略される。

【0014】

ネット110上に配置された抵抗およびコンデンサをRおよびCで表す。コンデンサCは、ネット110の容量性特性および/または容量性負荷を表す。抵抗Rは、ネット110の抵抗性特性を表すもので、ネット110の長さが増加するについれて、および/または、ネット110の幅が減少するにつれて、抵抗値が増大する。

【0015】

信号伝送システム100は、さらに、ノード142(または、B2)と144(または、B3)でネット110に接続された状態変化アシストドライバ(TAD)135および140を備えている。或る実施例においては、TAD135はインバータ145を備えている。インバータ145は、プリチャージクロック信号CLKを受信するための入力端子と、Pチャネル型トランジスタ150のゲートに接続された出力端子とを備えている。Pチャネル型トランジスタ150は、ソースがVDDなどの正電圧電源に接続され、ドレインがPチャネル型トランジスタ155のソースに接続される。Pチャネル型トランジスタ155は、ドレインがノード157に接続され、ゲートがノード142を介してネット110に接続される。Nチャネル型トランジスタ160は、ドレインがノード157に接続され、ソースが接地(VSS)されゲートがインバータ145の出力端子に接続される。

【0016】

TAD135は、さらにPチャネル型トランジスタ165を備えている。Pチャネル型トランジスタ165は、プリチャージクロック信号CLKを受信するためのゲートと、VDDに接続されたソースと、ノード142を介してネット110に接続されたドレインとを備えている。Nチャネル型トランジスタ170は、ドレインがノード142を介してネット110に接続され、ソースがVSSに接続され、そして、ゲートがノード157に接続される。

【0017】

本発明によれば、ネット110に接続されるTADの個数は様々に異なる。図示していない代わりの実施例によれば、TADは1つだけネット110に接続される。或いは、別のTADとドライバおよび/またはレシーバとが、後述するように、信号伝送システム100内のネット110に追加される。

TAD135および/またはTAD140を使用することによって、ネット110上で生じる電圧変動の進捗速度 (rate) が上がり、信号102の伝送速度が上がる。TAD135および/またはTAD140によって、TAD135と140とに対応するノードにおける電圧がレベル変化し、信号102に起因する電圧変動の進捗速度が上がる。TAD135と140は、信号の伝送速度の低下を効果的に補償する。信号速度の低下は、ライン線抵抗および配置された静電容量に起因する。別のTADをネット110に追加することによって、ネット110における信号の伝送速度がさらに上がる。このようにして、長いネット或いは容量性負荷の大きいネットにおける信号の伝送遅延を低減できる。

【0018】

図1および図2を参照して、信号伝送システム100の作用について考察する。具体的に、図2は、ネット110上のノード142における電圧変動を時間に関連づけて表す第1の波形200を示す。波形205は、TAD135によるアシストがない時のノード142における電圧変動を表す。システムの電力投入中および/またはシステムリセット中、ネット110は、図2の時刻ta0にプリチャージされ論理レベル『1』の電圧値を帯びる。論理レベル『1』の値は、例えば、およそ1.8ボルトである。プリチャージクロック信号CLKは、ネット110がプリチャージされて論理レベル『1』になっているとき、論理レベル『0』を示す。プリチャージクロック信号CLKは、ネット110のプリチャージ中低レベルなので、Pチャネル型トランジスタ165はオンである。Pチャネル型トランジスタ165は、ノード142の電圧をVDD電圧レベルへと変化させる。これによって、ネット110は、プリチャージされてVDD(論理レベル『1』)になる。

【0019】

ネット110がプリチャージされて高レベルになっているので、ノード142は評価 (evaluation) の前には高レベルである。従って、Pチャネル型トランジスタ155は、ゲートを介してノード142から論理レベル『1』値を受信しているので、評価前にはオフである。

ネット110のプリチャージ中、インバータ145は、クロック信号CLKの論理レベル『0』値を論理レベル『1』へと反転させる。インバータ145の高レベル出力信号は、Pチャネル型トランジスタ150とNチャネル型トランジスタ160とのゲートへ印加される。このように、ネット110のプリチャージ中であって評価期間 (evaluation period)の前には、Pチャネル型トランジスタ150はオフでNチャネル型トランジスタ160はオンである。従って、ネット110のプリチャージ中、ノード157は、電圧がNチャネル型トランジスタ160によってVSSへと変化させられる。

【0020】

次に、ユーザは、従来の外部の制御回路(図示しない)を使用して評価期間を開始する。制御回路は、プリチャージクロック信号CLKを論理レベル『0』から論理レベル『1』へと切り替える。プリチャージクロック信号CLKが論理レベル『1』へ切り替わると、Pチャネル型トランジスタ165がオフになる。プリチャージクロック信号CLKの論理レベル『1』の値は、インバータ145によって論理レベル『0』の値へと反転させられる。このように、インバータ145の低レベル出力信号で、Pチャネル型トランジスタ150はオンになり、Nチャネル型トランジスタ160はオフになる。この時、ノード157はVSS電圧レベルを維持する。

【0021】

本発明の代わりの実施例によれば、プリチャージクロック信号CLKは、チップ内(内部)クロック源(図示しない)によって生成されるかも知れない。チップ内クロック源は、プリチャージクロック信号CLKを生成する。プリチャージクロック信号は、インバータ145の入力端子およびPチャネル型トランジスタ165(図1)のゲートに印加される。そして、プリチャージクロック信号CLKの状態変化で評価期間の発生が決定する。

【0022】

時刻ta0(図2参照)の後、ドライバ105は、論理レベル『0』の電圧変動を生じさせる信号102を発生する。ネット110のRC特性によって、ネット110における(論理レベル『1』から論理レベル『0』への)電圧変動の量は、時間と距離との関数になる。電圧変動の量は、ドライバ105に近接した位置(ネット110上)の方が大きい。

【0023】

ネット110を伝送する信号102によって、時刻ta1に、ノード142の電圧はプリチャージVDD値から閾値VDD−Vthreshold(transistor 155) へと低下する。VDD値は、例えば、およそ1.8ボルトに等しい。Vthreshold(transistor 155) の電圧は、トランジスタ155の閾値電圧として定義される。Vthreshold(transistor 155) の値は、典型的には、およそ0.25ボルトに等しい。Pチャネル型トランジスタ155のゲートには、ノード142の電圧が印加される。Pチャネル型トランジスタ155のゲート電圧がおよそVDD−Vthreshold(transistor 155) へ低下すると、トランジスタ155はオンになる。Pチャネル型トランジスタ150および155は、両方ともオンになり、ノード157の電圧レベルをVSSからVDD(論理レベル『1』)へ変化させる。なお、Nチャネル型トランジスタはオフのままである。

【0024】

ノード157の電圧がVDDに変化するので、Nチャネル型トランジスタ170は時刻ta2(図2)にオンになる。Nチャネル型トランジスタ170は、時刻ta3にノード142の電圧をVSS(論理レベル『0』)へ変化させる。これで、ノード142における論理レベル『1』から論理レベル『0』への電圧変動は完了する。

【0025】

図2に示すように、TAD135により、ノード142の電圧レベルは、時刻ta3にΔV1の電圧値だけさらに低下する。TAD135のアシストがない時、ノード142の電圧変動は、波形205で示すようにゆっくりと進む。長く負荷の大きいネットの場合、TAD135のアシストがないと、ノード142の電圧変動の進捗速度はさらに低下する。

【0026】

信号102がネット110を伝わるとき、他のTAD(例えばTAD140)は、ネット110上の他のノードの電圧が論理レベル『0』へ変化し易くする。これによって、信号102のネット110における伝送速度はさらに上がる。

従来の手法では、中継器(インバータ)を使用してネットにおける信号の伝送速度を上げていた。しかし、中継器を奇数個設けることによって、伝送信号の極性(電圧変動)が反転する。本発明によれば、優位にも、ネットにおける信号の伝送速度を上げるために中継器を使用することを回避できる。加えて、本発明に係るTADは、伝送信号の極性を反転させない。

【0027】

本発明のプリチャージ法によれば、近接ネットは、評価期間の前に、特定の電圧レベル(例えば論理レベル『1』)までプリチャージされる。このプリチャージ法によって、従来の方法の「近接効果」問題を回避できる。ちなみに、近接効果は、近接ネットを伝わる信号が逆方向へ切り替えられたときに生じる。近接効果の問題は、有効切り替え静電容量の増加を引き起し、信号の伝送遅延時間の増加を招く。本発明のプリチャージ法では、近接ネットを伝わる信号は、逆方向へ切り替わらない。1つのネット上の信号が1つの方向に切り替わると、近接ネット上の他の信号は、同一方向に切り替わるか、或いは、現在の極性を維持する。

【0028】

図3、図4および図5は、本発明の機能性について示すものである。図3は、本発明の第2実施例に係る信号伝送システム300の概略ブロック図である。システム300は、信号305を受信するためのレシーバ112、325および330を備えている。TAD135、140、345および350は、ノードB2、B3、B4およびB5でネット110に接続される。TAD135、140、345および350は、それぞれ対応するノードの電圧レベルが閾値(例えば、VDD−Vthreshold 、ここで、Vthreshold は、例えば、およそ0.25ボルトに等しい)に達すると、そのノードの電圧レベルを変化させる。図4は、ネット410で信号405を送信する従来の信号伝送システム400を示す。ドライバ415は、レシーバ420、425および430によって受信される信号405を駆動する。信号405は、ネット410上のノードB1T〜B5Tを介して伝わり、その後レシーバ420によって受信される。

【0029】

図5は、ネット110上のノードB1〜B5における電圧レベルとネット410上のノードB1T〜B5Tにおける電圧レベルとを特定の時間に関連づけて比較するためのグラフを示す。TAD135、140、345および350は、ノードB2、B3、B4およびB5の電圧が論理レベル『1』から論理レベル『0』へと変化し易くする。これによって、論理レベル『1』から論理レベル『0』への電圧変動は、ノードB2T〜B5TでのものよりもノードB2〜B5での方が速くなる。例えば、ノードB5の電圧レベルは、評価期間(図5参照)の開始からおよそ1.2ナノ秒後に論理レベル『0』(0.0ボルト)まで低下する。一方、ノードB5Tの電圧レベルは、評価期間の開始からおよそ2.2ナノ秒後に最低電圧レベルの200ミリボルトまで低下する。評価期間 (evaluation period)は、図5に示すように、プリチャージクロック信号が論理レベル『1』へと立ち上がると同時に開始する。ノードB2〜B5における電圧変動の方が進捗速度が高いのは、TAD135、140、345および350によってアシストされるからである。ノードB2〜B5における電圧変動の方が進捗速度が高いことによって、ネット110における信号305の伝送速度が上がる。

【0030】

図6は、本発明の第3実施例に係る信号伝送システム500の概略ブロック図である。信号伝送システム500は、高い切り替え速度と優れたノイズ不活性との一方を犠牲にして他方を実現することできるプログラマブルTAD (programmable TAD) 505を備えている。プログラマブルTAD505は、ノード142でネット110に接続される。TAD505のプログラマブル機能 (programmable features)は、TADの回路構成にNチャネル型トランジスタ510を加えるか否かによって異なる。具体的には、Nチャネル型トランジスタ510は、ドレインがノード157に接続され、ソースがVSSに接続される。Nチャネル型トランジスタ510のゲートは、二頭の矢印515で示すように、ノード142に接続されるか、或いは、VSSに接続される。TAD505を備えた集積回路チップ(図示しない)の最終金属層(final metal layer:図示しない)を改造することによって、Nチャネル型トランジスタ510のゲートをノード152かVSSかに接続させる。

[例1:Nチャネル型トランジスタ510のゲートをVSSに接続した場合]

Nチャネル型トランジスタ510のゲートがVSSに接続されると、Nチャネル型トランジスタ510は、TAD505の回路構成から切り離される。従って、TAD505は、図1のTAD135と同様に機能し、ノード142の電圧を論理レベル『1』から論理レベル『0』へと変化させるための高速切り替えを行うことができるようになる。ここで、VDDがおよそ1.8ボルトに等しく、Pチャネル型トランジスタ155の閾値電圧(Vthreshold(transistor 155) )がおよそ0.25ボルトであるとすると、Pチャネル型トランジスタ155のゲート(或いは、ノード142)の電圧レベルは、VDD−Vthreshold(transistor 155) =1.8ボルト−0.25ボルト=1.55ボルトまで低下する。そして、Pチャネル型トランジスタ155はオンになる。Pチャネル型トランジスタ150および155がオンになり、Nチャネル型トランジスタ160はオフのままなので、ノード157の電圧は、VSSレベルからVDDレベルへと変化する。Nチャネル型トランジスタ170は、ノード157からVDD電圧レベルを受け取るのでオンになる。Nチャネル型トランジスタ170がオンになるので、ノード142はVSS(論理レベル『0』)へ変化する。このように、Nチャネル型トランジスタ510のゲートがVSSに接続されると、TAD505は、切り替えを開始し、ノード142の電圧レベルが閾値、例えば、1.55ボルトまで低下するのに応え、そのノード142を論理レベル『0』へ変化させる。

[例2:Nチャネル型トランジスタ510のゲートをノード142に接続した場合]

Nチャネル型トランジスタ510のゲートがノード142に接続されると、トランジスタ155および510は、インバータ525を構成する。インバータ525は、入力端子がノード142に接続され、出力端子がノード157に接続される。インバータ525の切り替え電圧VSWは、典型的に、およそ(2/3)VDD=1.2ボルトに維持される。従って、ノード142の電圧がおよそ(2/3)VDD=1.2ボルトにまで低下すると、インバータ525は、ノード157を論理レベル『1』の電圧レベルへと切り替える。ノード157が高レベルに切り替えられるので、トランジスタ170はオンになる。従って、ノード142はVSSへ変化し、ノード142での論理レベル『1』から論理レベル『0』への電圧変動は完了する。

【0031】

トランジスタ510のゲートをノード142に接続することによって、TAD505によりノード142を論理レベル『0』へと変化させ易くなる前は、ノード142では比較的低い電圧レベルのおよそ0.9ボルトが必要とされる。従って、TAD505は、ノイズに対して優れた不活性を示す。TAD505は、高ノイズ度或いは高干渉度を示す環境において特に有用である。ノイズに対する優れた不活性を得るために犠牲にされた結果として、TAD505の切り替え速度は比較的遅い。TAD505によってノード142の電圧を低下させ易くなる前は、ノード142の電圧を比較的低い電圧レベルへ低下させる必要があるからである。

【0032】

図7は、本発明の第4実施例に係る信号伝送システム600の一部を示す図である。信号伝送システム600は、ノード142でネット110に接続されたプログラマブルTAD605を備えている。TAD605のプログラマブル性は、TAD回路構成にNチャネル型トランジスタ(Nチャネル型トランジスタ610など)を追加して、TAD605のノイズに対する不活性をさらに向上させることによって達成される。Nチャネル型トランジスタ610は、ゲートがノード142に接続され、ドレインがノード157に接続され、そして、ソースがVSSに接続される。Pチャネル型トランジスタ155と並列Nチャネル型トランジスタ対510および610とでインバータ620が構成される。インバータ620は、入力端子がノード142に接続され出力端子がノード157に接続される。並列Nチャネル型トランジスタ対510および610は、インバータ620内の大規模トランジスタ (large size transistor)を効果的に構成する。これによって、インバータ620の切り替え電圧VSWは、(2/3)VDD未満まで低下する。このように、インバータ620がノード157を論理レベル『1』へ切り替えてトランジスタ170をオンにする前は、ノード142の電圧を(2/3)VDD未満まで低下させなければならない。Nチャネル型トランジスタ170がオンになると、ノード142はVSS(論理レベル『0』)へ変化する。

【0033】

Nチャネル型トランジスタ610と同様に、さらなるNチャネル型トランジスタをTAD605の回路構成に追加してもよい。このように、Nチャネル型トランジスタをさらに追加することで、インバータ620の切り替え電圧VSWの値が、典型的には、およそ(2/3)VDDからおよそ(1/2)VDDまでの範囲でさらに低下するので、TAD605のノイズ不活性がさらに向上する。

【0034】

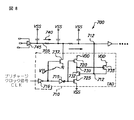

図8は、本発明の第5実施例に係る信号伝送システム700であって、システムの電力投入中および/またはシステムリセット中にネット705を論理レベル『0』までプリチャージするという信号伝送システムの概略ブロック図である。TAD710は、ノード712を介してネット705に接続され、インバータ715で構成される。インバータ715は、出力端子がPチャネル型トランジスタ720およびNチャネル型トランジスタ725のゲートに接続される。インバータ715の入力端子は、インバータ716の出力端子に接続される。インバータ716は、入力端子を介してプリチャージクロック信号CLKを受け取る。

【0035】

Pチャネル型トランジスタ720は、ソースがVDDに接続され、ドレインがノード730に接続される。Nチャネル型トランジスタ732は、ドレインがノード730に接続され、ソースがNチャネル型トランジスタ725のドレインに接続され、そして、ゲートがノード712に接続される。Nチャネル型トランジスタ725は、ソースがVSSに接続される。

【0036】

Pチャネル型トランジスタ735は、ソースがVDDに接続され、ドレインがノード712に接続され、そして、ゲートがノード730に接続される。Nチャネル型トランジスタ737は、ドレインがネット705に接続され、ソースがVSSに接続され、そして、ゲートがインバータ716の出力端子に接続される。

図8および図9を参照して、TAD710の作用について考察する。図9では、波形750は、TAD710のアシストがある場合のノード712における電圧変動を時間に関連づけて示す。波形755は、TAD710のアシストがない場合のノード712における電圧変動を時間に関連づけて示す。時刻tb0において、ネット705およびノード712は、論理レベル『0』までプリチャージされる。ネット705が、論理レベル『0』までプリチャージされているとき、プリチャージクロック信号CLKは論理レベル『0』の値を示す。低レベルクロック信号CLKは、インバータ716によって論理レベル『1』の信号へと反転させられる。インバータ716からの論理レベル『1』の出力信号で、Nチャネル型トランジスタ737はオンになる。Nチャネル型トランジスタ737は、プリチャージ中で評価期間の前にネット705の電圧レベルをVSS(論理レベル『0』)へ変化させる。

【0037】

ネット705のプリチャージ中、インバータ715は、インバータ716の高レベル出力信号を論理レベル『0』の信号へと反転させる。インバータ715の低レベル出力信号は、Pチャネル型トランジスタ720およびNチャネル型トランジスタ725のゲートへ印加される。Pチャネル型トランジスタ720およびNチャネル型トランジスタ725はオフになる。Nチャネル型トランジスタ732は、ゲートが、プリチャージされて低レベルになっているノード712に接続されているので、Nチャネル型トランジスタ732もオフである。Pチャネル型トランジスタ720はオンなので、ネット705のプリチャージ中であって評価の前にノード730をVDDレベルへ変化させる。

【0038】

ユーザは、次に、従来の外部の制御回路(図示しない)を使用して評価期間を開始させる。制御回路は、プリチャージクロック信号CLKを論理レベル『0』から論理レベル『1』へと切り替える。評価期間の開始中にプリチャージクロック信号CLKが論理レベル『1』に切り替わると、インバータ716の出力は論理レベル『0』の信号になる。インバータ716の低レベル出力信号でNチャネル型トランジスタ737はオフになる。また、インバータ716の低レベル出力信号は、インバータ715によって論理レベル『1』の信号へと反転させられる。インバータ715の高レベル出力信号でPチャネル型トランジスタ720はオフになり、Nチャネル型トランジスタ725はオンになる。このとき、ノード730はVDDレベルを維持する。

【0039】

時刻tb0後、三状態ドライバ (tri-state driver) 745は、論理レベル『1』への電圧変動を伴う信号740を発生させる。時刻tb1で、ノード712の電圧レベルは、Nチャネル型トランジスタ732の閾値電圧(すなわち、Vthreshold(transistor 732) )まで上昇する。これによって、Nチャネル型トランジスタ732がオンになる。Vthreshold(transistor 732) の値は、典型的に、およそ0.25ボルトである。トランジスタ725と732とはオンでトランジスタ720はオフなので、トランジスタ725および732は、ノード730をVDD電圧レベルからVSS接地電圧レベルへと変化させる。ノード730が低レベルになったので、Pチャネル型トランジスタ735は、ゲートを介してノード730のVSS接地電圧値を受け取り、時刻tb2でオンになる。時刻tb3において、Pチャネル型トランジスタ735は、ノード712をVDD(論理レベル『1』)へと変化させる。これで、ノード712における論理レベル『0』から論理レベル『1』への電圧変動が完了する。

【0040】

図9に示すように、TAD710は、ノード712における電圧変動の進捗速度を上げる。例えば、時刻tb3で、波形750は、波形755より電圧値がΔV2だけ高い。

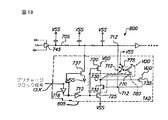

図10は、本発明の第6実施例に係る信号伝送システム800であって、システムの電力投入中および/またはシステムリセット中にネット705を論理レベル『0』までプリチャージするという信号伝送システムの概略ブロック図である。信号伝送システム800は、プログラマブルTAD805を備えている。プログラマブルTAD805は、ノード712を介してネット705に接続される。TAD805は、Pチャネル型トランジスタ770を備えている。Pチャネル型トランジスタ770は、ソースがVDDに接続され、ドレインがノード730に接続される。また、Pチャネル型トランジスタ770のゲートは、二頭の矢印775で示すように、ノード712かVSSかのどちらかに接続可能である。

【0041】

Pチャネル型トランジスタ770のゲートがVSSに接続された場合、トランジスタ770は、TAD805の回路構成から省かれる。TAD805は、図8のTAD710と同様に作用する。特に、前述したように、TAD805により、ノード712の電圧レベルがトランジスタ732の閾値電圧Vthreshold(transistor 732) まで上昇するのに応えてノード712をVDDへと変化させ易くなる。なお、Vthreshold(transistor 732) は、典型的に、およそ0.25ボルトである。

【0042】

Pチャネル型トランジスタ770のゲートがノード712に接続されると、トランジスタ770および732によりインバータ780が構成される。インバータ780は、入力端子がノード712に接続され、出力端子がノード730に接続され、そして、Pチャネル型トランジスタ735のゲートを駆動する。VDDがおよそ1.8ボルトに等しいとすると、ノード712の電圧がVSW=VDD/3=1.8/3=0.6ボルトまで上昇したとき、インバータ780は、ノード730の電圧レベルを論理レベル『1』から論理レベル『0』へと切り替える。しかしながら、Pチャネル型トランジスタ(図示しない)を追加してPチャネル型トランジスタ770に並列に接続することによって、インバータ780の切り替え電圧VSWを別の値(典型的には、(1/3)VDDから(1/2)VDDの範囲)へと調節してもよい。

【0043】

ノード730における論理レベル『0』の電圧でPチャネル型トランジスタ735はオンになる。Pチャネル型トランジスタ735は、ノード712をVDD(論理レベル『1』)へ変化させる。ノード712における論理レベル『0』から論理レベル『1』への電圧変動は、これで完了する。

TAD805は、ノード712の電圧を例えばVDD/3へと上昇するまでノード712を論理レベル『1』まで変化させ易くなるようにアシストしないので、ノイズに対して優れた不活性を示す。優れたノイズ不活性のために犠牲にされた結果、TAD805の切り替え速度は低い。

【0044】

図示しない別の実施例では、Pチャネル型トランジスタ770と同様に、別のPチャネル型トランジスタ(図示しない)をTAD805の回路構成に加える。このように、Pチャネル型トランジスタを加えることによって、インバータ780の切り替え電圧VSWが上昇し、TADのノイズ不活性が一層優れたものとなる。

【0045】

図11は、本発明の第7実施例に係る信号伝送システム900であって、双方向性の信号伝送機能を備えたシステム900の概略ブロック図である。例えば、ドライバ905は、信号を915方向へネット910を介して駆動し、ドライバ920は、信号を925方向へネット910を介して駆動する。別のドライバ(ドライバ930と935など)を追加してネット910に接続し、ネット910を介して信号を駆動させるようにしてもよい。

【0046】

TAD940および/または945は、ネット910に接続されネット910おける信号の伝送速度を上昇させ易くする。具体的に、TAD940および945は、ノード947と949でネット910に接続される。ネット910に接続されるTADの個数は様々に異なる。ノードの電圧レベルが、ネット910を伝わる信号によって上昇して閾値に達すると、TAD940および945は、それぞれ対応するノードにおける電圧レベルを変化させる。システムの電力投入中および/またはシステムリセット中にネット910がロウ論理レベルまでプリチャージされた場合、TAD940および945は、対応するノードにおける電圧レベルを論理レベル『1』へと変化させる。TAD940と945は、それぞれ前述した様々なTADの実施例に適用される。

【0047】

TAD940および945は、それぞれ915方向に伝送する信号の伝送速度を上昇させるか、或いは、反対方向925に伝送する別の信号の伝送速度を上昇させる。このため、TADのアシストを受けて高速で信号を送信するために、ネット910上の様々な位置にドライバを設置することができる。

図12は、双方向性の信号伝送機能を備えた従来のシステム950を示す。従来のシステム950は、ドライバ955、960および965を備えている。ドライバ955、960および965は、様々に異なるノードでネット970に接続される。ドライバ955は、975方向へネット970を介して信号を送信できるものとする。従来のシステム950では、ドライバ955が信号を送信する場合、中継器980および985をオフにすることが必要である。中継器980および985をオフにすることによって、975方向の信号は中継器990と995を渡って伝送する。また、ドライバ965が、997方向にネット970を介して信号を送信する場合、中継器990および995をオフにしなければならない。こうすれば、997方向の信号は、中継器980および985を渡って伝送できる。このように、従来の方法によれば、ネットを伝送する信号の方向に基づいてネット上の中継器を調節することが必要である。一方、本発明によれば、信号方向の相違に従って信号伝送システムを調節する必要もなく、信号の915方向或いは925方向(図11)への伝送速度を自動的に上昇させることができる。

【0048】

本発明の様々な実施例によれば、集積回路内に形成されるネットにおける信号の伝送速度を上昇させられる。例えば、先に考察したTADの様々な実施例は、レジスタファイル内のワード線或いは追加命令バッファ (re-order buffer)内のワード線に接続される。ワード線とは、比較的短い導体であって、単一のドライバによって駆動され、信号の伝送遅延時間を増加させる大きな容量性負荷を伴う。

【0049】

先に考察したTADの様々な実施例は、マイクロプロセッサのリザルトバス (result bus) に接続される。リザルトバスは、多数のドライバによって駆動され、その結果、双方向の信号伝送機能を発揮する。

先に考察したTADの様々な実施例は、追加命令バッファ内のビット線に接続することもできる。ビット線は、多数のドライバによって駆動され、その結果、双方向の信号伝送機能を発揮する。ビット線は、比較的短い導体であって、信号の伝送遅延時間を増加させる大きな容量性負荷を伴う。

【0050】

付記 本発明は以下の特徴を有する。

(付記1) 集積回路内に存在する第1のノードを含むネットを介して信号を送信するための装置であって、

前記ネットに接続され、該ネットを介して前記信号を駆動するドライバと、

前記ネットにおける前記第1のノードに接続され、該第1のノードの電圧レベルが閾値に到達するのに応えて当該第1のノードの電圧レベルを変化させる第1の状態変化アシストドライバ(TAD)と、を備えることを特徴とする装置。(請求項1)

【0051】

(付記2) 付記1に記載の装置において、前記ネットが論理レベル『1』にプリチャージされているとき、前記第1のTADは、前記第1のノードを論理レベル『0』へ変化させることを特徴とする装置。

(付記3) 付記1に記載の装置において、前記ネットが論理レベル『0』にプリチャージされているとき、前記第1のTADは、前記第1のノードを論理レベル『1』へ変化させることを特徴とする装置。

【0052】

(付記4) 付記1に記載の装置において、前記第1のTADは、前記第1のノードを論理レベル『0』へ変化させ、そして、該第1のTADは、

前記第1のノードに接続された第1の端子、接地された第2の端子、および、ゲート端子を有する第1のトランジスタと、

第1の電源電圧源に接続された第1の端子、第2の端子、および、プリチャージクロック信号の反転信号を受け取るゲート端子を有する第2のトランジスタと、

該第2のトランジスタの第2の端子に接続された第1の端子、前記第1のトランジスタのゲート端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第3のトランジスタと、

該第3のトランジスタの第2の端子に接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号の反転信号を受け取るゲート端子を有する第4のトランジスタと、を備えることを特徴とする装置。(請求項2)

【0053】

(付記5) 付記4に記載の装置において、前記第1のTADは、さらに、

前記第1のトランジスタのゲート端子に接続された第1の端子、接地された第2の端子、および、前記第1のノードに接続されるか或いは接地されたゲート端子を有する第5のトランジスタを備えることを特徴とする装置。

(付記6) 付記4に記載の装置において、前記第1のTADは、さらに、

前記第1のトランジスタのゲート端子に接続された第1の端子、接地された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第6のトランジスタを備えることを特徴とする装置。

【0054】

(付記7) 付記4に記載の装置において、前記第1のTADは、さらに、

前記ネットを論理レベル『1』にプリチャージするプリチャージトランジスタを備え、該プリチャージトランジスタは、前記第1の電源電圧源に接続された第1の端子、前記ネットに接続された第2の端子、前記プリチャージクロック信号を受け取るゲート端子を有することを特徴とする装置。

【0055】

(付記8) 付記1に記載の装置において、前記第1のTADは、前記第1のノードを論理レベル『1』へ変化させ、そして、該第1のTADは、

第1の電源電圧源に接続された第1の端子、第2の端子、および、プリチャージクロック信号を受け取るゲート端子を有する第1のプルアップトランジスタと、

該第1のプルアップトランジスタの第2の端子に接続された第1の端子、第2の端子、および、前記第1のノードに接続されたゲート端子を有する第1のプルダウントランジスタと、

該第1のプルダウントランジスタの第2の端子に接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号を受け取るゲート端子を有する第2のプルダウントランジスタと、

前記第1の電源電圧源に接続された第1の端子、前記第1のノードに接続された第2の端子、および、前記第1のプルアップトランジスタの第2の端子に接続されたゲート端子を有する第2のプルアップトランジスタと、を備えることを特徴とする装置。(請求項3)

【0056】

(付記9) 付記8に記載の装置において、前記第1のTADは、さらに、

前記第1の電源電圧源に接続された第1の端子、前記第1のプルアップトランジスタの第2の端子に接続された第2の端子、および、前記第1のノードに接続されるか或いは接地されたゲート端子を有する第3のプルアップトランジスタを備えることを特徴とする装置。

(付記10) 付記8に記載の装置において、前記第1のTADは、さらに、

前記電源電圧源に接続された第1の端子、前記第1のプルアップトランジスタの第2の端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第4のプルアップトランジスタを備えることを特徴とする装置。

【0057】

(付記11) 付記8に記載の装置において、前記第1のTADは、さらに、

前記ネットを論理レベル『0』にプリチャージするプリチャージトランジスタを備え、該プリチャージトランジスタは、前記ネットに接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号の反転信号を受け取るゲート端子を有することを特徴とする装置。

(付記12) 付記1に記載の装置において、該装置は、さらに、

さらなる信号を送信して前記ネットにおける双方向信号伝達を可能にする第2のドライバを備えることを特徴とする装置。

(付記13) 付記1に記載の装置において、該装置は、さらに、

第2のノードで前記ネットに接続され、該第2のノードの電圧レベルが閾値に到達するのに応えて当該第2のノードの電圧レベルを変化させる第2のTADを備えることを特徴とする装置。

【0058】

(付記14) 集積回路内において高速の信号伝送を行う装置であって、

第1のノードを有し、前記集積回路内で信号を送信するネットと、

前記第1のノードに接続され、該第1のノードの電圧レベルが閾値に到達するのに応えて当該第1のノードの電圧レベルを変化させる第1の状態変化アシストドライバ(TAD)と、を備えることを特徴とする装置。(請求項4)

(付記15) 付記14に記載の装置において、前記ネットが論理レベル『1』にプリチャージされているとき、前記第1のTADは、前記第1のノードを論理レベル『0』へ変化させることを特徴とする装置。

(付記16) 付記14に記載の装置において、前記ネットが論理レベル『0』にプリチャージされているとき、前記第1のTADは、前記第1のノードを論理レベル『1』へ変化させることを特徴とする装置。

【0059】

(付記17) 第1のノードを含むネットを有する信号伝送システムを使用して集積回路内において高速の信号伝送を行う方法であって、

(a)前記第1のノードの電圧レベルを検知するステップと、

(b)前記第1のノードの電圧が閾値に到達するのに応えて、該第1のノードの電圧レベルを変化させるステップと、を備えることを特徴とする方法。(請求項5)

(付記18) 集積回路内における第1のノードを含むネットを介して高速伝送を達成するための方法であって、

(a)前記ネットにおける第1のノードを介して信号を駆動するステップと、(b)前記信号が前記第1のノードに接近するのにつれて該第1のノードの電圧レベルが閾値に到達するとき、当該第1のノードの電圧レベルを変化させるステップと、を備えることを特徴とする方法。(請求項6)

【0060】

(付記19) 第1のノードを含むネットの電圧レベルを変化させるドライバであって、

前記第1のノードに接続された入力端子、第1の電圧源に接続された第1の端子、第2の電圧源に接続された第2の端子、および、出力端子を有し、前記第1のノードの電圧レベルが閾値になるのに応えてオンになるように構成された第1の変化回路と、

該第1の変化回路の出力端子に接続された入力端子、前記第1のノードに接続された第1の端子、および、前記第2の電圧源に接続された第2の端子を有し、前記第1の変化回路がオンになるのに応えて前記第1のノードを前記第2の電圧源の電位へ変化させる第2の変化回路と、を備えることを特徴とするドライバ。

【0061】

(付記20) 第1のノードを含むネットの電圧レベルを変化させるドライバであって、

前記第1のノードに接続された入力端子、第1の電圧源に接続された第1の端子、第2の電圧源に接続された第2の端子、および、出力端子を有し、前記第1のノードの電圧レベルが閾値になるのに応えてオンになるように構成された第1の変化回路と、

該第1の変化回路の出力端子に接続された入力端子、前記第1の電圧源に接続された第1の端子、および、前記第1のノードに接続された第2の端子を有し、前記第1の変化回路がオンになるのに応えて前記第1のノードを前記第1の電圧源の電位へ変化させる第2の変化回路と、を備えることを特徴とするドライバ。

【0062】

(付記21) 付記14に記載の装置において、前記第1のTADは、前記ネットを介して第1の方向に伝送される信号の伝送速度を増加することを特徴とする装置。

(付記22) 付記14に記載の装置において、前記第1のTADは、前記ネットを介して第2の方向に伝送される信号の伝送速度を増加することを特徴とする装置。

【0063】

(付記23) 付記14に記載の装置において、前記第1のTADは、前記第1のノードを論理レベル『0』へ変化させ、そして、該第1のTADは、

前記第1のノードに接続された第1の端子、接地された第2の端子、および、ゲート端子を有する第1のトランジスタと、

第1の電源電圧源に接続された第1の端子、第2の端子、および、プリチャージクロック信号の反転信号を受け取るゲート端子を有する第2のトランジスタと、

前記第2のトランジスタの第2の端子に接続された第1の端子、前記第1のトランジスタのゲート端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第3のトランジスタと、

前記第3のトランジスタの第2の端子に接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号の反転信号を受け取るゲート端子を有する第4のトランジスタと、を備えることを特徴とする装置。

【0064】

(付記24) 付記23に記載の装置において、前記第1のTADは、さらに、前記第1のトランジスタのゲート端子に接続された第1の端子、接地された第2の端子、および、前記第1のノードに接続されるか或いは接地されたゲート端子を備えた第5のトランジスタを備えることを特徴とする装置。

(付記25) 付記23に記載の装置において、前記第1のTADは、さらに、前記第1のトランジスタのゲート端子に接続された第1の端子、接地された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第6のトランジスタを備えることを特徴とする装置。

(付記26) 付記23に記載の装置において、前記第1のTADは、さらに、前記ネットを論理レベル『1』にプリチャージするプリチャージトランジスタを備え、該プリチャージトランジスタは、前記第1の電源電圧源に接続された第1の端子、前記ネットに接続された第2の端子、前記プリチャージクロック信号を受け取るゲート端子を有することを特徴とする装置。

【0065】

(付記27) 付記14に記載の装置において、前記第1のTADは、前記第1のノードを論理レベル『1』へ変化させ、そして、該第1のTADは、

第1の電源電圧源に接続された第1の端子、第2の端子、および、プリチャージクロック信号を受け取るゲート端子を有する第1のプルアップトランジスタと、

該第1のプルアップトランジスタの第2の端子に接続された第1の端子、第2の端子、および、前記第1のノードに接続されたゲート端子を有する第1のプルダウントランジスタと、

該第1のプルダウントランジスタの第2の端子に接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号を受け取るゲート端子を有する第2のプルダウントランジスタと、

前記第1の電源電圧源に接続された第1の端子、前記第1のノードに接続された第2の端子、および、前記第1のプルアップトランジスタの第2の端子に接続されたゲート端子を有する第2のプルアップトランジスタと、を備えることを特徴とする装置。

【0066】

(付記28) 付記27に記載の装置において、前記第1のTADは、さらに、前記第1の電源電圧源に接続された第1の端子、前記第1のプルアップトランジスタの第2の端子に接続された第2の端子、および、前記第1のノードに接続されるか或いは接地されたゲート端子を有する第3のプルアップトランジスタを備えることを特徴とする装置。

(付記29) 付記27に記載の装置において、前記第1のTADは、さらに、前記電源電圧源に接続された第1の端子、前記第1のプルアップトランジスタの第2の端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第4のプルアップトランジスタを備えることを特徴とする装置。

【0067】

(付記30) 付記27に記載の装置において、前記第1のTADは、さらに、前記ネットを論理レベル『0』にプリチャージするプリチャージトランジスタを備え、該プリチャージトランジスタは、前記ネットに接続された第1の端子、接地された第2の端子、および、前記プリチャージクロック信号の反転信号を受け取るゲート端子を有することを特徴とする装置。

(付記31) 付記14に記載の装置において、該装置は、さらに、

第2のノードで前記ネットに接続され、該第2のノードの電圧レベルが閾値に到達するのに応えて当該第2のノードの電圧レベルを変化させる第2のTADを備えることを特徴とする装置。

【0068】

(付記32) 付記17に記載の方法において、前記ネットが論理レベル『1』にプリチャージされているとき、前記変化させるステップ(b)において、前記第1のノードの電圧レベルを論理レベル『0』へ変化させることを特徴とする方法。

(付記33) 付記17に記載の方法において、前記ネットが論理レベル『0』にプリチャージされているとき、前記変化させるステップ(b)において、前記第1のノードの電圧レベルを論理レベル『1』へ変化させることを特徴とする方法。

(付記34) 付記17に記載の方法において、前記変化させるステップ(b)は、

該ステップ(b)の閾値を、より高速のスイッチング速度と前記信号伝送システムのノイズ不活性との折り合いを付ける特定のレベルに設定することを備えることを特徴とする方法。

【0069】

(付記35) 付記17に記載の方法において、前記変化させるステップ(b)は、

第1の信号が前記ネットを介して第1の方向に伝わるとき、前記第1のノードの電圧レベルを変化させることを備えることを特徴とする方法。

(付記36) 付記17に記載の方法において、前記変化させるステップ(b)は、

第2の信号が前記ネットを介して第2の方向に伝わるとき、該第1のノードの電圧レベルを変化させることを備えることを特徴とする方法。

(付記37) 付記17に記載の方法において、該方法は、さらに、

第2のノードの電圧レベルが閾値に到達するのに応えて、該ネットにおける第2のノードの電圧レベルを変化させるステップを備えることを特徴とする方法。

【0070】

(付記38) 付記17に記載の方法において、該方法は、さらに、

隣接するネット間の信号を逆にスイッチングするのを回避するために、前記集積回路における少なくとも2つの隣接するネットの電圧レベルをプリチャージするステップを備えることを特徴とする方法。

(付記39) 付記18に記載の方法において、該方法は、さらに、

前記集積回路のノイズ不活性を調整するために、前記ステップ(b)の閾値を設定するステップを備えることを特徴とする方法。

【0071】

(付記40) 付記18に記載の方法において、該方法は、さらに、

第2のノードを介して前記電圧レベルが閾値に到達して前記信号が該第2のノードに接近するとき、前記ネットにおける第2のノードの電圧レベルをプリチャージするステップを備えることを特徴とする方法。

(付記41) 付記18に記載の方法において、該方法は、さらに、

隣接するネット間の信号を逆にスイッチングするのを回避するために、前記集積回路における少なくとも2つの隣接するネットの電圧レベルをプリチャージするステップを備えることを特徴とする方法。

【0072】

(付記42) 集積回路内において第1のノードを含むネットを介して信号の高速伝送を行う装置であって、

前記ネットに接続され、該ネットを介して前記信号を駆動する手段と、

前記ネットに接続され、前記第1のノードの電圧レベルが閾値に到達するのに応えて当該第1のノードの電圧レベルを変化させる第1の手段と、を備えることを特徴とする装置。

(付記43) 付記42に記載の装置において、該装置は、さらに、

前記ネットに接続され、前記第2のノードの電圧レベルが閾値に到達するのに応えて当該第2のノードの電圧レベルを変化させる第2の手段を備えることを特徴とする装置。

(付記44) 付記19に記載のドライバにおいて、前記第2の変化回路は、

前記第1のノードに接続された第1の端子、前記第2の電圧源に接続された第2の端子、および、前記第1の変化回路の出力端子に接続されたゲート端子を有する第1のトランジスタを備えることを特徴とするドライバ。

【0073】

(付記45) 付記19に記載のドライバにおいて、前記第1の変化回路は、

前記第1の電圧源に接続された第1の端子、第2の端子、および、反転されたクロック信号を受け取るゲート端子を有する第2のトランジスタと、

該第2のトランジスタの第2の端子に接続された第1の端子、前記第2の変化回路の入力端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第3のトランジスタと、

該第3のトランジスタの第2の端子に接続された第1の端子、前記第2の電圧源に接続された第2の端子、および、前記反転されたクロック信号を受け取るゲート端子を有する第4のトランジスタと、を備えることを特徴とするドライバ。

【0074】

(付記46) 付記19に記載のドライバにおいて、該ドライバは、さらに、

前記第1の電圧源に接続された第1の端子、前記ネットに接続された第2の端子、および、クロック信号を受け取るゲート端子を有するプリチャージトランジスタを備えることを特徴とするドライバ。

(付記47) 付記19に記載のドライバにおいて、該ドライバは、さらに、

前記第2の変化回路の入力端子に接続された第1の端子、前記第2の電圧源に接続された第2の端子、および、前記第1のノード或いは前記第2の電圧源に接続されたゲート端子を有する第5のトランジスタを備えることを特徴とするドライバ。

(付記48) 付記20に記載のドライバにおいて、前記第2の変化回路は、

前記第1の電圧源に接続された第1の端子、前記第1のノードに接続された第2の端子、および、前記第1の変化回路の出力端子に接続されたゲート端子を有する第1のトランジスタを備えることを特徴とするドライバ。

【0075】

(付記49) 付記20に記載のドライバにおいて、前記第1の変化回路は、

前記第1の電圧源に接続された第1の端子、第2の端子、および、クロック信号を受け取るゲート端子を有する第2のトランジスタと、

該第2のトランジスタの第2の端子に接続された第1の端子、前記第2の変化回路の入力端子に接続された第2の端子、および、前記第1のノードに接続されたゲート端子を有する第3のトランジスタと、

該第3のトランジスタの第2の端子に接続された第1の端子、前記第2の電圧源に接続された第2の端子、および、前記クロック信号を受け取るゲート端子を有する第4のトランジスタと、を備えることを特徴とするドライバ。

【0076】

(付記50) 付記20に記載のドライバにおいて、該ドライバは、さらに、

前記ネットに接続された第1の端子、前記第2の電圧源に接続された第2の端子、および、クロック信号を受け取るゲート端子を有するプリチャージトランジスタを備えることを特徴とするドライバ。

(付記51) 付記20に記載のドライバにおいて、該ドライバは、さらに、

前記第1の電圧源に接続された第1の端子、前記第2の変化回路の入力端子に接続された第2の端子、および、前記第1のノード或いは前記第2の電圧源に接続されたゲート端子を有する第5のトランジスタを備えることを特徴とするドライバ。

【0077】

【発明の効果】

以上、詳述したように、本発明によれば、近接効果による伝送遅延時間の増加を招くことなく、集積回路内のネット上での信号の伝送速度を上げることができる。

【図面の簡単な説明】

【図1】本発明の第1実施例に係る信号伝送システムであって、状態変化アシストドライバ(TAD)で信号の伝送速度を上げるようにした信号伝送システムを概略的に示すブロック図である。

【図2】図1に示す信号伝送システム内の特定のノードにおける電圧変動を表す第1の波形、および、TADによってアシストされない場合の同一のノードにおける電圧変動を表す第2の波形のグラフを示す図である。

【図3】本発明の第2実施例に係る信号伝送システムであって別のTADが追加された信号伝送システムの概略ブロック図である。

【図4】従来の信号伝送システムを概略的に示すブロック図である。

【図5】図3および図4の信号伝送システム内の異なるノードにおける電圧レベルを表す様々な波形のグラフを示す図である。

【図6】本発明の第3実施例に係る信号伝送システムであって、高い切り替え速度と優れたノイズ不活性との一方を犠牲にして他方を実現できるプログラマブルTADを備えた信号伝送システムを概略的に示すブロック図である。

【図7】本発明の第4実施例に係る信号伝送システムであって、ノイズ不活性を向上させたプログラマブルTADを備えた信号伝送システムの一部を示す図である。

【図8】本発明の第5実施例に係る信号伝送システムであって、システムへの電力投入中および/またはシステムリセット中にプリチャージされて論理レベル『0』になったネットにTADが接続される信号伝送システムを概略的に示すブロック図である。

【図9】図8の信号伝送システム内のノードにおける電圧変動を表す第1の波形、および、TADによってアシストされない場合の同一ノードにおける電圧変動を表す第2の波形のグラフを示す図である。

【図10】本発明の第6実施例に係る信号伝送システムであって、高い切り替え速度と優れたノイズ不活性との一方を犠牲にして他方を実現できるプログラマブルTADを備えた信号伝送システムを概略的に示すブロック図である。

【図11】本発明の第7実施例に係る信号伝送システムであって、多数のドライバをネットに接続してネットにおける双方向信号伝送を可能にした信号伝送システムを概略的に示すブロック図である。

【図12】ネットにおける双方向信号伝送を可能にした従来の信号伝送システムを概略的に示すブロック図である。

【符号の説明】

100,300,400,500,600,700,800,900,950…信号伝送システム

105,115.120,125,415,905,920,930,935,955,960,965…ドライバ

110,410,705…ネット(信号経路)

112,325,330,420,425,430…レシーバ

135,140,345,350,710,940,945…状態変化アシストドライバ(TAD)

505,605,805…プログラマブルTAD

510,610…Nチャネル型トランジスタ

525,620,780…インバータ

745…三状態ドライバ

770…Pチャネル型トランジスタ770

CLK…プリチャージクロック信号

Claims (4)

- ドライバが信号を駆動するネットに含まれるノードに接続され、前記ドライバによる前記信号の駆動を補助する補助ドライバにおいて、

電源に接続されたソース端子と、前記ノードに接続されたドレイン端子と、プリチャージクロック信号が入力されるゲート端子を有する第1のトランジスタと、

接地されたソース端子と、前記ノードに接続されたドレイン端子と、ゲート端子を有する第2のトランジスタと、

電源に接続されたソース端子と、ドレイン端子と、前記プリチャージクロック信号の反転信号が入力されるゲート端子を有する第3のトランジスタと、

前記第3のトランジスタのドレイン端子に接続されたソース端子と、前記第2のトランジスタのゲート端子に接続されたドレイン端子と、前記ノードに接続されたゲート端子を有する第4のトランジスタと、

接地されたソース端子と、前記第4のトランジスタのドレイン端子に接続されたドレイン端子と、前記プリチャージクロック信号の反転信号が入力されるゲート端子を有する第5のトランジスタと、

接地されたソース端子と、前記第2のトランジスタのゲート端子に接続されたドレイン端子と、前記第2のトランジスタのドレイン端子または接地端子に配線により選択的に接続されるゲート端子を有する第6のトランジスタを備えることを特徴とする補助ドライバ。 - 請求項1に記載の補助ドライバにおいて、さらに、

接地されたソース端子と、前記第2のトランジスタのゲート端子に接続されたドレイン端子と、前記第2のトランジスタのドレイン端子または接地端子に配線により選択的に接続されるゲート端子を有する第7のトランジスタを備えることを特徴とする補助ドライバ。 - 請求項1または2に記載の補助ドライバにおいて、

前記第1,第3および第4のトランジスタは、第1導電型のトランジスタであり、

請求項1における前記第2,第5および第6のトランジスタ、または、請求項2における前記第2,第5,第6および第7のトランジスタは、前記第1導電型と反対の第2導電型のトランジスタであることを特徴とする補助ドライバ。 - 請求項1〜3のいずれか1項に記載の補助ドライバにおいて、

前記補助ドライバは、前記ノードの電圧が所定の電圧レベルに到達した場合に、前記ノードの電圧を変化させることを特徴とする補助ドライバ。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/265289 | 1999-03-09 | ||

| US09/265,289 US6249147B1 (en) | 1999-03-09 | 1999-03-09 | Method and apparatus for high speed on-chip signal propagation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000307662A JP2000307662A (ja) | 2000-11-02 |

| JP4242995B2 true JP4242995B2 (ja) | 2009-03-25 |

Family

ID=23009840

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000064756A Expired - Fee Related JP4242995B2 (ja) | 1999-03-09 | 2000-03-09 | 補助ドライバ |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6249147B1 (ja) |

| EP (1) | EP1035653B1 (ja) |

| JP (1) | JP4242995B2 (ja) |

| DE (1) | DE60040504D1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001177581A (ja) * | 1999-12-16 | 2001-06-29 | Hitachi Ltd | 信号伝送回路および半導体集積回路装置 |

| US9124266B1 (en) * | 2012-08-31 | 2015-09-01 | Marvell Israel (M.I.S.L) Ltd. | Increasing switching speed of logic circuits |

Family Cites Families (40)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3819877A (en) | 1971-12-10 | 1974-06-25 | Bell Telephone Labor Inc | Centralized network for a telephone station system |

| FR2296221A1 (fr) | 1974-12-27 | 1976-07-23 | Ibm France | Systeme de traitement du signal |

| JPS5630981B2 (ja) | 1974-12-29 | 1981-07-18 | ||

| US4003057A (en) | 1975-09-05 | 1977-01-11 | The United States Of America As Represented By The Field Operations Bureau Of The Federal Communications Commision | Rear window direction finding antenna |

| US4154978A (en) | 1977-12-08 | 1979-05-15 | Operating Systems, Inc. | Self-contained bidirectional amplifying repeater |

| FR2479515A1 (fr) | 1980-03-28 | 1981-10-02 | Telecommunications Sa | Systeme de transmission numerique a l'alternat |

| US5546083A (en) | 1981-07-14 | 1996-08-13 | The United States Of America As Represented By The Secretary Of The Air Force | Bidirectional repeater amplifier |

| FR2523719B1 (fr) | 1982-03-17 | 1985-09-13 | Merlin Gerin | Detecteur de position d'un element mobile, notamment d'une barre de controle d'un reacteur nucleaire |

| US4512016A (en) | 1983-02-04 | 1985-04-16 | At&T Information Systems Inc. | Digital communication station signaling control |

| IT1161837B (it) | 1983-05-18 | 1987-03-18 | Telettra Lab Telefon | Sistema e apparecchiatura per la telesorveglianza di trasmissioni di dati |

| US4628157A (en) | 1984-09-07 | 1986-12-09 | At&T Bell Laboratories | Bidirectional adaptive voice frequency repeater |

| US4584441A (en) | 1984-09-07 | 1986-04-22 | At&T Bell Laboratories | Bidirectional adaptive voice frequency repeater |

| US4598410A (en) | 1984-09-17 | 1986-07-01 | Ncr Corporation | Bidirectional repeater apparatus |

| US4591669A (en) | 1984-09-26 | 1986-05-27 | At&T Bell Laboratories | Adaptive filter update gain normalization |

| US4658396A (en) | 1985-03-11 | 1987-04-14 | Barden Robert A | Redundancy arrangement for a local area network |

| JPH0720060B2 (ja) * | 1985-08-14 | 1995-03-06 | 株式会社東芝 | 出力回路装置 |

| US4847831A (en) | 1987-03-30 | 1989-07-11 | Honeywell Inc. | Bidirectional repeater for manchester encoded data signals |

| JPH04345062A (ja) | 1991-05-22 | 1992-12-01 | Fujitsu Ltd | 信号伝播高速化回路 |

| US5734334A (en) | 1991-10-30 | 1998-03-31 | I-Cube, Inc. | Programmable port for crossbar switch |

| US5414312A (en) | 1993-07-15 | 1995-05-09 | Altera Corporation | Advanced signal driving buffer with directional input transition detection |

| US5510739A (en) | 1994-03-28 | 1996-04-23 | Motorola, Inc. | Circuit and method for enhancing logic transitions appearing on a line |

| US5572441A (en) | 1994-04-04 | 1996-11-05 | Lucent Technologies Inc. | Data connector for portable devices |

| US5469473A (en) * | 1994-04-15 | 1995-11-21 | Texas Instruments Incorporated | Transceiver circuit with transition detection |

| US5629860A (en) | 1994-05-16 | 1997-05-13 | Motorola, Inc. | Method for determining timing delays associated with placement and routing of an integrated circuit |

| US5475605A (en) | 1994-05-26 | 1995-12-12 | Cadence Design Systems, Inc. | Timing analysis for logic optimization using target library delay values |

| US5655107A (en) | 1994-11-30 | 1997-08-05 | International Business Machines Corporation | Digital logic wire delay simulation |

| US5497108A (en) | 1994-12-08 | 1996-03-05 | Dynalogic Corporation | BICMOS repeater circuit for a programmable logic device |

| US5578939A (en) | 1995-01-23 | 1996-11-26 | Beers; Gregory E. | Bidirectional transmission line driver/receiver |

| US5568064A (en) | 1995-01-23 | 1996-10-22 | International Business Machines Corporation | Bidirectional transmission line driver/receiver |

| US5748487A (en) | 1995-01-31 | 1998-05-05 | Imec | System and method for generating a hazard-free asynchronous circuit |

| GB9502646D0 (en) * | 1995-02-10 | 1995-03-29 | Texas Instruments Ltd | Bus maintenance circuit |

| KR100352009B1 (ko) | 1995-04-28 | 2002-12-12 | 마츠시타 덴끼 산교 가부시키가이샤 | 논리집적회로의 신호전파 지연시간 평가방법 |

| US5659575A (en) | 1995-04-28 | 1997-08-19 | Grinnell Corporation | Method and apparatus for improving data regeneration in asynchronous network communication |

| US5649170A (en) | 1995-06-30 | 1997-07-15 | International Business Machines Corporation | Interconnect and driver optimization for high performance processors |

| US5604450A (en) | 1995-07-27 | 1997-02-18 | Intel Corporation | High speed bidirectional signaling scheme |

| US5886540A (en) * | 1996-05-31 | 1999-03-23 | Hewlett-Packard Company | Evaluation phase expansion for dynamic logic circuits |

| US5742181A (en) | 1996-06-04 | 1998-04-21 | Hewlett-Packard Co. | FPGA with hierarchical interconnect structure and hyperlinks |

| US5723906A (en) | 1996-06-07 | 1998-03-03 | Hewlett-Packard Company | High-density wirebond chip interconnect for multi-chip modules |

| US5933021A (en) * | 1996-06-18 | 1999-08-03 | Sun Microsystems, Inc | Noise suppression method and circuits for sensitive circuits |

| WO1998042021A1 (fr) | 1997-03-19 | 1998-09-24 | Hitachi, Ltd. | Dispositif pour circuit integre semi-conducteur |

-

1999

- 1999-03-09 US US09/265,289 patent/US6249147B1/en not_active Expired - Fee Related

-

2000

- 2000-03-09 EP EP00104487A patent/EP1035653B1/en not_active Expired - Lifetime

- 2000-03-09 JP JP2000064756A patent/JP4242995B2/ja not_active Expired - Fee Related

- 2000-03-09 DE DE60040504T patent/DE60040504D1/de not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP1035653B1 (en) | 2008-10-15 |

| EP1035653A2 (en) | 2000-09-13 |

| DE60040504D1 (de) | 2008-11-27 |

| EP1035653A3 (en) | 2001-02-07 |

| US6249147B1 (en) | 2001-06-19 |

| JP2000307662A (ja) | 2000-11-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5698994A (en) | Data output circuit, intermediate potential setting circuit, and semiconductor integrated circuit | |

| JPH08227582A (ja) | 最少パルス幅アドレス遷移検出回路 | |

| KR100202645B1 (ko) | 프리차지회로를 내장한 씨모스 출력회로 | |

| JPH03154290A (ja) | 半導体装置 | |

| KR0179793B1 (ko) | 반도체 메모리의 센스 앰프 출력 제어 회로 | |

| US5306958A (en) | High-speed address transition detection circuit | |

| KR100298182B1 (ko) | 반도체메모리소자의출력버퍼 | |

| KR0163447B1 (ko) | 데이터 아웃 버퍼회로 | |

| US5751160A (en) | Output buffer with improved operational speed and transitional current | |

| KR100567497B1 (ko) | 버스 인터페이스 회로 및 리시버 회로 | |

| US5708607A (en) | Data read circuit of a memory | |

| US20080290894A1 (en) | On die termination (odt) circuit having improved high frequency performance | |

| US4963774A (en) | Intermediate potential setting circuit | |

| JP3113853B2 (ja) | データ出力バッファ回路 | |

| JP4242995B2 (ja) | 補助ドライバ | |

| KR100486301B1 (ko) | 전력 소비를 감소시키는 종단 회로. | |

| US5132574A (en) | Mos output circuit | |

| US5646556A (en) | Apparatus and method for precharging bus conductors to minimize both drive delay and crosstalk within the bus | |

| US6294942B2 (en) | Method and apparatus for providing self-terminating signal lines | |

| KR20050003895A (ko) | 풀업 슬루율을 용이하게 조절할 수 있는 오픈 드레인출력버퍼 회로 | |

| JP3899472B2 (ja) | プリセット機能を持つ出力バッファ回路 | |

| JP3878419B2 (ja) | 半導体集積回路 | |

| US5831908A (en) | Data output circuit, intermediate potential setting circuit, and semiconductor integrated circuit | |

| KR100205094B1 (ko) | 반도체 소자의 출력버퍼 회로 | |

| KR100434966B1 (ko) | 출력 드라이버 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060525 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080118 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080122 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080324 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080701 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080827 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081202 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081226 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120109 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |