JP4223195B2 - アブソリュートエンコーダ - Google Patents

アブソリュートエンコーダ Download PDFInfo

- Publication number

- JP4223195B2 JP4223195B2 JP2001033610A JP2001033610A JP4223195B2 JP 4223195 B2 JP4223195 B2 JP 4223195B2 JP 2001033610 A JP2001033610 A JP 2001033610A JP 2001033610 A JP2001033610 A JP 2001033610A JP 4223195 B2 JP4223195 B2 JP 4223195B2

- Authority

- JP

- Japan

- Prior art keywords

- pattern

- bit

- error

- code

- bits

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Transmission And Conversion Of Sensor Element Output (AREA)

- Optical Transform (AREA)

Description

【発明の属する技術分野】

本発明は、直線駆動される対象物の位置を検出するアブソリュートエンコーダに係り、特に位置検出誤りを防止するための改良に関する。

【0002】

【従来の技術】

従来、図1に示すようなM系列等の符号パターンに相当する光学格子を検出パターンとして形成した符号板1を用いて絶対位置を検出する光学式リニアエンコーダが広く知られている。この光学式リニアエンコーダは、工作機械、三次元測定器、投影機、顕微鏡などの測長装置として利用されている。

【0003】

具体的に、従来の光学式リニアエンコーダの一種であるアブソリュートエンコーダは、図1に示すように、n次のM系列符号パターン等を必要な周期に変換し、相当する光学格子を透明なガラス板上に形成した符号板1と、この符号板1に対してその長手方向に平行移動可能に配置された位置検出ユニット10とから基本的に構成されている。

【0004】

この位置検出ユニット10は、発光素子2とコリメータレンズ3とから主として構成され符号板1に平行光を照射して反射させ、その反射光を照射させる光照射手段と、符号板1を反射した平行光を受光するラインセンサ4とを備えている。

【0005】

発光素子2から照射される光はコリメータレンズ3により平行光にコリメートされ、符号板1に照射される。位置検出ユニット10を符号板1に対して相対的に移動させると、符号板1で反射される光信号はその移動に伴って明暗の周期を繰り返す。このようにして生じた光信号はラインセンサ4により検出され、離散的な階段状の信号となって出力される。

【0006】

ラインセンサ4が出力するn次M系列等のnビットの符号パターンに相当する離散信号は、nビットのビットパターンにディジタル符号化され、あらかじめ対応づけられた絶対位置データに変換される。この絶対位置データは、例えばn次のM系列符号パターンで、「0」の連続する部分に「0」を1個余分に追加した2nビットの符号系列においては、1ビットずつシフトさせていった各nビットのM系列パターンに対して、「0」から2n−1までの連続した10進数の値としてあらかじめ対応付けられている。このような対応付けから得られる絶対位置データを、相当する位置信号に変換することにより符号板1上の位置検出ユニット10の絶対位置を求めることができるようになっている。

【0007】

符号板1には、所定周期で繰り返される符号系列を表すパターンが光学格子として形成されている。この符号系列を得るには、例えば必要とする周期よりも大きな周期のn次のM系列パターンを途中削除して繋ぎあわせるか、2n−1ビットの符号列の「0」が連続する部分に「0」を1つ挿入して、すべて「0」からなるnビットのパターンを1つ追加して、2nビットの符号列とする方法等が知られている。

【0008】

前記検出方式において、ラインセンサ4が符号板1上のnビット符号パターンを読み誤ることにより、誤った絶対位置データが出力されてしまう問題がある。これに対しては、kビットの冗長ビットを含むn+kビットの符号パターンを位置検出周期毎にラインセンサ4で読み取ることとし、符号板1に形成した符号パターンの生成規則に基づいて生成できる検査用多項式を複数用いることにより、読み取った符号パターンの検査結果を加算することで、読み取り誤りが発生したビット位置を検出する事が従来技術により可能である。例えば、「000100110101111」の15の符号からなる4次のM系列パターンに対しては、n=4、k=3とすると、たとえば次の[数1]で表される3つの検査用多項式を用いる。M系列パターン中で連続する7桁のビットパターン(便宜上a〜gとする)において、1ビット読み誤った場合の検査式(1),(2),(3)の値を次の[表1]に示す。

【0009】

【数1】

X0 + X3 + X4 (1)

X1 + X4 + X5 (2)

X2 + X5 + X6 (3)

【表1】

[表1]に示すように、検査式(1),(2)及び(3)の値のすべてが「0」でない場合には、読み取られたa〜gまでの符号に最低1個の読取り誤りが発生したことが判定できる。したがって、7ビットの読取りパターンについて、検査多項式の検査結果の排他的論理和を取ることにより、ラインセンサの1ビットの読取り誤りを検出できる。

【0010】

符号板1に形成された光学格子のパターンを、n次M系列パターンの「0」の連続する部分に「0」を1ビット分追加して2nビット周期の符号系列とした場合、検査用多項式を用いた従来の誤り検出方法を適用すると、挿入した「0」を1個含むすべて「0」のnビットのパターンに対しては通常の誤り検出方法をそのまま適用できないという問題があった。したがって、この「0」を含むパターンを読み取った場合には検査結果により読取り誤りが検出されていても誤り無しとするか、その特定パターンの場合には検出された誤り情報を出力しないなどの特別な誤り検出を行う必要がある。そのような従来の技術として例えば特開平9-280892に開示されているものがある。

【0011】

【発明が解決しようとする課題】

しかしながら、上記従来のリニアエンコーダでは、複雑な誤り検出を行うので、回路構成が複雑化するという問題点があった。

【0012】

本発明は、上記実状に鑑みなされたもので、簡便な構成により、パターンの読み取り誤りを確実に検出、訂正できるアブソリュートエンコーダを提供することを目的とする。

【0013】

【課題を解決するための手段】

上記従来例の問題点を解決するための請求項1記載の発明は、絶対位置データに対応付けられた符号ビット系列をパターンとして表した符号板と、前記符号板上のパターンに沿って相対移動し、移動位置において、前記パターンの一部を読み取るパターン読取部を含むパターン検出部と、前記パターン検出部が読み取ったパターンの一部に基づいて絶対位置データを演算して出力するデータ変換部と、を備えたアブソリュートエンコーダにおいて、前記パターン検出部のパターン読取部は、絶対位置データの演算に必要なnビットのパターン長に加え、それに隣接するパターン部分をkビットの冗長パターンとして読み取り、前記データ変換部は、前記パターン検出部が読み取ったkビットの冗長パターンを含むパターンの一部から一続きの絶対位置データの演算に必要なパターン長nビットのパターンを順次抽出し、当該抽出したnビットのパターンに対応する絶対位置データが連続的に変化するか否かによって、前記パターン検出部が読み取ったパターンに誤りがあるか否かを判定する判定部を含むことを特徴としている。

【0014】

また、上記従来例の問題点を解決するための請求項2記載の発明は、請求項1に記載のアブソリュートエンコーダにおいて、前記符号板に表された符号ビット系列は、所定の系列生成ルールに従って生成された符号ビット系列の一部にビットを挿入し、または前記生成された符号ビット系列の一部を削除した不連続部分を有する符号ビット系列であることを特徴としている。

【0015】

上記従来例の問題点を解決するための請求項3記載の発明は、請求項1又は2に記載のアブソリュートエンコーダにおいて、前記判定部は、冗長パターンに含まれる符号を順次処理し、誤りがあると判定すると、直ちに誤りを報知することを特徴としている。

【0016】

また、上記従来例の問題点を解決するための請求項4記載の発明は、請求項1又は2に記載のアブソリュートエンコーダにおいて、前記パターン検出部が読み取った冗長パターンを誤り訂正符号として、前記演算した絶対位置データに含まれる所定ビットまでの誤りを訂正し、当該訂正後の絶対位置データを出力する誤り訂正部を含み、前記判定部が演算した絶対位置データに誤りがある場合に、前記所定ビットを超えるビット数の誤りがあるか否かを判断して、所定ビットを超えるビット数の誤りがあった場合に、前記訂正後の絶対位置データに誤りがあると判定することを特徴としている。

【0017】

すなわち、例えばn次のM系列パターンに相当する光学格子が形成された符号板から、誤り検出のための冗長なkビットを余分に付加したn+kビットの符号列に相当するM系列パターンを読み取る。ここでの冗長ビット長kは、適用する符号系列の生成規則から生成可能な検査用多項式によりmビットの誤り検出及び訂正に必要な長さに決定される。そして、読み取ったパターンに対して、mビットの誤り検出と訂正が可能な検査多項式を一つ以上用いて、所定の誤り訂正可能ビット長であるmビットの読取り誤り位置を検出し、誤りビットの訂正も行う。ここで、誤りが検出されて誤りビットを訂正した場合と検出されなかった場合のいずれにも、読み取った元の符号パターンにm+1ビット以上の読取り誤りが発生している可能性があるので、さらにm+1ビット以上の誤り検出を行う。ここで、先に検査多項式によるmビットの誤り検出、訂正を行ったにも関わらず、m+1ビット以上の誤りが検出された場合には、読み取った元のパターンにm+1ビット以上の同時誤りが生じているものとし、読取り誤りである旨を報知する。また、m+1ビット以上の誤り検出を行っても誤りが検知されなかった場合には、読取ったパターンに誤りが無かったか、mビット以下の誤りが検出されて訂正された場合なので、元の、あるいはmビット誤りが訂正された符号パターンを絶対位置データに換算して出力する。

【0018】

上記従来例の問題点を解決するための請求項5記載の発明は、請求項1から4のいずれかに記載のアブソリュートエンコーダにおいて、さらに、冗長パターンにより誤りがあると判定された場合には、前記データ変換部が出力する絶対位置データを破棄し、前記パターン検出部に再読みとりを指示する手段を含む、ことを特徴としている。

【0019】

上記従来例の問題点を解決するための請求項6記載の発明は、請求項1から5のいずれかに記載のアブソリュートエンコーダにおいて、前記符号板に表された符号ビット系列は、M系列符号であることを特徴としている。

【0020】

【発明の実施の形態】

以下、本発明の好適な第1の実施の形態について、10次のM系列符号パターンを形成した符号板1を用い、冗長ビット長k=3とした場合を例として、図面を参照しつつ説明する。尚、同様の構成となる部分については、同一の符号を付している。

【0021】

本発明の実施の形態に係るアブソリュートエンコーダは、図1に示した従来のものと同様の構成をとるものであるが、パターン読み取り部としてのラインセンサ4と、ラインセンサ4により読み取られた符号の処理とが異なる。すなわち、本実施の形態のアブソリュートエンコーダは、図2に示すように、ラインセンサ4を含んでなるパターン検出部21と、誤り検出部22と、データ変換部23と、信号出力部24と、制御部30とから構成されている。

【0022】

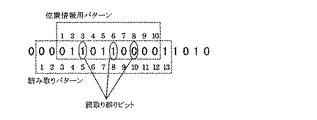

符号板1には、具体的に図3のような「0」または「1」からなるビット列がパターンとして記録されている。以下の説明では簡単のため、パターンの代わりにこのビット列を用いて説明する。ラインセンサ4は、符号板1に沿って相対移動し、移動位置での符号板1上に表されたパターンのうち、絶対位置の検出に必要な符号長に相当するnビット分のパターンとともに、その外側に隣接する符号(冗長パターン)k=3ビット分を読み取る。

【0023】

すなわち、ここでは10次のM系列符号パターンを用いた場合を例として説明しているので、図3の点線により示したn=10ビット分のビット列を読み取れば、絶対位置は検出できるのであるが、本実施の形態のラインセンサ4において特徴的なことは、このn=10ビットの少なくとも一方外側のビット列をkビット分だけ読み取ることである。

【0024】

具体的には、図4に示すように、本実施の形態では、パターン検出部21のラインセンサ4は、図3に示した点線部分の図面上左側2ビット分と、右側1ビット分の合計k=3ビットを冗長パターンとして読み取り、パターン検出部21が、このラインセンサ4で読み取ったn+kビットのパターンをビット列に変換して出力する。尚、後の説明の便利のため、この図4のn+kビットのパターン(13ビットのパターン)の各ビットを先頭から順に「第1ビット」から「第13ビット」と呼ぶ。

【0025】

データ変換部23は、パターン検出部21が出力するビット列に基づいて絶対位置データを演算して出力する。誤り検出部22は、データ変換部23が出力する絶対位置データに基づいてラインセンサ4の読み取り誤りを判定し、誤りがなければ、データ変換部23で得られた絶対位置データを信号出力部24に出力する。また、誤りがあれば、パターン検出部21に再度読み取りを指示する信号を出力する。信号出力部24は、絶対位置データの入力を受けて、当該絶対位置データに対応する位置信号を生成して、制御装置30に出力する。

【0026】

ここでデータ変換部23は、第1から第10ビットまでのビット列と、第2から第11ビットまでのビット列と、第3から第12ビットまでのビット列と、第4から第13までのビット列との各々に基づいて絶対位置データを演算し、誤り検出部22は、各々のビット列から得られる絶対値データが連続しているか否かにより、読み取り誤りが発生したか否かを判定する。

【0027】

以下、本発明の実施の形態に係るアブソリュートエンコーダの動作について、具体的に図3に示したビット列を読み取る場合を例として説明する。パターン検出部21のラインセンサ4がこのパターンが表された符号板1を読み取るときに、図5に示すように、第5ビット、第8ビット、第10ビットの3カ所で読み取り誤りが発生したと仮定すると、パターン検出部21は、本来、「0001001001001」と読み取られるべきビット列を「0001101100001」として出力する。

【0028】

すると、データ変換部23が、このパターン検出部21が出力するビット列に基づいて、まず、本来用いるべきnビット分として、第3ビットから第12ビットまでの「0110110000」の部分を用いて絶対位置データを演算する。ここで、第5,第8,第10の各ビットに誤りが含まれているので、このビット列からは正しい絶対位置データが演算されない。一例としてここでは、上記ビットにより、十進数で「935」の絶対位置データが演算されるものとする。

【0029】

次に、データ変換部23は、図6に示すように、第2ビットから第11ビットまでの10ビット分「0011011000」の部分(誤り検査用パターン)を用いて絶対位置データの演算を行う。この場合には、符号板1に対して位置検出ユニット10が右に1ビット分だけずれた位置にあるので、本来ならば「935」に連続する「936」となるはずであるが、読み取り誤りが含まれているために全く別の数値、たとえば十進数で「447」が得られるようになる。誤り検出部22は、「935」と、「447」とを比較し、これらが連続していないため、読み取り誤りが発生したと判断して、パターン検出部21にパターンの再読みとりを指示し、パターン検出部21が再度、パターンの読み取りを行うようになる。

【0030】

尚、読み取り誤りが発生していない場合には、これらの数値は連続することになるため、誤り検出部22は、第3ビットから第12ビットまでのビット列から得られる本来の絶対位置データを信号出力部24に出力する。そして、信号出力部24が、当該絶対位置データに対応する位置信号を生成し、制御装置30に出力する。

【0031】

また、従来例と同様に、M系列符号の一部(「0」がn個並んだ位置)に無効なビット(余計な「0」)を追加したり、M系列符号の一部を削除して不連続部分を生成し、これを符号板1に表している場合には、読み取り誤りの結果、たとえば、第3ビットから第12ビットまでのビット列から演算される絶対位置データ(本来の絶対位置データ)と、第2ビットから第11ビットまでのビット列(誤り検査用パターン)から演算される絶対位置データとが連続してしまう可能性が否定できない。この場合には、誤り検出部22は、図7に示すようなデータ変換部23が第4ビットから第13ビットまでのビット列に基づいて演算した絶対位置データや、第1ビットから第10ビットまでのビット列に基づいて演算した絶対位置データ等を用い、これらすべての絶対位置データが連続している場合にのみ、誤りなしとして、データ変換部23から入力される本来の絶対位置データを信号出力部24にそのまま出力する。

【0032】

さらに、ここでは、読み取られたビット列を1ビットずつシフトしたビット列が連続するか否かにより、読み取り誤りが発生したか否かを判定しているが、mビットずつシフトして、絶対位置データが「m」だけずれて連続しているか否かを検出することとしてもかまわない。また、左右双方にシフトする場合には、シフト量が異なってもよい。

【0033】

さらに、誤り検出部22は、カウンタを備え、読み取り誤りが発生したことを検知してパターン検出部21に対し再読み取りを指示したときに当該カウンタをインクリメントし、所定の値に当該カウンタが達したときには(読み取り誤りが繰り返し発生する場合には)、エラーを報知して処理を中断することとするのも好適である。この繰り返しの回数は、制御装置30の用途やシステム全体の利用形態に依存して決定されるべきであるので、ユーザが適宜設定可能としておくことが好ましい。

【0034】

このように本実施の形態によれば、適用するM系列符号の次数が決まれば、当該M系列符号の性質上、適切な冗長パターンのビット数を決定でき、検査多項式を用いた既存の誤り訂正方式を適用する場合に比べ、検出及び訂正できるビット数が限定されることがなく、検査多項式の誤り検出能力を超えるようなラインセンサの読み取り誤りに対しても対応できる。

【0035】

ここで、冗長パターンのビット数は、M系列符号の性質上、読み取りの際の同時誤りビット数が多いほど冗長パターンのビット数は少なくてもよくなるので、1ビットの誤りを想定して適切な冗長パターンのビット数を定めることで確実性の高い誤り検出を行うことができる。

【0036】

尚、ここまでの説明では、M系列符号を例として説明したが、順序がランダムで絶対位置データを対応付けるための全ての符号語が一意となれば(すなわちM系列と同様の性質を備えていれば)他の符号系列を用いても構わない。

【0037】

次に、本発明の第2の実施の形態に係るアブソリュートエンコーダについて図面を参照しながら説明する。本実施の形態のアブソリュートエンコーダは、図8に示すように、ラインセンサ4を含んでなるパターン検出部21と、誤り訂正部25と、データ処理部26と、データ変換部23と、信号出力部24と、制御装置30とから構成されている。尚、第1の実施の形態と同様のものについては同じ符号を付して詳細な説明を省略する。また以下では、10次(n=10)のM系列符号を表すパターンが符号板1上に形成され、冗長ビットの長さk=10、誤り訂正可能なビット長m=1とした場合を例として説明する。

【0038】

本実施の形態のアブソリュートエンコーダでは、n=10、k=10であるので、パターン検出部21は図9に示すように、点線部分の図面上右側10ビット分(k=10)ビットを冗長パターンとして読み取り、パターン検出部21が、このラインセンサ4で読み取ったn+kビットのパターンをビット列に変換して出力する。尚、説明の便宜上、この図9のn+kビットのパターン(20ビットのパターン)の各ビットを先頭から順に「第0ビット」から「第19ビット」と呼ぶ。

【0039】

そして、位置検出ユニットは図10に示す処理を開始し、誤り訂正部25がM系列の生成規則から各次数毎に定まる検査多項式を用いて、読み取ったパターンに誤りが含まれているか否かを検査する(S1)。ここで、10次のM系列パターンに対して、1ビットの誤り検出を行うための検査多項式は、一例として次式で与えられる。

【0040】

【数2】

X0+i + X7+i + X10+i (i= 0,1,2,… ,k-1) (4)

なお、10次のM系列パターンに対して、1ビットの誤り検出を行うには冗長ビットが最低7ビット必要であり、ここではさらに訂正も行うために、冗長ビット長を10ビットとしている。(4)式により、読み取ったビット列中の該当ビットの値(「0」または「1」)を加算する(2を法とする)ことで、読取り誤りが発生したか否かを検出する。図9に示した元の読取りパターンで1ビットの読取り誤りが発生した場合の検査式(4)の値を次の表に示す。

【0041】

【表2】

そして、mビット以下の誤りが検出されたか否かが調べられ(S2)、mビット以下の誤りが検出される場合(Yesの場合)、つまり例えば図9に示した符号パターンが、ラインセンサ4の読み取り誤りによって、図11に示すように第7ビットが1ビット誤ってmビット誤り訂正部に転送されたものとすると、(4)の検査式を用いた[表2]の結果より、i=0,7の場合の検査式である次式、

【数3】

X0 +X7 +X10 (5)

X7 +X14+X17 (6)

の値が「1」となり、iが0から9までの各検査式の値の組合せが、誤ったビット位置毎に一意に対応付けられる。ここでは、それぞれの検査式の結果をそれぞれ二進数の各桁と見立てて10進数の値に変換して識別値とし、その値と誤ったビット位置とを関連づけている。したがって、図11のような読取り誤りが発生した場合には検査式の各値を二進数の各桁と見立てた場合、誤り訂正部25では検査結果として二進数の「1000000100」に対応する「258」が算出され、読取り誤りの発生とともに、誤ったビット位置が第7ビットであることが検出される。

【0042】

そして誤り訂正部25は、誤ったとして検出された位置のビットを反転する(S3)。具体的に図11の第7ビットを反転して、全体のビットパターンを図9に示した「100110110110101111100」に訂正し、データ処理部26に出力する。この場合、発生した1ビットの読取り誤りが検出、訂正されたので、後に説明するデータ処理部26において、検出、訂正後の符号パターンから更に誤りが検出されることはない。

【0043】

また、処理S2において、誤りがないとして検出された場合には(Noの場合)、ビットの反転を行うことなく、そのままデータ処理部26での処理に移行する。

【0044】

一方、図9に示すパターンを読み違えた場合に、処理S2では1ビットのみが誤りであって訂正可能と判断されるにも関わらず、実際には複数のビットが誤っているということもあり得る。そのような場合とは、例えば、ラインセンサ4の読み取り誤りにより、図9のパターンのうち、図12に示すように、第0、7、16ビットの3ビットが誤って読み取られ、mビット誤り訂正部25に出力される場合がある。このとき(4)の検査式を用いた[表2]の結果より、i=6、9の場合の検査式、

【数4】

X6 + X13 + X16 (7)

X9 + X16 + X19 (8)

の値が1となり、検査結果により誤ったビット位置が第16ビットの1ビットと検出され、第0、7ビットの誤りが正しく検出されない。この場合には、第16ビットのみが反転されて、図13に示すような符号に訂正されてデータ処理部26に出力されることとなる。これは、検査多項式による誤り検出方式では、用いる検査多項式の検出能力を超える読取り誤りが発生した場合に、検出、訂正後の符号列にさらに誤りが含まれていないかどうか判定できないことによるものである。

【0045】

データ処理部26は、誤り訂正部25から入力される誤り訂正後のn+kビットの符号(ただし、誤り訂正部25で誤りが検出されなかった場合には読み取られた符号そのものになる)に対して、さらにm+1ビット以上の誤り検出を行う。具体的にこのデータ処理部26は、第1の実施の形態における誤り検出部22と同様に、読み取られたn+kビットの符号パターンからnビットを取り出して、そのnビットに対しデータ変換部23で変換された位置を示す値を得ておき、さらに1ビットずつずらしながらnビットを取り出して連続しているか否かを比べることでm+1ビット以上の誤りがあるか否か(誤り訂正によっても訂正不能であった誤りがまだ含まれているか否か)を検出し(S4)、誤りが検出されたかを判断して(S5)、誤りが検出されないならば(Noならば)、データ処理部26は、図9の第0〜第9ビットで表される本来の絶対位置データを信号出力部24に出力する。そして、信号出力部24が、当該絶対位置データに対応する位置信号を生成し、制御装置30に出力する。

【0046】

しかし、読み取りを誤った場合にも、たとえば、第0ビットから第9ビットまでのビット列から演算される絶対位置データ(本来の絶対位置データ)と、第1ビットから第10ビットまでのビット列(誤り検査用パターン)から演算される絶対位置データとが連続してしまう可能性も否定できない。このため、データ処理部26は、さらにシフトした第2ビットから第11ビットまでのビット列に基づいて演算した絶対位置データや、第3ビットから第12ビットまでのビット列に基づいて演算した絶対位置データ等を用い、複数の絶対位置データが連続している場合にのみ、誤りがないとして、データ変換部23から入力される本来の絶対位置データを信号出力部24に出力するようにしてもよい。

【0047】

また、処理S5において、誤りが検出されたときには(Yesならば)、誤りがあったことをアラームとして報知し(S6)、パターン検出部21に対し、再読み取りを指示して(S7)、処理を終了する。

【0048】

尚、これら第1、第2の実施形態では、誤り検出部22又はデータ処理部26が、読み取られたビット列を1ビットずつシフトしたビット列が連続するか否かにより、読み取り誤りが発生したか否かを判定しているが、jビットずつシフトして、絶対位置データが「j」だけずれて連続しているか否かを検出することとしてもかまわない。また、左右双方にシフトする場合には、左右それぞれにシフト量が異なってもよい。

【0049】

さらに、誤り検出部22又はデータ処理部26は、カウンタを備え、読み取り誤りが発生したことを検知してパターン検出部21に対し再読み取りを指示したときに当該カウンタをインクリメントし、所定の値に当該カウンタが達したときには(読み取り誤りが繰り返し発生する場合には)、エラーを報知して処理を中断することとするのも好適である。この繰り返しの回数は、制御装置30の用途やシステム全体の利用形態に依存して決定されるべきであるので、ユーザが適宜設定可能としておくことが好ましい。

【0050】

さらに、ここまでの説明では、M系列符号を例として説明したが、順序がランダムで絶対位置データを対応付けるための全ての符号語が一意となれば(すなわちM系列と同様の性質を備えていれば)他の符号系列を用いても構わない。

【0051】

さらに、ここまでの説明では、適用する検査多項式として1ビットの誤り検出訂正が可能な(4)式を10個用いた例として説明したが、本発明の要旨を逸脱しない範囲において、他の検査多項式を何個用いても構わない。

【0052】

また、第2の実施の形態では、誤り訂正部25において、符号系列の生成規則より定まる検査多項式を用いた誤り検出・訂正処理を行っている。ここで、適用する符号系列が例えばM系列であって、2のn乗−1ビットの符号列の、0が連続する部分に0を1個挿入して、オール0のnビットのパターンを1個追加する方法等により、生成規則を崩した符号系列には、検査多項式の対応不可能なパターンが含まれる。したがって、そのような符号系列に本発明を適用する場合、ラインセンサ4による不連続部の読取り時においては、読取りパターンに含まれる誤りビット数がmビット以下の場合にも、誤り訂正部25により完全な誤り検出を行うのは不可能となるが、そのような場合にもデータ処理部26におけるm+1ビット誤り検出処理によって、不連続部を含む読取りパターンに含まれる誤りビットを検出することが可能である。

【0053】

このように本実施の形態によれば、適用するM系列符号の次数が決まれば、当該M系列符号の性質上、適切な冗長パターンのビット数を決定でき、検査多項式を用いた既存の誤り訂正方式を適用する場合に比べ、検出できるビット数が限定されることがなく、検査多項式の誤り検出能力を超えるようなラインセンサの読み取り誤りに対しても対応できる。

【0054】

ここで、冗長パターンのビット数は、M系列符号の性質上、読み取りの際の同時誤りビット数が多いほど冗長パターンのビット数は少なくてもよくなるので、1ビットの誤りを想定して適切な冗長パターンのビット数を定めることで確実性の高い誤り検出を行うことができる。ただし、冗長ビット数に関しては、前記mビット誤り検出訂正部43の処理でmビットの誤り検出訂正の必要なビット数以上に決定する必要がある。

【0055】

さらに、第2の実施の形態のように、誤り訂正を行うこととすれば、符号板1の汚れ又は軽微な損傷によるパターンの欠落などに起因して、ラインセンサ4が読み取り誤りを起こしたり、あるいはラインセンサ4の出力波形の歪みに起因するM系列等のビット列への符号化誤りが特定箇所で頻繁に起こるような場合にも、検査多項式による誤り検出訂正によってmビットの読取り誤りまでは訂正可能となるため、そのような場合にも、符号板1の清掃又は交換などの対処が不要となり、アブソリュートエンコーダのメンテナンスにかかる労力及びコストを低減することができる。

【0056】

さらに、検査多項式の誤り訂正能力を超えるm+1ビット以上の誤りビットが発生した場合には、検査多項式を用いた誤り検出方式では、発生した誤りビットの内のmビット分しか検出訂正されないため、誤り検出訂正後の符号パターンに誤りビットが残っている可能性があり、そのままでは検出パターンを位置データとして適用できない。しかしながら、第2の実施の形態によれば、検査用多項式によるmビットの誤り検出訂正を行った後、位置情報用パターンと誤り検査用パターンのそれぞれに対応する絶対位置データを順次比較する方法を用いて、元の検出パターンに検査多項式の誤り検出訂正能力を超えるm+1ビット以上の誤りが含まれているか否か検査を行うように構成したので、位置データの信頼性を高めることができる。

【0057】

また、第1、第2の実施の形態によれば、M系列等の符号生成規則に基づいて生成できる検査用多項式及び、冗長ビットを含む検出パターンから演算される絶対位置データの連続性によって読み取り誤りを検出するので、M系列で次数の異なる場合など、適用する検出パターンの周期によらず、任意周期の検出パターンに対して同様の構成により適用することができる。

【0058】

【発明の効果】

本発明によれば、符号系列のパターンを用いたリニアエンコーダにおいて、誤り検出用の冗長ビットを含めたパターンを読み取り、この冗長ビットに基づいて読み取り誤りを検出するので、簡便な構成により、確実に読み取り誤りを検出できる。

【0059】

また、本発明では、読み取ったパターンを順次シフトした場合に、各シフト後のパターンから演算される絶対位置データの連続性によって読み取り誤りを検出するので、簡便な構成により、確実に読み取り誤りを検出できる。また、これにより、1ビットの誤りのみならず、複数ビットの誤りをも確実に検出できる。

【0060】

さらに本発明によれば、読取りの同時誤りビット数が多くなるほど誤り検出のために読取る冗長ビット数が少なくて済むため、1ビットの読取り誤りを想定して最適な冗長パターンのビット数を決めれば検出可能なビット数が制限されることがなく、読取りの同時誤りビット数に関わらず確実に読取り誤りを検出できる。

【0061】

さらに本発明によれば、冗長ビットを誤り訂正符号として用いる第1の検査訂正法によって所定ビット数までの読み取り誤りを訂正し、さらに所定ビット数を超える読み取り誤りを検出可能な第2の検査法によって所定ビット数を超える読み取り誤りを検出するようにしたので、所定ビット数以下の誤りを訂正可能にするとともに、第1検査訂正法により検出不能であった所定ビット数を超える誤りが第2の検査法によって見いだされたときには、これを誤りとして扱うことで、簡便な構成により、位置検出の誤りを確実に検出・訂正できる。

【図面の簡単な説明】

【図1】 アブソリュートエンコーダの一例を表す説明図である。

【図2】 本発明の第1の実施の形態に係るアブソリュートエンコーダを表す構成ブロック図である。

【図3】 符号板1に表されたビット列の一部の一例を表す説明図である。

【図4】 ラインセンサ4により読み取られるビット列の一例を表す説明図である。

【図5】 データ変換部23により処理されるビット列の一例を表す説明図である。

【図6】 データ変換部23により処理されるビット列の一例を表す説明図である。

【図7】 データ変換部23により処理されるビット列の一例を表す説明図である。

【図8】 本発明の第2の実施の形態に係るアブソリュートエンコーダを表す構成ブロック図である。

【図9】 ラインセンサ4により読み取られるビット列の一例を表す説明図である。

【図10】 本発明の第2の実施の形態に係るアブソリュートエンコーダの動作を示すフローチャート図である。

【図11】 ラインセンサ4により読み取られるビット列の一例を表す説明図である。

【図12】 ラインセンサ4により読み取られるビット列の一例を表す説明図である。

【図13】 ラインセンサ4により読み取られるビット列の一例を表す説明図である。

【符号の説明】

1 符号板、2 発光素子、3 コリメータレンズ、4 ラインセンサ、10位置検出ユニット、21 パターン検出部、22 誤り検出部、23 データ変換部、24 信号出力部、25 誤り訂正部、26 データ処理部、30 制御装置。

Claims (7)

- 絶対位置データに対応付けられた符号ビット系列をパターンとして表した符号板と、

前記符号板上のパターンに沿って相対移動し、移動位置において、前記パターンの一部を読み取るパターン読取部を含むパターン検出部と、

前記パターン検出部が読み取ったパターンの一部に基づいて絶対位置データを演算して出力するデータ変換部と、を備えたアブソリュートエンコーダにおいて、

前記パターン検出部のパターン読取部は、絶対位置データの演算に必要なnビットのパターン長に加え、それに隣接するパターン部分をkビットの冗長パターンとして読み取り、前記データ変換部は、前記パターン検出部が読み取ったkビットの冗長パターンを含むパターンの一部から一続きの絶対位置データの演算に必要なパターン長nビットのパターンを順次抽出し、当該抽出したnビットのパターンに対応する絶対位置データが連続的に変化するか否かによって、前記パターン検出部が読み取ったパターンに誤りがあるか否かを判定する判定部を含むことを特徴とするアブソリュートエンコーダ。 - 請求項1に記載のアブソリュートエンコーダにおいて、前記符号板に表された符号ビット系列は、所定の系列生成ルールに従って生成された符号ビット系列の一部にビットを挿入し、または前記生成された符号ビット系列の一部を削除した不連続部分を有する符号ビット系列であることを特徴とするアブソリュートエンコーダ。

- 請求項1又は2に記載のアブソリュートエンコーダにおいて、前記判定部は、冗長パターンに含まれる符号を順次処理し、誤りがあると判定すると、直ちに誤りを報知することを特徴とするアブソリュートエンコーダ。

- 請求項1又は2に記載のアブソリュートエンコーダにおいて、

前記パターン検出部が読み取った絶対位置データの演算に必要なnビットのパターンとkビットの冗長パターンを含むn+kビットのパターンについて所定ビットまでの誤りの検出及び訂正を行い、n+kビットの訂正後パターンを出力する誤り訂正部と、前記訂正後パターンに基づいて演算した複数の絶対位置データを用いて、前記訂正後パターンに誤りがあると判定する判定部を有することを特徴とするアブソリュートエンコーダ。 - 請求項4に記載のアブソリュートエンコーダにおいて、前記誤り訂正部は、前記符号ビット系列の系列生成ルールから生成可能なm(<n+k)ビットの誤り検出訂正能力を有する検査多項式を一つ以上用いて、前記パターン検出部が読み取った冗長ビットを含むn+kビットのパターンにmビット以下の誤りがあるか否かの判定を行い、誤りがあれば該当ビットを訂正してn+kビットの検出訂正後パターンを出力することを特徴とするアブソリュートエンコーダ。

- 請求項1から4のいずれかに記載のアブソリュートエンコーダにおいて、さらに、冗長パターンにより誤りがあると判定された場合には、前記データ変換部が出力する絶対位置データを破棄し、前記パターン検出部に再読みとりを指示する手段を含む、ことを特徴とするアブソリュートエンコーダ。

- 請求項1から5のいずれかに記載のアブソリュートエンコーダにおいて、前記符号板に表された符号ビット系列は、M系列符号であることを特徴とするアブソリュートエンコーダ。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001033610A JP4223195B2 (ja) | 2000-02-10 | 2001-02-09 | アブソリュートエンコーダ |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000-33945 | 2000-02-10 | ||

| JP2000033945 | 2000-02-10 | ||

| JP2001033610A JP4223195B2 (ja) | 2000-02-10 | 2001-02-09 | アブソリュートエンコーダ |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001296145A JP2001296145A (ja) | 2001-10-26 |

| JP2001296145A5 JP2001296145A5 (ja) | 2005-09-02 |

| JP4223195B2 true JP4223195B2 (ja) | 2009-02-12 |

Family

ID=26585234

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001033610A Expired - Fee Related JP4223195B2 (ja) | 2000-02-10 | 2001-02-09 | アブソリュートエンコーダ |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4223195B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016023982A (ja) * | 2014-07-17 | 2016-02-08 | シチズンホールディングス株式会社 | 測長器 |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4253501B2 (ja) * | 2002-12-27 | 2009-04-15 | オークマ株式会社 | アブソリュート位置検出装置 |

| JP5021244B2 (ja) * | 2006-07-03 | 2012-09-05 | 株式会社ミツトヨ | 変位検出エンコーダ |

| JP6320149B2 (ja) * | 2014-04-21 | 2018-05-09 | キヤノン株式会社 | アブソリュートエンコーダ |

| DE102016204313A1 (de) * | 2016-03-16 | 2017-09-21 | Dr. Johannes Heidenhain Gesellschaft Mit Beschränkter Haftung | Optischer Abstandssensor und Positionsmesseinrichtung mit einem derartigen Abstandssensor |

| JP6611672B2 (ja) * | 2016-06-02 | 2019-11-27 | 日本電産サンキョー株式会社 | ロータリエンコーダ |

| CN111238547B (zh) * | 2020-01-19 | 2022-02-08 | 东方电气自动控制工程有限公司 | 一种位置式编码器过零翻转时转速计算的算法 |

| JP7443140B2 (ja) | 2020-04-09 | 2024-03-05 | Dmg森精機株式会社 | 位置検出装置 |

| JPWO2022107421A1 (ja) * | 2020-11-20 | 2022-05-27 |

-

2001

- 2001-02-09 JP JP2001033610A patent/JP4223195B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2016023982A (ja) * | 2014-07-17 | 2016-02-08 | シチズンホールディングス株式会社 | 測長器 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001296145A (ja) | 2001-10-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US11619521B2 (en) | Position measurement encoder and method of operation | |

| JP4447875B2 (ja) | 絶対位置を測定する方法 | |

| JP4966044B2 (ja) | エンコーダ | |

| JP5079644B2 (ja) | 位置測定装置 | |

| JP5147513B2 (ja) | エンコーダ | |

| JP4223195B2 (ja) | アブソリュートエンコーダ | |

| JP3176861B2 (ja) | 位置測定装置 | |

| EP1876424B1 (en) | Displacement detecting encoder | |

| RU2004115730A (ru) | Диск dvd с защитой от копирования и способ его производства и проверки достоверности | |

| US20150300847A1 (en) | Absolute encoder | |

| GB2399896A (en) | Identifying uncorrectable codewords in a reed-solomon decoder handling errors and erasures | |

| JPH041522A (ja) | 異常事態を検出可能なアブソリュート・エンコーダ | |

| JP4726220B2 (ja) | アブソリュートエンコーダ | |

| EP2312273A2 (en) | Displacement detector, displacement detection method and computer program product | |

| JP2001296145A5 (ja) | ||

| KR100281946B1 (ko) | 신드롬 계산 장치 | |

| JP2004144667A (ja) | 位置情報の異常検出装置 | |

| JP7234087B2 (ja) | アブソリュートリニアエンコーダ | |

| US6728052B2 (en) | Recording/reproducing apparatus, error correcting coding method and information recording method | |

| JPH09280892A (ja) | M系列を用いたアブソリュートエンコーダ | |

| JPH04131713A (ja) | センサ続み誤りの検出および訂正が可能な1トラック型アブソリュート・エンコーダ | |

| JP4146133B2 (ja) | リニアエンコーダ | |

| KR100397095B1 (ko) | 에러 검출 장치 및 그 방법 | |

| JPH04301927A (ja) | 誤り検出機能付きロ−タリ−・アブソリュ−ト・エンコ−ダ | |

| US20220260365A1 (en) | Rotary position encoding using non-maximal-length pseudo-random codes |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050308 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050308 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20070222 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080902 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081023 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20081023 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081111 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081119 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4223195 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111128 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111128 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141128 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |