JP4201239B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4201239B2 JP4201239B2 JP2001368010A JP2001368010A JP4201239B2 JP 4201239 B2 JP4201239 B2 JP 4201239B2 JP 2001368010 A JP2001368010 A JP 2001368010A JP 2001368010 A JP2001368010 A JP 2001368010A JP 4201239 B2 JP4201239 B2 JP 4201239B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- semiconductor

- tft

- film

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

【0002】

本発明は、絶縁基板上に作製される薄膜トランジスタ(TFT)を有する半導体装置に関する。また、薄膜トランジスタを有する半導体表示装置に関する。

【0003】

【従来の技術】

【0004】

薄膜トランジスタ(TFT)をスイッチング素子として用いたアクティブマトリクス型表示装置の作製技術の開発は進んでいる。最近では、表示機能以外の付加価値のある半導体表示装置が求められている。

【0005】

同時に、このような半導体表示装置を用いた電子機器では、小型携帯機器をはじめ、低消費電力化が求められている。

【0006】

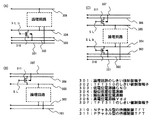

図1(A)に従来の半導体装置における回路のブロック図を示す。

【0007】

図1(A)において、インバータやNANDなどの論理回路は、直接電源線(高電位電源線Vddおよび低電位電源線GND)に接続されている。

【0008】

従来の半導体装置の回路の例として、インバータ回路の回路図を図1(B)に示す。

【0009】

図1(B)では、論理回路の例として、CMOS回路によるインバータ回路110が接続されている。

【0010】

例えば入力端子の電位が低電位(NチャネルTFT102のしきい値電圧より低い電位)のとき、PチャネルTFT101のソース・ドレイン間の抵抗値は小さくなり、実質的に0とみなせる(ON)。一方NチャネルTFT102のソース・ドレイン間の抵抗値は十分に大きく、実質的にソース・ドレイン間は電気的に切断された状態になる(OFF)。従って出力端子の電位は高電位になる。

【0011】

しかし、実際にはTFT102のソース・ドレイン間の抵抗値は十分に大きくならず、TFT102のソース・ドレイン間には電流(リーク電流)が流れ続ける場合がある。このとき、VddとGNDの間に直流パスを生じ、回路全体で問題になるほどVddとGNDの間に電流が流れ続けることがあり、電源線が電圧降下を起こして動作が異常になる、あるいは低消費電力化の妨げになる。

【0012】

【発明が解決しようとする課題】

【0013】

本発明は、上記従来技術の問題点に鑑みてなされたもので、その目的とするところは、絶縁基板上で、論理回路の動作周波数を向上させ、または消費電力を低減させつつ、待機(スリープ)時の論理回路の消費電力を低減することにある。また、論理回路を構成するTFTにおいて、大電流を取り出すことでTFTのサイズ縮小化をはかり、更なる高機能化・高付加価値を目指すことにある。

【0014】

【課題を解決するための手段】

【0015】

本発明における第1の構成によると、バックゲート電極に印加する電位を変化させ、TFTのしきい値を制御することによってリーク電流を低減することのできるTFTによって、待機時に論理回路を電源線から電気的に切り離し、あるいは動作時に論理回路と電源線を電気的に接続する制御をする構造をもつ半導体装置が提供される。論理回路と電源線の電気的接続・切断を制御する前記TFTを待機制御TFTとよぶ。

【0016】

本発明における第2の構成によると、上記待機制御TFTと同じ構造をもつ別のTFTによって構成された論理回路をもつ半導体装置が提供される。論理回路を構成する前記TFTは、待機制御TFTのバックゲート電極を作製する工程で同時に作製されたバックゲート電極を有する。

【0017】

【発明の実施の形態】

【0018】

図3に、本発明における半導体装置の回路図を示す。

【0019】

図3(A)は論理回路と低電位電源線GNDとの電気的接続をNチャネル型の待機制御TFT310を用いて制御する構成の回路である。

【0020】

論理回路はCMOS回路、またはNチャネルTFTで構成される回路、またはPチャネルTFTで構成される回路である。

【0021】

SLb端子は、待機時にSLb端子の電位を低電位にして、非待機時(動作時)にSLb端子の電位を高電位にすることによって、論理回路と低電位電源線GNDの電気的接続・切断を制御する制御端子である。

【0022】

図3(A)において、待機制御TFT310のバックゲート電極にはしきい値制御端子302が電気的に接続されており、待機制御TFT310がOFFの時、待機制御TFT310のリーク電流が十分に低減されるような電位が与えられる。バックゲート電極については図2を用いて後述する。

【0023】

待機制御TFTにおいて、リーク電流が十分に低減されるような電位とは、NチャネルTFTの場合、TFTのしきい値電圧をプラス方向へシフトさせる電位であって、TFTのソース電位より低い電位である。より、具体的には図5を用いて後述する。

【0024】

しきい値制御端子301は論理回路を構成するTFTのバックゲート電極に電気的に接続しており、論理回路が高速で動作できるような電位が与えられる。

【0025】

論理回路を構成するTFTにおいて、高速で動作できるような電位とは、NチャネルTFTの場合、TFTのしきい値電圧をノーマリーオンにならない程度にマイナス方向へシフトさせ、0に近付ける電位であって、TFTのソース電位より高い電位である。しきい値電圧を0に近付けることによって、論理回路の立ち上がり・立ち下がり始めが早くなる。また、しきい値電圧をマイナス方向へシフトさせることによって、TFTのオン状態の電流を大きくすることが出来る。さらに高速で動作できるような電位とは、バックゲート電極の電位がソース電位と同じときにすでにしきい値電圧がマイナス方向へシフトしてノーマリーオンになっている場合には、しきい値電圧をプラス方向へシフトさせる電位のこともいう。より、具体的には図5を用いて後述する。

【0026】

バックゲート電極の電位はゲート電極の電位に合わせて変化させても良い。すなわち、例えばNチャネル型待機制御TFTの場合、ゲート電極の電位が低電位のとき、論理回路と低電位電源GNDを電気的に切断し、さらにバックゲート電極の電位をソース電位より低くして、前記Nチャネル型待機制御TFTのリーク電流を低減する。またNチャネル型待機制御TFTのゲート電極の電位が高電位のとき、論理回路と低電位電源GNDを電気的に接続し、さらにバックゲート電極の電位をソース電位より高くしてNチャネル型待機制御TFTのソース・ドレイン間抵抗値を低減することによって、動作時における擬似低電位電源線の電位変動を低減することが出来る。論理回路を構成するTFTにおいてはそれぞれのTFTのゲート電極とバックゲート電極を電気的に接続、あるいはそれぞれのTFTのゲート電極とバックゲート電極を同じ論理にすることによって、立ち上がり・立ち下がり時間を短くし、論理回路を構成するTFTのオン状態の電流を大きくする、あるいは論理回路を構成するTFTのサイズを縮小することができる。

【0027】

図3(B)は、論理回路と高電位電源線の電気的接続・切断をPチャネルTFT型の待機制御TFT311を用いて制御する回路である。

【0028】

SL端子は、待機時にSL端子の電位を高電位にして、動作時にSL端子の電位を低電位にすることによって、論理回路と高電位電源線Vddの電気的接続・切断を制御する制御端子である。

【0029】

図3(C)は、電源線(高電位電源線Vddおよび低電位電源線GND)と論理回路の電気的接続を制御する回路である。

【0030】

図5(A)は図2の構造におけるNチャネルTFTの、図5(B)はPチャネルTFTのゲート電圧‐ドレイン電流特性( Vgs−Ids曲線) の一例を示したものである。

【0031】

図5(A)において、501は、バックゲート電極に電圧を印加しないときのNチャネルTFT特性であり、この例ではNチャネルTFTはノーマリーオンとなっている。502・503はバックゲート電極にそれぞれ+2V、+5Vの正電圧を印加したときの、504・505はバックゲート電極にそれぞれ−2V、−5Vの負電圧を印加したときのNチャネルTFT特性を示している。つまり、バックゲート電極に正電圧を印加したとき、NチャネルTFTのしきい値は左( マイナス) 方向へとシフトし、負電圧を印加したとき右( プラス) 方向へとシフトしている。これらの曲線によると、バックゲート電極に正あるいは負の電圧を印加することによって、NチャネルTFTのしきい値電圧を変化させることができることが理解される。

【0032】

図5(B)において、511はバックゲート電極に電圧を印加しないときのPチャネルTFT特性である。514・515はバックゲート電極にそれぞれ+2V、+5Vの正電圧を印加したときの、512・513はバックゲート電極にそれぞれ−2V、−5Vの負電圧を印加したときのPチャネルTFT特性を示している。つまり、バックゲート電極に正電圧を印加したとき、PチャネルTFTのしきい値は左( マイナス) 方向へとシフトし、負電圧を印加したとき右( プラス) 方向へとシフトしている。これらの曲線によると、前述のNチャネルTFTの場合と同様に、バックゲート電極に正あるいは負の電圧を印加することによって、NチャネルTFTのしきい値電圧を変化させることができることが理解される。

【0033】

図5( A) および( B) では、バックゲート電圧を正電圧+2V、+5Vおよび負電圧−2V、−5Vのときのみについて特性を示したが、より詳細にバックゲート電圧を変化させて、同様のTFT特性( Vgs−Ids曲線) を測定したところでは、NチャネルTFTとPチャネルTFTそれぞれにおいて、バックゲート電圧を変化させたときのしきい値Vth変化は、図6でプロットしたような知見が得られている。図6( A) はNチャネルTFT、図6( B) はPチャネルTFTの特性を示したものである。NチャネルTFTおよびPチャネルTFTどちらの場合もバックゲート電圧に正電圧を印加するとしきい値はマイナス方向へとシフトし、負電圧を印加するとプラス方向へとシフトしている。

【0034】

よって、バックゲート電極に電圧を印加することで、NチャネルTFT、PチャネルTFTそれぞれについて、しきい値電圧を変化させることができるとわかった。本発明は、この現象を利用してTFTのしきい値電圧Vthを制御しようとするものである。

【0035】

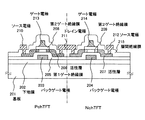

図2に、バックゲート電極を説明する本発明の半導体装置の断面構造を示す。図2には、本発明の半導体装置の代表例として、PチャネルTFT(PchTFT)とNチャネルTFT(NchTFT)とが示されている。

【0036】

図2において、201は基板であり、ガラス基板や石英基盤、あるいはプラスチック基板のような絶縁基板が用いられる。202は下地膜である。203および204はバックゲート電極である。205は第1ゲート絶縁膜である。206および207は半導体活性層(ポリシリコン島状領域)であり、ソース領域、ドレイン領域、低濃度不純物領域、およびチャネル形成領域から成る。バックゲート電極203は半導体活性層206と第1ゲート絶縁膜205を間に介して重なっている。バックゲート電極204は半導体活性層207と第1ゲート絶縁膜205を間に介して重なっている。208および209は第2ゲート絶縁膜である。210〜212はソース電極およびドレイン電極である。213および214はゲート電極である。ゲート電極213は半導体活性層206と第2ゲート絶縁膜208を間に介して重なっている。ゲート電極214は半導体活性層207と第2ゲート絶縁膜209を間に介して重なっている。215は層間絶縁膜である。バックゲート電極203および204には、任意の電位が印加できるように設計されている。

【0037】

バックゲート電極とは、TFTの構造がトップゲート型のときはボトム側すなわち基板側に、TFTの構造ボトムゲート型のときは、トップ側に対となる電極として形成され、互いのゲート電極はチャネル形成領域をはさみ込むように配置される電極である。本実施の形態ではトップゲート型TFT構造を示したが、ボトムゲート型でも良い。

【0038】

バックゲート電極は、半導体表示装置において、基板側からTFTへ照射される光に対する遮光膜としても用いることが出来る。

【0039】

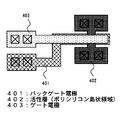

図4は、本発明におけるバックゲート電極を有した薄膜トランジスタ(TFT)を平面図として示したものである。

【0040】

図4において、バックゲート電極401は活性層(ポリシリコン島状領域)402上でゲート電極403よりわずかに大きく描いてあるが、ゲート電極403より小さくても、またゲート電極403と同じ大きさでも良い。また、バックゲート電極401はポリシリコン島状領域402全体を覆う大きさでも構わない。

【0041】

図示しないが、バックゲート電極401と活性層402、およびゲート電極403と活性層402は、それぞれ絶縁膜をはさむ。

【0042】

図4において、ゲート電極403とは反対側に形成されたバックゲート電極401に電圧を印加することで、このTFTのしきい値を制御しようとするものである。

【0043】

【実施例】

【0044】

(実施例1)

【0045】

本実施例では、本発明における半導体装置の例として、インバータを複数接続した回路と電源線との電気的接続を制御するTFT(待機制御TFT)とで構成した回路について説明する。

【0046】

図7(A)は、インバータ回路の電源線として、交互に、擬似低電位電源線704と高電位電源線706、低電位電源線703と擬似高電位電源線705、を電気的に接続した例である。

【0047】

図7(A)において、例えば待機時に常に図7(A)における入力端子の電位が低電位で、図7(A)における出力端子の電位が高電位になる場合、図7(A)に示した待機制御TFT720をOFFにすると、インバータ回路を構成するTFTのソース・ドレイン間抵抗値が十分に大きくなくても、図7(A)における第一のノード709と図7(A)における第二のノード710と図7(A)における出力端子は待機状態に入った時の各ノードの電位を保持できるので、待機時から動作時への復帰に使用する電力が低減される。

【0048】

第二のしきい値制御端子702の電位と第三のしきい値制御端子707の電位は、待機時にそれぞれNチャネル型の待機制御TFT720とPチャネル型の待機制御TFT721のリーク電流が小さくなるように電位を調整する。

【0049】

第一のしきい値制御端子701の電位と第四のしきい値制御端子708の電位は、論理回路(図7の場合、インバータ回路)が高速で動作できるように、電位を調整する。

【0050】

インバータ回路を構成するTFTのバックゲート電極は、NチャネルTFT同士またはPチャネルTFT同士を図7のように共通にせず、それぞれのゲート電極と接続しても良い。

【0051】

上記しきい値制御端子の電位は、外部電源回路、または抵抗分割回路、または公知のしきい値の自己補正回路、などによって与えることが出来る。

【0052】

図8(A)は主に図7におけるしきい値制御端子702の電位変化を表した図である。

【0053】

図7におけるしきい値制御端子702の電位変化は波形802乃至805のいずれでもよい。波形801は図7におけるSLb端子の電位変化を表す。

【0054】

波形802はしきい値制御端子702に一定の電位を与える場合であり、待機時に待機制御TFT720のリーク電流が十分小さくなるような電位に調整されている。

【0055】

波形803乃至805は非待機時(動作時)に、しきい値制御端子702の電位を上げることによって、待機制御TFT720に流れる電流を大きくして、擬似低電位電源線704をより安定させる。

【0056】

図8(B)は図7におけるしきい値制御端子701の電位変化を表した図である。

【0057】

波形810はしきい値制御端子701に一定の電位を与える場合であり、論理回路が高速で動作できるような電位に調整されている。

【0058】

波形811は論理回路を構成するそれぞれのTFTのゲート電極とバックゲート電極を電気的に接続した場合の一例である。TFTのゲート電極とバックゲート電極に同じ電圧を印加することで、実質的に半導体膜の膜厚を薄くしたのと同じように空乏層が早く広がるので、サブスレッショルド係数(S値)を小さくすることができ、さらに電界効果移動度を向上させることができる。したがって、電極が1つの場合に比べてオン電流を大きくすることができる。よって、この構造のTFTを論理回路に使用することにより、オン電流を大きくすることができるので、TFTのサイズを小さくすることができる。そのため集積密度を向上させることができる。

【0059】

図7(B)は、擬似低電位電源線704をインバータ回路の低電位電源とした例である。

【0060】

(実施例2)

【0061】

本実施例では本発明の半導体装置を用いた表示システムの例を説明する。

【0062】

図9は同一絶縁基板上に、アクティブマトリックス回路901と、信号線駆動回路902と、走査線駆動回路903と、信号制御回路906と、信号生成回路911と、待機制御回路920・921とを作成した例である。

【0063】

アクティブマトリックス回路901は、マトリクス状に配置された画素から構成される。本実施例においては、画素は複数のTFTから構成され、それぞれの画素ごとにメモリを持つ。画素ごとのメモリとしては、TFTでSRAMを構成しても良い。

【0064】

信号線駆動回路902は上記画素に映像信号を送る回路である。

【0065】

走査線駆動回路903は映像信号を書き込む画素を選択する回路である。

【0066】

信号制御回路906はタイミング信号制御回路904と映像信号制御回路905からなる。

【0067】

タイミング信号制御回路904は信号線駆動回路902と走査線駆動回路903を制御するためのクロックや同期信号を生成する。タイミング信号制御回路904は外部から入力される信号を加工したり、タイミング信号制御回路904内部で信号を発生したりする。

【0068】

映像信号制御回路905は外部から入力される映像信号に対して、D/A変換、γ補正回路、信号分割回路、圧縮された入力信号の伸長、などの処理を行う回路である。

【0069】

信号生成回路911はCPU907と、メモリ908と、入出力インターフェース回路909と、クロック生成回路910からなる。信号生成回路911は信号制御回路906へ映像信号や制御信号を送る。信号生成回路911はアクティブマトリックス回路901などと同一基板上に無くても良い。

【0070】

本実施例において、待機制御回路920、921は、待機信号(図7におけるSL、SLb信号に相当する信号)を生成する。また、待機制御回路920・921は、しきい値制御端子の電位(図7における第一乃至第四のしきい値制御端子701・702・707・708の電位)を供給する。待機制御TFT以外の論理回路を構成するTFTのしきい値制御端子の電位を与える回路は図示を省略する。本実施例において、待機制御回路920・921は、信号生成回路911の制御を受ける構成とする。

【0071】

本実施例において、待機制御回路920、921は、信号制御回路906を制御する第一の待機制御回路920と、信号線駆動回路902および走査線駆動回路903を制御する第二の待機制御回路921に分けてあるが、一つの待機制御回路で信号制御回路906と信号線駆動回路902と走査線駆動回路903を制御する構成としても良い。また、さらに細かく分けて、例えば信号制御回路906を複数の待機制御回路で制御する構成としても構わない。

【0072】

本実施例において、待機制御回路920、921は信号生成回路911からの制御信号によって、待機時と実行時のしきい値制御端子電位を変化させることができる。

【0073】

本実施例の構成により、待機時に、信号制御回路906と、信号線駆動回路902と、走査線駆動回路903の動作を止めても、アクティブマトリックス回路901は、映像信号をそれぞれの画素に設けたメモリで保持することによって、表示を続けることが出来る。また待機時に、信号制御回路906と、信号線駆動回路902と、走査線駆動回路903の消費電力を低減することが出来る。

【0074】

(実施例3)

【0075】

本発明の半導体表示装置を構成するTFTの作製工程について説明する。ここでは、同一基板上にNチャネルTFTとPチャネルTFTを作製する方法について説明する。

【0076】

図10は、TFTの作製工程を説明する断面図である。

【0077】

図10(A)において、基板1001は絶縁表面を有し、後の工程の処理温度に耐えうるものであれば、どのような材料の基板でも用いることが可能である。代表的には、ガラス基板、石英基板、セラミック基板などを用いることができる。また、シリコン基板、金属基板またはステンレス基板の表面に絶縁膜を形成したものを用いても良い。また、本実施例の処理温度に耐えうる耐熱性を有するプラスチック基板を用いてもよい。

【0078】

この基板1001の絶縁表面上に配線1002と第1の電極1003・1004を形成する。前記配線及び第1の電極はAl、W、Mo、Ti、Taから選ばれた一種又は複数種からなる導電性の材料で形成する。本実施例ではWを用いたが、TaNの上にWを積層したものを前記配線及び第1の電極として用いても良い。第1の電極1003・1004は、後述する半導体膜1008・1009を基板側から覆うことによって、基板側から本実施例で作成するTFTへ照射される光に対する遮光膜としても用いることが出来る。

【0079】

配線1002と第1の電極1003・1004を形成した後、第1の絶縁膜1005を形成する。本実施例では、第1の絶縁膜1005は、2つの絶縁膜(第1の絶縁膜A 1005a、第1の絶縁膜B 1005b)を積層することで形成されている。第1の絶縁膜A 1005aは酸窒化シリコン膜を用い、10〜50nmの厚さで形成する。第1の絶縁膜B 1005bは酸化シリコン膜又は酸窒化シリコン膜を用い、0.5〜1μmの厚さで形成する。

【0080】

第1の絶縁膜1005の表面は、先に形成した配線及び第1の電極に起因する凹凸を有している。好ましくは、この凹凸を平坦化することが望ましい。平坦化の手法としてはCMP(Chemical Mechanical Polish)を用いる。第1の絶縁膜1005に対するCMPの研磨剤(スラリー)には、例えば、塩化シリコンガスを熱分解して得られるフュームドシリカ粒子をKOH添加水溶液に分散したものを用いると良い。CMPにより第1の絶縁膜1005を0.1〜0.5μm程度除去して、表面を平坦化する。

【0081】

こうして、図10(B)に示すように平坦化された第1の絶縁膜1006が形成され、その上に半導体層を形成する。半導体層1007は結晶構造を有する半導体で形成する。これは、第1の絶縁膜1006上に形成した非晶質半導体層を結晶化して得る。非晶質半導体層は堆積した後、加熱処理やレーザー光の照射により結晶化させる。非晶質半導体層の材料に限定はないが、好ましくはシリコン又はシリコンゲルマニウム(SixGe1-x;0<x<1、代表的には、x=0.001〜0.05)合金などで形成する。

【0082】

その後、半導体層1007をエッチングにより島状に分割し、図10(C)に示すように半導体膜1008・1009を形成する。

【0083】

第1の電極1003は半導体膜1008と第1の絶縁膜1006を間に介して重なっている。また、第1の電極1004は半導体膜1009と第1の絶縁膜1006を間に介して重なっている。

【0084】

次いで、図10(D)に示すように、半導体膜1008・1009を覆う第2の絶縁膜1010を形成する。第2の絶縁膜1010は、プラズマCVD法やスパッタ法でシリコンを含む絶縁物で形成する。その厚さは40〜150nmとする。

【0085】

第2の絶縁膜1010上には第2の電極や第2の配線を形成するために導電膜を形成する。本発明において第2の電極は2層又はそれ以上の導電膜を積層して形成する。第2の絶縁膜1010上に形成する第1の導電膜1011はモリブデン、タングステンなどの高融点金属の窒化物で形成し、その上に形成する第2の導電膜1012は高融点金属又はアルミニウムや銅などの低抵抗金属、或いはポリシリコンなどで形成する。具体的には、第1の導電膜としてW、Mo、Ta、Tiから選ばれた一種又は複数種の窒化物を選択し、第2の導電膜としてW、Mo、Ta、Ti、Al、Cuから選ばれた一種又は複数種の合金、或いはn型多結晶シリコンを用いる。例えば、第1の導電膜1011をTaNで形成し、第2の導電膜1012をWで形成しても良い。また第2の電極や第2の配線を3層の導電膜で形成する場合、1層目をMo、2層目をAl、3層目をTiNとしても良い。また1層目をW、2層目をAl、3層目をTiNとしても良い。

【0086】

この第1の導電膜1011及び第2の導電膜1012を、マスク1013を用いてエッチングし、第2の配線及び第2の電極を形成する。

【0087】

図10(E)に示すように、第1のエッチング処理により、端部にテーパーを有する第1形状の電極1014・1015を形成する(第1の導電膜1014a・1015aと第2の導電膜1014b・1015bで成る)。第2の絶縁膜1016は、第1の形状の電極1014・1015で覆われない部分において、表面が20〜50nm程度エッチングされ薄くなった状態になっている。

【0088】

第1のドーピング処理は、イオン注入法または質量分離をしないでイオンを注入するイオンドープ法により行う。ドーピングは第1形状の電極1014・1015をマスクとして用い、半導体膜1008・1009に第1濃度の一導電型不純物領域1017・1018を形成する。第1濃度は1×1020〜1.5×1021/cm3とする。

【0089】

次に、レジストからなるマスクを除去せずに図10(F)に示すように第2のエッチング処理を行う。このエッチング処理では、第2の導電膜を異方性エッチングして第2の形状の電極1019・1020を形成する(第1の導電膜1019a・1020aと第2の導電膜1019b・1020bで成る)。第2の形状の電極1019・1020はこのエッチング処理により幅を縮小させ、その端部が第1濃度の一導電型不純物領域1017・1018(第2の不純物領域)の内側に位置するように形成する。次の工程で示すように、この後退幅によりLDDの長さを決める。第2の形状の電極1019・1020は第2の電極として機能する。

【0090】

この状態で一導電型の不純物を第2のドーピング処理を行い一導電型の不純物を半導体膜1008・1009に添加する。このドーピング処理で形成される第2濃度の一導電型不純物領域(第1の不純物領域1021・1022は、第2形状の電極1019・1020を構成する第1の導電膜1019a・1020aと一部が重なるように自己整合的に形成される。イオンドープ法で添加される不純物は、第1の導電膜1019a・1020aを通過させて添加するため、半導体膜に達するイオンの数は減少し、必然的に低濃度となる。その濃度は1×1017〜1×1019/cm3となる。

【0091】

次いで、図10(G)で示すように、レジストからなるマスク1023を形成し第3のドーピング処理を行う。この第3のドーピング処理により、半導体膜1009に第3濃度の一導電型とは反対の導電型の不純物領域1024を形成する。第3濃度の一導電型とは反対の導電型の不純物領域は第2形状の電極1020と重なる領域に形成されるものであり、1.5×1020〜5×1021/cm3の濃度範囲で当該不純物元素が添加される。

【0092】

以上までの工程でそれぞれの半導体膜に価電子制御を目的とした不純物を添加した領域が形成される。第1の電極1003・1004と、第2の形状の電極1019・1020は半導体膜と交差する位置においてバックゲート電極とゲート電極として機能する。

【0093】

その後、それぞれの半導体膜に添加された不純物元素を活性化処理する工程を行う。この活性化はガス加熱型の瞬間熱アニール法を用いて行う。加熱処理の温度は窒素雰囲気中で400〜700℃、代表的には450〜500℃で行う。この他に、YAGレーザーの第2高調波(532nm)を用いたレーザーアニール法を適用することもできる。レーザー光の照射により活性化を行うには、YAGレーザーの第2高調波(532nm)を用いこの光を半導体膜に照射する。勿論、レーザー光に限らずランプ光源を用いるRTA法でも同様であり、基板の両面又は片面からランプ光源の輻射により半導体膜を加熱する。

【0094】

その後、図10(H)に示すように、プラズマCVD法で窒化シリコンから成るパッシベーション膜1025を50〜100nmの厚さに形成し、クリーンオーブンを用いて410℃の熱処理を行い、窒化シリコン膜から放出される水素で半導体膜の水素化を行う。

【0095】

次いで、パッシベーション膜1025上に有機絶縁物材料から成る第3の絶縁膜1026を形成する。有機絶縁物材料を用いる理由は第3の絶縁膜1026の表面を平坦化するためのものである。より完全な平坦面を得るためには、この表面をCMP法により平坦化処理することが望ましい。CMP法を併用する場合には、第3の絶縁膜をプラズマCVD法で形成される酸化シリコン膜、塗布法で形成されるSOG(Spin on Glass)やPSGなどを用いることもできる。なお、パッシベーション膜1025は第3の絶縁膜1026の一部とみなしても良い。

【0096】

表示装置を同一基板上に作成する場合、図示しないが、第3の絶縁膜1026の表面に酸化インジウム・スズを主成分とする透明導電膜を60〜120nmの厚さで形成し、エッチング処理して画素電極を形成する。

【0097】

その後、図10(I)に示すように、第2の絶縁膜1010、パッシベーション膜1025、第3の絶縁膜1026にコンタクトホールを形成し、配線1027〜1029を形成する。この配線はチタン膜とアルミニウム膜を積層して形成する。

【0098】

以上までの工程において、一導電型不純物領域をn型、一導電型とは反対の不純物領域をp型とすると、同一基板上に、NチャネルTFT1030とPチャネルTFT1031が形成される。

【0099】

NチャネルTFT1030の一対のゲート電極1019、1003はチャネル形成領域1032を間に介して重なっている。第2濃度の一導電型の不純物領域1021はLDDとして、第1濃度の一導電型の不純物領域1017はソース又はドレイン領域として機能する。PチャネルTFT1031の一対のゲート電極1020、1004はチャネル形成領域1033を間に介して重なっている。第3濃度の一導電型とは反対の不純物領域1024はソース又はドレイン領域として機能する。

【0100】

LDDのチャネル長方向の長さは0.5〜2.5μm、好ましくは1.5μmで形成する。このようなLDDの構成は、主にホットキャリア効果によるTFTの劣化を防ぐことを目的としている。これらNチャネルTFT及びPチャネルTFTによりシフトレジスタ回路、バッファ回路、レベルシフタ回路、ラッチ回路などを形成することができる。特に、駆動電圧が高いバッファ回路には、ホットキャリア効果による劣化を防ぐ目的から、LDDを有するTFTの構造が適している。

【0101】

上記の工程によって作製された半導体装置をもとに、公知の液晶のセル組み工程によって、アクティブマトリクス型液晶表示装置を作製することが出来る。

【0102】

また上記の工程によって作製された半導体装置をもとに、公知の発光素子(EL:エレクトロ・ルミネッセンス)のセル組み工程によって、アクティブマトリクス型EL表示装置を作製することが出来る。さらにその他の表示装置にも適用できる。

【0103】

(実施例4)

【0104】

本実施例では、本発明の半導体装置が有するTFTの半導体活性層を作製する上で、半導体膜を結晶化する手法の例を示す。

【0105】

半導体活性層になる半導体膜は、絶縁膜上にプラズマCVD法により非晶質珪素膜150nmを形成する。そして、500℃で3時間の熱処理を行って、半導体膜が含有する水素を放出させた後、レーザアニール法により半導体膜の結晶化を行う。

【0106】

レーザアニ-ル法に用いるレーザとしては、連続発振のYVO4レーザを用いる。レーザアニール法の条件は、レーザ光としてYVO4レーザの第2高調波(波長532nm)を用いることができる。レーザ光を光学系により所定の形状のビームとして、基板表面上に形成した半導体膜の照射する。

【0107】

なお、基板上に照射されるビームの形状は、レーザの種類や、光学系によって変化させることができる。こうして、基板上に照射されるビームのアスペクト比やエネルギー密度の分布を変えることができる。例えば、基板上に照射されるビームの形状は、線状、矩形状、楕円状など、様々な形状とすることができる。

【0108】

本実施例では、YVO4レーザの第2高調波を、光学系によって200μm×50μmの楕円状にし、半導体膜に照射する。

【0109】

ここで、レーザ光を基板表面上に形成した半導体膜に照射する際に用いる、光学系の模式図を図11に示す。

【0110】

レーザ1101から射出されたレーザ光(YVO4レーザの第2高調波)は、ミラー1102を経由して、凸レンズ1103に入射する。レーザ光は凸レンズ1103に対して斜めに入射させる。このようにすることで、非点収差などの収差により焦点位置がずれ、照射面またはその近傍において楕円状ビーム1106を形成することができる。

【0111】

そして、このようにして形成される楕円状ビーム1106を照射しながら、例えば1107で示す方向または1108で示す方向にガラス基板1105を移動させる。こうして、ガラス基板1105上に形成された半導体膜1104において、楕円状ビーム1106を相対的に移動させながら照射する。

【0112】

なお、楕円状ビーム1106の相対的な走査方向は、楕円状ビーム1106の長軸に垂直な方向とした。

【0113】

本実施例では、凸レンズ1103に対するレーザ光の入射角φを約20°として200μm×50μmの楕円状ビームを形成し、ガラス基板1105を50cm/secの速度で移動させながら照射して、半導体膜の結晶化を行う。

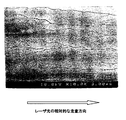

【0114】

このようにして得られた結晶性半導体膜にセコエッチングを行って、SEMにより1万倍にて表面を観察した結果を図12に示す。なお、セコエッチングにおけるセコ液はHF:H2O=2:1に添加剤としてK2Cr2O7を用いて作製されるものである。図12は、図中の矢印で示す方向にレーザ光を相対的に走査させて得られたものである。レーザ光の走査方向に平行に大粒径の結晶粒が形成されている様子がわかる。つまり、レーザ光の走査方向に対して延在するように結晶成長がなされる。

【0115】

このように、本実施例の手法を用いて結晶化を行った半導体膜には大粒径の結晶粒が形成されている。そのため、前記半導体膜を半導体活性層として用いてTFTを作製すると、前記TFTのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。また、個々の結晶粒の内部は実質的に単結晶と見なせる結晶性を有することから、単結晶半導体を用いたトランジスタと同等の高いモビリティ(電界効果移動度)を得ることも可能である。このような優れた特性のTFTを用いることで、実施例2のような付加価値のある表示システムを作製することができる。

【0116】

さらに、TFTを、そのキャリアの移動方向が、形成された結晶粒の延在する方向と揃うように配置すれば、キャリアが結晶粒界を横切る回数を極端に減らすことができる。そのため、オン電流値(TFTがオン(ON)状態にある時にソース・ドレイン間に流れるドレイン電流値)、オフ電流値(TFTがオフ(OFF)状態にある時に流れるドレイン電流値(リーク電流))、しきい値電圧、S値及び電界効果移動度のバラツキを低減することも可能となり、電気的特性は著しく向上する。

【0117】

なお、半導体膜の広い範囲に楕円状ビーム1106を照射するため、楕円状ビーム1106をその長軸に垂直な方向に走査して半導体膜に照射する動作(以下、スキャンと表記する)を、複数回行っている。ここで、1回のスキャン毎に、楕円状ビーム1106の位置は、その長軸に平行な方向にずらされる。また、連続するスキャン間では、その走査方向を逆にする。ここで、連続する2回のスキャンにおいて、一方を往路のスキャン、もう一方を復路のスキャンと呼ぶことにする。

【0118】

楕円状ビーム1106の位置を、1回のスキャン毎にその長軸に平行な方向にずらす大きさを、ピッチdと表現する。また、往路のスキャンにおいて、図12に示したような大粒径の結晶粒が形成された領域の、楕円状ビーム1106の走査方向に垂直な方向の長さを、D1と表記する。復路のスキャンにおいて、図12に示したような大粒径の結晶粒が形成された領域の、楕円状ビーム1106の走査方向に垂直な方向の長さを、D2と表記する。また、D1とD2の平均値を、Dとする。

【0119】

このとき、オーバーラップ率RO.L[%]を式1で定義する。

【0120】

【式1】

RO.L=(1−d/D)×100

【0121】

本実施例では、オーバーラップ率RO.Lを0[%]とした。

【0122】

(実施例5)

【0123】

本実施例では、本発明の半導体装置が有するTFTの半導体活性層を作製する上で、半導体膜を結晶化する手法において、実施例4とは異なる例を示す。

【0124】

半導体膜として非晶質珪素膜を形成するまでの工程は、実施例4と同様である。その後、特開平7−183540号公報に記載された方法を利用し、前記半導体膜上にスピンコート法にて酢酸ニッケル水溶液(重量換算濃度5ppm、体積10ml)を塗布し、500℃の窒素雰囲気で1時間、550℃の窒素雰囲気で12時間の熱処理を行う。続いて、レーザアニール法により、半導体膜の結晶性の向上を行う。

【0125】

レーザアニ-ル法に用いるレーザとしては、連続発振のYVO4レーザを用いる。レーザアニール法の条件は、レーザ光としてYVO4レーザの第2高調波(波長532nm)を用い、図11で示した光学系における凸レンズ1103に対するレーザ光の入射角φを約20°として、200μm×50μmの楕円状ビームを形成する。ガラス基板1105を50cm/secの速度で移動させながら、前記楕円状ビームを照射して、半導体膜の結晶性の向上を行う。

【0126】

なお、楕円状ビーム1106の相対的な走査方向は、楕円状ビーム1106の長軸に垂直な方向とした。

【0127】

このようにして得られた結晶性半導体膜にセコエッチングを行って、SEMにより1万倍にて表面を観察した。その結果を図13に示す。図13は、図中の矢印で示す方向にレーザ光を相対的に走査させて得られたものであり、走査方向に対して延在して大粒径の結晶粒が形成されている様子がわかる。

【0128】

このように、本発明を用いて結晶化を行った半導体膜には大粒径の結晶粒が形成されているため、前記半導体膜を用いてTFTを作製すると、そのチャネル形成領域に含まれる結晶粒界の本数を少なくすることができる。また、個々の結晶粒は実質的に単結晶と見なせる結晶性を有することから、単結晶半導体を用いたトランジスタと同等の高いモビリティ(電界効果移動度)を得ることも可能である。このような優れた特性のTFTを用いることで、実施例2のような付加価値のある表示システムを作製することができる。

【0129】

さらに、形成された結晶粒が一方向に揃っている。そのため、TFTを、そのキャリアの移動方向が、形成された結晶粒の延在する方向と揃うように配置すれば、キャリアが結晶粒界を横切る回数を極端に減らすことができる。そのため、オン電流値、オフ電流値、しきい値電圧、S値及び電界効果移動度のバラツキを低減することも可能となり、電気的特性は著しく向上する。

【0130】

なお、本実施例では、式1で定義されるオーバーラップ率RO.Lを0[%]とした。

【0131】

また、上記結晶化の手法によって得られた半導体膜(図中、Improved CG−Siliconと表記)のラマン散乱分光の結果を図14に太線で示す。ここで、比較のため、単結晶シリコン(図中、ref.(100)Si Waferと表記)のラマン散乱分光の結果を細線で示した。また、非晶質珪素膜を形成後、熱処理を行って半導体膜が含有する水素を放出させた後、パルス発振のエキシマレーザを用い結晶化を行った半導体膜(図中、excimer laser annealingと表記)のラマン散乱分光の結果を図14に点線で示した。

【0132】

本実施例の手法によって得られた半導体膜のラマンシフトは、517.3cm-1のピークを有する。また、半値幅は、4.96cm-1である。一方、単結晶シリコンのラマンシフトは、520.7cm-1のピークを有する。また、半値幅は、4.44cm-1である。パルス発振のエキシマレーザを用い結晶化を行った半導体膜のラマンシフトは、516.3cm-1である。また、半値幅は、6.16cm-1である。

【0133】

図14の結果により、本実施例に示した結晶化の手法によって得られた半導体膜の結晶性が、パルス発振のエキシマレーザを用い結晶化を行った半導体膜の結晶性と比べて、単結晶シリコンに近いことがわかる。

【0134】

(実施例6)

【0135】

本発明を用いた電子機器として、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオ、オーディオコンポ等)、ノート型パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を図15に示す。

【0136】

図15(A)は表示装置であり、筐体1501、支持台1502、表示部1503を含む。本発明は表示部1503を有する表示装置に適用が可能である。

【0137】

図15(B)はビデオカメラであり、本体1511、表示部1512、音声入力1513、操作スイッチ1514、バッテリー1515、受像部1516などによって構成されている。本発明は表示部1512を有する表示装置に適用が可能である。

【0138】

図15(C)はノート型のパーソナルコンピュータであり、本体1521、筐体1522、表示部1523、キーボード1524などによって構成されている。本発明は表示部1523を有する表示装置に適用が可能である。

【0139】

図15(D)は携帯情報端末であり、本体1531、スタイラス1532、表示部1533、操作ボタン1534、外部インターフェイス1535などによって構成されている。本発明は表示部1533を有する表示装置に適用が可能である。

【0140】

図15(E)は音響再生装置、具体的には車載用のオーディオ装置であり、本体1541、表示部1542、操作スイッチ1543、1544などによって構成されている。本発明は表示部1542を有する表示装置に適用が可能である。また、今回は車載用オーディオ装置を例に上げたが、携帯型もしくは家庭用オーディオ装置に用いてもよい。

【0141】

図15(F)はデジタルカメラであり、本体1551、表示部(A)1552、接眼部1553、操作スイッチ1554、表示部(B)1555、バッテリー1556などによって構成されている。本発明は表示部(A)1552および表示部(B)1555を有する表示装置に適用が可能である。

【0142】

図15(G)は携帯電話であり、本体1561、音声出力部1562、音声入力部1563、表示部1564、操作スイッチ1565、アンテナ1566などによって構成されている。本発明は表示部1564を有する表示装置に適用が可能である。

【0143】

これらの電子機器に使われる表示装置はガラス基板だけでなく耐熱性のプラスチック基板を用いることもできる。それによってよりいっそうの軽量化を図ることができる。

【0144】

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

【0145】

本実施例は、実施の形態及び実施例1乃至実施例5と自由に組み合わせて実施することが可能である。

【0146】

【発明の効果】

【0147】

本発明のバックゲート電極を有するTFTによって構成される半導体装置によると、論理回路と電源線の接続・切断を制御するTFTのリーク電流を、バックゲート電極の電位によって低減することが出来、待機時の消費電力を低減することが出来る。

【0148】

本発明のバックゲート電極を有するTFTによって構成される半導体装置によると、論理回路と電源線の接続・切断を制御する待機制御TFTのON状態のソース・ドレイン間電流を向上させるようにしきい値制御電極の電位を制御出来るので、動作時の擬似電源線の電位変動をていげんすることが出来る。または前記待機制御TFTのサイズを縮小できる。

【0149】

上記待機制御TFTと同じ作製工程によって作製された別のTFTが構成する論理回路の動作周波数は、バックゲート電極の電位によって向上させることが出来る。また論理回路を構成するTFTのリーク電流を低減することが出来る。

【0150】

上記待機時の消費電力を低減する回路と上記動作周波数を向上させた論理回路によって、同一絶縁基板上に、より高い付加価値のあるアクティブマトリックス型半導体装置を作ることが出来る。

【0151】

透明絶縁基板上のアクティブマトリックス型半導体表示装置において、バックゲート電極は遮光膜としても利用することが出来るので、製造プロセスを増やさずに本発明を実施することが出来る。

【図面の簡単な説明】

【図1】 従来の半導体装置のブロック・回路図である。

【図2】 本発明の半導体装置の断面構造である。

【図3】 本発明の半導体装置のブロック・回路図である。

【図4】 本発明に使用するTFTの平面図である。

【図5】 本発明を説明したTFTのVgs−Ids特性図である。

【図6】 本発明においてバックゲート電圧を変化させたときのしきい値電圧の変化を示した図である。

【図7】 本発明の半導体装置の例として、複数段インバータ回路の回路図である。

【図8】 図7におけるのしきい値制御端子の電位変化の例を表した図である。

【図9】 本発明の半導体装置の例として、信号制御回路を備えたアクティブマトリックス型半導体表示装置のブロック図である。

【図10】 TFTの作製工程を説明する断面図である。

【図11】 半導体膜に照射するレーザ光の光学系の模式図である。

【図12】 実施例4による結晶性半導体膜のSEM写真である。

【図13】 実施例5による結晶性半導体膜のSEM写真である。

【図14】 実施例5における結晶性半導体膜のラマン散乱分光のグラフである。

【図15】 本発明の半導体装置および半導体表示装置をもちいた半導体機器の一例を示す図である。

Claims (5)

- 透明絶縁基板上に形成された論理回路と、薄膜トランジスタとを有し、

前記薄膜トランジスタは前記論理回路と電源との接続を制御しており、

前記薄膜トランジスタは、第1のゲート電極と、前記第1のゲート電極上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された半導体膜と、前記半導体膜上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2のゲート電極とを有し、

前記第1のゲート電極と前記第2のゲート電極は、前記半導体膜を間に挟んで重なり合い、且つ前記第1のゲート電極は前記半導体膜全体を覆って遮光することを特徴とする半導体装置。 - 透明絶縁基板上に形成された論理回路と、第1の薄膜トランジスタとを有し、

前記論理回路は第2の薄膜トランジスタを有し、

前記第1の薄膜トランジスタは前記論理回路と電源との接続を制御しており、

前記第1及び第2の薄膜トランジスタは、第1のゲート電極と、前記第1のゲート電極上に形成された第1のゲート絶縁膜と、前記第1のゲート絶縁膜上に形成された半導体膜と、前記半導体膜上に形成された第2のゲート絶縁膜と、前記第2のゲート絶縁膜上に形成された第2のゲート電極とをそれぞれ有し、

前記第1のゲート電極と前記第2のゲート電極は、前記半導体膜を間に挟んで重なり合い、且つ前記第1のゲート電極は前記半導体膜全体を覆って遮光することを特徴とする半導体装置。 - 請求項2において、前記第1の薄膜トランジスタの第1のゲート電極と、前記第2の薄膜トランジスタの第1のゲート電極とをそれぞれ独立に制御する構造を特徴とする半導体装置。

- 請求項1乃至請求項3のいずれか一項において、前記半導体膜は結晶性を有し、結晶粒の延在する方向がキャリアの移動方向と揃い、チャネル形成領域、ソース領域、ドレイン領域およびLDD領域を有し、

前記LDD領域と前記第2のゲート電極の一部は重なっていることを特徴とする半導体装置。 - 請求項4において、前記半導体膜はシリコンから形成され、ラマンシフトは517.3cm-1 のピークを有し、半値幅は4.96cm-1以下であることを特徴とする半導体装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001368010A JP4201239B2 (ja) | 2001-11-30 | 2001-11-30 | 半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001368010A JP4201239B2 (ja) | 2001-11-30 | 2001-11-30 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003168803A JP2003168803A (ja) | 2003-06-13 |

| JP2003168803A5 JP2003168803A5 (ja) | 2005-07-07 |

| JP4201239B2 true JP4201239B2 (ja) | 2008-12-24 |

Family

ID=19177665

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001368010A Expired - Fee Related JP4201239B2 (ja) | 2001-11-30 | 2001-11-30 | 半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4201239B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100666552B1 (ko) | 2004-06-30 | 2007-01-09 | 삼성에스디아이 주식회사 | 반도체 소자의 제조 방법 및 이 방법에 의하여 제조되는반도체 소자 |

| KR100666563B1 (ko) | 2004-07-05 | 2007-01-09 | 삼성에스디아이 주식회사 | 반도체 장치의 제조 방법 및 이 방법에 의하여 제조되는반도체 장치 |

| JP5054919B2 (ja) * | 2005-12-20 | 2012-10-24 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| FR2932005B1 (fr) * | 2008-06-02 | 2011-04-01 | Commissariat Energie Atomique | Circuit a transistor integres dans trois dimensions et ayant une tension de seuil vt ajustable dynamiquement |

| US20180061763A1 (en) * | 2016-08-24 | 2018-03-01 | Qualcomm Switch Corp. | Device performance improvement using backside metallization in a layer transfer process |

-

2001

- 2001-11-30 JP JP2001368010A patent/JP4201239B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003168803A (ja) | 2003-06-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4275336B2 (ja) | 半導体装置の作製方法 | |

| JP5298094B2 (ja) | 半導体装置及びその作製方法 | |

| JP4386978B2 (ja) | 半導体装置の作製方法 | |

| KR20010020826A (ko) | 반도체 장치 및 그의 제조방법 | |

| JP4376331B2 (ja) | 半導体装置の作製方法 | |

| JP2011061227A (ja) | 半導体装置 | |

| JP4338937B2 (ja) | 半導体装置 | |

| JP4159633B2 (ja) | 半導体装置およびその作製方法並びに電子機器 | |

| JP4578618B2 (ja) | 半導体装置及びその作製方法 | |

| JP4201239B2 (ja) | 半導体装置 | |

| JP4275720B2 (ja) | 半導体装置及びその作製方法 | |

| JP4450900B2 (ja) | 半導体装置の作製方法 | |

| JP4850763B2 (ja) | 半導体装置の作製方法 | |

| JP2001210832A (ja) | 半導体装置及びその作製方法 | |

| JP5427482B2 (ja) | マイクロプロセッサ | |

| JP4656685B2 (ja) | 半導体装置 | |

| JP4044176B2 (ja) | 半導体装置 | |

| JP3998888B2 (ja) | 薄膜トランジスタの作製方法 | |

| JP2000114173A (ja) | 半導体装置の作製方法 | |

| JP3923141B2 (ja) | 半導体装置およびその作製方法 | |

| JP4641586B2 (ja) | 半導体装置の作製方法 | |

| JP4514862B2 (ja) | 半導体装置の作製方法 | |

| JP4256087B2 (ja) | 半導体装置の作製方法 | |

| JP4801520B2 (ja) | 半導体装置およびその作製方法 | |

| JP2000114172A (ja) | 半導体装置の作製方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041104 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041104 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080304 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20080313 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080407 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20080729 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080821 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20081003 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20081003 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111017 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121017 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121017 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131017 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |