JP4100646B2 - 薄膜トランジスタおよびそれを備えた液晶表示装置 - Google Patents

薄膜トランジスタおよびそれを備えた液晶表示装置 Download PDFInfo

- Publication number

- JP4100646B2 JP4100646B2 JP37218298A JP37218298A JP4100646B2 JP 4100646 B2 JP4100646 B2 JP 4100646B2 JP 37218298 A JP37218298 A JP 37218298A JP 37218298 A JP37218298 A JP 37218298A JP 4100646 B2 JP4100646 B2 JP 4100646B2

- Authority

- JP

- Japan

- Prior art keywords

- electrode

- semiconductor active

- gate electrode

- active film

- thin film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 239000010409 thin film Substances 0.000 title claims description 207

- 239000004973 liquid crystal related substance Substances 0.000 title claims description 74

- 239000010408 film Substances 0.000 claims description 295

- 239000004065 semiconductor Substances 0.000 claims description 254

- 239000000758 substrate Substances 0.000 claims description 60

- 239000011159 matrix material Substances 0.000 claims description 4

- 230000000694 effects Effects 0.000 description 15

- 229910021417 amorphous silicon Inorganic materials 0.000 description 12

- 238000009413 insulation Methods 0.000 description 10

- 230000007423 decrease Effects 0.000 description 7

- 230000005684 electric field Effects 0.000 description 4

- 238000002161 passivation Methods 0.000 description 4

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229910052698 phosphorus Inorganic materials 0.000 description 3

- 239000011574 phosphorus Substances 0.000 description 3

- 230000001681 protective effect Effects 0.000 description 3

- 239000003990 capacitor Substances 0.000 description 2

- 239000000969 carrier Substances 0.000 description 2

- 230000000052 comparative effect Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 230000002093 peripheral effect Effects 0.000 description 2

- 229910004205 SiNX Inorganic materials 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 230000001151 other effect Effects 0.000 description 1

Images

Landscapes

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

Description

【発明の属する技術分野】

本発明は好ましくは液晶表示装置などに適用される薄膜トランジスタとそれを備えた液晶表示装置に関し、特に半導体能動膜とソース電極とドレイン電極を特別な形状とした構造に関する。

【0002】

【従来の技術】

図24は、従来の一般的な薄膜トランジスタ型液晶表示装置において、逆スタガ型の薄膜トランジスタ、ゲート配線、ソース配線等を備えた薄膜トランジスタアレイ基板の一構造例を示す平面図、図25は図24に示す薄膜トランジスタの部分断面図、図26は同薄膜トランジスタの要部拡大平面図である。

この例の薄膜トランジスタアレイ基板では、ガラス等からなる透明基板99上に、ゲート配線Gとソース配線Sがマトリクス状に配設されている。そして、ゲート配線Gとソース配線Sとで囲まれた領域が1つの画素とされ、この画素領域毎に画素電極100が設けられている。

【0003】

この例の薄膜トランジスタアレイ基板において、透明基板上の各画素領域にゲート配線Gから引き出された平面視矩形状のゲート電極101が形成され、これらのゲート配線Gとゲート電極101を覆うようにゲート絶縁膜102が形成され、ゲート電極101上のゲート絶縁膜102上にアモルファスシリコン(a-Si)等からなるアイランド状の半導体能動膜103が設けられている。そして、リン等のn型不純物を含むアモルファスシリコン(a-Si:n+)からなるオーミックコンタクト層104を介して半導体能動膜103の一側端部上にソース電極105が形成され、半導体能動膜103の他端部上に同様のオーミックコンタクト層104を介してドレイン電極106が形成され、ソース電極105がソース配線Sに接続されるとともに、ドレイン電極106が保護絶縁膜107のコンタクトホール108を介して画素電極100に接続されて薄膜トランジスタTが構成されている。

【0004】

【発明が解決しようとする課題】

この種の薄膜トランジスタアレイ基板を用いる液晶表示装置にあっては、近年画面サイズが大型化されてきているので、大型化に対応して画素領域も大きく形成されるようになってきている。従って、画素電極100の作動に必要な電流値(Ion current:オン電流)も大きくなってきている。

【0005】

この要求に対応するためには、薄膜トランジスタTの半導体能動膜103における電流通路となるチャネル部の幅を広くする必要があると考えられる。チャネル部とは、ソース電極先端部とドレイン電極先端部との間の部分に位置する半導体能動膜103に対してゲート電極101が発生させる電界によって生じる電流通路のことであり、前述の画素電極100の作動に必要な電流値を上昇させるためには、このチャネル部の幅を広げることにより対応することができる。

【0006】

しかしながら図24ないし図26に示す構造の薄膜トランジスタTであると、ソース電極先端部とドレイン電極先端部の幅W1(図26を参照)を大きくすると、必然的に半導体能動膜103の幅W2も大きくなり、ゲート電極101の端部から側方にはみ出す半導体能動膜103の端部103a部分の面積が大きくなり、液晶表示装置に通常備えられているバックライトの光を受ける半導体能動膜103の端部103a部分の面積が大きくなるために、薄膜トランジスタTの光電流によるオフ時の電流(I off current )が大きくなる問題があった。

このように薄膜トランジスタTの光電流によるオフ電流が増大すると、液晶駆動時の画素電極100の電圧保持のために蓄積容量を大きくしなくてはならず、蓄積容量増大のために画素電極周りに補助的な蓄積容量形成用の電極(一般的にCsと称される)を配する必要などが生じ、別途電極を設ける構造を採用する結果として液晶表示装置の開口率が低下する問題を有していた。

【0007】

また、前記バックライトからの光電流の影響を無くするために、遮光性のゲート電極101上にのみ半導体能動膜103を配置する構成とすることも考えられるが、図26に示す構造にこのような構造を採用するとゲート電極101とソース電極105との間、あるいはゲート電極101とドレイン電極106との間の絶縁耐圧が低下し易い問題があった。

【0008】

本発明は前記事情に鑑みてなされたもので、本発明は、オン電流が大きくなっても、オフ電流の増加を抑制して液晶表示装置に応用した場合の開口率の低下を防止し、コントラストを高めることができる薄膜トランジスタの提供を目的とする。更に本発明は、ゲート電極とソース電極との間の部分の絶縁性並びにゲート電極とドレイン電極との間の部分の絶縁耐性の低下を生じることなくオン電流の増加とオフ電流の低下をなすことができる薄膜トランジスタとそれを備えた液晶表示装置の提供を目的とする。

【0009】

【課題を解決するための手段】

本発明は、ゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が設けられ、前記ゲート電極の両側から延びて前記半導体能動膜上にソース電極とドレイン電極とが間隔をあけて対峙して設けられ、対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極に乗り上げた部分の前記ソース電極の幅および前記ゲート電極に乗り上げた部分の前記ドレイン電極の幅よりも、該幅方向の前記チャネル部の幅が大きくされてなることを特徴とする。

ゲート電極に乗り上げた部分のソース電極幅、および、ドレイン電極の幅よりも、該幅方向のチャネル部の幅を大きく形成し、半導体能動膜に生成される導電パスとしてのチャネル部を広くし、薄膜トランジスタとしてのオン電流を大きくする。

【0010】

本発明は前記構造の薄膜トランジスタにおいて、チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されたことを特徴とする。

この構造によってオフ電流を低減することができる。また、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0011】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切りかつゲート電極上で折れ曲がって前記横切り方向とは異なった方向にゲート電極を横切った形状に形成され、ソース電極が前記半導体能動膜上であって半導体能動膜の前記2つの横切り部分の一方の部分からゲート電極上に伸びて形成され、前記半導体能動膜上であって半導体能動膜の前記2つの横切り部分の他方の部分からゲート電極上に延びかつ前記ソース電極と対峙させてドレイン電極が形成され、対峙する前記ソース電極と前記ドレイン電極との部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極を横切った半導体能動膜の幅よりも前記横切り方向の前記チャネル部の幅が大きくされてなることを特徴とする。

この構造においてソース電極とドレイン電極との間の部分に位置する半導体能動膜にチャネル部が生成されるが、ゲート電極を横切った部分のソース電極の幅およびドレイン電極の幅よりもチャネル部の幅が大きくされるので、チャネル部の幅が従来構造よりも大きくされたことになり、半導体能動膜に生成される導電パスとしてのチャネル部が広くなり、薄膜トランジスタとしてのオン電流が大きくなる。また、ゲート電極を横切った半導体能動膜の幅よりも前記横切り方向のチャネル部の幅が大きくされてなることから、ゲート電極を横切った部分の半導体能動膜の幅が小さくなり、ゲート電極から側方にはみ出す部分の半導体能動膜の面積が小さくなる結果としてオフ電流の上昇が抑制される。

【0012】

本発明は前記構造の薄膜トランジスタにおいて、チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されたことを特徴とする。

この構造によってオフ電流を更に低減することができる。また、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0013】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切りかつゲート電極上で膨出部を持った形状に形成され、ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の短冊方向に延びる形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の延びる方向に延びた形状に前記ソース電極と対峙させてドレイン電極が形成され、対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極を横切った半導体能動膜部分の幅よりも前記ゲート電極の延びる方向の前記チャネル部の幅が大きくされてなることを特徴とする。

この構造においてソース電極とドレイン電極との間の部分に位置する半導体能動膜にチャネル部が生成されるが、ゲート電極を横切った部分のソース電極の幅およびドレイン電極の幅よりもチャネル部の幅を大きくすることにより、薄膜トランジスタとしてのオン電流を大きくさせる。また、ゲート電極を横切った半導体能動膜の幅よりもゲート電極の延びる方向のチャネル部の幅が大きくされてなることから、ゲート電極を横切った部分の半導体能動膜の幅が小さくなり、ゲート電極から側方にはみ出す部分の半導体能動膜の面積が小さくなる結果としてオフ電流の上昇が抑制される。

【0014】

更に本発明は前記構造の薄膜トランジスタにおいて、チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されたことを特徴とする。

この構造によってオフ電流を更に低減することができる。また、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0015】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切りかつゲート電極上で膨出部を持った形状に形成され、ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の短冊方向に折れ曲がりさらに前記横切り方向に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の短冊方向の折れ曲がり部分及び前記横切り方向に延びた部分に間隙をあけて進入した形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極を横切った半導体能動膜部分の長さよりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする。

この構造においてソース電極とドレイン電極との間の部分に位置する半導体能動膜にチャネル部が生成されるが、ゲート電極を横切った部分のソース電極の幅およびドレイン電極の幅よりもチャネル部の幅が大きくされるので、チャネル部の幅が従来構造よりも大きくされたことになり、半導体能動膜に生成される導電パスとしてのチャネル部が広くなり、薄膜トランジスタとしてのオン電流を大きくできる。また、ゲート電極を横切った半導体能動膜の幅よりもソース電極のドレイン電極と対峙する辺の長さが長くされてなることから、ゲート電極を横切った部分の半導体能動膜の幅が小さくなり、ゲート電極から側方にはみ出す部分の半導体能動膜の面積が小さくなる結果としてオフ電流の上昇が抑制される。

【0016】

更に本発明は前記構造の薄膜トランジスタにおいて、チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されたことを特徴とする。

この構造によってオフ電流を更に低減することができる。また、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0017】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切りかつゲート電極上で膨出部を持った形状に形成され、ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記横切り方向に二股状に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の二股部分の奥側に間隙をあけて進入しかつ進入先端部分を前記ゲート電極の延びる方向に延びた形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極を横切った半導体能動膜部分の長さよりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする。

この構造においてソース電極とドレイン電極との間の部分に位置する半導体能動膜にチャネル部が生成されるが、ゲート電極を横切った部分のソース電極の幅およびドレイン電極の幅よりもチャネル部の幅を大きくすることにより、薄膜トランジスタとしてのオン電流を大きくさせる。また、ゲート電極を横切った半導体能動膜の幅よりもソース電極のドレイン電極と対峙する辺の長さが長くされてなることから、ゲート電極を横切った部分の半導体能動膜の幅が小さくなり、ゲート電極から側方にはみ出す部分の半導体能動膜の面積が小さくなる結果としてオフ電流の上昇が抑制される。

【0018】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切りかつゲート電極上で膨出部を持った形状に形成され、ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記横切り方向に二股状に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の二股部分の奥部に間隙をあけて進入した形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記ゲート電極を横切った半導体能動膜部分の長さよりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする。

この構造においてソース電極とドレイン電極との間の部分に位置する半導体能動膜にチャネル部が生成されるが、ゲート電極を横切った部分のソース電極の幅およびドレイン電極の幅よりもチャネル部の幅を大きくすることにより、薄膜トランジスタとしてのオン電流を大きくさせる。また、ゲート電極を横切った半導体能動膜の幅よりもソース電極のドレイン電極と対峙する辺の長さが長くされてなることから、ゲート電極を横切った部分の半導体能動膜の幅が小さくなり、ゲート電極から側方にはみ出す部分の半導体能動膜の面積が小さくなる結果としてオフ電流の上昇が抑制される。

【0019】

本発明は、短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極を横切った状態に形成され、ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方からゲート電極中心に向けて延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方からゲート電極中心に向けて延びかつ前記ソース電極と対峙した形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、該チャネル部周辺にオフ電流低減用の切り欠き部が形成されてなることを特徴とする。

この構造によってオフ電流を低減できるので、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。また、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる。

【0020】

本発明は、一対の基板間に液晶が封入され、一方の基板に複数のソース配線と複数のゲート配線がマトリクス状に配線され、複数のソース配線と複数のゲート配線とで区画される領域にそれぞれスイッチング素子と画素電極とが設けられ、前記スイッチング素子が、先のいずれかに記載の薄膜トランジスタからなるものである。

先に記載の薄膜トランジスタを液晶表示装置の画素電極駆動用のスイッチング素子として用いるならば、オン電流を高くしても、オフ電流が低いままで、液晶表示のコントラストの高い表示を得ることができる。また、オン電流を高くし、オフ電流を低くできることで画素電極に印加する電圧を保持することが容易にでき、画素電極に十分な量の電流を流すことができるので、蓄積容量を必要以上に増加させる必要は無くなり、開口率の低下を防止できる。

【0021】

【発明の実施の形態】

以下に本発明の各実施形態を詳細に説明するが、本発明はこの実施形態に限定されるものではない。

「第1実施形態」

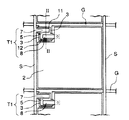

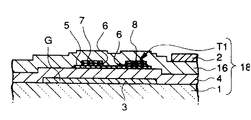

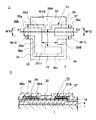

図1は本発明の第1実施形態の薄膜トランジスタT1を備えた薄膜トランジスタアレイ基板の要部平面図、図2は薄膜トランジスタ部分の要部断面図、図3は薄膜トランジスタの要部拡大平面図である。

この実施形態の薄膜トランジスタアレイ基板においては、ガラス等からなる透明の基板1上に、複数のゲート配線G・・・と複数のソース配線S・・・とが平面視マトリクス状に配設されている。そして、ゲート配線G・・・とソース配線S・・・とで囲まれた領域が1つの画素とされ、これらの画素領域毎にITO(インジウムスズ酸化物)などの透明導電材料からなる画素電極2が基板1上に位置した状態で設けられている。

【0022】

この例の薄膜トランジスタアレイ基板において、透明基板上の各画素領域にゲート配線Gから引き出された短冊状のゲート電極3が形成され、これらゲート配線G・・・とゲート電極3を覆うようにゲート絶縁膜4が形成され、ゲート電極3上のゲート絶縁膜4上にアモルファスシリコン(a-Si)等からなるアイランド状の半導体能動膜5が設けられている。そして、リン等のn型不純物を含むアモルファスシリコン(a-Si:n+)からなるオーミックコンタクト層6を介して半導体能動膜5の一側端部上にソース電極7が形成され、半導体能動膜5の他端部上に同様のオーミックコンタクト層6を介してドレイン電極8が形成され、ソース電極7がソース配線Sに接続されるとともに、ドレイン電極8が後述のパッシベーション膜(保護絶縁膜)16に形成されたコンタクトホールを介して画素電極2に接続されて薄膜トランジスタT1が構成されている。

【0023】

この実施形態の構造において、ソース配線Sとゲート配線Gと画素電極2が透明基板上に形成されている構造においては、図24と図25に示す従来構造の薄膜トランジスタアレイ基板と同等であるが、本実施形態の構造において従来構造と異なっているのは、ゲート電極3上に形成された半導体能動膜5の形状と、ソース電極7の形状とドレイン電極8の形状である。

【0024】

この実施形態においてゲート配線Gから画素領域に引き出されて短冊状のゲート電極3が形成されており、このゲート電極3上のゲート絶縁膜上にゲート電極3を図1または図3に示すように平面視左右に横切る方向にゲート電極3上で折れ曲がった形状に半導体能動膜5が形成されている。この半導体能動膜5は、ゲート電極3の基端側(ゲート配線Gに近い側)の大部分を図1または図3の左側(ソース配線Sに近い側)から平面視横切る形に形成された第1の横切り部分11と、ゲート電極3の先端側の大部分を図1または図3の右側(画素電極2に近い側)から平面視横切る形に形成された第2の横切り部分12とからなり、第1の横切り部分11と第2の横切り部分12がゲート電極3の中央部側のゲート絶縁膜上で連続一体化されていて、第1の横切り部分11と第2の横切り部分12とでゲート電極3を左右に横切る形とされ、半導体能動膜5は全体として平面視折れ曲がり形状に形成されている。

【0025】

次に、図3に示す第1の横切り部分11のソース配線側の端部11aがソース配線Sとゲート電極3の左側端部(ソース配線側の端部)3bとの間の部分の上方に位置され、第1の横切り部分11の反対側の延出部11bがゲート電極3の右側端部(画素電極側の側端部)3aよりも平面視若干内側の位置になるように形成されている。また、前記第2の横切り部分12のソース配線側の延出部12aがゲート電極3の左側端部(ソース配線側の側端部)3bよりも平面視若干内側に位置されるとともに、第2の横切り部分12の反対側(画素電極側)の端部はゲート電極3の右側端部3aと画素電極2との間に位置されている。そして、第1の横切り部分11がゲート電極3の左側端部3b上を乗り上げた部分の幅W5よりも、第1の横切り部分11と第2の横切り部分12の幅を合わせた部分の幅(前記横切り方向と直交するゲート電極3の伸びる方向(ゲート電極3の長さ方向あるいは短冊方向))W6が大きく形成されている。

第1の横切り部分11の延出部11bがゲート電極3の右側端部3aよりも内側の部分に位置することで半導体能動膜5の画素電極側の部分には凹部5aが形成されるとともに、第2の横切り部分12の延出部12aがゲート電極3の左側端部3bよりも内側に位置することで半導体能動膜5のソース配線側には凹部5bが形成されている。

【0026】

次に、図3に示すように、半導体能動膜5の第1の横切り部分11上にこの第1の横切り部分11の幅W5よりも幅狭の幅W8を有する短冊状のソース電極7がオーミックコンタクト層6を介して延在され、半導体能動膜5の第2の横切り部分12上にこの第2の横切り部分12の幅W5よりも幅狭の幅W8を有する短冊状のゲート電極8がオーミックコンタクト層6を介して延在されている。本実施形態においてソース電極7はソース配線Sに接続され、ドレイン電極8は画素電極2に接続されている。

【0027】

前記ソース電極7の先端部7aは第1の横切り部分11の端部11bよりも若干内側の位置に配置され、前記ドレイン電極8の先端部8aは第2の横切り部分12の端部12aよりも若干内側の位置に配置されていて、ソース電極5の先端部側とドレイン6の先端部側とが互いの側部を対峙させて半導体能動膜5上において対峙され、両者が対峙している間の部分に対応する半導体能動膜5の中央部分がチャネル部15とされている。このチャネル部15の幅(ゲート電極3における半導体能動膜5の横切り方向の幅、換言するとソース電極7とドレイン電極8の長さ方向の幅)W7は先に説明した半導体能動膜5の第1の横切り部分11および第2の横切り部分12がゲート電極3の左側端部3b上を乗り越える部分の幅W5よりも大きく形成されている。

【0028】

また、図2に示すように基板1上の薄膜トランジスタT1とゲート絶縁膜4とソース配線S・・・を覆ってパッシベーション膜(保護絶縁膜)16が形成され、基板1と画素電極2と薄膜トランジスタT1とゲート絶縁膜4とパッシベーション膜16により薄膜トランジスタアレイ基板18が構成されている。

【0029】

図1ないし図3に示す構造の薄膜トランジスタT1は、例えば、図4と図5に示す構造の液晶表示装置にスイッチング素子として適用される。

図4と図5に示す液晶表示装置20は先に構造を説明した薄膜トランジスタアレイ基板18と、この薄膜トランジスタアレイ基板18に対向して配置された対向基板21と、これら基板18、21の間に封入された液晶22と、薄膜トランジスタアレイ基板18の周辺部に設けられたゲートドライバ23、23とソースドライバ24、24、24、24とを主体として構成されている。

これらのゲートドライバ23とソースドライバ24は薄膜トランジスタアレイ基板18に複数設けられたゲート配線G・・・とソース配線S・・・にそれぞれ駆動信号を印加して各画素領域に設けられている薄膜トランジスタTによりスイッチング制御を行い、画素電極2に通電制御して液晶22の配向制御を行うためのものである。

【0030】

このような液晶駆動の際に各画素電極2へのスイッチングを薄膜トランジスタT1が行う。ゲート電極3に通電された場合にゲート電極3は半導体能動膜5に電界を印加して半導体能動膜5のチャネル部15にキャリアの移動を可能とするチャネルを生成させる。ここでチャネルが生成された半導体能動膜5においてソース電極7に通電されるとチャネル部15を介して電流が流れるので、ソース電極7からドレイン電極8に電流が流れて画素電極2に電圧が印加され、画素電極2が液晶22に作用させる電界により画素電極2に対応する位置の液晶22の配向制御がなされ、液晶表示装置20で表示ができるようになる。なお、実際には薄膜トランジスタアレイ基板18の裏面側にはバックライトが設けられているので、このバックライトの光を液晶22が通過させるか遮ることで表示、非表示の切り換えがなされるようになっている。

【0031】

前述のような薄膜トランジスタT1の作動において、図1ないし図3に示す薄膜トランジスタT1の構造であると、半導体能動膜5に凹部5a、5bが形成されていて、半導体能動膜5が平面視ゲート電極3から側方にはみ出す部分の面積が少ないために、バックライトから半導体能動膜5が光を受けて半導体能動膜5に流れようとする光電流を少なくできるので、従来構造とオン電流(Ion)が同等、即ちWが同一長さの時において薄膜トランジスタT1としてのオフ時の電流(Ioff)を低減できる。換言すると、半導体能動膜5の第1の横切り部分11がゲート電極3の左側端部3b上に乗り上げる部分の幅W5が第1の横切り部分11と第2の横切り部分12の幅を合わせた部分の幅W6よりも小さく形成されているとともに、半導体能動膜5の第2の横切り部分12がゲート電極3の右側端部3a上を乗り上げる部分の幅W5が第1の横切り部分11と第2の横切り部分12の幅を合わせた部分の幅W6よりも小さく形成されているので、半導体能動膜5においてバックライトからの光を受ける部分の面積が少なくされている結果としてオフ時の電流を小さくできる。また、オフ時の電流を小さくできるので、液晶駆動のための画素電極2の電圧保持のための蓄積容量を必要以上に大きくする必要は無くなり、蓄積容量形成用の電極を別途配する必要性を少なくすることで開口率の低下を抑えることができる。

【0032】

また、ソース電極7とドレイン電極8がゲート電極3の側端部3a、3bに乗り上げる部分の幅W8よりもチャネル部15の幅W7が大きいので、電流パスとしてのチャネル部15の幅が大きく形成された結果として薄膜トランジスタT1のオン時の電流を大きくさせている。従って本発明構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保しつつ、リーク電流となるオフ電流(Ioff)を小さくすることができる。

【0033】

なお、本実施形態においては半導体能動膜5の延出部11a、12bが平面視ゲート電極3の側方にはみ出す量を適宜調節しても良いのは勿論である。この延出部11a、12aはソース電極7あるいはドレイン電極8とゲート電極3の側端部3a、3bとの間の絶縁耐性を向上させるために有利であるので、これらの延出部11a、12bのはみ出し量は絶縁耐性を考慮し、光電流の増大を考慮して好適なはみ出し量に設定することが好ましい。

更に、本実施形態においては、ソース電極7とドレイン電極8の位置を交換しても良く、ソース電極7とドレイン電極8のどちらか一方に画素電極を接続し、どちらか他方をソース配線に接続することができる。

【0034】

「第2実施形態」

図6は本発明の第2実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT2の要部の平面構造を示すもので、この実施形態の薄膜トランジスタT2は、図3に示す薄膜トランジスタT1とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0035】

この第2実施形態の薄膜トランジスタT2においては先の第1実施形態の薄膜トランジスタT1の半導体能動膜5とほぼ同等形状の半導体能動膜9が設けられているが、先の第1実施形態の薄膜トランジスタT1と異なっているのは、ソース電極7とドレイン電極8の間に生成されるチャネル部15の周辺部に半導体能動膜9の切り欠き部9A、9Bが形成された点にある。

【0036】

切り欠き部9Aはソース電極7とドレイン電極8の間の中間位置の半導体能動膜9のソース配線側(ゲート電極3の左側端部3b側)の端部に形成され、切り欠き部9Bはソース電極7とドレイン電極8の間の中間部の半導体能動膜9の画素電極側(ゲート電極3の左側端部3b側)の端部に形成されている。これらの切り欠き部9Aと9Bの深さはソース電極7とドレイン電極8の間に存在するチャネル部15の幅W7を必要以上に狭くしないように切り欠き部9Aの底部の位置をチャネル部15の端部とし、切り欠き部9Bの底部の位置をチャネル部15の端部に位置合わせして設けられているが、切り欠き部9A、9Bの底部がチャネル部15の幅を多少狭くしても差し支えない。また、換言すると、半導体能動膜5においてチャネル部15の部分の両端部側が切り欠き部9A、9Bにより一部除去された形状とされている。

【0037】

図6に示されるように半導体能動膜9のチャネル部15の周辺部に切り欠き部9A、9Bが設けられた半導体トランジスタ構造であると、薄膜トランジスタとしてのオフ電流を小さくできる効果がある。

従って図6に示す構造では、先の第1実施形態の構造と同様にチャネル部15の幅W7を大きくすることで導電パスを大きくしてオン電流を増加させることができると同時にオフ電流の低減もできるので、液晶表示装置に適用した場合に先の第1実施形態の構造よりも更に表示品位を向上させることができると同時に開口率の低下も少なくできる効果がある。従ってこのような効果は液晶表示装置としての表示画面の大型化に寄与する。

【0038】

なお、本実施形態においては切り欠き部9A、9Bのうち、どちらか1つのみを設ける構成を採用することもできる。また、切り欠き部9A、9Bの底部の位置はソース電極7の先端部7aとドレイン電極8の先端部8aに隣接する位置にかかわらず、適宜調整しても良く、半導体能動膜9の延出部11a、12bのはみ出し量も適宜調節して良い。更に、本実施形態においては、ソース電極7とドレイン電極8の位置を交換しても良く、ソース電極7とドレイン電極8のどちらか一方を画素電極に接続し、どちらか他方をソース配線に接続しても良い。

【0039】

「第3実施形態」

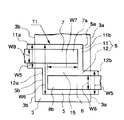

図7は本発明の第3実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT3の平面構造を示すもので、この実施形態において先の第1実施形態の構造と同じ部分には同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT3は、先の実施形態のものと同等のゲート電極3に対し、その上にゲート絶縁膜を介して形成される半導体能動膜25が平面矩形状とされ、しかもその半導体能動膜25がゲート電極3を図7の左右方向(ゲート配線と平行方向)に横切る形状に形成されている。前記半導体能動膜25の右側(一側)端部25aがゲート電極3の右側端部3aから平面視右側にはみ出すように形成され、半導体能動膜25の左側(他側)端部25bがゲート電極3の左側端部3bから平面視左側にはみ出すように形成されている。そして、半導体能動膜25の一側端部25a上には先の第1実施形態の構造と同等のオーミックコンタクト層26Aを介してドレイン電極26が設けられ、半導体能動膜25の他側端部上には先の第1実施形態の構造と同等のオーミックコンタクト層27Aを介してソース電極27が形成されている。

【0040】

第3実施形態の構造において特徴的なものは、ドレイン電極26とソース電極27の形状であり、ドレイン電極26は、ゲート電極3を横切る方向に延びる基体部26aとその先端部に基体部26aと直交する方向(ゲート電極3の短冊方向)に延びる延出部26bとからなり、ソース電極27は、ゲート電極3を横切る方向に延びる基体部27aとその先端部に基体部27aと直交する方向(ゲート電極3の短冊方向)に延びる延出部27bとからなる。ドレイン電極26の基体部26aは、半導体能動膜25の一側端部25aとゲート電極3の右側端部3aに乗り上げて半導体能動膜25の中央部側に延びるように設けられ、ソース電極27の基体部27aは、半導体能動膜25の他側端部25bとゲート電極3の左側端部3bに乗り上げて半導体能動膜25の中央部側に延びるように設けられており、それぞれ平面視T字状に形成されている。

そして、ドレイン電極26の延出部26b、26bとソース電極27の延出部27b、27bとの間の部分に相当する半導体能動膜25の中央部分がチャネル部29とされている。また、ソース電極27およびドレイン電極26が平面視ゲート電極3の側端部3a、3bを乗り上げる部分の幅W10よりもチャネル部29の幅W11の方が大きく形成されてチャネル部29が広くなるように形成されている。

【0041】

即ち、ソース電極27とドレイン電極26がゲート電極3の側端部を乗り上がる部分の幅W10よりもチャネル部29の幅W11が大きいので、電流パスとしてのチャネル部29の幅が大きく形成された結果として薄膜トランジスタT3のオン時の電流を大きくすることができる。従って本実施形態の構造により、先の実施形態の場合と同様に、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

なお、この第3実施形態の構造においては半導体能動膜25の端部25a、25bがゲート電極3の両側にはみ出す部分の面積が、先の第1実施形態および第2実施形態の構造よりも広いので、バックライトの光電流の影響によるオフ時の電流低減の面では先の実施形態よりも若干、不利になるが、先に説明の如くオン時の電流を大きくすることができる効果が得られることは明らかである。

図7において例えば、ゲート電極3からはみ出した半導体能動膜25の端部25a、25bにおいては、バックライトの光によりキャリアが発生するが、これらのキャリア発生領域は、ドレイン電極26の基体部26aと延出部26bの同電位部分で囲まれた領域、あるいは、ソース電極27の基体部27aと延出部27bの同電位部分で挟まれた領域であり、それらの領域はいずれも平面方向に電界が弱いので、ソース電極26とドレイン電極27間に流れようとするオフ電流(Ioff)に対して前記のキャリアは参加し難いと考えられる。

また、半導体能動膜25の一側端部25aと他側端部25bの幅(ゲート電極3の短冊方向の幅)を十分に確保してあるので、ソース電極26とゲート電極3との間の絶縁耐性を高くすることができ、ドレイン電極27とゲート電極3との間の絶縁耐性を高くすることができる。

【0042】

「第4実施形態」

図8は本発明の第4実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT4の平面構造を示すもので、この実施形態の薄膜トランジスタT4は、図7に示す薄膜トランジスタT3とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0043】

この第4実施形態の薄膜トランジスタT4において先の第3実施形態の薄膜トランジスタT3と異なっているのは、ソース電極27とドレイン電極26の間に生成されるチャネル部29の周辺部に半導体能動膜28の切り欠き部28A、28Bが形成された点にある。切り欠き部28Aはソース電極27とドレイン電極26の間の中間位置の半導体能動膜28の一側に形成され、切り欠き部28Bはソース電極27とドレイン電極26の間の中間位置の半導体能動膜28の他側に形成されている。

これらの切り欠き部28Aと28Bの深さはソース電極27とドレイン電極26の間に存在するチャネル部29の幅W11を過度に狭くしないように切り欠き部28Aの底部の位置と切り欠き部28Bの底部の位置をチャネル部29の端部近傍に位置合わせして設けられている。

【0044】

図8に示されように半導体能動膜28のチャネル部29の周辺部に切り欠き部28A、28Bが設けられた半導体トランジスタ構造であると、薄膜トランジスタとしてのオフ電流を小さくできる効果がある。

従って図8に示す構造では、チャネル部29の幅を大きくすることで導電パスを大きくしてオン電流を増加させることができると同時にオフ電流の上昇を抑制できるので、液晶表示装置のスイッチング素子として用いた場合に先の第3実施形態の構造よりも更に液晶表示装置の表示品位を向上させることができると同時に開口率も向上させることができる効果がある。従ってこのような効果は液晶表示装置としての表示画面の大型化に寄与する。

【0045】

「第5実施形態」

図9は本発明の第5実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT5の平面構造を示すもので、この実施形態の薄膜トランジスタT5は、図7に示す薄膜トランジスタT3とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0046】

この第5実施形態の薄膜トランジスタT5において先の第3実施形態の薄膜トランジスタT3と異なっているのは、半導体能動膜30が、ゲート電極3上のゲート絶縁膜上に位置する平面視矩形状の膨出部30aとその左右両側中央部に形成された延出部30b、30cとからなり、ソース電極27がゲート電極3の左側端部3bに乗り上げる部分に対応して延出部30bが形成され、ドレイン電極26がゲート電極3の右側端部3aに乗り上げる部分に対応して延出部30cが形成されていて、半導体能動膜30は延出部30bと膨出部30aと延出部30cによりゲート電極3を平面視左右に横切るように配置されている。

【0047】

これらの延出部30b、30cはそれぞれソース電極27とドレイン電極26の幅W12よりも若干広い幅W13になるように形成されていて、ソース電極27およびドレイン電極26とゲート電極3との間の絶縁耐性を高める効果を奏するものである。また、半導体能動膜30において延出部30bの幅方向両側部分には凹部30dが形成されていて、この部分の半導体能動膜が平面視ゲート電極3の側方にはみ出さないように形成されるとともに、延出部30cの幅方向両側部分にも凹部30eが形成されていて、この部分の半導体能動膜が平面視ゲート電極3の側方にはみ出さないように形成されている。更に、ドレイン電極26とソース電極27の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層26A、27Aが形成されている。

【0048】

図9に示すように半導体能動膜30に凹部30d、30d、30e、30eを形成して半導体能動膜30の両端側においてゲート電極3の両側方にはみ出す部分の面積を少なくすることで、液晶表示装置に備えられるバックライトからの光を受ける面積を少なくし、光電流の発生を少なくすることができる。これにより、バックライトから半導体能動膜30が光を受けて半導体能動膜30に流れようとする光電流を少なくできるので、薄膜トランジスタT5としてのオフ時の電流(Ioff)を低減できる。また、第5実施形態においてその他の効果は先の図7に示す第3実施形態の構造と同等である。

【0049】

「第6実施形態」

図10は本発明の第6実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT6の平面構造を示すもので、この実施形態の薄膜トランジスタT6は、図9に示す薄膜トランジスタT5とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0050】

この第6実施形態の薄膜トランジスタT6において先の第5実施形態の薄膜トランジスタT5と異なっているのは、ソース電極27とドレイン電極26の間に生成されるチャネル部34の周辺部に半導体能動膜33の切り欠き部33A、33Bが形成された点にある。切り欠き部33Aはソース電極27とドレイン電極26の間の中間位置の半導体能動膜33の一側端部に形成され、切り欠き部33Bはソース電極27とドレイン電極26の間の中間位置の半導体能動膜33の他側端部に形成されている。

【0051】

これらの切り欠き部33Aと33Bの深さはソース電極27とドレイン電極26の間に存在するチャネル部34の幅W11を過度に狭くしないように切り欠き部33Aの底部の位置と切り欠き部33Bの底部の位置をチャネル部34の端部近傍に位置合わせして設けられていることが好ましい。更に、ドレイン電極26とソース電極27の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層26A、27Aが形成されている。

【0052】

図10に示されように半導体能動膜33のチャネル部34の周辺部に切り欠き部30A、30Bが設けられた半導体トランジスタ構造であると、薄膜トランジスタとしてのオフ電流を小さくできる効果がある。

従って図10に示す構造では、チャネル部34の幅を大きくすることで導電パスを大きくしてオン電流を増加させることができると同時にオフ電流の低減もできるので、先の第5実施形態の構造と同等の効果を得た上に、更に液晶表示装置に応用した場合の液晶表示装置の表示品位を向上させることができると同時に開口率を向上させることができる効果がある。従ってこのような効果は液晶表示装置としての表示画面の大型化に寄与する。

【0053】

「第7実施形態」

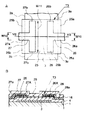

図11は先の各実施形態の構造と同様に液晶表示装置の薄膜トランジスタアレイ基板に適用される薄膜トランジスタの第7実施形態を示すもので、この第7実施形態の薄膜トランジスタT7においてソース配線Sとゲート配線Gと画素電極2が透明基板上に形成されている構造においては、先の第1〜第6実施形態の構造の薄膜トランジスタアレイ基板と同等であるが、本実施形態の構造において先の実施形態の構造と異なっているのは、ゲート電極3上のゲート絶縁膜上に形成された半導体能動膜の形状と、ソース電極の形状とドレイン電極の形状である。

【0054】

この実施形態においてゲート配線Gから画素領域に引き出されて短冊状のゲート電極3が形成されており、このゲート電極3上のゲート絶縁膜上にゲート電極3を図11の左右方向に横切る形で半導体能動膜35が形成されている。

半導体能動膜35は、平面視ゲート電極3上のゲート絶縁膜上に位置する矩形状の膨出部35aと膨出部35aの一側(ゲート電極3の基端部側、即ちゲート配線に近い側)に膨出部35aの左右両側に突出するように形成された延出部35b、35cとから構成されている。これらのうちの延出部35bがゲート電極3の左側端部3bから左側方に平面視はみ出して形成され、延出部35cがゲート電極3の右側端部3aから右側方に平面視はみ出して形成され、半導体能動膜35は延出部35bと膨出部35aと延出部35cとによってゲート電極3を平面視左右に(ゲート配線と平行方向に)横切るように配置されている。

【0055】

半導体能動膜35の延出部35bの上には延出部35bの幅W15よりも若干狭い幅W16のソース電極36が形成されている。このソース電極36は、先の半導体能動膜35の延出部35bに沿い、ゲート電極3の左側端部3bを横切って形成された第1の電極部36aと、ゲート電極35上において平面視ゲート電極3の伸びる方向(短冊方向)に延出された第2の電極部36bと、第2の電極部36bの先端部側において第2の電極部36bと平面視直交する方向に延出された第3の電極部36cを有して構成され、第2の電極部36bと第3の電極部36cとがゲート電極3上で平面視L字型に配置されている。

【0056】

次に、ドレイン電極37は半導体能動膜35の延出部35cの幅W15よりも若干狭い幅W16を有する短冊状の形状とされ、先のソース電極36の第1の電極部36aと同一直線位置で、平面視した場合において延出部35c上と膨出部35a上に位置するように形成されている。また、本実施形態の構造において、第1の電極部36aと第2の電極部36bとが接続された折曲部分36dとドレイン電極37の先端部との間の距離と、ドレイン電極37の先端部と第3の電極部36cの先端部との間の距離がほぼ同一に形成されていることが好ましいが、これらの距離が多少異なっていても差し支えない。

【0057】

また、ドレイン電極37の先端部とソース電極36との間に対応する部分の半導体能動膜35がチャネル部38とされ、ソース電極36とドレイン電極37とが実質的に向かい合う幅、即ち、ソース電極36の第2の電極部36bにおいてドレイン電極37側の辺36eの長さ(W17)と第3の電極部36cにおいてドレイン電極37側の辺36fの長さ(W18)との合計値(W17+W18)は、先の半導体能動膜35の延出部35bあるいは延出部35cの幅W15よりも大きく形成されている。更に、ソース電極36とドレイン電極37の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層36A、37Aが形成されている。

【0058】

なお、本実施形態においては、これまでの第1実施形態〜第6実施形態の構造とは異なり、ソース電極36をソース配線に接続することが必要であり、ドレイン電極37を画素電極2に接続することが必要である。この理由は、ゲート電極3をオフとした時に発生する、ゲート電極3とドレイン電極37との間に発生する容量(一般にCgdと称される)を小さくするためである。このCgdの値が大きいとゲートオフ時の画素に保持されている電荷の降下が大きくなり、表示品位を劣化させるためである。

【0059】

前述のような薄膜トランジスタT7の構造であると、平面視した場合において半導体能動膜35から側方にはみ出すのは、ソース電極36あるいはゲート電極37よりも若干幅の大きな半導体能動膜35の延出部35bと延出部35cのみであるので、半導体能動膜の一部分がゲート電極35から平面視側方にはみ出す部分の面積が少ないために、バックライトから半導体能動膜35が光を受けて半導体能動膜35に流れようとする光電流を少なくできるので、薄膜トランジスタT7としてのオフ時の電流(Ioff)を抑制できる。

【0060】

また、ソース電極36とドレイン電極37がゲート電極3の側端部を乗り越える部分の幅W16よりもチャネル部38の幅W17、W18とも大きいので、電流パスとしてのチャネル部38の幅が大きく形成された結果として薄膜トランジスタT7のオン時の電流を大きくさせている。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保しつつ、リーク電流となるオフ電流(Ioff)を小さくできる。

【0061】

「第8実施形態」

図12は本発明の第8実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT8の平面構造を示すもので、この実施形態の薄膜トランジスタT8は、図11に示す薄膜トランジスタT7とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0062】

この第8実施形態の薄膜トランジスタT8において先の第7実施形態の薄膜トランジスタT7と異なっているのは、先の実施形態の半導体能動膜35と同等の半導体能動膜39が膨出部39aと延出部39bと延出部39cとからなり、更にソース電極36とドレイン電極37の間に生成されるチャネル部32の周辺部に半導体能動膜39の切り欠き部39A、39Bが形成された点にある。切り欠き部39Aはソース電極36の折曲部36dとドレイン電極37の先端部の間の中間位置の半導体能動膜39のソース配線側(図12の上側)の端部に形成され、切り欠き部39Bはソース電極36の第3の電極部36cとドレイン電極37の先端部の間の中間部の半導体能動膜39の端部に形成されている。これらの切り欠き部39Aと39Bの深さは、ソース電極36とドレイン電極37との間に存在するチャネル部32を必要以上に狭くしないように切り欠き部39Aの底部の位置をチャネル部32の端部とし、切り欠き部39Bの底部の位置をチャネル部38の端部に位置合わせして設けられている。更に、ソース電極36とドレイン電極37の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層36A、37Aが形成されている。

【0063】

図12に示されように半導体能動膜39のチャネル部32の周辺部に切り欠き部39A、39Bが設けられた半導体トランジスタ構造であると、薄膜トランジスタとしてのオフ電流を小さくできる効果がある。

従って図12に示す構造では、切り欠き部39Aを介してソース電極36とドレイン電極37とが対峙する部分の第2の電極部36bの辺の長さW19と、切り欠き部39Bを介してソース電極36とドレイン電極37とが対峙する部分の第3電極部36cの辺の長さW14との合計長さを延出部39bの幅W16あるいは延出部39cの幅W16よりも長くしたので、チャネル部32の幅を大きくしたことになり、導電パスを大きくしてオン電流を増加させることができると同時にオフ電流の低減もできるので、先の第7実施形態の構造よりも更に表示品位を向上させることができると同時に開口率も向上させることができる効果がある。従ってこのような効果は液晶表示装置としての表示画面の大型化に寄与する。なお、本第8実施形態においてその他の効果は先の第7実施形態と同等である。

【0064】

「第9実施形態」

図13は本発明の第9実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT9の平面構造を示すもので、この実施形態の薄膜トランジスタT9において先に説明した実施形態の構造と同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0065】

この第9実施形態の薄膜トランジスタT9において先の実施形態の薄膜トランジスタと異なっているのは、半導体能動膜40が、ゲート電極3上のゲート絶縁膜上に位置する平面視矩形状の膨出部40aとその左右両側中央部に形成された延出部40b、40cとからなり、ソース電極41がゲート電極3の左側端部3bに乗り上げる部分に対応して延出部40bが形成され、ドレイン電極42がゲート電極3の右側端部3aに乗り上げる部分に対応して延出部40cが形成されていて、半導体能動膜40は延出部40bと膨出部40aと延出部40cによりゲート電極3を平面視左右に横切るように配置されている。

【0066】

この実施形態のソース電極41は、半導体能動膜40の延出部40bに乗り上げて半導体能動膜40の膨出部40a側まで達する短冊状の第1の電極部41aと、第1の電極部41aの先端部からゲート電極3上のゲート絶縁膜上において平面視ゲート電極3の伸びる方向(短冊方向)に平面視二股状に分岐されて各々ゲート電極3の端部近くに達する短冊状の第2の電極部41bと、第2の電極部41bの両先端部からゲート電極3の横切り方向(ゲート配線と平行な図13の左右方向)に伸びて平面視半導体能動膜40の膨出部40aの角部近くまで延出する短冊状の第3の電極部41cとから構成され、第2の電極部41b、41bと第3の電極部41c、41cは全体として平面視略C字状に形成されている。

【0067】

ドレイン電極42は、半導体能動膜40の延出部40cに乗り上げて半導体能動膜40の膨出部40aまで達する第1の電極部42aと、この第1の電極部42aの先端部に第1の電極部42aに対して直交する方向に伸びる第2の電極部42bとからなる平面視T字状に形成されている。また、ドレイン電極42の第1の電極部42aの先端部は先のソース電極41の第3の電極部41c、41cの先端部間の中央に進入した状態に配置され、ドレイン電極42の第2の電極部42bは先のソース電極41の第3の電極部41c、41cの先端部間の中央に位置されていて、ソース電極41の第2の電極部41bおよび第3の電極部41c、41cとドレイン電極42の第2の電極部42cとの間の領域に対応する半導体能動膜部分がチャネル部43とされている。本実施形態では、ドレイン電極42に対してソース電極41の第2の電極部41bと第3の電極部41cとが対峙する部分の辺の長さが、半導体能動膜40の延出部40bあるいは延出部40cの幅W21よりも長くされている。

【0068】

前述の延出部40b、40cはそれぞれソース電極41とドレイン電極42の幅W20よりも若干広い幅W21になるように形成されていて、ソース電極41およびドレイン電極42とゲート電極3との間の絶縁耐性を高める。また、半導体能動膜40の膨出部40aは平面視ゲート電極3の上方にのみ形成されていてゲート電極3の側方にはみ出すのは半導体能動膜40の膨出部40aよりも幅が遥かに小さな延出部40bと延出部40cのみとされている。更に、ソース電極41とドレイン電極42の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層41A、42Aが形成されている。

なお、本実施形態においてソース電極41はソース配線Sに接続され、ドレイン電極42は画素電極2に接続される必要がある。この理由は、ゲート電極3をオフとした時に発生する、ゲート電極3とドレイン電極42との間に発生する容量(一般にCgdと称される)を小さくするためである。このCgdの値が大きいとゲートオフ時の画素に保持されている電荷の降下が大きくなり、表示品位を劣化させるためである。

【0069】

図13に示すように半導体能動膜40の両端側においてゲート電極3の両側方にはみ出す部分を少なくすることで、液晶表示装置に備えられるバックライトからの光を受ける面積を少なくし、光電流の発生を少なくすることができる。これにより、バックライトから半導体能動膜40が光を受けて半導体能動膜40に流れようとする光電流を少なくできるので、薄膜トランジスタT9としてのオフ時の電流(Ioff)を抑制できる。

【0070】

また、ソース電極41とドレイン電極42がゲート電極3の側端部を乗り越える部分の幅W20よりもチャネル部43の幅W22が大きいので、電流パスとしてのチャネル部43の幅が大きく形成された結果として薄膜トランジスタT9のオン時の電流を大きくさせている。従って本発明構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保しつつ、オフ電流(Ioff)を抑制することができる。

【0071】

「第10実施形態」

図14は本発明の第10実施形態の薄膜トランジスタアレイ基板に適用される薄膜トランジスタT10の平面構造を示すもので、この実施形態の薄膜トランジスタT10は、図13に示す薄膜トランジスタT9とほぼ同等の構造であり、同等の構成部分については同一符合を付してそれらの部分の説明は省略する。

【0072】

この第10実施形態の薄膜トランジスタT10において先の第9実施形態の薄膜トランジスタT9と異なっているのは、ドレイン電極44が短冊状に形成されている点である。このドレイン電極44は先の第9実施形態のドレイン電極42の第1の電極部42aと同じ幅に形成され、その先端部44aが略C字型のソース電極先端部の中間部に進入されるとともに、先端部44aとソース電極41の第2の電極部41bと第3の電極部41cとの間の部分に対応する半導体能動膜部分にチャネル部45が形成されている。更に、ソース電極41とドレイン電極42の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層41A、42Aが形成されている。

【0073】

図14に示す構造の薄膜トランジスタT10においても先の実施形態の薄膜トランジスタT9と全く同等の効果を得ることができる。

【0074】

「第11実施形態」

図15は本発明に係る薄膜トランジスタの第11実施形態を示すもので、この第11実施形態の薄膜トランジスタT11は、ゲート電極3を横切る形で矩形状に半導体能動膜47が形成され、この半導体能動膜47はゲート電極3上のゲート絶縁膜上に位置する本体部47aと、ゲート電極3の図15において右側方側(画素電極側)に平面視はみ出して延出された延出部47aと、ゲート電極3の図15において左側方側(ソース配線側)に平面視はみ出して延出された延出部47bとから構成されている。そして、半導体能動膜3の延出部47aとゲート電極3の右端部3aとを平面視乗り上がってゲート電極3の中央部側に向かうように短冊状のドレイン電極48が形成されるとともに、半導体能動膜47の延出部47bとゲート電極3の左端部3bとを平面視乗り上がってゲート電極3の中央部側に向かう短冊状のソース電極49が形成されている。

【0075】

前記ドレイン電極48とソース電極49の幅W25は半導体能動膜47の幅W26よりも若干短く形成され、ドレイン電極48の先端部48aとソース電極49の先端部49aとの間の部分に対応する半導体能動膜47の中央部にチャネル部50が形成されている。また、チャネル部50の周辺部であって、ソース電極49の先端部49aとドレイン電極48の先端部48aとの間の部分の半導体能動膜47の周辺部には切り欠き部47A、47Bが形成されている。

これらの切り欠き部47A、47Bはチャネル部50の幅W27を必要以上に狭めないような深さに形成されるので、切り欠き部47Aの底部と切り欠き部47Bの底部は、ドレイン電極48の先端部48aの角部とソース電極49の角部を結ぶ線51よりも若干内側に入る位置にされている。更に、ソース電極49とドレイン電極48の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層48A、49Aが形成されている。

図15に示す構造の薄膜トランジスタT11においてはオフ電流の上昇を抑制することができるという効果を奏する。

【0076】

「第12実施形態」

図16は本発明に係る薄膜トランジスタの第12実施形態を示すもので、この実施形態の薄膜トランジスタT12は、先に図7を基に説明した第3実施形態の薄膜トランジスタT3の構造に対し、半導体能動膜の構成が一部異なるのみで、その他の構造は同一にしたものである。よって、同一の構成部分は同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT12において半導体能動膜55は、ゲート電極3上のゲート絶縁膜上にのみ形成された矩形状とされ、半導体能動膜55は平面視ゲート電極3の側方にはみ出されていない構造とされている。更に、ソース電極27とドレイン電極27の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層26A、27Aが形成されている。

【0077】

図16に示す構造において、ソース電極27とドレイン電極26がゲート電極3の側端部を乗り越える部分の幅W10よりもチャネル部55の幅(ゲート電極3の伸びる方向:短冊方向の幅)W11が大きいので、電流パスとしてのチャネル部55の幅が大きく形成された結果として薄膜トランジスタT12のオン時の電流を大きくすることができる。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

また、図7に示す実施形態の構造では半導体能動膜25の端部25a、25bがゲート絶縁膜3の側方にはみ出されていてバックライトの光を受けて光電流が多少流れるおそれがあったが、図16に示す実施形態の構造では半導体能動膜55のはみ出し部分は存在しないので、図7に示す構造よりも薄膜トランジスタとしてのオフ電流(Ioff)を少なくすることができる。

【0078】

「第13実施形態」

図17は本発明に係る薄膜トランジスタの第13実施形態を示すもので、この実施形態の薄膜トランジスタT13は先に図13を基に説明した第9実施形態の薄膜トランジスタT9の構造に対し、半導体能動膜の構成が一部異なるのみで、その他の構造は同一にしたものである。よって、同一の構成部分は同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT13において半導体能動膜57は、ゲート電極3上のゲート絶縁膜上にのみ形成された矩形状とされ、半導体能動膜57は平面視ゲート電極3の側方にはみ出されていない構造とされている。更に、ソース電極41とドレイン電極42の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層41A、42Aが形成されている。

【0079】

図17に示す構造において、ソース電極41とドレイン電極42がゲート電極3の側端部を乗り越える部分の幅W20よりもチャネル部57の幅(ソース電極部42に対峙する第2の電極部41bと第3の電極部41cの各辺の長さの合計値)が大きいので、電流パスとしてのチャネル部43の幅が大きく形成された結果として薄膜トランジスタT13のオン時の電流を大きくすることができる。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

また、図13に示す実施形態の構造では半導体能動膜40の延出部40b、40cがゲート絶縁膜3の側方にはみ出されていてバックライトの光を受けてわずかながら光電流が流れるおそれがあったが、図17に示す実施形態の構造では半導体能動膜57のはみ出し部分は存在しないので、図13に示す構造よりも薄膜トランジスタとしてのオフ電流Ioffを少なくすることができる。

【0080】

「第14実施形態」

図18は本発明に係る薄膜トランジスタの第14実施形態を示すもので、この実施形態の薄膜トランジスタT14は、先に図14を基に説明した第10実施形態の薄膜トランジスタT10の構造に対し、半導体能動膜の構成が一部異なるのみで、その他の構造は同一にしたものである。よって、同一の構成部分は同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT14において半導体能動膜60は、ゲート電極3上のゲート絶縁膜上にのみ形成された矩形状とされ、半導体能動膜60は平面視ゲート電極3の側方にはみ出されていない構造とされている。更に、ソース電極41とドレイン電極44の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層41A、44Aが形成されている。

【0081】

図18に示す構造において、ソース電極41とドレイン電極44がゲート電極3の側端部を乗り越える部分の幅W20よりもチャネル部45の幅(ソース電極44に対峙する第2の電極部41bと第3の電極部41cの各辺の長さの合計値)が大きいので、電流パスとしてのチャネル部45の幅が大きく形成された結果として薄膜トランジスタT13のオン時の電流を大きくすることができる。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

また、図14に示す実施形態の構造では半導体能動膜40の延出部40b、40cがゲート絶縁膜3の側方にはみ出されていてバックライトの光を受けてわずかながら光電流が流れるおそれがあったが、図18に示す実施形態の構造では半導体能動膜60のはみ出し部分は存在しないので、図14に示す構造よりも薄膜トランジスタとしてのオフ電流Ioffを少なくすることができる。

【0082】

「第15実施形態」

図19は本発明に係る薄膜トランジスタの第15実施形態を示すもので、この実施形態の薄膜トランジスタT15は、先に図11を基に説明した第7実施形態の薄膜トランジスタT7の構造に対し、半導体能動膜の構成が一部異なるのみで、その他の構造は同一にしたものである。よって、同一の構成部分は同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT15において半導体能動膜63は、ゲート電極3上のゲート絶縁膜上にのみ形成された矩形状とされ、半導体能動膜63は平面視ゲート電極3の側方にはみ出されていない構造とされている。更に、ソース電極36とドレイン電極37の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層36A、37Aが形成されている。

【0083】

図19に示す構造において、ソース電極36とドレイン電極37がゲート電極3の側端部を乗り越える部分の幅W16よりも第2の電極部36bの辺の長さW17と第3の電極部36cの辺の長さW18の合計値が長いので電流パスとしてのチャネル部38の幅が大きく形成された結果として薄膜トランジスタT15のオン時の電流を大きくすることができる。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

【0084】

また、図11に示す実施形態の構造では半導体能動膜35の延出部35b、35cがゲート絶縁膜3の側方にはみ出されていてバックライトの光を受けてわずかながら光電流が流れるおそれがあったが、図19に示す実施形態の構造では半導体能動膜63のはみ出し部分は存在しないので、図11に示す構造よりも薄膜トランジスタとしてのオフ電流(Ioff)を少なくすることができる。

【0085】

「第16実施形態」

図20は本発明に係る薄膜トランジスタの第16実施形態を示すもので、この実施形態の薄膜トランジスタT16は、先に図3を基に説明した第1実施形態の薄膜トランジスタT1の構造に対し、半導体能動膜の構成が一部異なるのみで、その他の構造は同一にしたものである。よって、同一の構成部分は同一の符合を付してそれらの部分の説明は省略する。

この実施形態の薄膜トランジスタT16において半導体能動膜65は、ゲート電極3上のゲート絶縁膜上にのみ形成された矩形状とされ、半導体能動膜65は平面視ゲート電極3の側方にはみ出されていない構造とされている。更に、ソース電極7とドレイン電極8の各々の下面側には先の実施形態の場合と同等にオーミックコンタクト層6が形成されている。

【0086】

図20に示す構造において、ソース電極7とドレイン電極8がゲート電極3の側端部を乗り越える部分の幅W8よりもチャネル部38の幅(ゲート電極3の伸びる方向:短冊方向の幅)W7が大きいので、電流パスとしてのチャネル部15の幅が大きく形成された結果として薄膜トランジスタT16のオン時の電流を大きくすることができる。従って本実施形態の構造により、画素の大きな大型の液晶表示装置に適用する場合に大きな画素の書き込みに必要な電流量を確保することができる。

また、図3に示す実施形態の構造では半導体能動膜11の延出部11a、12bがゲート絶縁膜3の側方にはみ出されていてバックライトの光を受けてわずかながら光電流が流れるおそれがあったが、図20に示す実施形態の構造では半導体能動膜65のはみ出し部分は存在しないので、図3に示す構造よりも薄膜トランジスタとしてのオフ電流Ioffを少なくすることができる。

【0087】

【実施例】

透明ガラス基板上に図1に示す平面構造で図2に示す断面構造の薄膜トランジスタを作製した。ゲート配線とゲート電極はCrから形成し、これらを覆って厚さ3000ÅのSiNxからなるゲート絶縁膜を形成し、アモルファスシリコン(a-Si)からなるアイランド状の厚さ1500Åの半導体能動膜を形成し、リンをドープしたアモルファスシリコン(a-Si:n+)からなるオーミックコンタクト層を介してCrからなるソース配線およびソース電極とドレイン電極を形成した。その後、パッシベーション膜(SiNx:厚さ4000Å)を成膜し、コンタクトホールを形成した後、ITOからなる画素電極をソース配線とゲート配線で囲まれた領域に対応させて形成し、前記コンタクトホールを介して画素電極とドレイン電極を接続した。

また、ソース電極の幅は4μm、ドレイン電極の幅は4μm、半導体能動膜の第1の横切り部分の幅は7μm、第2の横切り部分の幅は7μm、ソース電極とドレイン電極間の距離は3μmとした。

【0088】

得られた半導体トランジスタのオン電流(Ion)とオフ電流(Ioff)を測定した結果を図21に示す。また、図24ないし図26に示す従来構造の薄膜トランジスタのオン電流(Ion)とオフ電流(Ioff)を測定した結果を図21に併記した。

【0089】

図21において▲1▼で示す線が本発明構造のオフ電流(Ioff)を示し、▲2▼で示す線が従来構造のオフ電流(Ioff)を示し、▲3▼で示す線が本発明構造のオン電流(Ion)を示し、▲4▼で示す線が従来構造のオン電流(Ion)を示す。

図21に示す結果から、本発明構造であるならば、従来構造と同等のオン電流が得られるにもかかわらず、オン電流の増加に伴うオフ電流の上昇が抑えられていることが明らかである。

【0090】

次に、図9に示す構造の薄膜トランジスタを作製した。各部分を構成する材料は先の実施例と同等とした。また、ソース電極の幅は4μm、ドレイン電極の幅は4μmとした。

得られた半導体トランジスタのオン電流(Ion)とオフ電流(Ioff)を測定した結果を図22に示す。また、図24ないし図26に示す従来構造の薄膜トランジスタのオン電流(Ion)とオフ電流(Ioff)を測定した結果も図22に併記した。

【0091】

図22において▲5▼で示す線が本発明構造のオフ電流(Ioff)を示し、▲6▼で示す線が従来構造のオフ電流(Ioff)を示し、▲7▼で示す線が本発明構造のオン電流(Ion)を示し、▲8▼で示す線が従来構造のオン電流(Ion)を示す。

図21に示す結果から、本発明構造であるならば、従来構造と同等のオン電流が得られるにもかかわらず、オン電流の増加に対するオフ電流の増加が抑制されていることが明らかである。

【0092】

次に、図15に示す構造の薄膜トランジスタを作製し、切り欠き部の深さの値とオン電流(Ion)とオフ電流(Ioff)の関係を測定した結果を図23に示す。 この例の構造では、半導体能動膜の幅を15μm、ソース電極幅を12μm、ドレイン電極幅を12μm、ソース電極とドレイン電極間の距離を7μmに設定した。

図23に示す結果から、図15に示す構造を採用することでオフ電流を十分に低い範囲に抑制できることが明らかである。

【0093】

【発明の効果】

以上説明したように本発明は、ゲート電極に乗り上げたソース電極幅またはドレイン電極幅よりもチャネル部の幅を大きくしたので、導電パスとしてのチャネル部を大きくしつつ、オフ電流を抑制させることができる。

また、上記の構造に対してチャネル部周辺の半導体能動膜に切り欠き部を設けることで、オフ電流を少なくすることができるので、オン電流の高いオフ電流の低い薄膜トランジスタを提供できる。

【0094】

また、オフ電流の上昇を抑制できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0095】

本発明は、ゲート電極上において半導体能動膜で折れ曲がり状に横切る形状として半導体能動膜上に第1の横切り部分と第2の横切り部分を設け、ゲート電極を横切る半導体能動膜の幅よりも横切り方向のチャネル部の幅を大きくするとともに、導電パスとしてのチャネル部を大きくすることにより、オン電流を増加させて、かつ、オフ電流を抑制することができる。

また、上記の構造に対してチャネル部周辺の半導体能動膜に切り欠き部を設けることで、オフ電流を少なくすることができるので、オン電流の高いオフ電流の低い薄膜トランジスタを提供できる。

更に、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を抑制すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0096】

本発明は、ゲート電極上で膨出部を有するように半導体能動膜を形成し、半導体能動膜上に折れ曲がり形状のソース電極とそれに対峙するドレイン電極を設けることにより、導電パスとしてのチャネル部を大きくし、結果としてオン電流を増加させ、オフ電流を抑制することができる。

また、上記の構造に対してチャネル部周辺の半導体能動膜に切り欠き部を設けることで、オフ電流を少なくすることができるので、オン電流の高いオフ電流の低い薄膜トランジスタを提供できる。

更に、オフ電流を低減できることから、液晶表示装置に適用し、ソース電極あるいはドレイン電極に画素電極を接続した場合に画素電極の電圧保持のために蓄積容量を増大させる必要はないので、開口率を低下させることもない。更に、オフ電流を低減すると同時に先に記載の構造によりオン電流を大きくできるので、液晶駆動の際のオフ電流とオン電流の差異を大きくすることができ、液晶表示の際のコントラストを大きくできる薄膜トランジスタを提供できる。

【0097】

本発明は、ゲート電極上で膨出部を有するように半導体能動膜を形成し、半導体能動膜上に二股に折れ曲がり形状のソース電極とそれに対峙するドレイン電極を設けることにより、導電パスとしてのチャネル部を大きくでき、結果としてオン電流を増加させつつ、オフ電流を抑制することができる。

【0098】

本発明は、ゲート電極上に半導体能動膜を設け、半導体能動膜上の一側にソース電極を他側にドレイン電極を各々伸びた形状に形成し、ソース電極とドレイン電極との間の半導体能動膜に切り欠き部を設けたので、オフ電流を少なくすることができるので、オフ電流の低い薄膜トランジスタを提供できる。

【0099】

次に、先に記載の薄膜トランジスタを液晶表示装置の画素電極駆動用のスイッチング素子として用いるならば、オン電流が高く、オフ電流の低い、液晶表示のコントラストの高い表示を得ることができる。また、オン電流を高くすることで画素電極に印加する電圧を保持することが容易にでき、画素電極に十分な量の電流を流すことができるので、蓄積容量を必要以上に増加させる必要は無くなり、開口率の低下を防止できる。

【図面の簡単な説明】

【図1】 本発明に係る薄膜トランジスタアレイ基板の第1実施形態の要部を示す平面図。

【図2】 図1のII−II線に沿う断面図。

【図3】 図1に示す第1実施形態の薄膜トランジスタアレイ基板の薄膜トランジスタ部分の拡大平面略図。

【図4】 図1に示す薄膜トランジスタアレイ基板を備えた液晶表示装置の一実施形態を示す平面図。

【図5】 図4に示す液晶表示装置のV−V線に沿う断面図。

【図6】 第2実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図。

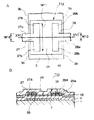

【図7】 図7Aは第3実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図7Bは図7AのVII−VII線に沿う断面図。

【図8】 図8Aは第4実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図8Bは図8AのVIII−VIII線に沿う断面図。

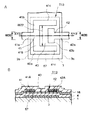

【図9】 図9Aは第5実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図9Bは図9AのIX−IX線に沿う断面図。

【図10】 図10Aは第6実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図10Bは図10AのX−X線に沿う断面図。

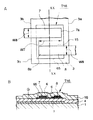

【図11】 図11Aは第7実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す平面略図、図11Bは図11AのXI−XI線に沿う断面図。

【図12】 図12Aは第8実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図12Bは図12AのXII−XII線に沿う断面図。

【図13】 図13Aは第9実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図13Bは図13AのXIII−XIII線に沿う断面図。

【図14】 図14Aは第10実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す平面略図、図14Bは図14AのXIV−XIV線に沿う断面図。

【図15】 図15Aは第11実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図15Bは図15AのXV−XV線に沿う断面図。

【図16】 図16Aは第12実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図16Bは図16AのXVI−XVI線に沿う断面図。

【図17】 図17Aは第13実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図17Bは図17AのXVII−XVII線に沿う断面図。

【図18】 図18Aは第14実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図18Bは図18AのXVIII−XVIII線に沿う断面図。

【図19】 図19Aは第15実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図19Bは図19AのXIX−XIX線に沿う断面図。

【図20】 図20Aは第16実施形態の薄膜トランジスタアレイ基板に用いられる薄膜トランジスタ部分を示す拡大平面略図、図20Bは図20AのXX−XX線に沿う断面図。

【図21】 第1実施形態で得られた薄膜トランジスタのオン電流とオフ電流を比較例の薄膜トランジスタと比較して示した図。

【図22】 第5実施形態で得られた薄膜トランジスタのオン電流とオフ電流を比較例の薄膜トランジスタと比較して示した図。

【図23】 第11実施形態で得られた薄膜トランジスタのオフ電流を示した図。

【図24】 従来の一般的な液晶表示装置の薄膜トランジスタアレイ基板の要部を示す図。

【図25】 図24に示す液晶表示装置の薄膜トランジスタ部分を断面とした図。

【図26】 図24に示す薄膜トランジスタアレイ基板の薄膜トランジスタ部分の拡大平面図。

【符号の説明】

S・・・ソース配線、G・・・ゲート配線、W7、W9、W11、W17、W18、W22、W27・・・チャネル部の幅、1・・・基板、2・・・画素電極、3・・・ゲート電極、4・・・ゲート絶縁膜、5、9、25、28、31、33、35、39、40、47、55、57、60、63、65・・・半導体能動膜、9A、9B、28A、28B、33A、33B、39A、39B、47A、47B・・・切り欠き部、7、27、36、41、48・・・ソース電極、8、26、37、42、44、49・・・ドレイン電極、11・・・第1の横切り部分、12・・・第2の横切り部分、15、29、31、32、34、38、43、45、50・・・チャネル部。

Claims (6)

- 短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極の延びる方向に延びる2辺のそれぞれを横切る2つの矩形の延出部及び前記2辺を前記延出部が横切った幅よりも大きい幅を有したゲート電極上の膨出部を持った形状に形成され、

ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の延びる方向に延びる形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の延びる方向に延びた形状に前記ソース電極と対峙させてドレイン電極が形成され、対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記2辺を前記延出部が横切った幅よりも前記ゲート電極の延びる方向の前記チャネル部の幅が大きくされており、

前記チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されてなることを特徴とする薄膜トランジスタ。 - 短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極の延びる方向に延びる2辺のそれぞれを横切る2つの矩形の延出部及び前記2辺を前記延出部が横切った幅よりも大きい幅を有したゲート電極上の膨出部を持った形状に形成され、

ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記ゲート電極の延びる方向に折れ曲がりさらに前記延出部が横切る方向に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の延びる方向の折れ曲がり部分及び前記延出部が横切る方向に延びた部分に間隙をあけて進入した形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記2辺を前記延出部が横切った幅よりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする薄膜トランジスタ。 - 請求項2記載の薄膜トランジスタにおいて、前記チャネル部周辺の半導体能動膜にオフ電流低減用の切り欠き部が形成されてなることを特徴とする薄膜トランジスタ。

- 短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極の延びる方向に延びる2辺のそれぞれを横切る2つの矩形の延出部及び前記2辺を前記延出部が横切った幅よりも大きい幅を有したゲート電極上の膨出部を持った形状に形成され、

ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記延出部が横切る方向に二股状に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の二股部分の奥側に間隙をあけて進入しかつ進入先端部分を前記ゲート電極の延びる方向に延びた形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記2辺を前記延出部が横切った幅よりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする薄膜トランジスタ。 - 短冊状のゲート電極上にゲート絶縁膜を介してアイランド状の半導体能動膜が前記ゲート電極の延びる方向に延びる2辺のそれぞれを横切る2つの矩形の延出部及び前記2辺を 前記延出部が横切った幅よりも大きい幅を有したゲート電極上の膨出部を持った形状に形成され、

ソース電極が前記半導体能動膜上であって前記ゲート電極の一側方から半導体能動膜の前記膨出部に向けて延びかつ前記膨出部において前記延出部が横切る方向に二股状に延びた形状に形成され、前記半導体能動膜上であって前記ゲート電極の他の側方から半導体能動膜の前記膨出部に向けて前記ソース電極の二股部分の奥部に間隙をあけて進入した形状にドレイン電極が形成され、前記間隙をあけて対峙する前記ソース電極と前記ドレイン電極との間の部分に対応する半導体能動膜の部分がチャネル部とされてなり、前記2辺を前記延出部が横切った幅よりも前記ソース電極の前記ドレイン電極と対峙する辺の長さが長くされてなることを特徴とする薄膜トランジスタ。 - 一対の基板間に液晶が封入され、一方の基板に複数のソース配線と複数のゲート配線がマトリクス状に配線され、複数のソース配線と複数のゲート配線とで区画される領域にそれぞれスイッチング素子と画素電極とが設けられ、前記スイッチング素子が、請求項1ないし5のいずれかに記載の薄膜トランジスタからなることを特徴とする液晶表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP37218298A JP4100646B2 (ja) | 1998-12-28 | 1998-12-28 | 薄膜トランジスタおよびそれを備えた液晶表示装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP37218298A JP4100646B2 (ja) | 1998-12-28 | 1998-12-28 | 薄膜トランジスタおよびそれを備えた液晶表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000196098A JP2000196098A (ja) | 2000-07-14 |

| JP4100646B2 true JP4100646B2 (ja) | 2008-06-11 |

Family

ID=18500001

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP37218298A Expired - Lifetime JP4100646B2 (ja) | 1998-12-28 | 1998-12-28 | 薄膜トランジスタおよびそれを備えた液晶表示装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4100646B2 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4211250B2 (ja) * | 2000-10-12 | 2009-01-21 | セイコーエプソン株式会社 | トランジスタ及びそれを備える表示装置 |

| KR100391157B1 (ko) | 2001-10-25 | 2003-07-16 | 엘지.필립스 엘시디 주식회사 | 액정 표시 장치용 어레이 기판 및 그의 제조 방법 |

| KR100464208B1 (ko) * | 2001-12-20 | 2005-01-03 | 엘지.필립스 엘시디 주식회사 | 액정 표시장치 및 그 구동방법 |

| JP4604440B2 (ja) * | 2002-02-22 | 2011-01-05 | 日本電気株式会社 | チャネルエッチ型薄膜トランジスタ |

| KR100875182B1 (ko) | 2002-04-20 | 2008-12-22 | 엘지디스플레이 주식회사 | 액정표시장치 및 그 제조방법 |

| JP5004606B2 (ja) * | 2006-05-31 | 2012-08-22 | 株式会社ジャパンディスプレイイースト | 表示装置 |

| TWI328878B (en) | 2006-09-15 | 2010-08-11 | Au Optronics Corp | Electrode structure of a transistor, and pixel structure and display apparatus comprising the same |

| CN100483735C (zh) * | 2006-10-09 | 2009-04-29 | 友达光电股份有限公司 | 晶体管的电极结构和包括该结构的像素结构及显示装置 |

| JP2009049058A (ja) * | 2007-08-14 | 2009-03-05 | Hitachi Displays Ltd | 半導体装置および表示装置 |

| JP5628302B2 (ja) * | 2010-05-10 | 2014-11-19 | シャープ株式会社 | 半導体装置、アクティブマトリクス基板、及び表示装置 |

| US8536571B2 (en) * | 2011-01-12 | 2013-09-17 | Semiconductor Energy Laboratory Co., Ltd. | Manufacturing method of semiconductor device |

| JP2012178452A (ja) * | 2011-02-25 | 2012-09-13 | Japan Display East Co Ltd | 表示装置及び表示装置の製造方法 |

| WO2012169397A1 (ja) * | 2011-06-07 | 2012-12-13 | シャープ株式会社 | 薄膜トランジスタ、その製造方法、および表示素子 |

| JP6061536B2 (ja) * | 2012-07-30 | 2017-01-18 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN105895706A (zh) | 2016-07-01 | 2016-08-24 | 深圳市华星光电技术有限公司 | 薄膜晶体管及显示装置 |

| US11081507B2 (en) * | 2017-07-12 | 2021-08-03 | Sakai Display Products Corporation | Semiconductor device and method for manufacturing same |

| CN110870077A (zh) * | 2017-07-12 | 2020-03-06 | 堺显示器制品株式会社 | 半导体装置以及其制造方法 |

-

1998

- 1998-12-28 JP JP37218298A patent/JP4100646B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000196098A (ja) | 2000-07-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4100646B2 (ja) | 薄膜トランジスタおよびそれを備えた液晶表示装置 | |

| KR100507271B1 (ko) | 고개구율 및 고투과율 액정표시장치 및 그 제조방법 | |

| JP3742837B2 (ja) | フリンジフィールド駆動液晶表示装置及びその製造方法 | |

| JP2006317516A (ja) | 液晶表示装置及びその製造方法 | |

| JP2002229069A (ja) | 横電界スイッチング方式の液晶ディスプレイの電極配列構造 | |

| JP2001209070A (ja) | 液晶表示素子 | |

| KR102050460B1 (ko) | 박막 트랜지스터 기판 및 그를 이용한 디스플레이 장치 | |

| KR20130063102A (ko) | 산화물 반도체층을 갖는 박막트랜지스터 및 이를 구비한 어레이 기판 | |

| KR101323477B1 (ko) | 액정표시장치 및 그 제조 방법 | |

| KR100829786B1 (ko) | 횡전계 방식 액정표시장치용 어레이기판과 그 제조방법 | |

| JPWO2013061929A1 (ja) | 液晶表示素子および液晶表示装置 | |

| KR100807582B1 (ko) | 스토리지 커패시터 및 이를 구비한 액정 표시장치 | |

| KR100835975B1 (ko) | 횡전계방식 액정표시장치용 어레이기판과 그 제조방법 | |

| KR102068962B1 (ko) | 액정표시장치용 어레이 기판 | |

| JP2009080376A (ja) | 液晶表示装置 | |

| WO2014054563A1 (ja) | 半導体装置及び表示装置 | |

| KR101085150B1 (ko) | 횡전계 방식의 액정표시장치 및 그의 제조방법 | |

| KR101609826B1 (ko) | 프린지 필드 스위칭 모드 액정표시장치용 어레이 기판 | |

| KR100693365B1 (ko) | 액티브매트릭스 기판 및 표시장치 | |

| JP2003043523A (ja) | 薄膜トランジスタパネル | |

| JP2005019627A (ja) | 液晶表示装置 | |

| KR100336892B1 (ko) | Tft-lcd | |

| KR100311213B1 (ko) | 고개구율 및 고투과율 액정 표시 장치 및 그 제조방법 | |

| KR100773876B1 (ko) | 횡전계방식 액정표시장치용 어레이기판과 그 제조방법 | |

| KR100488923B1 (ko) | 액정표시소자 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041005 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060919 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061017 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080219 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080317 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110328 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110328 Year of fee payment: 3 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110328 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120328 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120328 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130328 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140328 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |