JP4059939B2 - パワーmosデバイス及びその作製方法 - Google Patents

パワーmosデバイス及びその作製方法 Download PDFInfo

- Publication number

- JP4059939B2 JP4059939B2 JP24125796A JP24125796A JP4059939B2 JP 4059939 B2 JP4059939 B2 JP 4059939B2 JP 24125796 A JP24125796 A JP 24125796A JP 24125796 A JP24125796 A JP 24125796A JP 4059939 B2 JP4059939 B2 JP 4059939B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- impurity

- power mos

- channel

- mos device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/113—Isolations within a component, i.e. internal isolations

- H10D62/115—Dielectric isolations, e.g. air gaps

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P30/00—Ion implantation into wafers, substrates or parts of devices

- H10P30/20—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping

- H10P30/202—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping characterised by the semiconductor materials

- H10P30/204—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping characterised by the semiconductor materials into Group IV semiconductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P30/00—Ion implantation into wafers, substrates or parts of devices

- H10P30/20—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping

- H10P30/208—Ion implantation into wafers, substrates or parts of devices into semiconductor materials, e.g. for doping of electrically inactive species

Landscapes

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

【発明が属する技術分野】

本明細書で開示する発明は、大電力制御用の絶縁ゲイト型半導体装置、特にパワーMOSデバイスとよばれる半導体装置およびその作製方法に関する。代表的にはMOSゲイト・デバイスであるパワーMOS・FET(以後、単にパワーMOSと略記する)やIGBT(Insurated Gate Bipolar Transistor )等が挙げられる。

【0002】

【従来の技術】

近年、半導体素子は益々微細化の一途を辿る傾向にあり、ディープサブミクロン領域の加工寸法が要求される様になっている。しかし、MOS・FETにおいてチャネル形成領域がディープサブミクロン領域の寸法になると短チャネル効果という現象が問題となることが知られている。

【0003】

短チャネル効果とは、ゲイト電極の線幅が短くなる、即ちチャネル形成領域が短くなるにつれて、チャネル形成領域の電荷がゲイト電圧だけでなく、ソース/ドレイン領域の空乏層電荷や電界および電位分布の影響を大きく受ける様になるために引き起こされる現象である。そして、短チャネル効果によりしきい値電圧の低下、サブスレッショルド特性の劣化、耐圧の劣化といった諸問題が発生することが知られている。

【0004】

この現象はチャネルを形成することで動作するMOS構造のデバイス全般に共通する問題であり、大電力制御用のパワーMOSデバイスにおいても例外ではない。パワーMOSデバイスは大電流、大電圧を扱うので高耐圧を必要とする場合が多く、短チャネル効果による耐圧の劣化は非常に大きな問題となる。

【0005】

一般的にパワーMOSデバイスとは電子機器のスイッチング素子などとして用いられる半導体装置(半導体素子)を指し、パワーMOS、IGBTなどの高速MOS系パワー・デバイスなどが知られている。これらは大電圧、大電流を扱うためにICやLSIとは構造が異なる点に特徴がある。

【0006】

ここで、パワーMOSの単一セルにおける基本的な構造を図2に示す。なお、図中において+や−で表す記号は導電性の相対的な強弱を示す指針として用いている。即ち、例えばN- よりもN+ の方が強いN型を示すことを表している。

【0007】

図2において、N+ 型を有する半導体基板201上にはエピタキシャル成長によりドリフト領域と呼ばれる弱いN型(N- )領域202が形成されている。このN型を有する半導体基板201はそのままドレイン領域として機能する。

【0008】

また、ドリフト領域202には強いP型(P+ )領域203が不純物拡散によって形成され、さらにその中にN+ 型を有するソース領域204が配置される。この強いP型領域203はゲイト電極直下の一部がチャネル形成領域として機能する。そして、半導体表面にはゲイト絶縁膜205を介してゲイト電極206が配置された構造となる。

【0009】

この様なパワーMOS構造の場合、ゲイト電極206に対して正の電圧を印加するとゲイト電極206近傍のP型領域(チャネル形成領域)203にチャネル領域207が形成されて矢印の方向に電流が流れる(エンハンスメント型のNチャネル型FETの場合)。

【0010】

この様に、ICやLSIに用いられるMOS・ICでは半導体基板の表面近傍において横方向に電流が流れる構成であるのに対し、図2に示すパワーMOSにおいては半導体基板を挟んでソース/ドレイン領域が配置されて縦方向に電流が流れる点に特徴がある。

【0011】

この様にパワーMOSで縦方向に電流が流れる様な構造とする理由はオン抵抗(ドレイン電流が流れる全ての領域の抵抗値)を小さくして電流密度を上げるためであり、大電流を扱い、高速動作を主旨とするパワーMOSには重要な構成の一つである。

【0012】

従って、高速動作特性を要求される場合はドリフト領域の比抵抗は小さいことが望ましく、逆に高耐圧特性を要求される場合はドリフト領域比抵抗を大きくして耐圧を向上させる工夫が成されていた。

【0013】

しかしながら、高速動作特性を要求される場合、ドリフト領域の比抵抗を小さくすると短チャネル効果による耐圧の劣化が発生した時に耐圧限界を超えて素子が破壊されるといった問題が起こり得る。

【0014】

ここで、パワーMOSに短チャネル効果が生じた場合の様子を簡略化して図3に示す。なお、図3は図2のチャネル領域207の周辺を拡大した図を表している。

【0015】

図3において、301は弱いN型(N- )で形成されるドリフト領域、302は強いP型(P+ )で形成されるチャネル形成領域、303は強いN型(N+ )で形成されるソース領域、304はチャネル領域、305はゲイト電極である。また、306で示される点線はドレイン電圧が小さい時に形成される空乏層を表している。

【0016】

通常、チャネル領域304を流れる電流はゲイト電圧のみで制御される。この場合、306で示される様に、チャネル領域304近傍の空乏層はチャネルに概略平行となり、均一な電界が形成される。

【0017】

しかし、ドレイン電圧が高くなると、ドリフト領域301近傍の空乏層がチャネル領域304、ソース領域303の方へと広がり、307で示される実線で表される様に、ドレイン空乏層の電荷や電界がソース領域303、チャネル領域304近傍の空乏層へと影響を及ぼす様になる。即ち、オン電流が複雑な電界分布により変化し、ゲイト電圧のみで制御することが困難な状況となるのである。

【0018】

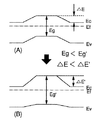

ここで、短チャネル効果が生じる場合におけるチャネル形成領域周辺のエネルギー状態を図4を用いて説明する。図4において実線で示す状態図はドレイン電圧が0Vの時のソース領域401、P型領域(チャネル形成領域)402、ドリフト領域403近傍のエネルギーバンド図である。

【0019】

この状態において十分大きいドレイン電圧Vdが印加されると、図4において点線で示す様な状態へと変化する。即ち、ドレイン電圧Vdにより形成されたドリフト領域の空乏層電荷や電界が、ソースおよびチャネル形成領域401、402の空乏層電荷に影響を与え、エネルギー(電位)状態はソース領域401からドリフト領域403にかけて連続的に変化する様になる。

【0020】

そして、このような短チャネル効果が半導体素子に与える影響として、しきい値電圧(Vth)の低下やパンチスルー現象が生じる。また、パンチスルー現象によってドレイン電流に対するゲイト電圧の影響が低下するとサブスレッショルド特性が悪くなる。

【0021】

まず、しきい値電圧の低下はNチャネル型FETに対してもPチャネル型FETに対しても同様に見られる現象である。また、この低下の度合いはドレイン電圧に依存するばかりでなく、基板不純物濃度、ソース/ドレイン拡散層深さ、ゲイト酸化膜厚、基板バイアス等の様々なパラメータに依存する。

【0022】

しきい値電圧の低下は消費電力を小さくするといった意味では望ましいことであるが、一般的には集積回路の駆動電圧が小さくなることで周波数特性が高くならないといったデメリットが問題となってしまう。

【0023】

そのため、これまではしきい値電圧を制御するための手段としてはチャネル形成領域全体に、均一に一導電性を付与する不純物元素を添加して、その添加量でもってしきい値電圧を制御するのが一般的であった。しかし、この方法でもやはり短チャネル効果自体を防ぐことはできず、パンチスルー現象などが発生してしまっていた。また、添加した不純物がキャリアを散乱させるのでキャリアの移動度を低下させる要因ともなっていた。

【0024】

また、パンチスルー現象に伴うサブスレッショルド特性の劣化とはサブスレッショルド係数(S値)が大きくなる、即ちFETのスイッチング特性が劣化することを意味している。ここでサブスレッショルド特性に及ぼす短チャネル効果の影響を図5に示す。

【0025】

図5は横軸にゲイト電圧Vg、縦軸にドレイン電流Idの対数をとったグラフであり、501の領域における傾き(サブスレッショルド特性)の逆数がS値である。この図5ではチャネル長を徐々に短くした時の特性の変化を比較しており、矢印の方向に向かってチャネル長は短くなっている。

【0026】

その結果、チャネル長が短くなるに従って特性の傾きが小さくなる、即ちS値が大きくなる傾向にあることが確認できる。このことは、チャネル長が短くなるに従って半導体素子のスイッチング特性が劣化することを意味する。

【0027】

【発明が解決しようとする課題】

以上の様に、短チャネル効果という現象はパワーMOSデバイスにおいても大きな問題であり、今後の微細化に向けて解決すべき問題である。

【0028】

特に、パワーMOSデバイスでは高速動作特性と高耐圧特性がトレードオフの関係にあり、高速動作特性に重きを置いた場合には短チャネル効果による耐圧の劣化が素子破壊の問題として顕在化する。

【0029】

そこで本明細書で開示する発明は、上記問題点を解決して、高速動作特性と高耐圧特性の両特性を同時に実現する絶縁ゲイト型半導体装置、特にパワーMOSデバイスおよびその作製方法を提供することを課題とする。

【0030】

【課題を解決するための手段】

本明細書で開示する発明の構成は、

結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

前記ドリフト領域より前記チャネル形成領域およびソース領域に向かって広がる空乏層をピニングするために人為的かつ局部的に形成された不純物領域と、

を有することを特徴とする。

【0031】

また、他の発明の構成は、

結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

不純物元素の添加により所定のしきい値電圧に制御するために人為的かつ局部的に形成された不純物領域と、

を有することを特徴とする。

【0032】

なお、本明細書において、結晶半導体とは現在のIC、LSIレベルで一般的に用いられている水準の単結晶シリコンを代表的な例としているが、さらに高水準の単結晶シリコン(究極的には宇宙空間で作製された様な理想状態の単結晶シリコン)もその範疇に含まれる。

【0033】

本発明の主旨は、チャネル形成領域に人為的かつ局部的に形成した不純物領域によりドリフト領域からチャネル形成領域に向かって広がる空乏層を効果的に抑制し、短チャネル効果によって引き起こされるパンチスルー現象、サブスレッショルド特性の劣化、耐圧の劣化などの諸問題を防止することにある。

【0034】

本出願人はあたかもチャネル形成領域に不純物領域のピンを形成することに似ていることから、本発明によるデバイスをピニング型パワーMOSデバイスと呼んでいる。なお、本明細書中において「ピニング」とは「抑止」を意味しており、「ピニングする」とは「抑止する」という意味で用いている。

【0035】

即ち、チャネル形成領域に対して局部的に不純物領域を形成し、その領域をエネルギー的な障壁として利用するものである。そして、不純物領域をエネルギー的な障壁として利用することでドリフト領域側の空乏層がチャネル形成領域側へ広がるのをエネルギー的に抑止し、それによってチャネル形成領域に形成される電界がゲイト電圧のみによって制御される様にする。

【0036】

本発明は上記構成をなすために不純物領域を形成する不純物元素としてエネルギーバンド幅(Eg)を広げる不純物元素を用いている。その様な不純物元素としては炭素(C)、窒素(N)、酸素(O)から選ばれた一種または複数種類の元素が挙げられる。

【0037】

この場合、添加された不純物はチャネル形成領域に局部的にエネルギーバンド幅の大きいエネルギー障壁を形成する。本発明の様に炭素、窒素、酸素を用いた場合には、図6(A)で示す状態であったエネルギーバンドを図6(B)で示す状態とし、エネルギーバンド幅(Eg)を広げることで障壁ΔEがさらに大きな障壁ΔE’となる。例えば、酸素を添加した場合には SiOx で示される様な構造の絶縁性の高抵抗領域となり電気的にも障壁となる。

【0038】

また、上記不純物元素以外にエネルギーバンド幅をシフトさせる不純物元素を用いることもできる。その様な不純物元素としては13族の元素(代表的にはボロン)や15族の元素(代表的にはリンまたは砒素)が挙げられる。本発明ではNチャネル型パワーMOSを作製する場合には13族元素を用い、Pチャネル型パワーMOSを作製する場合には15族元素を用いる。

【0039】

ただし、どちらを用いる場合もチャネル形成領域と不純物領域は同一導電型となるので、不純物領域の方の濃度を高くしておくことが望ましい。また、チャネル形成領域が実質的に真性である場合には、不純物領域の濃度を低くすることができる。

【0040】

この場合、添加された不純物はチャネル形成領域において局部的にエネルギーバンドをシフトさせる。例えば、Nチャネル型パワーMOSに対してボロンを添加した場合には、図7(A)で示す状態であったエネルギーバンドを図7(B)で示す状態とし、フェルミレベル(Ef)をシフトさせることで障壁ΔEがさらに大きな障壁ΔE’となる。勿論この場合、フェルミレベルをシフトさせることは結果的にチャネル形成領域のエネルギーバンドをシフトさせることに他ならない。

【0041】

また、この領域はチャネル領域とは逆の導電性を有し、抵抗値は低いもののエネルギー的には十分障壁となる。同様にPチャネル型パワーMOSに対してリンまたは砒素を添加した場合にも逆導電性領域が形成されてエネルギー障壁として活用することができる。

【0042】

また、他の発明の構成は、

結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

前記ドリフト領域より前記チャネル形成領域およびソース領域に向かって広がる空乏層をピニングし、かつ、該不純物領域によりキャリアの移動経路を規定するために人為的かつ局部的に形成された不純物領域と、

を有することを特徴とする。

【0043】

また、他の発明の構成は、

結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を少なくとも有する絶縁ゲイト型半導体装置であって、

前記チャネル形成領域はキャリアが移動する領域と、

不純物元素の添加により所定のしきい値電圧に制御し、かつ、キャリアの移動経路を規定するために人為的かつ局部的に形成された不純物領域と、

を有することを特徴とする。

【0044】

不純物領域はチャネル形成領域内においてドットパターン状に設けることもできるし、線状パターン形状に設けることも可能である。特に、不純物領域をチャネル方向(キャリアが移動する方向)と概略平行な線状パターン形状に設けた場合、不純物領域が側壁となってキャリアが移動するレールの様な機能を果たす。その結果キャリアの移動経路を規定するため、キャリア同士の衝突による散乱確率が低減されて移動度が向上するといった利点が生まれる。

【0045】

以上の様に、チャネル形成領域に人為的かつ局部的に不純物領域を形成することで、キャリアが移動する領域と、ドリフト領域からチャネル形成領域へ広がる空乏層をピニングするための不純物領域とを同一チャネル形成領域内に配置することで短チャネル効果による諸特性の劣化を防止することができる。

【0046】

また、チャネル長の微細化に伴う短チャネル効果に起因する代表的現象であるしきい値電圧の低下を、不純物領域間に人為的に狭チャネル効果を生じさせることで緩和してやることも本発明の重要な構成の一つである。

【0047】

狭チャネル効果とは、チャネル形成領域が狭くなることでしきい値電圧の増加などの症状が現れる現象であり、MOS・ICで問題となることが多い。本発明はこの現象を利用して意図的に狭チャネル効果を引き起こしてしきい値電圧を制御し、短チャネル効果に伴うしきい値電圧の低下を相殺する効果もある。

【0048】

また、他の発明の構成は、

結晶半導体を利用してソース領域、ドレイン領域ドリフト領域およびチャネル形成領域とを形成する工程と、

前記チャネル形成領域において人為的かつ局部的に不純物領域を形成する工程と、

前記チャネル形成領域上にゲイト絶縁膜およびゲイト電極とを形成する工程と、

を少なくとも有する絶縁ゲイト型半導体装置の作製方法において、

前記チャネル形成領域はキャリアが移動する領域と前記不純物領域とで構成され、

前記不純物領域にはエネルギーバンド幅(Eg)を広げる不純物元素が人為的かつ局部的に添加されていることを特徴とする。

【0049】

また、他の発明の構成は、

結晶半導体を利用してソース領域、ドレイン領域ドリフト領域およびチャネル形成領域とを形成する工程と、

前記チャネル形成領域において人為的かつ局部的に不純物領域を形成する工程と、

前記チャネル形成領域上にゲイト絶縁膜およびゲイト電極とを形成する工程と、

を少なくとも有する絶縁ゲイト型半導体装置の作製方法において、

前記チャネル形成領域はキャリアが移動する領域と前記不純物領域とで構成され、

前記不純物領域にはエネルギーバンド幅(Eg)をシフトさせる不純物元素が人為的かつ局部的に添加されていることを特徴とする。

【0050】

以上の構成でなる本発明について、以下に記載する実施例でもって詳細な説明を行うこととする。

【0051】

【実施例】

〔実施例1〕

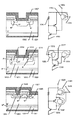

図1に示すのは本発明を利用したパワーMOS・FETの構造を示す一実施例図である。図1(A)はパワーMOSの上面図であり、本実施例には単一セル2個を記載するのみであるが通常はワンチップ上に数百〜数万個のセルが配置されてパワーMOSを構成している。

【0052】

そして、図1(B)は図1(A)をA−A’の破線で分断した時の分断面を示している。なお、図1(A)の右側のセルはその断面に不純物領域が見える様に切ってあり、左側のセルはその断面に不純物領域が見えない様に切ってある。また、図1(C)は図1(A)において100で示される円内の拡大図である。

【0053】

図1(B)において、101はドレイン領域となる半導体基板であり、本実施例ではNチャネル型FETを例にするためN+ 型のシリコン基板とする。102はエピタキシャル成長させたN- 型のシリコン層であり、ドリフト領域とて機能する。103はチャネル形成領域となるP+ 型の導電性領域で不純物拡散により形成する。そして、104はソース領域となるN+ 型の導電性領域である。

【0054】

なお、チャネル形成領域103はN- 型のシリコン層をP型を付与する不純物元素(例えばボロン)で反転させて形成するが、不純物元素の濃度を調節してちょうどN型の導電性を相殺する様にすれば実質的に真性なチャネル形成領域とすることも可能である。

【0055】

さらに、上記半導体層の上方には酸化珪素膜でなるゲイト絶縁膜105を介してポリシリコン膜でなるゲイト電極106が配置され、それを覆って珪化膜でなる層間絶縁膜107、導電性材料でなるソース電極108が形成されており、ドレイン領域101側には導電性材料でなるドレイン電極109が形成された構成となっている。

【0056】

ここまでの説明は代表的なパワーMOS構造である縦型二重拡散構造の説明にすぎない。本発明の特徴はチャネル形成領域(P+ 型(又は実質的にI型)の導電性領域103とゲイト電極106とが重畳する領域)に対して、エネルギー障壁を形成するための不純物領域110を形成する点にある。

【0057】

不純物領域110は炭素、窒素、酸素から選ばれた一種または複数種類の元素を用いても良いし、本実施例の様にNチャネル型FETならば13族元素であるボロンを用いても良い。本実施例では不純物元素として酸素を用いた場合を説明する。

【0058】

不純物元素として酸素を用いた場合、不純物領域は例えば SiOX で示される絶縁性領域を形成する。この様な不純物領域はエネルギーバンド幅を広げてエネルギー障壁として振る舞うため、ドリフト領域102からチャネル形成領域111へと広がる空乏層を効果的に抑制(ピニング)する。

【0059】

また、不純物領域110は極めて微細な領域であるので、通常の露光法よりも電子描画法やFIB法といった微細リソグラフィ技術を利用することが望ましい。この様に、チャネル形成領域全域に不純物注入を行うのではなく、人為的かつ局部的に不純物領域を形成する点に従来のチャネルドープとの相違がある。

【0060】

不純物領域110を形成する位置はパワーMOSの上面から見ると、図1(A)の様になっている(図1(B)において不純物領域が図中に示す様に見えるのは線状パターンを縦に切断した断面を見ているからである)。

【0061】

図1(A)において、111で示される閉じた領域は全てP+ 型の導電性領域103とゲイト電極106とが重畳する領域であり、チャネル形成領域を構成している。また、キャリアの流れる方向は112で示される矢印の方向であり、線状パターン形状の不純物領域がキャリアの流れる方向(チャネル方向)と概略平行になる様に配置されている。なお、本実施例ではNチャネル型FETを例にしているのでキャリア(電子)の流れる方向と電流の方向とは逆向きである。

【0062】

また、図1(A)の左側の図が示す様に、本明細書では「チャネル形成領域111の中心線を辿って一周した距離」をチャネル幅Wとし、「チャネル形成領域をキャリアが横切る距離」をチャネル長Lとして考える。

【0063】

本実施例ではチャネル形成領域111に線状パターン形状の不純物領域を形成することに特徴があるが、線状パターンにはある範囲の条件を満たす必要がある。そのことについての説明を行う。

【0064】

まず、チャネル幅Wの内、不純物領域110が占有している幅をW pi, n と定義する。W pi, n の値としては例えば10〜100Åもあれば十分である。また、図1(C)に示す様に任意の不純物領域110の幅をWpi,1、Wpi,2、Wpi,3・・・Wpi,nとすると、Wpiは次式で表される。

【0065】

【数1】

【0066】

但し、本発明の構成を達成するためにはチャネル形成領域の端部以外の領域に、不純物領域が少なくとも一つ形成されている必要があるのでnは1以上の整数である。

【0067】

また、チャネル幅Wの内、不純物領域110間の領域(電流の流れるパス)が占有している幅をW pa, m と定義する。W pa, m の値としては例えば100 〜3000Å(代表的には500 〜1500Å)とすることができる。また、図1(C)に示す様に任意の不純物領域110間の領域をWpa,1、Wpa,2、Wpa,3・・・Wpa,mとすると、Wpaは次式で表される。

【0068】

【数2】

【0069】

但し、前述の様にチャネル形成領域の端部以外の領域に不純物領域が少なくとも一つ形成されているので、チャネル形成領域は少なくとも2分されてmは2以上の整数となる。

【0070】

即ち、全チャネル幅WはW=Wpi+Wpa、かつ、n+mは3以上という関係が成り立っている。そして、WとWpi、WとWpaおよびWpiとWpaとの関係は、同時に以下の条件を満たすことが望ましい。

Wpi/W=0.1 〜0.9

Wpa/W=0.1 〜0.9

Wpi/Wpa=1/9 〜9

【0071】

これらの数式の意味するところは、Wpa/WまたはWpi/Wが0または1であってはならないという事である。例えば、Wpa/W=0(Wpi/W=1と同義)の場合、チャネル形成領域を完全に不純物領域で塞いでしまうので電流の流れるパスが存在しない状態となる。

【0072】

逆にWpa/W=1(Wpi/W=0と同義)の場合、チャネル形成領域に不純物領域が全く存在しないのでドリフト領域から広がる空乏層を抑えることができない。

【0073】

以上の理由により、Wpa/WおよびWpi/Wの関係式は0.1 〜0.9 (好ましくは0.2 〜0.8 )の範囲に収まり、また、同時にWpi/Wpa=1/9 〜9 を満たすことが望ましい。

【0074】

ここで、本発明を利用してパワーMOSを作製した場合において、短チャネル効果がどの様に抑制されるかを図8を用いて説明する。なお、図8(A)は図3と同一構造のチャネル形成領域を示す拡大図(符号は図3と同じものを用いる)である。

【0075】

まず、図1に示す様な構造を有するパワーMOSに対してゲイト電圧、ドレイン電圧を印加した場合には、図8(A)に示す様な状態でソース領域303近傍の空乏層801、チャネル領域304近傍の空乏層802、ドリフト領域301近傍の空乏層803が形成される。即ち、ドリフト領域301近傍の空乏層803は不純物領域804が障壁となって、チャネル領域304近傍において広がりを防止された形となる。

【0076】

図8(A)では判りにくいが不純物領域804は図1(A)の右側の図に示す様に配置されているので、チャネル形成領域を塞ぐ格子状のフィルターでドリフト領域301の空乏層の広がりを抑えているというモデルで考えれば理解しやすい。

【0077】

従って、本発明による構造のパワーMOSにおいては、図8(A)に示す様に空乏層が実質的に相互に干渉することなく分断される。即ち、ソース領域303近傍の空乏層801、チャネル領域304近傍の空乏層802が、ドリフト領域301近傍の空乏層803の影響を殆ど受けないで分布する。

【0078】

即ち、図4に示した従来のエネルギー状態図と異なり、チャネル領域304のエネルギー状態は殆どゲイト電圧による電界のみに制御されるので、チャネル領域304に対して概略平行な形状を有する。従って、短チャネル効果特有のパンチスルー現象の様な問題がなく、高い耐圧特性を有するパワーMOSを実現することができる。

【0079】

さらに、図3と図8(A)とを比較すると明らかな様に、本発明においては空乏層の占める体積が、図3に示した様な従来のものと比べて減少しているため、従来よりも空乏層電荷が小さく、空乏層容量が小さい特徴がある。ここで、S値を導出する式は次式で表される。

【0080】

【数3】

【0081】

即ち、前述の様に、図5に示すグラフにおいて501で示される領域における傾きの逆数を表していることが判る。また、数3の式は近似的に次式の様に表すことができる。

【0082】

【数4】

【0083】

数4において、kはボルツマン定数、Tは絶対温度、qは電荷量、Cd は空乏層容量、Citは界面準位の等価容量、Coxはゲイト酸化膜容量である。従って、本発明によれば空乏層容量Cd が従来よりも十分小さくなるので、S値を85mV/decade 以下(好ましくは70mV/decade 以下)の小さな値とすることができる、即ち優れたサブスレッショルド特性を得ることができるのである。

【0084】

また、本発明が目指すところは、空乏層容量Cd および界面準位の等価容量Citを0に可能な限り近づけることである。即ち、Cd =Cit=0となる理想状態におけるS値(60mV/decade )に近づけることにある。

【0085】

また、本発明において線状パターン形状を有する不純物領域を図1(A)に示す様に配置することはFETの性能を示す代表的なパラメータである移動度の向上に対して非常に大きな意味がある。その理由について以下に説明する。

【0086】

移動度は半導体(本実施例ではシリコン基板)中のキャリアの散乱によって決まるが、シリコン基板における散乱は格子散乱と不純物散乱とに大別される。格子散乱はシリコン基板中の不純物濃度が低く、比較的高温で支配的であり、不純物散乱は不純物濃度が高く、比較的低温で支配的である。これらが影響し合って形成される全体的な移動度μは次式で表される。

【0087】

【数5】

【0088】

この数5で示される式は、全体的な移動度μが、格子散乱の影響を受けた場合の移動度μl ( lはlattice を意味する) の逆数および不純物散乱の影響を受けた場合の移動度μi ( iはimpurityを意味する) の逆数の和に反比例することを意味している。

【0089】

ここで、格子散乱ではドリフト電界がそれほど強くなければ音響フォノンが重要な役割を果たし、その時の移動度μl は、次式の様に温度の-3/2乗に比例する。従って、キャリアの有効質量(m*)と温度(T)で決まってしまう。

【0090】

【数6】

【0091】

また、不純物散乱による移動度μi は、次式の様に温度の3/2 乗に比例し、イオン化した不純物の濃度Ni に逆比例する。即ち、イオン化した不純物の濃度Ni を調節することで変化させることができる。

【0092】

【数7】

【0093】

これらの式によると、従来の様にチャネル形成領域全体に不純物を添加するチャネルドープでは不純物散乱の影響を受けて移動度を稼ぐことができない。しかしながら、本発明では局部的に不純物領域を形成しているので、隣接する不純物領域の間(Wpaの幅を持つ領域) には不純物が添加されない。

【0094】

即ち、理論的には数7においてイオン化した不純物の濃度Ni を限りなく0に近づけることを意味するため、移動度μi は限りなく無限大に近づいていくことになる。即ち、数5において1/μi の項を無視することができる程度にまで不純物を減少させることを意味するので全体の移動度μは限りなく移動度μl に近づいていく。

【0095】

また、キャリアの有効質量(m*)を小さくすることで移動度μl をさらに大きくすることも理論的には可能である。これは極低温の領域において、キャリア(特に電子の場合)の有効質量が結晶軸の軸方位に依存して変化する現象を利用することで成しうる。

【0096】

文献によれば、キャリアの移動する方向が単結晶シリコンの<100>軸方向と一致する様に構成した時、最小の有効質量を得ることができる。但し、この例は4°Kという極低温領域における結果である。

【0097】

また、結晶格子間をうまくキャリアがすり抜けて行ける様に、チャネル方向および不純物領域110の軸方向(配列方向)と、結晶格子の軸方向とを概略平行(軸方向のずれを±10°以内に収める)にさせることが望ましい。単結晶ならばシリコン原子は規則正しく配列しているので、結晶格子の配列方向と平行に移動するキャリアは格子散乱の影響を殆ど受けないで済む。

【0098】

例えば、単結晶シリコン基板において上記の様な方向における回転軸を0°とすると、他にも90°、180°、270°の回転軸の場合において同様の効果を得ることができる。従って、図1(A)の様にキャリアが移動するパワーMOSにおいては、角を除く全ての方向で上記構成を成すことが可能である。

【0099】

以上の様に、チャネル形成領域を移動するキャリアはチャネル形成領域内に存在する不純物領域以外の領域を通る。このキャリアが移動する経路(以後、この領域をレーン領域と呼ぶ)のエネルギー状態は線状パターン形状の不純物領域によって図9に示す状態となっていると考えられる。

【0100】

図9(A)において、901、902で示される領域は不純物領域のエネルギー状態を示しており、エネルギー的に高い障壁となっている。そして、不純物領域から離れるに従って徐々にエネルギー的に低い領域903となる。即ち、チャネル領域を移動するキャリア(ここでは電子を例にとる)は903で示されるエネルギー状態の低い領域を優先的に移動し、901、902で示されるエネルギー障壁(不純物領域)は壁の様な役割を果たす。

【0101】

ここで、チャネル領域を移動するキャリア(電子)のイメージを模式的に図9(B)で表す。イメージ的には、チャネル領域を移動するキャリア900は図9(B)に表す様にまるで雨樋の中を転がる球体の様にその方向性が規定され、ソース領域からドレイン領域に向かってほぼ最短距離を移動する。

【0102】

また、図9(B)に示す様に、チャネル形成領域には図9(A)に示した様なレーン領域が複数並列に配置されて構成されているが、901、902で示される領域を越えることがないため、隣接するレーン領域との間においてキャリアの移動は行われない。

【0103】

以上の理由によりキャリアが他のキャリアと衝突する確率は大幅に減少するため、移動度が大幅に向上する。即ち、本発明の構成は不純物散乱を低減するのみならず、キャリア同士の自己衝突による散乱をも低減することで大幅な移動度の向上を実現することができる。

【0104】

この様に従来においては常に悪影響を及ぼすとされてきたエネルギー障壁(グレインバンダリーなど)を逆に意図的に形成して利用するという本発明の発想は非常に新しいものである。

【0105】

また、チャネル形成領域111に対して図1(A)、図1(C)に示す様に不純物領域110を配置することは短チャネル効果によるしきい値電圧の低下を低減する上で非常に重要である。なぜならば、この構成が意図的に狭チャネル効果を生み出すために必要な構成だからである。

【0106】

例えば、図1(A)に示す様にチャネル形成領域111のチャネル幅Wは不純物領域110によって分断され、実質的に狭いチャネル幅Wpa,mを有する複数のチャネル形成領域の集合体と見なすことができる。

【0107】

即ち、その複数の狭いチャネル幅Wpa,mを有する領域において狭チャネル効果が得られるのである。マクロ的に見ると図1(A)に示す様にチャネル形成領域全域においてこの様にして狭チャネル効果が得られるので、全体的に狭チャネル効果が得られる構成となり、しきい値電圧が増加するのである。

【0108】

従って、チャネル長が短くなることで短チャネル効果によってしきい値電圧が低下したとしても、以上の理由により狭チャネル効果によってしきい値電圧を意図的に増加させてしきい値制御を行うことができるので、結果的にしきい値電圧の変化を緩和することが可能となる。

【0109】

〔実施例2〕

本実施例では、チャネル形成領域に形成する不純物領域の形状をドットパターン状とする場合の例を示す。説明は図10を用いて行う。

【0110】

図10に示すパワーMOSの構造は、図1において線状パターン形状を有する不純物領域をドットパターン形状に置き換えたものである。まず、図1と異なるのは図10(B)に示す様に不純物領域1001が配置される点である。

【0111】

そして、不純物領域1001を上面から見たときの拡大図は図10(C)に示す様になる。なお、本実施例ではドットパターン状の不純物領域の例として円形の不純物領域を記載しているが、楕円形、正方形、長方形などであっても構わない。

【0112】

例えば、図11(A)に示す様に不純物領域1101が交互に噛み合う様に配置したパターンとすることができる。この場合、不純物領域1101間の隙間を次の列で補う構成となるので、空乏層の広がりを効果的に抑制することができる。この構成は、チャネル長が特に短い領域において効果を発揮する。

【0113】

また、図11(B)に示す様に、不純物領域をチャネル方向と垂直な楕円形とすることも、空乏層を広がりを抑えるためには非常に有効な構成である。

【0114】

〔実施例3〕

本発明において、チャネル形成領域に不純物領域を形成する手段として、不純物の偏析作用を利用した方法をとることもできる。本実施例では、その様な例として熱酸化膜近傍におけるボロン(B)およびリン(P)の偏析を利用した方法について図14を用いて説明する。

【0115】

実施例1に示した構造のパワーMOSを作製するに際して、酸素を添加することによって不純物領域を形成した後に800 〜1100℃程度の加熱処理を行うと、添加された酸素とシリコン(Si)とが反応して熱酸化物が形成される。

【0116】

そして、不純物領域の周辺に含有されていた不純物元素(ボロンまたはリン))が酸化物領域に偏析する。ここで、熱酸化工程により熱酸化膜/シリコン界面近傍のボロンまたはリンの濃度がどの様な分布を示すかを図14を用いて説明する。

【0117】

図14に示す様に、Si中に存在する添加イオン(B、P)は酸化膜が形成されると再分布する。これは、シリコン(Si)中および熱酸化膜( SiOx )中において添加イオンの溶解度と拡散速度が異なるために起こる現象である。不純物のSi中における溶解度を [C] Siとし、 SiOx 中における溶解度を [C] SiOxとする時、平衡偏析係数mは次式で定義される。

m= [C] Si/ [C] SiOx

【0118】

この時、Si/SiOx 界面近傍の不純物の偏析はmの値に支配される。通常、Si中における不純物の拡散係数が十分大きいとして、m<1の場合、Si中の不純物はSiO2中に取り込まれる(図14(A))。また、m>1の場合、SiO x が不純物を排斥し、その結果としてSi/SiOx 界面近傍の不純物濃度が増大する(図14(B))。

【0119】

文献値によると、ボロンのmの値は0.3 程度であり、リンのmの値は10程度である。従って、本実施例における熱酸化工程後のボロンの濃度分布は図14(A)の様になり、熱酸化膜中にボロンが取り込まれ、不純物領域の側面(Si/SiOx 界面近傍)におけるボロン濃度は極めて微量な状態となる。また、逆に形成された熱酸化物中には多量のボロンが含有される。

【0120】

この様な熱酸化膜中へのボロンの取込み現象は既に知られていたが、本発明の様にエネルギー障壁(不純物領域)を形成するためにこの現象を利用する発想は全く新しいものである。

【0121】

なお、図14(B)に示す様に、不純物元素としてリンを用いた場合には熱酸化膜とシリコンとの界面に偏析(パイルアップ)する。この現象もまた、Pチャネル型FETに不純物領域を形成する際に活用することができる。

【0122】

以上の様に、本実施例の様な酸化物へのリンまたはボロンの偏析現象を利用することで大幅な移動度の向上を図ることが可能である。なぜならば、本実施例を実施すると不純物領域(代表的には SiOX で示される酸化物)周辺の不純物(リンまたはボロン)が不純物領域に収集されてしまうので、不純物領域間のキャリアが移動する領域における不純物散乱の影響を極めて少なくすることができるからである。

【0123】

このことは、先にも述べた様に数5においてμi が大きくなることに相当するので、全体の移動度μは理想的にμ=μl に近づいていく。即ち、実質的に格子散乱のみで決まる極めて大きな移動度を実現しうることを示す。

【0124】

〔実施例4〕

本明細書においてはパワーMOS・FETを代表例として説明してきたが、本発明はその他のパワーMOSデバイス全般に適用することが可能である。他のパワーMOSデバイスとしては、例えばIGBT(Insurated Gate Bipolar Transistor )、MCT(CMOS Cntrolled Tyristor )、EST(Emitter Swicthed Tyristor )、BRT(Base Resistance controlled Tyristor )、IEGT(Injection Enhanced Insurated Gate Bipolar Transistor)、DGMOS(Double Gate MOS )などが挙げられる。特に、最近ではパワーMOS・FET、IGBTの応用製品としてIPM(Intelligent Power Module)、パワーICなどが主流となってきている。

【0125】

本実施例では、上記パワーMOSデバイスの内、IGBT、MCT、ESTについて簡単な説明を行う。説明は図12を用いて行うこととする。

【0126】

まず、IGBTとはMOS・FETの高速スイッチング特性と、バイポーラトランジスタの低オン電圧特性をワンチップに構成したパワーデバイスである。図12(A)に示すNチャネル型IGBTの基本構造においてパワーMOS・FETと異なる点は、ドレイン側のN+ 領域をP+ 領域1201に置き換えてpn接合を1個追加してある点である。

【0127】

駆動時にはP+ 領域1201からドリフト領域となるN- 領域1202へとホール(正孔)が打ち込まれ、N- 領域1202の電子を引きつけるため、N- 領域1202の電子密度が増加する。そのため、N- 領域1202の抵抗は極めて低くなり、結果的にパワーMOSよりも低い電圧でオンするという特徴を有する様になるのである。

【0128】

このIGBTはP+ 領域1201とN- 領域1202との間にバッファ層としてN+ 領域を挟み込んだ構造の非ラッチアップ構造や、トレンチ技術を用いてチップ単位面積当たりのセル数を向上させたトレンチ構造など、他にも様々な構造のものが開発されている。

【0129】

なお、図12(A)の左側の図はIGBTの等価回路であり、1203がゲイト端子、1204はエミッタ端子、1205はコレクタ端子である。1206はP+ 領域1201とエミッタ電極1207との間の抵抗である。また、1208で示されるのはNチャネル・エンハンスメント型のトランジスタである。

【0130】

次に、MCTについての説明を行う。なお、本実施例では主流であるPチャネル・エンハンスメント型MCTについての説明を行う。図12(B)に示す様に、MCTの構造は縦型三重拡散構造で、N+ 型のシリコン基板1209にP+ 型シリコン層1210とP- 型シリコン層1211をエピタキシャル成長させて構成する。

【0131】

さらに、N型拡散層1212、P型拡散層1213を形成した後、P+ 型拡散層1214、N+ 型拡散層1215を形成して三重拡散構造とする。なお、例えばN型とはN+ 型よりも弱く、N- 型よりも強い導電性を有することを意味している。

【0132】

Pチャネル・エンハンスメント型MCTの特徴としては、オン電圧が低いにも関わらず耐圧が高いことであり、本発明を適用することでさらに信頼性の高い高耐圧特性を得ることが可能である。

【0133】

なお、図12(B)の左側の図はMCTの等価回路であり、1216がゲイト端子、1217はアノード端子、1218はカソード端子である。また、1219はPチャネル・エンハンスメント型トランジスタ(ON FETと呼ばれる)であり、1220はNチャネル・エンハンスメント型トランジスタ(OFF FET と呼ばれる)である。

【0134】

次に、ESTについての説明を行う。ESTはIGBTとサイリスタを横に並べた構成となっており、縦型二重拡散構造となっている。また、図12(C)に示す様に、ESTはP+ 型のシリコン基板1221にN+ 型シリコン層1222とN- 型シリコン層1223をエピタキシャル成長させて構成する。

【0135】

さらに、P- 型拡散層1224、P+ 型拡散層1225を形成した後、N+ 型拡散層1226、1227を形成した構成とする。ESTの特徴としては、MCT同様、オン電圧が低いにも関わらず耐圧が高いことであり、本発明を適用することでさらに信頼性の高い高耐圧特性を得ることが可能である。

【0136】

なお、図12(C)の左側の図はESTの等価回路であり、1228がゲイト端子、1229はカソード端子、1230はアノード端子である。また、1231、1232は共にNチャネル・エンハンスメント型トランジスタである。

【0137】

以上の様に、本発明はゲイト絶縁型(MOSゲイト型)のあらゆるパワーMOSデバイスに応用することが可能であり、その応用範囲は産業上、極めて広範囲に渡るものである。

【0138】

〔実施例4〕

本発明を利用して作製したパワーMOSデバイスは極めて応用範囲の広いデバイスである。本実施例では、その代表的な例を簡単な図を用いて説明する。説明には図13を用いる。

【0139】

図13(A)に示すのはビデオデッキであり、1301は本体、1302はテープ挿入部、1303は外部端子部、1304は画像編集ダイアル、1305は液晶表示部である。また、1306はビデオデッキ内部に組み込まれた集積化回路で、その中のパーツとしてパワーモジュールが組み込まれ、その構成デバイスとしてパワーMOSデバイス1307が用いられる。

【0140】

また、図13(B)に示すのは電池式シェーバーであり、1308は本体、1309はスイッチ、1310はシェイビング部である。また、1311はシェーバー内部に組み込まれた充電器であって、電池式シェーバーの電流制御用にパワーMOSデバイス1312が用いられる。

【0141】

また、図13(C)に示すのは蛍光灯であり、1313は蛍光灯、1314はかさ、1315は制御部である。また、1316は蛍光灯内部に組み込まれた集積化回路であって、蛍光灯のインバータ制御用にパワーMOSデバイス1317が用いられる。

【0142】

また、図13(D)に示すのは電導工具であり、1318は本体、1319はドリル、1320はハンドリング部、1321はコンセントである。また、1322は蛍光灯内部に組み込まれた集積化回路であって、電導工具の速度制御用にパワーMOSデバイス1323が用いられる。

【0143】

以上示した他にも、パワーMOSデバイスは自動車の車両制御系および車体系装置、テレビ、カメラ、コンピュータ用電源、空調装置、プラグラマブル・ロジック・コントロールなどあらゆる分野の製品に用いられており、極めて応用範囲の広いデバイスである。

【0144】

【発明の効果】

本発明を利用することでチャネル長が短くなった場合に生じる短チャネル効果を防止することが可能となる。具体的には、まずドリフト領域近傍の空乏層がソース領域やチャネル形成領域下に広がるのを、チャネル形成領域に局部的に形成した不純物領域で遮り、チャネル形成領域のエネルギー(電位)状態にドレイン電圧が影響しない構成とする。これによりパンチスルー現象やサブスレッショルド特性の劣化を防止することが可能となる。また、同時に高いドレイン耐圧を実現することができる。

【0145】

また、短チャネル効果の特徴の一つであるしきい値電圧の低下を狭チャネル効果によるしきい値電圧の増加によって抑制することができる。この狭チャネル効果は、チャネル形成領域に局部的に不純物領域を形成するという本発明の構成によって人為的に成しうる効果である。

【0146】

以上の様に、本発明を利用することでチャネル長の短いディープサブミクロン領域におけるパワーMOSデバイスにおいても、短チャネル効果を引き起こすことなく動作させることができる。

【0147】

また、本発明ではチャネル形成領域にエネルギー的にスリット状のレーン領域を形成することでキャリアの移動方向を規定し、キャリア同士の自己衝突による散乱を低減することが可能である。

【0148】

即ち、キャリアの移動度低下を招く原因となる不純物散乱、格子散乱、キャリア同士の自己衝突による散乱が大幅に低減され、移動度が大きく向上する。

【0149】

以上の効果により、高速動作特性と高耐圧特性とを同時に実現できるパワーMOSデバイスを作製することが可能となる。従って、パワーMOSデバイスを用いるあらゆる分野の電子・電気機器の性能を向上させることができる。従って、本発明は工業・産業上、非常に有益な技術であると言える。

【図面の簡単な説明】

【図1】 パワーMOSデバイスの構造を示す図。

【図2】 パワーMOSデバイスの構造を示す図。

【図3】 パワーMOSデバイスの構造を示す図。

【図4】 エネルギー状態を説明するための図。

【図5】 MOSデバイスの電気特性を示す図。

【図6】 エネルギー状態を説明するための図。

【図7】 エネルギー状態を説明するための図。

【図8】 パワーMOSデバイスの構造を示す図。

【図9】 キャリアの挙動を説明するための図。

【図10】 パワーMOSデバイスの構造を示す図。

【図11】 不純物領域の配置パターンを示す図。

【図12】 パワーMOSデバイスの構造を示す図。

【図13】 パワーMOSデバイスの応用製品を示す図。

【図14】 不純物の偏析状態を説明するための図。

【符号の説明】

101 N+ 型半導体基板

102 N- 型半導体基板

103 P+ 型半導体基板

104 N+ 型半導体基板

105 ゲイト絶縁膜

106 ゲイト電極

107 層間絶縁膜

108 ソース電極

109 ドレイン電極

110 不純物領域

111 チャネル形成領域

112 キャリアの流れる方向

304 チャネル領域

306 ドレイン電圧が小さい時の空乏層

307 ドレイン電圧が大きい時の空乏層

Claims (27)

- 結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を有し、

前記チャネル形成領域にはボロンが添加されており、

前記チャネル形成領域はキャリアが移動する領域と、

前記ドリフト領域より前記チャネル形成領域および前記ソース領域に向かって広がる空乏層をピニングする不純物領域と、を有し、

前記不純物領域は、偏析した前記ボロンを含む熱酸化物を有することを特徴とするパワーMOSデバイス。 - 結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を有し、

前記チャネル形成領域にはボロンが添加されており、

前記チャネル形成領域はキャリアが移動する領域と、

前記ドリフト領域より前記チャネル形成領域および前記ソース領域に向かって広がる空乏層をピニングし、かつ、キャリアの移動経路を規定する不純物領域と、を有し、

前記不純物領域は、偏析した前記ボロンを含む熱酸化物を有することを特徴とするパワーMOSデバイス。 - 結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を有し、

前記チャネル形成領域にはボロンが添加されており、

前記チャネル形成領域はキャリアが移動する領域と、

不純物元素の添加により形成され、しきい値電圧を制御するための不純物領域と、を有し、

前記不純物領域は、偏析した前記ボロンを含む熱酸化物を有することを特徴とするパワーMOSデバイス。 - 結晶半導体を利用して形成されたソース領域、ドレイン領域、ドリフト領域およびチャネル形成領域と、

前記チャネル形成領域上に形成されたゲイト絶縁膜およびゲイト電極と、

を有し、

前記チャネル形成領域にはボロンが添加されており、

前記チャネル形成領域はキャリアが移動する領域と、

不純物元素の添加により形成され、しきい値電圧を制御し、かつ、キャリアの移動経路を規定する不純物領域と、を有し、

前記不純物領域は、偏析した前記ボロンを含む熱酸化物を有することを特徴とするパワーMOSデバイス。 - 請求項1または請求項2において、

前記不純物領域にはエネルギーバンド幅(Eg)を広げる不純物元素が添加されていることを特徴とするパワーMOSデバイス。 - 請求項3または請求項4において、

前記不純物元素はエネルギーバンド幅(Eg)を広げることを特徴とするパワーMOSデバイス。 - 請求項5または請求項6において、

前記不純物元素は酸素であることを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項4のいずれか一項において、

前記キャリアが移動する領域においてはキャリアの不純物散乱を防止する手段若しくはキャリアの格子散乱以外の要因による移動度低下を防止する手段が施されていることを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項4のいずれか一項において、

前記チャネル形成領域の幅Wに対して前記不純物領域および前記不純物領域間の幅が占有する割合をそれぞれWpi、Wpaとする時、前記W、前記Wpiおよび前記Wpaとの間には、Wpi/W=0.1〜0.9、Wpa/W=0.1〜0.9、Wpi/Wpa=1/9〜9の関係式が成り立つことを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項4のいずれか一項において、

前記チャネル形成領域のチャネル方向に垂直な少なくとも一断面は、実質的に前記不純物領域により区切られた複数のチャネル形成領域の集合体と見なせることを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項4のいずれか一項において、

前記チャネル形成領域において駆動時に生じる短チャネル効果に伴うしきい値電圧の低下は、前記不純物領域を利用することで得られる狭チャネル効果に伴うしきい値電圧の増加により緩和されることを特徴とするパワーMOSデバイス。 - 請求項1または請求項3において、

前記不純物領域はドットパターン形状を有していることを特徴とするパワーMOSデバイス。 - 請求項12において、

前記ドットパターン形状は、円形、楕円形、正方形、長方形、交互にかみ合うように配置したパターン形状のいずれか一であることを特徴とするパワーMOSデバイス。 - 請求項2または請求項4において、

前記不純物領域はチャネル方向と概略平行に形成された線状パターンであることを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項14のいずれか1項において、

前記ドリフト領域は、前記ソース領域より弱い導電性を有することを特徴とするパワーMOSデバイス。 - 請求項1乃至請求項15のいずれか1項において、

前記結晶半導体は単結晶シリコンであることを特徴とするパワーMOSデバイス。 - 結晶半導体を利用してソース領域、ドレイン領域、ドリフト領域およびボロンが添加されたチャネル形成領域を形成する工程と、

前記チャネル形成領域に不純物領域を形成する工程と、

前記チャネル形成領域上にゲイト絶縁膜およびゲイト電極を形成する工程と、

を少なくとも有するパワーMOSデバイスの作製方法において、

前記チャネル形成領域はキャリアが移動する領域と前記不純物領域とで構成され、

前記不純物領域はエネルギーバンド幅(Eg)を広げる不純物元素を添加することによって形成され、前記不純物元素の添加後、加熱処理を行うことにより、偏析した前記ボロンを含む熱酸化物が形成されることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記不純物元素は酸素であることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記キャリアが移動する領域においてはキャリアの不純物散乱を防止する手段若しくはキャリアの格子散乱以外の要因による移動度低下を防止する手段が施されていることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記チャネル形成領域の幅Wに対して前記不純物領域および前記不純物領域間の幅が占有する割合をそれぞれWpi、Wpaとする時、前記W、前記Wpiおよび前記Wpaとの間には、Wpi/W=0.1〜0.9、Wpa/W=0.1〜0.9、Wpi/Wpa=1/9〜9の関係式が成り立つことを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記チャネル形成領域のチャネル方向に垂直な少なくとも一断面は、実質的に前記不純物領域により区切られた複数のチャネル形成領域の集合体と見なせることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記チャネル形成領域において駆動時に生じる短チャネル効果に伴うしきい値電圧の低下は、前記不純物領域を利用することで得られる狭チャネル効果に伴うしきい値電圧の増加により緩和されることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記不純物領域はドットパターン形状を有していることを特徴とするパワーMOSデバイスの作製方法。 - 請求項23において、

前記ドットパターン形状は、円形、楕円形、正方形、長方形、交互にかみ合うように配置したパターン形状のいずれか一であることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17において、

前記不純物領域はチャネル方向と概略平行に形成された線状パターンであることを特徴とするパワーMOSデバイスの作製方法。 - 請求項17乃至請求項25のいずれか1項において、

前記ドリフト領域は、前記ソース領域より弱い導電性を有することを特徴とするパワーMOSデバイスの作製方法。 - 請求項17乃至請求項26のいずれか1項において、

前記結晶半導体は単結晶シリコンであることを特徴とするパワーMOSデバイスの作製方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24125796A JP4059939B2 (ja) | 1996-08-23 | 1996-08-23 | パワーmosデバイス及びその作製方法 |

| US08/914,869 US5952699A (en) | 1996-08-23 | 1997-08-19 | Insulated gate semiconductor device and method of manufacturing the same |

| US09/362,804 US6703671B1 (en) | 1996-08-23 | 1999-07-28 | Insulated gate semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP24125796A JP4059939B2 (ja) | 1996-08-23 | 1996-08-23 | パワーmosデバイス及びその作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH1065165A JPH1065165A (ja) | 1998-03-06 |

| JPH1065165A5 JPH1065165A5 (ja) | 2004-11-04 |

| JP4059939B2 true JP4059939B2 (ja) | 2008-03-12 |

Family

ID=17071559

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP24125796A Expired - Fee Related JP4059939B2 (ja) | 1996-08-23 | 1996-08-23 | パワーmosデバイス及びその作製方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US5952699A (ja) |

| JP (1) | JP4059939B2 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3634086B2 (ja) | 1996-08-13 | 2005-03-30 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置の作製方法 |

| US6703671B1 (en) * | 1996-08-23 | 2004-03-09 | Semiconductor Energy Laboratory Co., Ltd. | Insulated gate semiconductor device and method of manufacturing the same |

| JP4103968B2 (ja) | 1996-09-18 | 2008-06-18 | 株式会社半導体エネルギー研究所 | 絶縁ゲイト型半導体装置 |

| US6590230B1 (en) | 1996-10-15 | 2003-07-08 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| US6118148A (en) | 1996-11-04 | 2000-09-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and manufacturing method thereof |

| JP4017706B2 (ja) | 1997-07-14 | 2007-12-05 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| JP4282778B2 (ja) | 1997-08-05 | 2009-06-24 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| EP0915509B1 (en) * | 1997-10-24 | 2005-12-28 | STMicroelectronics S.r.l. | Process for integrating, in a same semiconductor chip, MOS technology devices with different threshold voltages |

| US6686623B2 (en) * | 1997-11-18 | 2004-02-03 | Semiconductor Energy Laboratory Co., Ltd. | Nonvolatile memory and electronic apparatus |

| JP4236722B2 (ja) * | 1998-02-05 | 2009-03-11 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JPH11233788A (ja) * | 1998-02-09 | 1999-08-27 | Semiconductor Energy Lab Co Ltd | 半導体装置 |

| TW507258B (en) | 2000-02-29 | 2002-10-21 | Semiconductor Systems Corp | Display device and method for fabricating the same |

| US7633471B2 (en) | 2000-05-12 | 2009-12-15 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and electric appliance |

| DE10161125C1 (de) * | 2001-12-12 | 2003-07-31 | Infineon Technologies Ag | Halbleiterbauelement mit optimierter Stromdichte |

| TW565937B (en) * | 2002-08-22 | 2003-12-11 | Vanguard Int Semiconduct Corp | Manufacturing method of source/drain device |

| ATE514190T1 (de) | 2003-03-19 | 2011-07-15 | Infineon Technologies Ag | Halbleiteraufbau mit hoch dotiertem kanalleitungsgebiet und verfahren zur herstellung eines halbleiteraufbaus |

| CA2736950A1 (en) * | 2009-03-27 | 2010-09-30 | Sumitomo Electric Industries, Ltd. | Mosfet and method for manufacturing mosfet |

| CA2738385A1 (en) * | 2009-03-27 | 2010-09-30 | Keiji Wada | Mosfet and method for manufacturing mosfet |

| DE112014006762B4 (de) | 2014-06-27 | 2021-09-30 | Mitsubishi Electric Corporation | Siliciumcarbid-Halbleiteranordnung |

| CN107046059B (zh) * | 2016-02-05 | 2020-04-21 | 瀚薪科技股份有限公司 | 碳化硅半导体元件以及其制造方法 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01501272A (ja) * | 1986-10-27 | 1989-04-27 | ヒユーズ・エアクラフト・カンパニー | ストライプ状のチャンネルのトランジスタおよびその製造方法 |

| JP3194941B2 (ja) * | 1990-03-19 | 2001-08-06 | 富士通株式会社 | 半導体装置 |

| JP3301116B2 (ja) * | 1992-07-20 | 2002-07-15 | ソニー株式会社 | 半導体装置及びその製造方法 |

| JP2848757B2 (ja) * | 1993-03-19 | 1999-01-20 | シャープ株式会社 | 電界効果トランジスタおよびその製造方法 |

| US5426325A (en) * | 1993-08-04 | 1995-06-20 | Siliconix Incorporated | Metal crossover in high voltage IC with graduated doping control |

| US5831294A (en) * | 1993-09-30 | 1998-11-03 | Sony Corporation | Quantum box structure and carrier conductivity modulating device |

| JP3635683B2 (ja) * | 1993-10-28 | 2005-04-06 | ソニー株式会社 | 電界効果トランジスタ |

| US5516711A (en) * | 1994-12-16 | 1996-05-14 | Mosel Vitelic, Inc. | Method for forming LDD CMOS with oblique implantation |

| US5478763A (en) * | 1995-01-19 | 1995-12-26 | United Microelectronics Corporation | High performance field effect transistor and method of manufacture thereof |

| KR0161398B1 (ko) * | 1995-03-13 | 1998-12-01 | 김광호 | 고내압 트랜지스터 및 그 제조방법 |

| US5698884A (en) * | 1996-02-07 | 1997-12-16 | Thunderbird Technologies, Inc. | Short channel fermi-threshold field effect transistors including drain field termination region and methods of fabricating same |

-

1996

- 1996-08-23 JP JP24125796A patent/JP4059939B2/ja not_active Expired - Fee Related

-

1997

- 1997-08-19 US US08/914,869 patent/US5952699A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JPH1065165A (ja) | 1998-03-06 |

| US5952699A (en) | 1999-09-14 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4059939B2 (ja) | パワーmosデバイス及びその作製方法 | |

| JP4103968B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP4014676B2 (ja) | 絶縁ゲイト型半導体装置およびその作製方法 | |

| JP4014677B2 (ja) | 絶縁ゲイト型半導体装置 | |

| WO1993012545A1 (fr) | Dispositif a semiconducteur a grille isolee verticale et procede pour sa fabrication | |

| JP3949193B2 (ja) | 絶縁ゲイト型半導体装置 | |

| JP3634086B2 (ja) | 絶縁ゲイト型半導体装置の作製方法 | |

| JP2008103737A (ja) | 絶縁ゲイト型半導体装置 | |

| EP0407011B1 (en) | Insulated gate semiconductor devices | |

| US6445036B1 (en) | Semiconductor device having trench-structured rectangular unit cells | |

| US6180959B1 (en) | Static induction semiconductor device, and driving method and drive circuit thereof | |

| US6703671B1 (en) | Insulated gate semiconductor device and method of manufacturing the same | |

| JP3221901B2 (ja) | 半導体装置 | |

| US12266718B2 (en) | Voltage-controlled switching device with channel region | |

| JPS6366969A (ja) | 高耐圧多結晶シリコン薄膜トランジスタ | |

| JP4053102B2 (ja) | 半導体装置およびその作製方法 | |

| JP5312489B2 (ja) | 半導体装置 | |

| JP2004235230A (ja) | 短チャネル効果を抑制したmis型電解効果トランジスタ | |

| JP4684358B2 (ja) | 半導体装置の作製方法 | |

| JP4896699B2 (ja) | 絶縁ゲイト型半導体装置およびその作製方法 | |

| JP4515530B2 (ja) | 半導体装置 | |

| JP2010118676A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070619 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070719 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071218 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071219 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101228 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101228 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111228 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111228 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121228 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121228 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131228 Year of fee payment: 6 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |