JP4059219B2 - デジタルミキサ - Google Patents

デジタルミキサ Download PDFInfo

- Publication number

- JP4059219B2 JP4059219B2 JP2004074505A JP2004074505A JP4059219B2 JP 4059219 B2 JP4059219 B2 JP 4059219B2 JP 2004074505 A JP2004074505 A JP 2004074505A JP 2004074505 A JP2004074505 A JP 2004074505A JP 4059219 B2 JP4059219 B2 JP 4059219B2

- Authority

- JP

- Japan

- Prior art keywords

- channel

- parameter

- assigned

- key

- rotary encoder

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04H—BROADCAST COMMUNICATION

- H04H60/00—Arrangements for broadcast applications with a direct linking to broadcast information or broadcast space-time; Broadcast-related systems

- H04H60/02—Arrangements for generating broadcast information; Arrangements for generating broadcast-related information with a direct linking to broadcast information or to broadcast space-time; Arrangements for simultaneous generation of broadcast information and broadcast-related information

- H04H60/04—Studio equipment; Interconnection of studios

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11B—INFORMATION STORAGE BASED ON RELATIVE MOVEMENT BETWEEN RECORD CARRIER AND TRANSDUCER

- G11B20/00—Signal processing not specific to the method of recording or reproducing; Circuits therefor

- G11B20/10—Digital recording or reproducing

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04S—STEREOPHONIC SYSTEMS

- H04S7/00—Indicating arrangements; Control arrangements, e.g. balance control

Landscapes

- Engineering & Computer Science (AREA)

- Signal Processing (AREA)

- Physics & Mathematics (AREA)

- Acoustics & Sound (AREA)

- Circuit For Audible Band Transducer (AREA)

Description

このchストリップは、デジタルミキサの性能や価格によっても異なるが、スライダ、ロータリーエンコーダ、およびキーやボタン等の操作子を有し、割り当てられたchのパラメータを制御するための操作子群として機能するものである。

「DIGITAL PRODUCTION CONSOLE DM2000 取扱説明書」,ヤマハ株式会社,2002年

例えば、デジタルミキサにマルチトラックレコーダを接続して録音を行う際に、1トラック分ずつパラメータを調整してレコーダに送り出し、レコーダが確認用に返してくる信号を裏のレイヤのchに入力し、これを聞き易い音量にレベル調整してモニタしたい等である。

この発明は、このような問題を解決し、デジタルミキサの操作性を向上させることを目的とする。

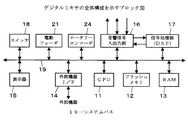

図1は、この発明の実施形態であるデジタルミキサの構成を示すブロック図である。図1に示すように、このデジタルミキサ(以下単に「ミキサ」ともいう)は、CPU11,フラッシュメモリ12,RAM13,外部機器インタフェース(I/F)14,表示器15,音響信号入出力部16,信号処理部(DSP)17,スイッチ18,電動フェーダ21,ロータリーエンコーダ24を備え、これらがシステムバス19によって接続されている。そして、入力する音響信号に対して種々の信号処理を施して出力する機能を有する。

フラッシュメモリ12は、CPU11が実行する制御プログラム等を記憶する書き換え可能な不揮発性記憶手段である。

RAM13は、各種パラメータの設定内容を記憶したり、CPU11のワークメモリとして使用したりする記憶手段である。

外部機器I/F14は、このミキサと接続するパーソナルコンピュータ等の外部機器と情報の授受を行うためのインタフェースである。

表示器15は、このミキサの操作パネル上に設けられ、液晶ディスプレイ(LCD)等によって構成される表示手段であり、設定の参照,変更,保存等を行うための画面やミキサの動作状態等を表示する。

DSP17は、音響信号入出力部から入力する音響信号に対し、設定されている各種パラメータの値に従った信号処理を施すモジュールである。その処理の詳細については後述する。

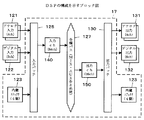

内蔵エフェクタ123は、入力する信号に対し、選択されたエフェクトを付与して出力する複数ブロックのエフェクタである。そのチャンネル構成は、モノラル,ステレオ等で切り換え可能となっている。

入力パッチ125は、アナログ入力121とデジタル入力122の各入力及び内蔵エフェクタ123から入力される信号を、64chある入力ch140に割り振るための任意結線を行うものである。そして、入力ch140の各chには、入力パッチ125で割り振られた入力信号が入力する。

出力ch150は、各種バス127と1対1で対応するように16ch設けられている。そして、その各chは、図3に示した入力chの構成のうち、イコライザ142,ノイズゲート143,コンプレッサ144,フェーダ&オン145に相当するモジュールを有している。出力ch150では、これらのモジュールによって入力した信号に対して所定の処理を行い、処理後の信号を出力パッチ130へ出力する。

なお、DSP17は、入力ch140や出力ch150から選択した信号を混合して図示しないモニタ用出力に出力することもできる。

以上説明したDSP17の各要素は、回路によって実現しても、演算処理によって実現してもよい。

この操作パネル100は、表示器15を備え、ここに表示する表示画面を参照しながら種々の操作子を操作することにより、DSP17における信号処理等に用いるパラメータの変更を指示し、またこれらのパラメータを編集するためのものである。

そして、このための操作子としては、chストリップ20,レイヤ選択キー群30,エンコーダ機能指定キー群40,AUXバス選択キー群50,カーソル操作子60,増減操作子70,エンタキー80を設けている。

そして、各chストリップ20には、図2に示した入力ch140あるいは出力ch150のいずれかのchが割り当てられ、chストリップ20の各操作子は、基本的にはそのchのパラメータを制御し、値を設定するための操作子として機能する。ただし、これに例外を設けた点がこの発明の特徴であり、この点については後述する。

また、ここでは出力ch150を割り当てるレイヤはマスタレイヤとして別途用意し、マスタレイヤ選択キー35によってこのレイヤを選択できるようにしている。そして、このレイヤが選択された場合には、各chストリップ20には1番目から16番目の出力chを割り当てるようにしている。

固定機能キー表示部201には、各固定機能キー41に割り当てられているパラメータが表示される。この割り当ては固定であるが、一応確認のために表示しているものである。アサイン可能キー表示部202には、各アサイン可能キー42に割り当てられているパラメータが表示される。パラメータ選択部203には、アサイン可能キー42に割り当て可能なパラメータの一覧が表示される。

この画面においてパラメータを割り当てた後でアサイン可能キー42のいずれかを押下すると、そのキーに割り当てられているパラメータをロータリーエンコーダ24に割り当てることができる。

以上の各操作子を設けた操作パネル100を用いることにより、デジタルミキサを動作させるために必要な多数のパラメータを設定することができる。

このミキサにおいては、CPU11が表1に示す各イベントの発生を検出すると、表1に示したように所定のレジスタにイベントに応じた値をセットする。また、表1に示した各レジスタは、表2に示したようなデータを設定するためのレジスタである。

そして、例えばn番目のアサイン可能キーについてこの指定がなされると、n番目のアサイン可能キーに割り当てられているパラメータの番号を記憶するレジスタEA(n)に、割り当てを指示されたパラメータの番号をセットする処理を行う。ここで、パラメータの番号は、表3に示すように、割り当て可能な各パラメータについて1〜44まで定められている。また、何も割り当てないことを示す番号0や、固定機能キー41に割り当てられているAUXセンドレベル及びパンに対応する番号も用意されている。

この処理においては、まずステップS1でロータリーエンコーダの操作量をレジスタbufにセットする。そして、ステップS2でレジスタEANの値が126であれば、ロータリーエンコーダ24にはc番目のchストリップ20に割り当てられているchのAUXセンドレベルが割り当てられていることになる。そこで、ステップS3でそのchのAUXセンドレベルの値を操作量に応じて更新して終了するが、どのバスについての値を更新するかは、レジスタAUXNの値に従う。

また、ステップS4で43の場合には、上述したようにロータリーエンコーダ24には、裏のレイヤにおいてc番目のchストリップ20に割り当てられるchのフェーダのパラメータが割り当てられていることになる。そこで、ステップS6及びS7でそのフェーダの値を更新して終了する。

以上の処理において、ステップS3,S5,S7ではCPU11が変更手段として機能する。

また、ミキサやその操作パネルの構成や操作法等が上記の実施形態に限られないことはもちろんである。

さらにまた、デジタルミキサ以外でも同様なチャンネルストリップを有する各種音響信号処理装置にも適用可能である。

従って、この発明を適用することにより、操作性のよいデジタルミキサを提供することができる。

Claims (2)

- 操作部にそれぞれロータリーエンコーダを有する複数のチャンネルストリップを設けたデジタルミキサであって、

前記各チャンネルストリップへのチャンネルの割り当てを定めるレイヤを複数記憶し、その中から選択されたレイヤに従って前記各チャンネルストリップにチャンネルを割り当てる第1の割当手段と、

前記ロータリーエンコーダに、そのロータリーエンコーダが属するチャンネルストリップに割り当てられているチャンネルのパラメータを割り当てるよう指示する第1の機能割り当てキーと、

自然数nについて前記各レイヤのうち2n−1番目と2n番目のレイヤに表裏の対応関係があるものとして、前記ロータリーエンコーダに、選択されているレイヤの裏のレイヤにおいてそのロータリーエンコーダの属するチャンネルストリップに割り当てられるチャンネルのパラメータを割り当てるよう指示する第2の機能割り当てキーと、

前記第1の機能割り当てキーまたは第2の機能割り当てキーの操作に応じて、操作されたキーに対応したパラメータを選択的に前記ロータリーエンコーダに割り当てる第2の割当手段と、

前記ロータリーエンコーダの操作に従って、該ロータリーエンコーダに割り当てられているパラメータの値を変更する変更手段とを設けたことを特徴とするデジタルミキサ。 - 1つのチャンネルのパラメータを変更するためのパラメータエンコーダを有し、各チャンネルを制御する複数のチャンネルストリップと、

複数のレイヤを記憶し、その中から選択されたレイヤに従って前記各チャンネルストリップにチャンネルを割り当てる第1の割当手段と、

チャンネルが割り当てられたチャンネルストリップのパラメータエンコーダへ、そのチャンネルのパラメータを割り当てるよう指示する第1の機能割り当てキーと、

選択されているレイヤと表裏の関係にある裏レイヤについて、前記選択されているレイヤのチャンネルが割り当てられたチャンネルストリップのパラメータエンコーダへ、対応する前記裏レイヤのチャンネルのパラメータを割り当てるよう指示する第2の機能割り当てキーと、

前記第1の機能割り当てキーまたは第2の機能割り当てキーの操作に応じて、操作されたキーに対応したパラメータを選択的に前記ロータリーエンコーダに割り当てる第2の割当手段と、

パラメータエンコーダの操作に従って前記パラメータエンコーダに割り当てられたパラメータを変更するパラメータ変更手段とを設けたことを特徴とするデジタルミキサ。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GB0321102A GB2406027B (en) | 2003-09-09 | 2003-09-09 | Digital mixer |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2005086802A JP2005086802A (ja) | 2005-03-31 |

| JP2005086802A5 JP2005086802A5 (ja) | 2005-07-28 |

| JP4059219B2 true JP4059219B2 (ja) | 2008-03-12 |

Family

ID=29226761

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004074505A Expired - Fee Related JP4059219B2 (ja) | 2003-09-09 | 2004-03-16 | デジタルミキサ |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US7499558B2 (ja) |

| JP (1) | JP4059219B2 (ja) |

| GB (1) | GB2406027B (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20070280489A1 (en) * | 2006-03-28 | 2007-12-06 | Numark Industries, Llc | Docking system and mixer for portable media devices with graphical interface |

| JP2008177646A (ja) * | 2007-01-16 | 2008-07-31 | Roland Corp | オーディオミキサ |

| US9852765B2 (en) * | 2007-03-01 | 2017-12-26 | Apple Inc. | Graphical user interface, process, program, storage medium and computer system for arranging music |

| US8498724B2 (en) | 2007-03-09 | 2013-07-30 | Yamaha Corporation | Digital mixer |

| JP5326214B2 (ja) * | 2007-03-09 | 2013-10-30 | ヤマハ株式会社 | デジタルミキサ |

| JP5326215B2 (ja) * | 2007-03-09 | 2013-10-30 | ヤマハ株式会社 | デジタルミキサ |

| US20080229200A1 (en) * | 2007-03-16 | 2008-09-18 | Fein Gene S | Graphical Digital Audio Data Processing System |

| JP4380746B2 (ja) | 2007-07-23 | 2009-12-09 | ヤマハ株式会社 | ディジタルミキサ |

| US8697976B2 (en) * | 2008-07-30 | 2014-04-15 | Yamaha Corporation | Parameter setting apparatus having separate operators for course and fine adjustments for the same parameter |

| EP2278735A3 (en) * | 2009-07-13 | 2012-10-24 | Yamaha Corporation | Digital mixer |

| CN101959101B (zh) * | 2009-07-13 | 2012-09-05 | 雅马哈株式会社 | 数字混合器 |

| JP5929499B2 (ja) * | 2012-05-21 | 2016-06-08 | ヤマハ株式会社 | 制御装置及びプログラム |

| JP5713042B2 (ja) * | 2013-03-25 | 2015-05-07 | ヤマハ株式会社 | デジタルオーディオミキシング装置及びプログラム |

| JP6515496B2 (ja) * | 2014-11-14 | 2019-05-22 | ヤマハ株式会社 | ミキシングコンソール |

| JP2016225692A (ja) * | 2015-05-27 | 2016-12-28 | ヤマハ株式会社 | 音信号処理装置 |

| WO2021138649A1 (en) * | 2020-01-04 | 2021-07-08 | Risher Vaughan | Fade device |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2299493B (en) * | 1995-03-28 | 2000-01-12 | Sony Uk Ltd | Digital signal processing |

| GB2301002B (en) * | 1995-05-19 | 2000-03-01 | Sony Uk Ltd | Audio mixing console |

| US6839441B1 (en) * | 1998-01-20 | 2005-01-04 | Showco, Inc. | Sound mixing console with master control section |

| JP3700931B2 (ja) * | 2001-06-11 | 2005-09-28 | ヤマハ株式会社 | マルチトラック・ディジタル録音再生装置 |

| US7350156B2 (en) * | 2001-09-21 | 2008-03-25 | Yamaha Corporation | Audio signal editing apparatus and control method therefor |

| JP4003424B2 (ja) * | 2001-09-21 | 2007-11-07 | ヤマハ株式会社 | 音声信号編集方法、音声信号編集装置およびプログラム |

-

2003

- 2003-09-09 GB GB0321102A patent/GB2406027B/en not_active Expired - Fee Related

-

2004

- 2004-03-16 JP JP2004074505A patent/JP4059219B2/ja not_active Expired - Fee Related

- 2004-08-23 US US10/925,093 patent/US7499558B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| GB2406027A (en) | 2005-03-16 |

| US20050055117A1 (en) | 2005-03-10 |

| GB0321102D0 (en) | 2003-10-08 |

| US7499558B2 (en) | 2009-03-03 |

| GB2406027B (en) | 2006-08-09 |

| JP2005086802A (ja) | 2005-03-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4059219B2 (ja) | デジタルミキサ | |

| JP3882190B2 (ja) | レベル調整装置 | |

| US8098850B2 (en) | Digital mixer | |

| JP5961980B2 (ja) | 音響信号処理装置 | |

| JP5454405B2 (ja) | 音響調整卓 | |

| JP4175292B2 (ja) | ディジタルミキサ装置 | |

| US8744096B2 (en) | Digital audio mixer | |

| JP6946811B2 (ja) | 音処理装置及びパラメータ割り当て方法 | |

| JP4103644B2 (ja) | デジタルミキサ | |

| JP5223805B2 (ja) | ミキシング制御装置 | |

| JP5387472B2 (ja) | ミキシング装置 | |

| JP4596261B2 (ja) | デジタルミキサおよびプログラム | |

| JP4765494B2 (ja) | 音響信号処理装置 | |

| US20050019021A1 (en) | Audio signal processing device | |

| JP4930112B2 (ja) | ミキシング装置 | |

| JP5489001B2 (ja) | 音響信号処理装置 | |

| JP3988692B2 (ja) | 音響信号処理装置 | |

| JP4596262B2 (ja) | デジタルミキサおよびプログラム | |

| JP3933104B2 (ja) | 音響信号処理装置及びプログラム | |

| JP5338633B2 (ja) | ミキシングコンソールおよびプログラム | |

| JP5358889B2 (ja) | ミキシング装置 | |

| JP4036110B2 (ja) | ミキシングシステムおよびプログラム | |

| JP2016181122A (ja) | パラメータ制御装置及びプログラム | |

| JP2008252550A (ja) | 音響信号処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070904 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071105 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20071127 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20071210 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101228 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101228 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111228 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111228 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121228 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131228 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |