JP4013498B2 - パターン描画装置及びパターン描画体の製造方法 - Google Patents

パターン描画装置及びパターン描画体の製造方法 Download PDFInfo

- Publication number

- JP4013498B2 JP4013498B2 JP2001217152A JP2001217152A JP4013498B2 JP 4013498 B2 JP4013498 B2 JP 4013498B2 JP 2001217152 A JP2001217152 A JP 2001217152A JP 2001217152 A JP2001217152 A JP 2001217152A JP 4013498 B2 JP4013498 B2 JP 4013498B2

- Authority

- JP

- Japan

- Prior art keywords

- pattern

- track

- memory

- data

- cluster

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 11

- 239000000758 substrate Substances 0.000 claims description 27

- 238000000034 method Methods 0.000 description 47

- 238000010586 diagram Methods 0.000 description 10

- 238000006243 chemical reaction Methods 0.000 description 7

- 239000010408 film Substances 0.000 description 6

- 230000003287 optical effect Effects 0.000 description 5

- 229920002120 photoresistant polymer Polymers 0.000 description 5

- 230000001360 synchronised effect Effects 0.000 description 4

- 230000005540 biological transmission Effects 0.000 description 2

- 230000003247 decreasing effect Effects 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000000059 patterning Methods 0.000 description 2

- 230000007261 regionalization Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- 238000002834 transmittance Methods 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000003384 imaging method Methods 0.000 description 1

Images

Classifications

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J2/00—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed

- B41J2/435—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material

- B41J2/44—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using single radiation source per colour, e.g. lighting beams or shutter arrangements

- B41J2/442—Typewriters or selective printing mechanisms characterised by the printing or marking process for which they are designed characterised by selective application of radiation to a printing material or impression-transfer material using single radiation source per colour, e.g. lighting beams or shutter arrangements using lasers

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B41—PRINTING; LINING MACHINES; TYPEWRITERS; STAMPS

- B41J—TYPEWRITERS; SELECTIVE PRINTING MECHANISMS, i.e. MECHANISMS PRINTING OTHERWISE THAN FROM A FORME; CORRECTION OF TYPOGRAPHICAL ERRORS

- B41J19/00—Character- or line-spacing mechanisms

- B41J19/16—Special spacing mechanisms for circular, spiral, or diagonal-printing apparatus

Landscapes

- Physics & Mathematics (AREA)

- Optics & Photonics (AREA)

- Exposure And Positioning Against Photoresist Photosensitive Materials (AREA)

- Exposure Of Semiconductors, Excluding Electron Or Ion Beam Exposure (AREA)

- Information Retrieval, Db Structures And Fs Structures Therefor (AREA)

- Record Information Processing For Printing (AREA)

Description

【産業上の利用分野】

本発明は、集積回路、表示装置、光学素子等の製造過程において、基板上のの薄膜などに微細なパターン形成を行うパターン描画装置に関する。

【0002】

【従来の技術】

半導体基板や光学素子等の製造過程においては、薄膜のパターニング工程が不可欠である。パターニングは、例えば、被処理膜にフォトレジストを塗布し、該フォトレジストにパターンを露光し、露光したレジストの現像処理を行い、残ったレジストをマスクとして被処理膜のエッチング処理を行うことによって行われる。上記パターンの露光にはパターン描画装置が使用される。パターン描画には、フォトマスクを使用する面露光の他に、光ビームによる線走査によって露光を行うものがある。後者は光ディスクの原盤の作成や自由なパターンの描画に使用される。例えば、特開昭59−171119号、特開平10−11814号などには、回転走査系によるパターン描画装置が記載されている。これ等のパターン描画装置は、フォトレジストが塗布された基板をターンテーブルに載置し、パターンデータで変調されたレーザ光で回転走査することによって該基板にパターンを描画している。

【0003】

【発明が解決しようとする課題】

しかしながら、上述した回転走査系のパターン描画装置では、スキャナなどによってX−Y座標系で取り込まれた元のパターンデータをr−θ座標系のデータに変換し、これを一旦メモリに記憶する。そして、基板の回転に同期してメモリから画素データを呼び出して光ビームを変調することによって、基板上に塗布されたフォトレジストを露光してパターンを描画している。従って、記憶した描画すべきパターンを少なくとも一回転走査(1トラック分)する毎にr−θ座標系のデータに変換する。高解像度のパターンを描画しなければならいな場合は、1トラックの円周の全ての描画点に対してX−Y座標系からr−θ座標系にデータ変換をしなければならないので、演算量が増大して変換時間が長くなり、高速の描画が制限される。また、CPUの演算処理能力が相対的に低い場合には、高解像度や多値レベルのパターンの描画が制限される。これに伴って、大容量のメモリも必要となる。

【0004】

よって、本発明は、同程度の処理能力のCPUであってもより高速の描画を可能とするパターン描画装置を提供することを目的とする。

【0005】

また、本発明は、同程度の処理能力のCPUであってもより高解像度の描画を可能とするパターン描画装置を提供することを目的とする。

【0006】

【課題を解決するための手段】

上記目的を達成するために本発明のパターン描画装置は、パターンを描画すべき基板上に同心円状に配列される複数のトラックを形成してパターンを描画するパターン描画装置において、1のトラック上の少なくとも2箇所に各トラック毎の基本となる基本画素列を正あるいは逆に並べることを繰り返し、これを連続な複数トラックについて行うことによって、上記パターンを形成する。

【0007】

かかる構成とすることによって、より少ないX−Y座標系からr−θ座標系への変換画素データでパターンを描画することが可能となる。

【0008】

好ましくは、上記基板は周方向において分割した複数のセクタ領域とこのセクタ領域の1つ又は連続する複数を組み合わせたクラスタ領域とに画定されて前記クラスタ領域を複数含み、上記基本画素列が前記クラスタ領域のトラック上に並べられる。

【0009】

かかる構成とすることによって、全体のパターン形成の制御プログラムが容易となる。

【0010】

好ましくは、上記基本画素列の間にパターンを形成しない疑似画素列を並べる。それにより、パターンデータの変換を不要として描画処理の演算負担を軽減する。

【0011】

好ましくは、上記クラスタ領域以外のセクタ領域のトラック上にパターンを形成しない疑似画素列が並べられる。それにより、セクタ単位で描画の有無を設定可能となり、パターン形成のプログラムを容易化することが可能となる。

【0012】

好ましくは、上記トラックは、画素データによって変調された描画ビームによって基板を回転走査した軌跡である。例えば、光ビームと感光膜とによるパターン描画が容易に行える。

【0013】

本発明のパターン描画体の製造方法は、パターンを描画すべき基板上に同心円状に配列される複数のトラックを形成してパターンを描画するパターン描画体の製造方法において、1のトラック上の少なくとも2箇所に各トラック毎の基本となる基本画素列を正あるいは逆に並べることを繰り返し、これを連続な複数トラックについて行うことによって、上記パターンを形成する。

【0014】

好ましくは、上記基板を周方向において分割した複数のセクタ領域とこのセクタ領域の1つ又は連続する複数を組み合わせたクラスタ領域とに画定し、上記基板に上記クラスタ領域を複数含め、上記基本画素列を上記クラスタ領域のトラック上に並べる。

【0015】

好ましくは、上記クラスタ領域以外のセクタ領域のトラック上にパターンを形成しない疑似画素列が並べられる。

【0016】

また、本発明のパターン描画体を備えた装置の製造方法は、上述したパターン描画体の製造方法のいずれかに記載の方法により該パターン描画体を得るようにした装置の製造方法であることを特徴とする。

【0017】

上述したパターン描画装置、描画方法は、集積回路等の半導体装置、LCD表示装置、電気泳動表示装置等の表示装置、フォトマスク、反射板、導光板、回折格子等の光学装置、等のパターン描画体を備えた装置の製造に使用される。

【0018】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照して説明する。

【0019】

図1は、本発明のパターン描画装置の全体構成を説明するブロック図である。

【0020】

同図において、光ビーム光源としてのレーザ光発生装置11から出射された光ビーム(レーザ光)12は電気光学変調器(EOM)13を経てハーフミラー14に至る。光ビーム12はその一部がハーフミラー14を通過して第1の光検出器15に入射し、その他は反射して音響光学変調器(AOM)17に入射する。光ビーム12は光検出器15によってその強度が検出される。検出された光強度はレベル信号に変換され、光検出器15からレベル調整器16に供給される。レベル調整器16は、光ビームスポット21のターンテーブル31の径方向における位置rに応じて電気光学変調器13に印加する制御信号を制御して透過量を設定し、光ビームの強度を調整する。それにより、ターンテーブル31の回転制御を角速度一定(CAV)で行った場合に、フォトレジストを走査する光ビームの露光エネルギ密度が常に一定となるようにする。上述した、電気光学変調器13、第1の光検出器15、レベル調整器16等はレベル調整ループを構成する。

【0021】

ハーフミラー14で反射した光ビーム12は、上述した、レベル調整ループで所定強度に調整されて、音響光学変調器(AOM)17、反射ミラー18、反射ミラー19、及び対物レンズ20を経てターンテーブル31に上に導出される。音響光学変調器17は、後述のパターンジェネレータ40から供給されるパターン信号に応じて透過率を変えることによって光ビーム12を強度変調する。対物レンズ20は、光ビーム12を基板32上に集光し、光スポット21を形成する。光スポット21は、図示しない、フォーカスサーボによって一定の径(あるいは焦点深度)になるように制御されている。フォーカスサーボとしては、例えば、スキュー法を採用することができる。また、基板に複数の積層膜が形成されている場合、当該複数の積層膜の特定の膜に焦点を合わせるように調整することも可能である。光スポット21の径は、一回転走査の径方向の幅(トラックの幅)に相当し、パターンの書込み(描画)に使用される。

【0022】

基板32を載置するターンテーブル31は、スピンドルモータ35によって回転駆動される。この回転は図示しない駆動回路によって行われるが、該回路はパターンジェネレータ40から供給されるクロック信号に従って駆動信号を発生する。また、ターンテーブル31は、その径方向に移動するスライダ34に載置され、スライダ34は送りモータ33によって駆動される。ターンテーブル31の一回転でスライダが1ピッチ送られるようにすることで光スポット21による渦巻き状の回転走査軌跡が得られる。送りモータ33の送り量はパターンジェネレータ40によって制御される。なお、ターンテーブル31を移動するのでなく、別途のスライダによって結像光学系(18〜21)をターンテーブルの径方向に移動することとしても良い。

【0023】

図2は、パターンジェネレータ40の構成を説明する機能ブロック図である。パターンジェネレータ40は、描画点座標生成部401、描画データ生成部402、パターン記憶部403、メモリ404、メモリコントローラ405、D/A変換器406、発振器407等によって構成される。これ等機能は、コンピュータシステムによって実現することが可能である。

【0024】

描画点座標生成部401は、メモリコントローラ405から供給されるデータ転送要求信号に従って、描画するトラックの各画素のアドレスをターンテーブルに対応した極座標(ri,θi)形式で出力する。例えば、1トラック分の画素アドレス群を連続的に発生する。描画データ生成部402は、極座標で表される各画素(ri,θi)のアドレスを、これに対応するX−Y座標系の位置(xi,yi)のパターンデータのアドレスに変換する。極座標(ri,θi)とX−Y座標(xi,yi)との座標の変換は、xi=ricosθi、yi=risinθiの関係式により行える。ここで、riは、X−Y座標の原点位置O(0,0)から任意の位置P(xi,yi)の画素までの距離OP(トラック番号riに相当する)であり、θiはX軸と線分OPとがなす角度である。基板上に描画すべきパターンのデータは、例えば、スキャナ等によって二次元表示されるビットマップデータとして予めパターン記憶部403に保持されている。また、CADデータ(コンピュータによるパターン設計データ)等を変換したものであっても良い。記憶部403には、描画すべき前記パターンの形成に関する情報も記憶される。この情報は、メモリ404を介してメモリコントローラ405に提供される。描画データ生成部402は、上述した、描画点座標生成部401から供給される一連の極座標アドレス(ri,θi)に対応するX−Y座標系のアドレス(xi,yi)でパターン記憶装置403から描画すべきパターンの画素データを読み出し、メモリ404に記憶させる。例えば、1トラック分の画素データがメモリ404に記憶される。

【0025】

メモリ404は、例えば、図3に示すように、バンクAとバンクBの2つの領域を備えており、一方の領域を読み出しあるいは書込み中に他方の領域を書込みあるいは読み出すことが可能である。バンクAは、メモリのアドレス[0]〜[SizeBank-1]の領域が割り当てられ、バンクBは、メモリのアドレス[SizeBank]〜[2×SizeBank]の領域が割り当てられる。メモリコントローラ405がバンクAの現在の読み出しアドレス、アドレス[adrCrrnt]のデータD[adrCrrnt]を読み出し中に、バンクBのデータが更新される。従って、1のトラック分の画素データ群を読み出し中に、次のトラックの画素データ群を書き込むことができ、FIFO(First In First Out)の動作を行うことができる。

【0026】

メモリコントローラ405は、メモリ404から各トラックの画素データを逐次読み出してD/A変換器406に供給し、音響光学変調器17の変調入力を得る。音響光学変調器17の透過率を画素データに応じて設定することによって光ビームを画素データで変調する。

【0027】

メモリコントローラ405は、メモリ404の一方のバンクから1トラック分の画素データの読み出しが終了すると、他方のバンクから次の1トラックの画素データの読み出しを行うと共に、描画点座標生成部分401にデータ転送要求信号を発し、更に、次のトラックの画素データのアドレスを出力させる。これを繰り返して、描画点座標生成部分401が第1のトラックの画素データのアドレスから最終トラックの画素データのアドレスまでを発生すると、基板上のパターンを描画すべき領域の画素のアドレスが読み出される。画素データを供給するメモリコントローラ405及びD/A変換器406は発振器407から供給されるクロック信号に同期して動作するが、この発振器407の出力するクロックはスピンドルモータ35及び送りモータ33の回転制御にも使用され、ターンテーブル31の回転、スライダ34の径方向移動が画素データの送りと同期するようになされる。従って、ターンテーブル31及びスライダ34の回転制御系の各送り33とデータの送りとが同期し、r−θ系座標の回転走査によってパターンが描画される。

【0028】

本発明の実施例においては、前述した、描画点座標生成、描画データ生成における座標変換などの演算処理量を減らすべく、パターンジェネレータ40は、以下に述べるような、メモリに記録されたデータの繰り返し利用、非描画領域におけるゼロデータ生成等を行う機能を更に備える。

【0029】

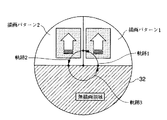

図4は、実施例において基板32に描くパターンの例を示している。このパターンは、円形の基板32の中心より上側の右半分の領域に描かれる描画パターン1、該基板の上側の左半分の領域に描かれる描画パターン2、該基板の下側半分の領域に描かれる非描画領域で構成されている。描画パターン1及び2は、基板の中心を通る線に対して線対称の図形であり、図示の例では、描画パターン1及び2は、四角の中に矢印が描かれている。また、描画パターン1を形成する走査軌跡を軌跡1、描画パターン2を形成する走査軌跡を軌跡2、非描画領域を走査する軌跡を軌跡3として図4中に示している。

【0030】

このようなパターンを描画する、パターンジェネレータ40の動作について説明する。前述したように、メモリ404はバンクA及びBの2つのバンクを含み、各バンクの記憶容量(サイズ)はSizeBankであるが、この記憶容量は軌跡1でパターン1を描画するに必要な容量よりも大きい容量が確保されている。アドレス[adrCrrnt]のデータをD[adrCrrnt]で表す。

【0031】

パターンジェネレータ40は、図5に示すように、描画領域を同サイズの扇形の領域のセクタに分割して処理を行う。この例では、一周の走査軌跡(1トラック)を24のセクタに分割している。セクタ数は描画パターンに応じて適宜に選定される。このセクタを単一又は連続した複数でまとめてクラスタを構成する。図示の例では、描画パターン1、描画パターン2、非描画領域に対応してクラスタ+(セクタ0〜5)、クラスタ−(セクタ6〜11)、ダミークラスタ(セクタ12〜23)として各セクタを割り当てている。クラスタ+では、描画パターン1に対応してメモリアドレスを順方向に走査する。それにより、基板上に基本画素列を描画する。クラスタ−では、描画パターン2に対応してメモリアドレスを逆方向に走査する。それにより、基板上に上記基本画素列を逆の並びで描画する。クラスタ+及びクラスタ−のセクタ数は同じである。非描画領域では、アドレスは変化せず疑似(零)データを生成する。

【0032】

この場合のメモリコントローラ405の処理をフローチャートを参照して説明する。図6は、メモリコントローラ405のメインルーチンを説明するフローチャートである。図7は、データ出力サブルーチンを示すフローチャートである。図8は、セクタ以外のドット(画素)処理を行うサブルーチンを説明するフローチャートである。図9は、トラックの最終ドット処理のサブルーチンを説明するフローチャートである。図10は、クラスタの最終ドット処理のサブルーチンを説明するフローチャートである。図11は、クラスタ以外の最終ドットを処理するサブルーチンを説明するフローチャートである。

【0033】

各フローチャートにおいて使用される演算子、変数、定数は、次のように定義される。これ等変数等は、装置の動作状態をモニタするコンピュータによって随時更新される。

【0034】

<=:右辺から左辺への代入

++:インクリメント

--:デクリメント

= ?:比較

cntDot_Sect:セクタ内(かつ1トラック内)で何番目のドットを処理するかを示す変数。

【0035】

cntSect_Rev:トラック内で何番目のセクタを処理するかを示す変数。

【0036】

cntSect_Clst:クラスタ内で何番目のセクタを処理するかを示す変数。

【0037】

cntTrack:描画領域内で何番目のトラックを処理するかを示す変数。

【0038】

adrCrrnt:メモリコントローラがメモリにアクセスするためのアドレス。

【0039】

NDot_Clst:1トラック上の1セクタを構成するドットの数。

【0040】

NSect_Rev:1トラックを構成するセクタの数。本例では、24である。

【0041】

NSect_Clst:1クラスタを構成するセクタの数。本例では、6である。

【0042】

adrFrnt:次のクラスタ+の先頭ドットに対応するアドレス。

【0043】

変数adrCrrntは、サイズ2×SizeBankで巡回する。すなわち、adrCrrnt=2SizeBank-1のとき、adrCrrntをインクメントすると、adrCrrnt=0となる。逆に、adrCrrnt=0のときに、adrCrrntをデクリメントすると、adrCrrnt=2SizeBank-1となる。

【0044】

図6に示すように、メモリコントローラは、描画開始が指令されると初期化を行う。すなわち、変数cntDot_Sect、cntSelect_Rev、cntSect_Clst、cntTrack、adrCrrntをそれぞれ0に設定する。また、描画領域にクラスタ+を選択し、描画領域の該当フラグを設定する(S12)。

【0045】

次に、描画中のトラックの番号が描画終了のトラック番号になったかどうかを、変数cntTrackの値が描画トラックの終了を示す終了値NTrackになったどうかによって判別する(S14)。描画トラックの終了に該当する場合には(S14;Yes)、描画処理を終了する(S16)。

【0046】

初期状態では、まだ、最終描画トラックの終了には該当しないので(S14;No)、メモリ404に記憶された画素データのデータ出力を行う(S18)。現在のセクタの処理ドット番号が該セクタの最終ドット番号であるかどうかを、変数cntDot_SectがNDot_Clst-1と等しいかどうかによって判別する。なお、変数は「0」より始まるので、最後のドット番号はNDot_Clst-1となる(S20)。まだ、セクタの最終ドットに至らない場合には(S20;No)、セクタの読み出しドットの番号を「1」増加し(S22)、セクタの最終ドット以外の処理を行う(S24)。

【0047】

セクタの最終ドット以外の処理は、図8に示すように、現在の描画領域が、ダミー領域、クラスタ+領域、クラスタ−のいずれであるかを判別する(S242)。ダミー領域であるときは、このサブルーチンを終了してステップS14に戻る。クラスタ+領域であるときは、メモリ404にアクセスするアドレスを「1」増加して(S244)、ステップS14に戻る。クラスタ−であるときはメモリ404にアクセスするアドレスを「1」減少し(S246)、ステップS14に戻って処理手順を繰り返す。

【0048】

セクタの処理ドット番号が該セクタの最終ドット番号であるとき(S20;Yes)、描画点の次セクタへの移動に対応してセクタのドット番号を示す変数cntDot_Sectを「0」に設定(リセット)する(S20)。

【0049】

次に、セクタの番号がトラックの最後のセクタ番号かどうかを、変数cntSect_Revと変数NSect_Rev-1とを比較して判別する(S28)。まだ、最後のセクタではないとき(S28;No)、変数cntSect_Revを増加し、セクタ番号を「1」増加する(S30)。

【0050】

現在の描画点の領域がダミー領域であるかどうかを判別する(S32)。ダミー領域であるときは(S32;Yes)、後述するように、「0」データを出力することとし、メモリ404からの読み出しを行わないので、ステップS14に戻って処理手順を繰り返す。

【0051】

ダミー領域でないときは(S32;No)、現在の描画点のセクタが該当クラスタ内の最後のセクタかどうかを、変数cntSect_Clstと変数NSect_Clst-1とを比較して判別する(S40)。最後のセクタではない場合(S40;No)、セクタの最終ドットになっているので(S20;Yes)、変数cntSect_Clstを「1」増加し(S42)、クラスタの最終ドット以外の処理を行う(S44)。

【0052】

このクラスタの最終ドット以外の処理は、図9に示すように、現在の描画領域が、クラスタ+領域、クラスタ−のいずれであるかを判別する(S442)。クラスタ+領域であるときは、メモリ404にアクセスするアドレスを「1」増加して(S444)、ステップS14に戻る。クラスタ−であるときはメモリ404にアクセスするアドレスを「1」減少し(S446)、ステップS14に戻って処理手順を繰り返す。

【0053】

次に、現在の描画点のセクタが該当クラスタ内の最後のセクタである場合(S40;Yes)、変数cntSect_Clstに「0」を設定してカウントをリセットする(S42)。クラスタの最終ドットの処理を行う(S44)。

【0054】

クラスタの最終ドットの処理は、図10に示すように、現在の描画領域が、クラスタ+領域、クラスタ−のいずれであるかを判別する(S442)。クラスタ+領域であるときは、次のクラスタの先頭ドットのアドレスAdrFrntとして現在のメモリ404にアクセスするアドレスadrCrrntに「1」を加えたものを設定する(S484)。領域フラグをクラスタ−に設定し(S486)、ステップS14に戻る。現在の描画領域がクラスタ−であるときは変数adrCrrntに変数adrFrntを設定する(S448)。領域フラグをダミーに設定し(S490)、ステップS14に戻って処理手順を繰り返す。

【0055】

次に、トラックの最後のセクタである場合(S28;Yes)、変数cntSect_Revに「0」を設定して、セクタ番号をリセットし(S50)、変数cntTrackを「1」増加して、処理トラックを次トラックに設定する(S52)。トラックの最終ドット処理を行う(S54)。

【0056】

トラックの最終ドット処理は、図11に示すように、現在の描画領域が、ダミー領域、クラスタ+領域、クラスタ−のいずれであるかを判別する(S542)。ダミー領域であるときは、領域フラグにクラスタ+を設定し(S548)、ステップS14に戻って処理手順を繰り返す。

【0057】

現在の領域がクラスタ+領域であるときは、変数adrCrrntに「1」を加えて、メモリのアクセスアドレスを増加し(S544)、領域フラグにクラスタ+を設定し(S548)、ステップS14に戻って処理手順を繰り返す。

【0058】

現在の描画領域がクラスタ−であるときは変数adrCrrntに変数AdrFrntを設定し(S546)、領域フラグにクラスタ+を設定し(S548)、ステップS14に戻って処理手順を繰り返す。

【0059】

ステップ14から上述した手順を繰り返してメモリ404のアドレス指定を行ってデータの読み出しを繰り返す。

【0060】

このようにして、メモリコントローラ405がメモリ404のアドレス指定を行ってドット(画素)データを読み出し、パターンを描画する。

【0061】

図12は、メモリコントローラ405のデータ送信要求信号の生成を説明するフローチャートである。前述したように、メモリコントローラ405は、メモリ404のバンクAのデータを読み終えると、データ転送要求信号を描画点座標生成部401に送信する。このルーチンでは、描画点座標生成部401はSizeBank分の座標を生成し、描画データ生成部402は各描画点のデータをバンクAに送信する。バンクBのデータを読み終えたときも同様の処理を行う。

【0062】

データ転送要求処理は、まず、データ転送要求フラグbankReqに「0」を設定し、リセットする(S62)。次に、現在の読み出し位置が所定位置、すなわち、トラック内のセクタが0番でセクタ内のドット番号も0番であるトラックの先頭セクタのセクタ先頭位置であるかを、変数cntSect_Revが「0」で、かつ変数cntDot_Sectも「0」であるかを判別する(S64)。

【0063】

このトラックのセクタ先頭位置である場合には(S64;Yes)、メモリコントローラ405がメモリ404のA又はBバンクの最終アドレスにアクセスしたかどうかを後述する変数crossBorderの値によって判別する(S66)。変数crossBorderの値が「1」ではなく、まだ、最終のアドレスにアクセスしていない場合(S66;No)、データ転送要求を発生することなく、ステップ64に戻り、処理を繰り返す。最終のアドレスにアクセスした場合(S66;Yes)、データ転送要求フラグbankReqに「1」を設定し、データ転送要求信号を描画点座標生成部401に送出して(S68)、ステップS64に戻り、処理を繰り返す。

【0064】

一方、現在の読み出し位置がトラックのセクタ先頭位置ではないとき(S64;No)、データ転送要求が発生しているかどうかを、変数bankReqが「1」であるかどうかによってを判別する(S70)。データ転送要求が発生していないときは(S70;No)、ステップS64に戻り、処理を繰り返す。データ転送要求が発生していないときは(S70;Yes)、変数bankReqに「0」を設定して、変数bankReqをリセットし(S72)、ステップS64に戻る。変数bankReqはリセットされてデータ転送要求は消滅する(S62)。処理ステップ64〜ステップS72の各一つのループは発振器407のクロックに同期している。データ転送要求信号bankReqはメモリ上の必要なデータの上書きを防止するために、ターンテーブルの回転と同期して転送される。描画データの再利用は1周内で繰り返し行うことができる。

【0065】

図13は、バンク切換りの検出を行う変数crossBorderを説明するフローチャートである。変数crossBorderは、メモリコントローラがバンクA又はBの最終のアドレスにアクセスすると「1」となり、変数bankReq信号の出力後「0」になる。

【0066】

まず、バンク切換りの検出処理は、メモリコントローラが変数crossBorderをリセットする(S82)。現在のメモリ404の読み出しアドレスがAバンクの最大アドレスになっているか、あるいはBバンクの最大アドレスになっているかどうかを、読み出しアドレスを示す変数adrCrrntの値がSizeBank-1あるいは2SizeBank-1と等しいかどうかによって判別する(S84)。メモリ404の読み出しアドレスがA又はBバンクの最終アドレスとなっている場合には(S84;Yes)、片バンクの読み出し終了、あるいはメモリバンクの境界に読み出し位置があることを示す変数crossBorderを「1」に設定し(S86)、ステップ64に戻って処理を繰り返す。

【0067】

メモリ404の読み出しアドレスがA又はBバンクの最終アドレスではない場合には(S84;No)、データ転送要求が発生しているかどうかを、変数bankReqが「1」であるかどうかによってを判別する(S88)。データ転送要求が発生していないときは(S88;No)、ステップS84に戻り、処理を繰り返す。データ転送要求が発生しているときは(S88;Yes)、変数crossBorderを「0」を設定して、変数crossBorderをリセットし(S90)、ステップS84に戻る。変数crossBorderはリセットされてバンク切換り信号は消滅する(S62)。処理ステップ84〜ステップS90の各一つのループは発振器407のクロックに同期している。このように、変数crossBorderはバンクの境界を読み出しアドレスが通過すると、「1」となり、変数bankReqが「1」になり、データ転送要求信号が発生すると「0」にリセットされる。

【0068】

これ等の一連の動作を動作を繰り返すことによって描画点データを生成する処理が従来よりも半減し、高速描画可能となる。

【0069】

図14は、他の実施例を説明する説明図である。この例では、「J」状の矢印の1のパターンデータを用いて4つのパターンを描画する例を示している。1トラックの軌跡を形成する、互いに等しい長さの軌跡1、2、3及び4を同じ描画データで描くことによって、4つのパターンを形成している。

【0070】

図15は、この場合のクラスタのレイアウトを示している。描画領域は、24セクタに分割され、セクタ0〜5がクラスタ0+、セクタ6〜11がクラスタ1+、セクタ12〜17がクラスタ2+、セクタ18〜23がクラスタ3+となっている。ここで、クラスタの「+」は、アドレス指定が増加(順)方向に読み出されることを示している。

【0071】

この実施例では、図6に示した処理のサブルーチンの内容が図16乃至20のように変更される。

【0072】

すなわち、図16に示されるように、セクタの最終ドット以外の処理(S24)は、メモリコントローラ405がメモリ404にアクセスするアドレスを「1」増加して(S244)、ステップS14に戻る。また、図17に示されるように、トラックの最終ドットの処理(S54)は、メモリコントローラ405がメモリ404にアクセスするアドレスを「1」増加する(S544)。更に、クラスタの先頭ドットに対応するメモリアドレスを示す変数adrBackに現在アドレスのadrCrrntの値を設定し(S545)、ステップS14に戻る。クラスタの最終ドットの処理(S48)は、図18に示されるように、メモリコントローラ405がメモリ404にアクセスするアドレスをadrBackに設定して「1」増加して(S244)、ステップS14に戻る。クラスタの最終ドット以外の処理(S44)は、図19に示すように、メモリコントローラ405がメモリ404にアクセスするアドレスを「1」増加して(S244)、ステップS14に戻る。

【0073】

この第2の実施例では、描画点座標生成部401、描画データ生成部402が全面の描画点データを生成するようにした場合に比べて、同じデータを4回使用するので約1/4の処理データ量となる。

【0074】

このように、本発明の実施例によれば、所定のトラック範囲において、基本となるパターンのデータを繰り返し使用し、あるいはダミーデータを使用して全体のパターンを描画するので、全体のパターンデータをデータ変換する場合に比べてデータ変換に要する演算の負担が減少する。

【0075】

【発明の効果】

以上説明したように、本発明のパターン描画装置によれば、R−θ座標系にデータ変換されたデータを繰り返し使用してパターンを描画するようにしたので、データ変換の演算処理量が減少し、より高速な描画が可能となる。また、解像度の向上も可能となる。

【図面の簡単な説明】

【図1】図1は、本発明のパターン描画装置の全体構成を説明する機能ブロック図である。

【図2】図2は、パターンジェネレータ40の構成例を説明するブロック図である。

【図3】図3は、メモリ404の内部領域の使用例を説明する説明図である。

【図4】図4は、第1のパターンの描画例を説明する説明図である。

【図5】図5は、第1のパターンを描画する際の、セクタ、クラスタの構成例を説明する説明図である。

【図6】図6は、メモリコントローラ405の、メモリ404からのデータ読み出し動作を説明するフローチャートである。

【図7】図7は、データ出力の処理を説明するフローチャートである。

【図8】図8は、セクタの最終ドット以外の処理を説明するフローチャートである。

【図9】図9は、クラスタの最終ドット以外の処理を説明するフローチャートである。

【図10】図10は、クラスタの最終ドットの処理を説明するフローチャートである。

【図11】図11は、トラックの最終ドットの処理を説明するフローチャートである。

【図12】図12は、データ転送要求信号の生成を説明するフローチャートである。

【図13】図13は、メモリ内の読み出しバンクの切替を説明するフローチャートである。

【図14】図14は、第2のパターンの描画例を説明する説明図である。

【図15】図15は、第2のパターンを描画する際の、セクタ、クラスタの構成例を説明する説明図である。

【図16】図16は、第2のパターンの描画における、セクタの最終ドット以外の処理を説明するフローチャートである。

【図17】図17は、第2のパターンの描画における、トラックの最終ドットの処理を説明するフローチャートである。

【図18】図18は、第2のパターンの描画における、クラスタの最終ドットの処理を説明するフローチャートである。

【図19】図19は、第2のパターンの描画における、クラスタの最終ドット以外の処理を説明するフローチャートである。

【符号の説明】

401 描画点座標生成部

402 描画データ生成部

404 メモリ

405 メモリコントローラ

Claims (2)

- パターンを描画すべき基板上に同心円状に配列される複数のトラックを形成して二次元パターンを描画するパターン描画装置であって、

1のトラック上に描画すべき基本画素列をメモリに記憶し、当該1のトラック上の少なくとも2箇所に記憶された前記基本画素列を正あるいは逆に並べることを繰り返し、これを連続な複数トラックについて行うことによって、前記二次元パターンを形成するものであり、

前記1のトラック上に描画すべき基本画素列の前記メモリへの記憶が、前記パターンの画素データをX−Y座標系に対応したアドレスで記憶しているパターン記憶装置から、前記1のトラック上の位置を示す極座標の値に対応した前記X−Y座標系の値に対応するアドレスで前記パターン記憶装置から読出して前記メモリに記憶させる描画データ生成部によって行われる、ことを特徴とするパターン描画装置。 - パターンを描画すべき基板上に同心円状に配列される複数のトラックを形成して二次元パターンを描画するパターン描画体の製造方法であって、

1のトラック上に描画すべき基本画素列をメモリに記憶し、当該1のトラック上の少なくとも2箇所に記憶された前記基本画素列を正あるいは逆に並べることを繰り返し、これを連続な複数トラックについて行うことによって、前記二次元パターンを形成するものであり、

前記1のトラック上に描画すべき基本画素列の前記メモリへの記憶が、前記パターンの画素データをX−Y座標系に対応したアドレスで記憶しているパターン記憶装置から、前記1のトラック上の位置を示す極座標の値に対応した前記X−Y座標系の値に対応するアドレスで読出して前記メモリに記憶させることよって行われる、ことを特徴とするパターン描画体の製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001217152A JP4013498B2 (ja) | 2001-07-17 | 2001-07-17 | パターン描画装置及びパターン描画体の製造方法 |

| TW091113294A TW577827B (en) | 2001-07-17 | 2002-06-18 | Pattern drawing device and manufacturing method of pattern drawing body |

| CN02126238.1A CN1251025C (zh) | 2001-07-17 | 2002-07-17 | 图案描绘方法及图案描绘体的制造方法 |

| US10/197,640 US6872498B2 (en) | 2001-07-17 | 2002-07-17 | Pattern drawing device and manufacturing method of pattern drawing body |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001217152A JP4013498B2 (ja) | 2001-07-17 | 2001-07-17 | パターン描画装置及びパターン描画体の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2003029419A JP2003029419A (ja) | 2003-01-29 |

| JP4013498B2 true JP4013498B2 (ja) | 2007-11-28 |

Family

ID=19051531

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001217152A Expired - Fee Related JP4013498B2 (ja) | 2001-07-17 | 2001-07-17 | パターン描画装置及びパターン描画体の製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6872498B2 (ja) |

| JP (1) | JP4013498B2 (ja) |

| CN (1) | CN1251025C (ja) |

| TW (1) | TW577827B (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6915024B1 (en) * | 2000-09-29 | 2005-07-05 | Hewlett-Packard Development Company, L.P. | Image sharpening by variable contrast mapping |

| WO2010119607A1 (ja) * | 2009-04-13 | 2010-10-21 | パナソニック株式会社 | 光ディスク記録装置、及び光ディスク描画方法 |

| JP5914064B2 (ja) * | 2012-03-12 | 2016-05-11 | 株式会社エルエーシー | プリント装置 |

Family Cites Families (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS59171119A (ja) | 1983-03-18 | 1984-09-27 | Hitachi Ltd | レ−ザパタ−ン形成装置 |

| JPH1011814A (ja) | 1996-06-27 | 1998-01-16 | Pioneer Electron Corp | 光ディスク原盤記録方法 |

-

2001

- 2001-07-17 JP JP2001217152A patent/JP4013498B2/ja not_active Expired - Fee Related

-

2002

- 2002-06-18 TW TW091113294A patent/TW577827B/zh not_active IP Right Cessation

- 2002-07-17 CN CN02126238.1A patent/CN1251025C/zh not_active Expired - Fee Related

- 2002-07-17 US US10/197,640 patent/US6872498B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| TW577827B (en) | 2004-03-01 |

| US6872498B2 (en) | 2005-03-29 |

| CN1397842A (zh) | 2003-02-19 |

| JP2003029419A (ja) | 2003-01-29 |

| CN1251025C (zh) | 2006-04-12 |

| US20030020800A1 (en) | 2003-01-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI432908B (zh) | 微影系統及投射方法 | |

| JP4281041B2 (ja) | 位相格子マスク | |

| JP2919391B2 (ja) | パターン形成方法およびその装置 | |

| JP2003332221A (ja) | 露光装置 | |

| TWI620038B (zh) | 曝光方法和系統以及雷射直接成像系統 | |

| US20040160590A1 (en) | Photo-fabrication apparatus | |

| CN101174103A (zh) | 图案描画装置及图案描画方法 | |

| JP2003195512A (ja) | 多重露光描画装置および多重露光描画方法 | |

| JP3737292B2 (ja) | 光変調装置及び光学的情報処理システム | |

| JP2006339183A (ja) | パターン描画装置およびブロック数決定方法 | |

| US8189902B1 (en) | Creating an XY image pattern on a rotating substrate | |

| JP3310400B2 (ja) | 電子ビーム露光方法および露光装置 | |

| JP2003057837A (ja) | 多重露光描画装置および多重露光描画方法 | |

| JP4273291B2 (ja) | 多重露光描画装置および多重露光描画方法 | |

| JP4013498B2 (ja) | パターン描画装置及びパターン描画体の製造方法 | |

| JPS6333145B2 (ja) | ||

| JP2000292934A (ja) | レーザ描画装置及びレーザ描画方法 | |

| JP2725828B2 (ja) | 像の投影用のフォトマスクを形成するための方法及び装置 | |

| US7589755B2 (en) | Apparatus and method for recording image on photosensitive material | |

| KR101391215B1 (ko) | 묘화 장치 및 화상 데이터의 작성 방법 | |

| US6924071B1 (en) | Photomask and method for reducing exposure times of high density patterns on the same | |

| JP2000267295A (ja) | 露光方法及びその装置 | |

| JP4691653B2 (ja) | データ生成方法、データ生成装置、及びプログラム | |

| JP3975478B2 (ja) | パターン描画装置 | |

| JPH0397364A (ja) | 画像走査記録装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050720 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070307 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070507 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070529 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070730 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070821 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070903 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100921 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100921 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110921 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120921 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130921 Year of fee payment: 6 |

|

| LAPS | Cancellation because of no payment of annual fees |