JP3917193B2 - 利得精度を改善したシグマ―デルタ変調器 - Google Patents

利得精度を改善したシグマ―デルタ変調器 Download PDFInfo

- Publication number

- JP3917193B2 JP3917193B2 JP51648299A JP51648299A JP3917193B2 JP 3917193 B2 JP3917193 B2 JP 3917193B2 JP 51648299 A JP51648299 A JP 51648299A JP 51648299 A JP51648299 A JP 51648299A JP 3917193 B2 JP3917193 B2 JP 3917193B2

- Authority

- JP

- Japan

- Prior art keywords

- signal

- sigma

- output terminal

- input

- gain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 238000005070 sampling Methods 0.000 claims description 12

- 238000001914 filtration Methods 0.000 claims description 6

- 238000010586 diagram Methods 0.000 description 8

- 238000013139 quantization Methods 0.000 description 6

- 238000000034 method Methods 0.000 description 4

- 239000000654 additive Substances 0.000 description 2

- 230000000996 additive effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

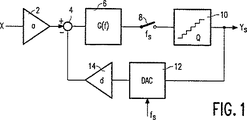

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/324—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement

- H03M3/326—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors

- H03M3/338—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors by permutation in the time domain, e.g. dynamic element matching

- H03M3/34—Continuously compensating for, or preventing, undesired influence of physical parameters characterised by means or methods for compensating or preventing more than one type of error at a time, e.g. by synchronisation or using a ratiometric arrangement by averaging out the errors by permutation in the time domain, e.g. dynamic element matching by chopping

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/39—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators

- H03M3/412—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution

- H03M3/422—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only

- H03M3/424—Structural details of delta-sigma modulators, e.g. incremental delta-sigma modulators characterised by the number of quantisers and their type and resolution having one quantiser only the quantiser being a multiple bit one

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| EP97202657.9 | 1997-08-29 | ||

| EP97202657 | 1997-08-29 | ||

| PCT/IB1998/001187 WO1999012264A2 (en) | 1997-08-29 | 1998-08-03 | Sigma-delta modulator with improved gain accuracy |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001505038A JP2001505038A (ja) | 2001-04-10 |

| JP2001505038A5 JP2001505038A5 (enExample) | 2006-01-05 |

| JP3917193B2 true JP3917193B2 (ja) | 2007-05-23 |

Family

ID=8228683

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP51648299A Expired - Fee Related JP3917193B2 (ja) | 1997-08-29 | 1998-08-03 | 利得精度を改善したシグマ―デルタ変調器 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6404367B1 (enExample) |

| EP (1) | EP0948843A2 (enExample) |

| JP (1) | JP3917193B2 (enExample) |

| WO (1) | WO1999012264A2 (enExample) |

Families Citing this family (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7200187B2 (en) * | 2001-07-26 | 2007-04-03 | O'brien Thomas J | Modulator for digital amplifier |

| EP1472791B1 (en) * | 2002-01-30 | 2006-09-06 | Koninklijke Philips Electronics N.V. | Electronic circuit with a sigma delta a/d converter |

| DE10331572B4 (de) * | 2003-07-11 | 2005-06-09 | Infineon Technologies Ag | Sigma-Delta-Wandleranordnung |

| US7423566B2 (en) * | 2003-09-12 | 2008-09-09 | Texas Instruments Incorporated | Sigma-delta modulator using a passive filter |

| US7098823B2 (en) * | 2004-01-15 | 2006-08-29 | Analog Devices, Inc. | Reduced chop rate analog to digital converter system and method |

| US7593483B2 (en) * | 2004-05-07 | 2009-09-22 | Broadcom Corporation | Nonlinear mapping in digital-to-analog and analog-to-digital converters |

| WO2006034177A1 (en) * | 2004-09-17 | 2006-03-30 | Analog Devices, Inc. | Multi-bit continuous-time front-end sigma-delta adc using chopper stabilization |

| US7193545B2 (en) * | 2004-09-17 | 2007-03-20 | Analog Devices, Inc. | Differential front-end continuous-time sigma-delta ADC using chopper stabilization |

| JP4122325B2 (ja) * | 2004-10-01 | 2008-07-23 | 松下電器産業株式会社 | 利得制御機能付きデルタシグマ変調回路 |

| US7463905B1 (en) * | 2004-12-09 | 2008-12-09 | Nortel Networks Limited | Cellular telephony mast cable reduction |

| TWI329977B (en) * | 2005-11-09 | 2010-09-01 | Realtek Semiconductor Corp | Operational amplifier and related noise seperation method thereof |

| DE102006004012B3 (de) * | 2006-01-27 | 2007-09-13 | Xignal Technologies Ag | Zeitkontinuierlicher Delta-Sigma-Analog-Digital-Wandler mit Operationsverstärkern |

| TWI307223B (en) * | 2006-02-09 | 2009-03-01 | Realtek Semiconductor Corp | Signal processing system capable of changing signal levels |

| US7679443B2 (en) * | 2006-08-31 | 2010-03-16 | Texas Instruments Incorporated | System and method for common mode translation |

| US7714757B2 (en) * | 2007-09-26 | 2010-05-11 | Medtronic, Inc. | Chopper-stabilized analog-to-digital converter |

| US7623053B2 (en) | 2007-09-26 | 2009-11-24 | Medtronic, Inc. | Implantable medical device with low power delta-sigma analog-to-digital converter |

| US7999710B2 (en) * | 2009-09-15 | 2011-08-16 | Texas Instruments Incorporated | Multistage chopper stabilized delta-sigma ADC with reduced offset |

| US8665128B2 (en) * | 2010-12-08 | 2014-03-04 | National Semiconductor Corporation | Sigma-delta difference-of-squares log-RMS to DC converter with forward path multiplier and chopper stabilization |

| US8665126B2 (en) * | 2010-12-08 | 2014-03-04 | National Semiconductor Corporation | ΣΔ difference-of-squares LOG-RMS to DC converter with forward and feedback paths signal squaring |

| EP2592751B1 (en) | 2011-11-14 | 2017-05-31 | Dialog Semiconductor GmbH | A sigma-delta modulator for increased volume resolution in audio output stages |

| JP6632425B2 (ja) * | 2016-02-26 | 2020-01-22 | 旭化成エレクトロニクス株式会社 | インクリメンタル型デルタシグマ変調器、変調方法、およびインクリメンタル型デルタシグマad変換器 |

| US9859907B1 (en) | 2016-10-28 | 2018-01-02 | Analog Devices, Inc. | Systems and methods for removing errors in analog to digital converter signal chain |

| US10298245B1 (en) | 2018-03-16 | 2019-05-21 | Synaptics Incorporated | Audio analog-to-digital converter systems and methods |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5030954A (en) * | 1990-09-17 | 1991-07-09 | General Electric Company | Double rate oversampled interpolative modulators for analog-to-digital conversion |

| US5461381A (en) * | 1993-12-13 | 1995-10-24 | Motorola, Inc. | Sigma-delta analog-to-digital converter (ADC) with feedback compensation and method therefor |

| US5838270A (en) * | 1995-01-12 | 1998-11-17 | Texas Instruments Incorporated | Second order and cascaded 2-1 oversampled modulators with improved dynamic range |

| US5724037A (en) * | 1995-05-23 | 1998-03-03 | Analog Devices, Inc. | Data acquisition system for computed tomography scanning and related applications |

| US5654711A (en) * | 1995-06-07 | 1997-08-05 | Asahi Kasei Microsystems Ltd. | Analog-to-digital converter with local feedback |

| US5729230A (en) * | 1996-01-17 | 1998-03-17 | Hughes Aircraft Company | Delta-Sigma Δ-Σ modulator having a dynamically tunable continuous time Gm-C architecture |

| US5754131A (en) * | 1996-07-01 | 1998-05-19 | General Electric Company | Low power delta sigma converter |

| US5907299A (en) * | 1996-10-23 | 1999-05-25 | Sonix Technologies, Inc. | Analog-to digital converter with delta-sigma modulator |

| DE19848778A1 (de) * | 1998-02-20 | 1999-09-02 | Hewlett Packard Co | Differenz-Bandpaß-Sigma-Delta-Analog-Digital- Wandler |

-

1998

- 1998-08-03 JP JP51648299A patent/JP3917193B2/ja not_active Expired - Fee Related

- 1998-08-03 WO PCT/IB1998/001187 patent/WO1999012264A2/en not_active Ceased

- 1998-08-03 EP EP98933856A patent/EP0948843A2/en not_active Withdrawn

- 1998-08-25 US US09/139,242 patent/US6404367B1/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| EP0948843A2 (en) | 1999-10-13 |

| US6404367B1 (en) | 2002-06-11 |

| WO1999012264A3 (en) | 1999-05-27 |

| JP2001505038A (ja) | 2001-04-10 |

| WO1999012264A2 (en) | 1999-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3917193B2 (ja) | 利得精度を改善したシグマ―デルタ変調器 | |

| JP3375967B2 (ja) | ディジタル論理ゲートコアを有するシグマ−デルタ変換器 | |

| JP3852721B2 (ja) | D/a変換器およびデルタシグマ型d/a変換器 | |

| US8077066B2 (en) | ΔΣ modulator | |

| CN1327618C (zh) | 具有电流模式dem和dem判决逻辑的多电平量化器增量总和调制器 | |

| US6369730B1 (en) | Sigma-delta analog-to-digital converter | |

| US20120242521A1 (en) | Method and circuit for continuous-time delta-sigma dac with reduced noise | |

| JP2892549B2 (ja) | スイッチトキャパシタ積分器 | |

| JPH1155121A5 (enExample) | ||

| CN105432020A (zh) | 具有主dac反馈延迟的量化噪声耦合δ-σadc | |

| CN101809863A (zh) | 自动共模抑制校准 | |

| JP2001094429A (ja) | アナログデジタル混在δς変調器 | |

| KR100472612B1 (ko) | 잡음성분을줄인1비트a/d변환장치 | |

| CN1203484A (zh) | 具有较高线性的数-模转换器件 | |

| US12176925B2 (en) | Sigma-delta analogue-to-digital converter with gmC-VDAC | |

| JPH08154058A (ja) | 選択装置およびこれを用いた無線装置 | |

| JP2005524152A (ja) | 演算増幅積分器 | |

| KR100946798B1 (ko) | 동적 범위가 향상된 시그마-델타 변조기 | |

| JP3372753B2 (ja) | オーバーサンプリング型a/d変換器 | |

| JP3344546B2 (ja) | デルタシグマ変調回路 | |

| Pelgrom | Time-Continuous Σ Δ Modulation | |

| JPH10209874A (ja) | アナログ−ディジタル変換器 | |

| JP2004007827A (ja) | A/d変換装置およびそのa/d変換方法 | |

| KR100330976B1 (ko) | 완전차동 준디지털 포스트필터를 사용한 시그마-델타 디지털-아날로그 변환기 | |

| Chen | VLSI Implementation of a High-Speed Delta-Sigma Analog to Digital Converter |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050803 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050803 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060725 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061025 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061212 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070208 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100216 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100216 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110216 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120216 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120216 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130216 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140216 Year of fee payment: 7 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |