JP3874577B2 - 電圧制御発振回路 - Google Patents

電圧制御発振回路 Download PDFInfo

- Publication number

- JP3874577B2 JP3874577B2 JP21227099A JP21227099A JP3874577B2 JP 3874577 B2 JP3874577 B2 JP 3874577B2 JP 21227099 A JP21227099 A JP 21227099A JP 21227099 A JP21227099 A JP 21227099A JP 3874577 B2 JP3874577 B2 JP 3874577B2

- Authority

- JP

- Japan

- Prior art keywords

- transistor

- voltage

- capacitor

- transistors

- current

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000010355 oscillation Effects 0.000 claims description 118

- 239000003990 capacitor Substances 0.000 claims description 56

- 238000012544 monitoring process Methods 0.000 claims description 16

- 238000007599 discharging Methods 0.000 claims description 12

- 238000006243 chemical reaction Methods 0.000 description 23

- 238000010586 diagram Methods 0.000 description 12

- 230000014509 gene expression Effects 0.000 description 10

- 230000003321 amplification Effects 0.000 description 3

- 238000003199 nucleic acid amplification method Methods 0.000 description 3

- 239000000470 constituent Substances 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

Images

Landscapes

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

Description

【発明の属する技術分野】

本発明は、発振周波数を電圧制御できる発振回路に係り、特に、電圧制御の容易性、信頼性の向上等を図ったものに関する。

【0002】

【従来の技術】

従来、この種の電圧制御発振回路の基本構成としては、例えば、図1に示されたようなものが公知・周知となっている。

すなわち、この電圧制御発振回路は、定電流源20と、この定電流源20と直列接続されたコンデンサ21と、このコンデンサ21の端子電圧を監視してその充放電を制御する振幅監視回路22とを主たる構成要素としてなるものである。

そして、定電流源20は、より具体的には、V/I変換回路23により構成されたものとなっている。

かかる電圧制御発振回路においては、振幅監視回路22によりコンデンサ21の両端の電圧が所望の2つのしきい値となったと判定された瞬間に、充放電が切り替えられるようになっており、コンデンサ21は、定電流Icにより充電される一方、放電電流Idで放電されるようになっている。

【0003】

このコンデンサ21における充放電の波形、換言すれば、発振波形は、図9に示されたように、いわゆる三角波となっており、その発振周波数fは、コンデンサ21の静電容量Cと、定電流Ic、放電電流Id及び発振振幅ΔV(図9参照)によって、下記する式1によって求められるものとなっている。

【0004】

f=Ic×Id/{ΔV×C(Ic+Id)}・・・(式1)

【0005】

ここで、V/I変換回路23の出力電流をIoscとし、Ic=k×Iosc、Id=j×Ioscとすれば(但し、k,jは実数)、式1は、下記する式2の如くに書き改めることができる。

【0006】

f=j×k×Iosc/{ΔV×C(j+k)}・・・(式2)

【0007】

したがって、図1に示された構成における電圧制御発振回路において、その発振周波数fの制御は、静電容量C、発振振幅ΔV及び、係数j,kを決めて、V/I変換回路23の出力電流Ioscを変化させることによって行うことができるものとなっており、発振周波数fは、電流Ioscに比例するものとなる。

【0008】

このような電圧制御発振回路において、その発振周波数の下限及び上限の制限は、次のようにして行われている。

まず、発振周波数fは、電流Ioscにより制御されるので、発振周波数fの下限及び上限の制限は、電流Ioscの取り得る範囲の制限により可能となる。このため、従来は、V/I変換回路23を図10に示されたような電流の加算/減算回路に構成することによって、電流Ioscの上限及び下限の制限ができるようにしていた。

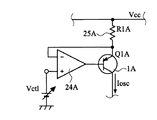

ここで、図10に示された回路において、演算増幅器24の出力側に接続されたトランジスタQ1に流れる電流I5は、制御電圧Vctlを電圧/電流変換して得られるもので、この電流I5を変化させることで発振周波数を変えることができるものとなっており、下記する式3によって表される。

【0009】

I5=Vctl/R5・・・(式3)

【0010】

なお、ここで、R5は、トランジスタQ1のエミッタとアースとの間に接続されたエミッタ抵抗器の抵抗値である。

また、図10に示された回路において、トランジスタQ10を流れる電流となる第6の定電流源36による電流I6及び第7の定電流源37による電流I7は、出力電流Ioscを下限と上限を定めるものとなっている。

すなわち、例えば、下限の発振周波数となる際の出力電流をIoscをIminとし、上限の発振周波数となる際の出力電流をIoscをImaxとすれば、この発振回路が通常の発振状態にある場合、すなわち、Imin<Iosc<Imaxである場合、出力電流Ioscは、下記する式4によって表されるものとなっている。

【0011】

Iosc=I6+I7−I5・・・(式4)

【0012】

この式4から先のImin及びImaxは、下記する式5、式6によって表される。

【0013】

Imin=I7・・・(式5)

【0014】

但し、I5≧I6(Vctl≧I6×R5)である。

【0015】

Imax=I6+I7・・・(式6)

【0016】

但し、I5=0(Vctl=0)である。

【0017】

そして、これら式3乃至式6に基づいて、制御電圧Vctlと出力電流Ioscとの関係は、図11に示されたようなものとなる。

発振周波数の下限及び上限は、式5,式6に示されたように電流によって定まるが、本来は、発振周波数の下限及び上限も電圧によって制御できるのが都合がよい。すなわち、先の電流Imin及びImaxが電圧で制御できると好都合であるが、そのためには、先の電流I6及びI7を生ずる回路部分を局部的なV/I変換回路とする必要がある。そのため、従来、例えば、図12に示されたように電流I6及びI7を生ずる回路部分を局部的なV/I変換回路としたものが用いられていた。

【0018】

図12において、I5=Vctl/R5であり、先の式3が成立することは、図10に示された回路と同様である。

そして、I6=V6/R6及びI7=V7/R7であるから、電流Imin及びImaxは、下記する式7,式8のように表される。

【0019】

Imin=V7/R7・・・(式7)

【0020】

Imax=V6/R6+V7/R7・・・(式8)

【0021】

ところで、このような電圧制御発振回路の実際の使用においては、例えば、冷陰極管を圧電トランスで点灯制御する場合等において、発振周波数の下限と上限の比が所定値となるように使用したい場合が多々生ずる。

このような用い方をするための従来の方法を説明すれば次の通りである。

図12に示された回路において、発振下限周波数をfminとし、発振上限周波数をfmaxとして、fmax=m×fminとしたい場合、先の式2により発振周波数は、充電電流Ioscに比例するので、Imax=m×Iminが成り立てばよいこととなる。

そこで、先の式7、式8より次の式9を得る。

【0022】

V6/R6=(m−1)×(V7/R7)・・・(式9)

【0023】

通常、抵抗器の抵抗値の誤差等の発振周波数への影響をキャンセルするため、R6=R7とし、その結果、式10を得る。

【0024】

V6:V7=(m−1):1・・・(式10)

【0025】

結局、発振下限周波数fminと発振上限周波数fmaxの比は、V6とV7の比で決定することができるものとなる。

このように、従来の電圧制御発振回路においては、その発振周波数の下限と上限とを決めて、かつ、それらを電圧によって制御しようとする場合には、V/I変換回路を図12に示されたような構成とし、所望の発振周波数の下限及び上限が得られるように電圧V6,V7並びに抵抗値R6,R7を適宜選択し、制御電圧Vctl及び抵抗値R5によって発振周波数を可変するものであった。

なお、発振周波数の下限と上限の両方を同時に設定せず、いずれか片側のみの設定の場合も上述したと同様に考えることができる。

【0026】

【発明が解決しようとする課題】

しかしながら、上述したような従来回路においては、発振上限周波数及び発振下限周波数を電圧制御するためには、図1におけるV/I変換回路23の部分を図12に示されたように、電流加算/減算回路と3つの局部的なV/I変換回路を設ける構成としなければならず、回路規模が大きくなり、素子数が増えて価格の上昇を招くばかりか、素子数の増加による回路の信頼性の低下をも招くこととなるという問題があった。

また、発振周波数の上限設定の電流Imaxを与える制御電圧Vctlの条件は、先に述べたように式3及び式6並びに図10から、Vctl=0であり、ゼロを越える任意の電圧で電流Imaxを得ようとすると、電流加算/減算回路の構成上、従来回路では実際には困難である。

さらに、発振下限周波数fminと発振上限周波数fmaxの比を、例えば、fmin:fmax=1:1.1程度の比較的小さな値とするような場合、従来回路においては、その実現のためには、式10から電圧比V6:V7=10:1となり、所望の周波数比と電圧比とが大きく異なるため、周波数の設定精度が低下し、設計が難しいという欠点があった。

【0027】

本発明は、上記実状に鑑みてなされたもので、発振周波数の上限及び下限又はいずれか一方を、外部から制御電圧を印加することで制御することができ、しかも、その制御電圧を任意の値に設定することができる簡易な回路構成を有する電圧制御発振回路を提供するものである。

本発明の他の目的は、発振周波数の上限及び下限の周波数比を、外部からの制御電圧の比と等しくすることのできる電圧制御発振回路を提供することにある。

【0028】

【課題を解決するための手段】

上記発明の目的を達成するため、本発明に係る電圧制御発振回路は、

コンデンサと、前記コンデンサへ所望の発振周波数に応じた電流を供給する電流供給手段と、前記コンデンサの充放電のタイミングを制御する振幅監視手段とを有し、前記振幅監視手段が前記コンデンサの端子電圧に応じて充放電のタイミングを制御することにより、前記コンデンサの両端に前記所望の発振周波数の信号が得られるよう構成されてなる電圧制御発振回路であって、

前記電流供給手段は、電圧クランプ回路と、前記電圧クランプ回路の出力段に設けられ、かつ、前記コンデンサへの通電路に直列に設けられた抵抗器とを具備してなり、

前記コンデンサへは、前記電圧クランプの出力電圧を前記抵抗器の抵抗値で除した電流が供給され、

前記電圧クランプ回路は、外部から印加される制御電圧が所定の最大値となった場合に、出力電圧が当該所定の最大値にクランプされる一方、前記制御電圧が所定の最小値となった場合に、出力電圧が当該所定の最小値にクランプされるよう構成されてなり、

前記所定の最大値は、発振周波数の上限において、前記コンデンサに必要とされる最大電流値と前記抵抗器の抵抗値との乗算値に等しく、

前記所定の最小値は、発振周波数の下限において、前記コンデンサに必要とされる最小電流値と前記抵抗器の抵抗値との乗算値に等しく設定されてなるものである。

【0029】

かかる構成においては、制御電圧を所定の最大値に設定した場合、所望する発振周波数の上限に必要とされる最大電流がコンデンサへ供給され、また、制御電圧を所定の最小値に設定した場合、所望する発振周波数の下限に必要とされる最小電流がコンデンサへ供給されるので、制御電圧の所定の最大値及び最小値へのそれぞれの設定と、発振周波数の上限と下限とが一対一に対応することとなり、外部からの制御電圧により発振周波数の上限及び下限の設定が従来に比して容易となるものである。

【0030】

また、コンデンサと、前記コンデンサへ所望の発振周波数に応じた電流を供給する電流供給手段と、前記コンデンサの充放電のタイミングを制御する振幅監視手段とを有し、前記振幅監視手段が前記コンデンサの端子電圧に応じて充放電のタイミングを制御することにより、前記コンデンサの両端に前記所望の発振周波数の信号が得られるよう構成されてなる電圧制御発振回路であって、

前記電流供給手段は、非反転入力端子に外部からの制御電圧が印加される演算増幅器と、

前記演算増幅器の出力電圧が印加されるnpn形の第1のトランジスタと、

前記第1のトランジスタと直列接続された抵抗器とを具備し、前記第1のトランジスタのコレクタ側から前記コンデンサへの供給電流が得られるよう構成されてなり、

前記演算増幅器は、npn形の第2及び第3のトランジスタにより構成されてなる差動回路が設けられ、前記第2及び第3のトランジスタのエミッタとアースとの間には第1の定電流源が設けられる一方、前記第2及び第3のトランジスタのコレクタ側には、pnp形の第4及び第5のトランジスタにより構成されてなるカレントミラー回路による能動負荷が設けられ、

前記第2のトランジスタには、npn形の第6のトランジスタが並列接続されて、これら第2及び第6のトランジスタにより構成されてなる差動回路が設けられ、

前記第6のトランジスタのベースには、pnp形の第7のトランジスタのエミッタが接続されると共に、当該エミッタには、第2の定電流源が接続され、前記第7のトランジスタのコレクタは、アースに接続され、前記第7のトランジスタのベースには、所定の最小電圧が印加され、

前記第3のトランジスタのベースには、pnp形の第8のトランジスタのエミッタが接続されると共に、当該エミッタには、第3の定電流源が接続される一方、前記第8のトランジスタのコレクタは、アースに接続され、前記第8のトランジスタのベースは、反転入力端子とされ、

pnp形の第9及び第10のトランジスタにより構成されてなる差動回路が設けられ、前記第9及び第10のトランジスタのエミッタは、前記第2のトランジスタのベースに接続されると共に、当該エミッタには、第4の定電流源が接続される一方、前記第9及び第10のコレクタは、共にアースに接続され、前記第9のトランジスタのベースは、外部からの制御電圧が印加される非反転入力端子とされ、前記第10のトランジスタのベースには、所定の最大電圧が印加され、

前記所定の最大電圧は、発振周波数の上限において、前記コンデンサに必要とされる最大電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記所定の最小電圧は、発振周波数の下限において、前記コンデンサに必要とされる最小電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記第2のトランジスタのコレクタから出力電圧を得るよう構成されてなるものも好適である。

【0031】

かかる構成においては、第1のトランジスタは、そのベースが演算増幅器の出力端子に接続され、そのエミッタとアースとの間に抵抗器が接続されると共に、当該エミッタは、演算増幅器の反転入力端子に接続されるものとなっている。

また、第2の定電流源は、第7のトランジスタのエミッタと電源ラインとの間に接続され、第3の定電流源は、第8のトランジスタのエミッタと電源ラインとの間に接続され、第4の定電流源は、第9及び第10のトランジスタのエミッタと電源ラインとの間に接続されるものである。

さらに、第4及び第5のトランジスタは、相互にベースが接続されると共に、第5のトランジスタのベースとコレクタとが接続される一方、第4及び第5のトランジスタのコレクタには、電源電圧が印加され、また、第4のトランジスタのエミッタは、第2のトランジスタのコレクタに、第5のトランジスタのコレクタは、第3のトランジスタのコレクタに、それぞれ接続されるものである。

【0032】

このような構成とすることにより、制御電圧を所定の最大値に設定した場合、所望する発振周波数の上限に必要とされる最大電流がコンデンサへ供給され、また、制御電圧を所定の最小値に設定した場合、所望する発振周波数の下限に必要とされる最小電流がコンデンサへ供給されるので、制御電圧の所定の最大値及び最小値へのそれぞれの設定と、発振周波数の上限と下限とが一対一に対応することとなり、外部からの制御電圧により発振周波数の上限及び下限の設定が従来に比して容易となるものである。

【0033】

【発明の実施の形態】

以下、本発明の実施の形態について、図1乃至図7を参照しつつ説明する。

なお、以下に説明する部材、配置等は本発明を限定するものではなく、本発明の趣旨の範囲内で種々改変することができるものである。なお、従来回路の説明において用いた図1の回路構成は、本発明の実施の形態における電圧制御発振回路と基本的に同一であるため、以下の説明においても図1を用いることとして、同一構成要素については、同一の符号を用いるものとする。

【0034】

まず、本発明の実施の形態における電圧制御発振回路の基本的構成としては、図1に示されたように従来回路と基本的に同一である。

すなわち、電圧制御発振回路は、定電流源20と、この定電流源20と直列接続されたコンデンサ21と、このコンデンサ21の端子電圧を監視してその充放電を制御する振幅監視回路22とを主たる構成要素としてなるものである。そして、定電流源20は、より具体的には、V/I変換回路(電圧・電流変換回路)23Aにより構成されたものとなっている。

本発明に係る電圧制御発振回路は、特に、V/I変換回路23Aにおける演算増幅器24Aの回路構成を、発振周波数の上限及び下限又はいずれか一方が、任意の値に設定できる制御電圧によって制御することができるようにした点(詳細は後述)が従来と異なるものである。

【0035】

図1に示された構成において、V/I変換回路23Aは、制御電圧Vctlを電流に変換するためのもので、演算増幅器24Aと、第1のトランジスタ(図1においては「Q1」と表記)1と、エミッタ抵抗器25とを主たる構成要素としてなるものである。

演算増幅器24Aの出力端には、npn形の第1のトランジスタ1のベースが接続され、この第1のトランジスタ1のエミッタと演算増幅器24Aの非反転入力端子とが接続されると共に、第1のトランジスタ1のエミッタとアースとの間には、エミッタ抵抗器 が接続されている。そして、演算増幅器24Aの非反転入力端子に印加される制御電圧Vctlを変えることで、第1のトランジスタ1のコレクタ側に出力される電流Ioscが変化されるようになっている。

【0036】

また、振幅監視手段としての振幅監視回路22によりコンデンサ21の両端の電圧が所望の2つのしきい値となったと判定された瞬間に、充放電が切り替えられるようになっており、コンデンサ21は、定電流Icにより充電される一方、放電電流Idで放電されるようになっており、この基本的な動作は従来と変わるところがないものである。

【0037】

次に、図2を参照しつつこの発明の実施の形態におけるV/I変換回路23Aに用いられる演算増幅器24Aの内部における回路構成例について説明する。

まず、制御電圧Vctlが印加される非反転入力端子(図2においては「in+」の表記がなされた箇所)に、pnp形の第9のトランジスタ(図2においては「Q9」と表記)9のベースが接続され、この第9のトランジスタ9のコレクタは、アースに接続される一方、エミッタは、pnp形の第10のトランジスタ(図2においては「Q10」と表記)10のエミッタと共に、定電流I4を出力する第4の定電流源34に接続されている。

第10のトランジスタ10は、コレクタがアースに接続される一方、ベースには、発振上限周波数を定める電圧Vmaxが印加されるようになっており、この第10のトランジスタ10は、先の第9のトランジスタ9と、エミッタ共通の第1の差動回路を形成するものとなっている。

【0038】

また、npn形の第2のトランジスタ(図2においては「Q2」と表記)2とnpn形の第6のトランジスタ(図2においては「Q6」と表記)6とが、相互にエミッタが接続されて、その接続点とアースとの間に定電流I1を出力する第1の定電流源31が接続される一方、コレクタ同士が接続されて、第2及び第6のトランジスタ2,6により局部的なエミッタ共通の第2の差動回路が構成されたものとなっている。

この第2及び第6のトランジスタ2,6のコレクタは、pnp形の第4のトランジスタ(図2においては「Q4」と表記)4のコレクタに接続されており、第4のトランジスタ4のエミッタには、電源電圧Vccが印加されるようになっている。

【0039】

そして、第2のトランジスタ2のベースは、先の第9及び第10のトランジスタ9,10のエミッタと第4の定電流源34の接続点に接続される一方、第6のトランジスタ6のベースは、pnp形の第7のトランジスタ(図2においては「Q7」と表記)7のエミッタと定電流I2を出力する第2の定電流源32との接続点に接続されたものとなっている。

第7のトランジスタ7は、そのコレクタがアースに接続される一方、ベースには、発振下限周波数を定める電圧Vminが印加されるようになっている。

また、npn形の第3のトランジスタ(図2においては「Q3」と表記)3と、pnp形の第5のトランジスタ(図2においては「Q5」と表記)5とが相互にコレクタが接続される一方、第3のトランジスタ3のエミッタは、第2及び第6のトランジスタ2,6のエミッタと相互に接続され、また、第5のトランジスタ5のエミッタには、電源電圧Vccが印加されるようになっている。

【0040】

そして、第5のトランジスタ5のベースは、先の第4のトランジスタ4のベースに接続されると共に、第5のトランジスタ5のコレクタに接続されており、第4及び第5のトランジスタ4,5は、いわゆるカレントぺアを構成して、第2及び第3のトランジスタ2,3に対する能動負荷となっている。

また、第3のトランジスタ3のベースは、定電流I3を出力する第3の定電流源33とpnp形の第8のトランジスタ8のエミッタとの接続点に接続されたものとなっている。そして、第2及び第3のトランジスタ2,3は、第3の差動回路を構成するものとなっている。

【0041】

第8のトランジスタ(図2においては「Q8」と表記)8は、そのコレクタがアースに接続される一方、ベースは、反転入力端子となっている(図2においては「in−」と表記)。

なお、第4のトランジスタ4のコレクタと第2のトランジスタ2のコレクタとの接続点は、演算増幅器24Aの初段出力となっている。

この初段出力の後には、公知・周知の増幅段を設けてさらに増幅した後にこの演算増幅器24Aの最終出力としても、また、増幅段を設けることなくこの初段出力を演算増幅器24Aの最終出力としてもいずれでもよいものである。

【0042】

図3には、図1における第1のトランジスタ1及びエミッタ抵抗器25を図2示された回路に接続した場合の構成例が示されており、以下、これについて説明する。なお、図2に示された構成要素と同一の構成要素については、同一の符号を付してその詳細な説明を省略し、以下、異なる点を中心に説明する。

この図3に示された回路構成例においては、第2及び第4のトランジスタ2,4の相互のコレクタの接続点が演算増幅器24Aの外部においてpnp形の第16のトランジスタ16のベースに接続されている。

この第16のトランジスタ16は、エミッタに電源電圧Vccが印加されるようになっている一方、コレクタは、第8の抵抗器(図3においては「R8」と表記)48を介してアースに接続されている。

さらに、第16のトランジスタ16のコレクタは、npn形の第1のトランジスタ1のベースに接続されている。

なお、この第1のトランジスタ1は、図1においても示されたようにエミッタがエミッタ抵抗器25を介してアースに接続されたものとなっていると共に、そのエミッタは、演算増幅器24A内の第8のトランジスタ8のベースに接続されたものとなっている。

【0043】

次に、かかる構成における動作について図3を参照しつつ説明する。

まず、図3に示された回路構成例に示された演算増幅器24Aの内部の回路部分は、電圧・電流変換を行う回路であると同時に、いわゆる電圧クランプ回路と捉えることもできるものとなっている。

すなわち、制御電圧VctlがVctl=Vminとなった場合、第9及び第10のトランジスタ9,10による第1の差動回路においては、第9のトランジスタ9のべース電圧がVminであり、第10のトランジスタ10のベース電圧であるVmaxに対してVmin<Vmaxであるため、第9のトランジスタ9が動作状態となる。

これによって、第2のトランジスタ2のベース電圧は、ほぼVminとなる。一方、この第2のトランジスタ2と第2の差動回路を構成する第6のトランジスタ6のベース電圧もほぼVminであるため、第2及び第6のトランジスタ2,6共に動作状態となり、これらの相互のコレクタ電圧は、ほぼVminにクランプされることとなる。

【0044】

また、制御電圧VctlがVctl=Vmaxとなった場合は、第9及び第10のトランジスタ9,10のそれぞれのベース電圧が同一となるため、第9及び第10のトランジスタ9,10の双方が動作状態となり、第2のトランジスタ2のベース電圧は、ほぼVmaxとなる。

これに対して、第6のトランジスタ6のベース電圧は,VminでありVmin<Vmaxであるため、第2のトランジスタ2が動作状態となり、第6のトランジスタ6は、非動作状態となる。これによって、第2のトランジスタ2のコレクタ電圧は、ほぼVmaxにクランプされることとなる。

したがって、第1のトランジスタ1のエミッタとエミッタ抵抗器25との接続点における電圧Voは、下記する式11で表される範囲にクランプされる。

【0045】

Vmin≦Vo≦Vmax・・・(式11)

【0046】

なお、ここで、Vminは、クランプ下限電圧であり、Vmaxは、クランプ上限電圧である。

ここで、第1のトランジスタ1のコレクタ電流をIoscとすれば、この電流Ioscは、電圧Voとエミッタ抵抗器25の抵抗値R1によって決定されるものとなる。そして、式11との関係から、電流Ioscは、下記する式12の範囲に制御されることとなる。

【0047】

Vmin/R1≦Iosc≦Vmax/R1・・・(式12)

【0048】

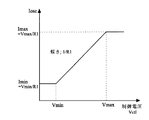

なお、図4には、図2及び図3に示された構成における制御電圧Vctlの変化に対する電流Ioscの変化を示した特性曲線が示されている。同図によれば、制御電圧VctlがVctl=Vminにおいて、Ioscは最小電流Iminとなり、その大きさは、Imin=Vmin/R1となり、Vctl=Vmaxにおいて、Ioscは最大電流Imaxとなり、その大きさは、Imax=Vmax/R1となることが表されている。

【0049】

図1に示された回路構成における発振周波数fは、Ioscに比例することは公知・周知のことである(式2参照)。

したがって、発振周波数fは、Iosc=Iminで下限の周波数fminに、Iosc=Imaxで上限の周波数fmaxに、それぞれ設定されることとなる。

なお、発振周波数の下限を得る際の制御電圧Vctlは、Vminであり、発振周波数の上限を得る際の制御電圧Vctlは、Vmaxであるというのは、理想的な場合であって、厳密には、若干の誤差が生ずる。

すなわち、具体的には、制御電圧Vctl=Vminの場合、発振周波数は、その下限周波数より若干高めとなり(換言すれば、電流IoscがIminより若干大きめの値となる)、また、制御電圧Vctl=Vmaxの場合、発振周波数は、その上限周波数より若干低めとなる(換言すれば、電流IoscがImaxより若干小さめ値となる)。

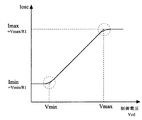

図5には、上述の様子が示されている。すなわち、同図においては、制御電圧Vctlの変化に対する実際の電流Ioscの変化が実線太線の特性曲線として表されると共に、制御電圧Vctl=Vmin及びVctl=Vmaxの付近において、実線細線の折れ線が理想特性線となっている。

なお、理想特性からのずれの大きさは、通常、Vmin±0.15及びVmax±0.15程度の範囲で生じるものとなっている。

【0050】

このような電圧のずれが生ずるのは、例えば、Vctl=Vmaxの場合、第9及び第10のトランジスタ9,10の両方が動作状態となっているためであり、第9及び第10のトランジスタ9,10により差動回路が構成されていることに起因するものである。これは、Vctl=Vminの場合についても同様である(すなわち、Vctl=Vminの際、第2及び第6のトランジスタ2,6の双方が動作状態となり、これらが差動回路を構成するため理想の動作との電圧のずれが生ずる)。

現実的には、図5に示されたような特性曲線を得、これに基づいて、制御電圧VctlをVminより低く、また、制御電圧VctlをVmaxより高く、それぞれ設定することで、Ioscを正確にImin又はImaxとすることができ、実用上の影響はない。

【0051】

ここで、発振周波数fの範囲は、次のように表すことができる。

まず、発振周波数fと電流Ioscとの関係は、従来の場合と同様で、式2によって表すことができる。

【0052】

f=j×k×Iosc/{ΔV×C(j+k)}・・・(式2)

【0053】

これに先の式12を適用することにより、発振周波数fの範囲は式13のように表される。

【0054】

j×k×Vmin/{ΔV×C×R1(j+k)}≦f≦j×k×Vmax/{ΔV×C×R1(j+k)}・・・(式13)

【0055】

また、これまでの説明により発振周波数の上限と下限の比は、下記する式14によって表される。

【0056】

fmin:fmax=Vmin:Vmax・・・(式14)

【0057】

図2に示された回路構成例は、入力トランジスタ、すなわち、第8及び第9のトランジスタ8,9がpnp形の場合の構成例であるが、この入力トランジスタをnpn形とした場合の回路構成例が図6に示されており、以下、同図を参照しつつこの第2の回路構成例について説明する。

この第2の回路構成例は、トランジスタの極性が図2に示された回路構成例と異なることに起因する接続の違いがあるだけで、基本的な構成は図2に示された回路構成例と異なるところがないものである。

このため、図6においては、図2に示された回路構成例における構成要素と対応する構成要素については、図2における当該構成要素の符号の後に、「A」を付した符号を用いることとした。例えば、図2における第9のトランジスタ9に対応する図6における第9のトランジスタ9Aの如くである。また、図6における他の表記(電流等)においても、図2における表記に対応するものについては、「A」を付したものとして構成要素の符号の場合と同様な表し方をした。

【0058】

この図6に示された回路構成例における回路接続については、トランジスタの極性が図2に示された回路構成例と異なることに起因するものであるだけなので、その詳細な説明は省略し、印加電圧の接続位置の違いについてのみ言及する。

すなわち、この図6に示された回路構成例においては、第10のトランジスタ10Aのベースに、発振下限周波数を定める電圧Vminが印加される一方、第7のトランジスタ7Aのベースに発振上限周波数を定める電圧Vmaxが印加されたものとなっており、丁度、図2に示された印加電圧の配置を入れ替えたものとなっている。

なお、回路動作についても、トランジスタの極性の違いに起因する個々の部分での違いはあるものの、制御電圧Vctl=Vminにおいて、発振下限周波数fminが、制御電圧Vctl=Vmaxにおいて、発振上限周波数fmaxが、それぞれ得られるという基本的な点においては、図2において先に説明したと同様であるので、ここでの詳細な説明は省略するものとする。

【0059】

次に、図7には、図1における第1のトランジスタ1をpnp形とした場合の構成例が示されており、以下、同図を参照しつつこの回路構成例について説明する。

この回路構成例において、pnp形の第1のトランジスタ1Aのコレクタが出力電流Ioscを外部へ取り出す出力端となっている点は、図1の場合と同様であるが、エミッタにエミッタ抵抗器25Aを介して電源電圧Vccが印加されるように構成された点が図1の場合と異なっている。

そして、演算増幅器24Aの非反転入力端子には、制御電圧Vctlが印加される一方、反転入力端子には、第1のトランジスタ1Aのエミッタが接続された構成となっている。なお、動作については、基本的に図1に示されたものと変わるところがないので、ここでの詳細な説明は省略することとする。

【0060】

上述した発明の実施の形態においては、発振周波数の上限と下限の双方を設定した場合についての回路構成例について説明したが、いずれか一方を設定する場合であっても基本的な回路構成は変わるところがない。

すなわち、具体的には、例えば、図2に示された回路構成例において、発振周波数の下限、すなわち、fminのみを設定したい場合には、第10のトランジスタ10のベースへの印加電圧Vmaxを、電源電圧Vccとするか、又は第10のトランジスタ10を削除した構成とすればよい。

一方、fmaxのみを設定したい場合には、例えば、図2に示された回路構成例において、第7のトランジスタ7のベースへの印加電圧Vminを、アース電位とするか、又は第6及び第7のトランジスタ6,7並びに第2の定電流源32を削除した構成とすればよい。

さらに、図2に示された回路構成において、その出力部分を従来のgmアンプ(コンダクタンス・アンプ)型としてもよい。

【0061】

【発明の効果】

以上、述べたように、本発明によれば、外部からの制御電圧を所定の最大電圧に設定した場合には、発振周波数が所望する上限値となり、制御電圧を所定の最小電圧に設定した場合には、発振周波数が所望する下限値となり、しかも、所定の最大電圧対所定の最小電圧の比が、所望する発振周波数の上限対所望する発振周波数の下限の比と等しくなる電圧制御発振回路を提供することができる。

特に、電圧クランプ回路を用いて構成することにより、発振周波数の上限及び下限を定めるそれぞれの制御電圧の値を任意に設定することができ、比較的簡易な回路構成となるという効果を奏するものである。

【図面の簡単な説明】

【図1】電圧制御発振回路の基本構成を示す構成図である。

【図2】本発明に係る電圧制御発振回路において用いられるV/I変換回路の演算増幅器の内部の第1の回路構成例を示す回路図である。

【図3】図2に示された回路構成例を用いた場合のV/I変換回路の回路構成例を示す回路図である。

【図4】図2に示された回路構成例における制御電圧Vctlと出力電流Ioscとの関係を示す特性線図である。

【図5】図2に示された回路構成例における制御電圧Vctlの変化に対する出力電流Ioscの現実の回路における変化を示す特性線図である。

【図6】本発明に係る電圧制御発振回路において用いられるV/I変換回路の演算増幅器の内部の第2の回路構成例を示す回路図である。

【図7】本発明に係る電圧制御発振回路において用いられるV/I変換回路の出力部分の他の回路構成例を示す回路図である。

【図8】従来の電圧制御発振回路における演算増幅の内部の回路構成例であって、出力部分をgmアンプ形式とした場合の回路構成例を示す回路図である。

【図9】電圧制御発振回路におけるコンデンサの充放電電圧の変化を示す特性線図である。

【図10】従来回路において、発振周波数の上限及び下限を設定する場合のV/I変換回路の回路構成例を示す回路図である。

【図11】図10に示された回路における制御電圧Vctlと出力電流Ioscとの関係を示す特性線図である。

【図12】図10に示された回路において、電流I6及びI7が生ずる部分を局部的なV/I変換回路とした場合の回路構成例を示す回路図である。

【符号の説明】

20…定電流源

21…コンデンサ

22…振幅監視回路

23A…V/I変換回路

24A…演算増幅器

Claims (4)

- コンデンサと、前記コンデンサへ所望の発振周波数に応じた電流を供給する電流供給手段と、前記コンデンサの充放電のタイミングを制御する振幅監視手段とを有し、前記振幅監視手段が前記コンデンサの端子電圧に応じて充放電のタイミングを制御することにより、前記コンデンサの両端に前記所望の発振周波数の信号が得られるよう構成されてなる電圧制御発振回路であって、

前記電流供給手段は、電圧クランプ回路と、前記電圧クランプ回路の出力段に設けられ、かつ、前記コンデンサへの通電路に直列に設けられた抵抗器とを具備してなり、

前記コンデンサへは、前記電圧クランプの出力電圧を前記抵抗器の抵抗値で除した電流が供給され、

前記電圧クランプ回路は、外部から印加される制御電圧が所定の最大値となった場合に、出力電圧が当該所定の最大値にクランプされる一方、前記制御電圧が所定の最小値となった場合に、出力電圧が当該所定の最小値にクランプされるよう構成されてなり、

前記所定の最大値は、発振周波数の上限において、前記コンデンサに必要とされる最大電流値と前記抵抗器の抵抗値との乗算値に等しく、

前記所定の最小値は、発振周波数の下限において、前記コンデンサに必要とされる最小電流値と前記抵抗器の抵抗値との乗算値に等しいことを特徴とする電圧制御発振回路。 - コンデンサと、前記コンデンサへ所望の発振周波数に応じた電流を供給する電流供給手段と、前記コンデンサの充放電のタイミングを制御する振幅監視手段とを有し、前記振幅監視手段が前記コンデンサの端子電圧に応じて充放電のタイミングを制御することにより、前記コンデンサの両端に前記所望の発振周波数の信号が得られるよう構成されてなる電圧制御発振回路であって、

前記電流供給手段は、非反転入力端子に外部からの制御電圧が印加される演算増幅器と、

前記演算増幅器の出力電圧が印加されるnpn形の第1のトランジスタと、

前記第1のトランジスタと直列接続された抵抗器とを具備し、前記第1のトランジスタのコレクタ側から前記コンデンサへの供給電流が得られるよう構成されてなり、

前記演算増幅器は、npn形の第2及び第3のトランジスタにより構成されてなる差動回路が設けられ、前記第2及び第3のトランジスタのエミッタとアースとの間には第1の定電流源が設けられる一方、前記第2及び第3のトランジスタのコレクタ側には、pnp形の第4及び第5のトランジスタにより構成されてなるカレントミラー回路による能動負荷が設けられ、

前記第2のトランジスタには、npn形の第6のトランジスタが並列接続されて、これら第2及び第6のトランジスタにより構成されてなる差動回路が設けられ、

前記第6のトランジスタのベースには、pnp形の第7のトランジスタのエミッタが接続されると共に、当該エミッタには、第2の定電流源が接続され、前記第7のトランジスタのコレクタは、アースに接続され、前記第7のトランジスタのベースには、所定の最小電圧が印加され、

前記第3のトランジスタのベースには、pnp形の第8のトランジスタのエミッタが接続されると共に、当該エミッタには、第3の定電流源が接続される一方、前記第8のトランジスタのコレクタは、アースに接続され、前記第8のトランジスタのベースは、反転入力端子とされ、

pnp形の第9及び第10のトランジスタにより構成されてなる差動回路が設けられ、前記第9及び第10のトランジスタのエミッタは、前記第2のトランジスタのベースに接続されると共に、当該エミッタには、第4の定電流源が接続される一方、前記第9及び第10のコレクタは、共にアースに接続され、前記第9のトランジスタのベースは、外部からの制御電圧が印加される非反転入力端子とされ、前記第10のトランジスタのベースには、所定の最大電圧が印加され、

前記所定の最大電圧は、発振周波数の上限において、前記コンデンサに必要とされる最大電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記所定の最小電圧は、発振周波数の下限において、前記コンデンサに必要とされる最小電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記第2のトランジスタのコレクタから出力電圧を得るよう構成されてなることを特徴とする電圧制御発振回路。 - コンデンサと、前記コンデンサへ所望の発振周波数に応じた電流を供給する電流供給手段と、前記コンデンサの充放電のタイミングを制御する振幅監視手段とを有し、前記振幅監視手段が前記コンデンサの端子電圧に応じて充放電のタイミングを制御することにより、前記コンデンサの両端に前記所望の発振周波数の信号が得られるよう構成されてなる電圧制御発振回路であって、

前記電流供給手段は、非反転入力端子に外部からの制御電圧が印加される演算増幅器と、

前記演算増幅器の出力電圧が印加されるnpn形の第1のトランジスタと、

前記第1のトランジスタと直列接続された抵抗器とを具備し、前記第1のトランジスタのコレクタ側から前記コンデンサへの供給電流が得られるよう構成されてなり、

前記演算増幅器は、pnp形の第2及び第3のトランジスタにより構成されてなる差動回路が設けられ、前記第2及び第3のトランジスタのエミッタには、第1の定電流源が接続される一方、前記第2及び第3のトランジスタのコレクタ側には、npn形の第4及び第5のトランジスタにより構成されてなるカレントミラー回路による能動負荷が設けられ、

前記第2のトランジスタには、pnp形の第6のトランジスタが並列接続されて、これら第2及び第6のトランジスタにより構成されてなる差動回路が設けられ、

前記第6のトランジスタのベースには、npn形の第7のトランジスタのエミッタが接続されると共に、当該エミッタとアースとの間には、第2の定電流源が設けられ、前記第7のトランジスタのコレクタには、電源電圧が印加され、前記第7のトランジスタのベースには、所定の最大電圧が印加され、

前記第3のトランジスタのベースには、npn形の第8のトランジスタのエミッタが接続されると共に、当該エミッタとアースとの間には、第3の定電流源が設けられる一方、前記第8のトランジスタのコレクタには電源電圧が印加され、前記第8のトランジスタのベースは、反転入力端子とされ、

npn形の第9及び第10のトランジスタにより構成されてなる差動回路が設けられ、前記第9及び第10のトランジスタのエミッタは、前記第2のトランジスタのベースに接続されると共に、当該エミッタとアースとの間には、第4の定電流源が設けられる一方、前記第9及び第10のコレクタには、電源電圧が印加され、前記第9のトランジスタのベースは、外部からの制御電圧が印加される非反転入力端子とされ、前記第10のトランジスタのベースには、所定の最小電圧が印加され、

前記所定の最大電圧は、発振周波数の上限において、前記コンデンサに必要とされる最大電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記所定の最小電圧は、発振周波数の下限において、前記コンデンサに必要とされる最小電流値と前記抵抗器の抵抗値との乗算値に等しく設定され、

前記第2のトランジスタのコレクタから出力電圧を得るよう構成されてなることを特徴とする電圧制御発振回路。 - npn形の第1のトランジスタをpnp形に変え、当該第1のトランジスタのエミッタには、抵抗器を介して電源電圧が印加されると共に、当該エミッタは、演算増幅器の反転入力端子に接続されたことを特徴とする請求項2または請求項3いずれか記載の電圧制御発振回路。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP21227099A JP3874577B2 (ja) | 1999-07-27 | 1999-07-27 | 電圧制御発振回路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP21227099A JP3874577B2 (ja) | 1999-07-27 | 1999-07-27 | 電圧制御発振回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2001044808A JP2001044808A (ja) | 2001-02-16 |

| JP3874577B2 true JP3874577B2 (ja) | 2007-01-31 |

Family

ID=16619821

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP21227099A Expired - Fee Related JP3874577B2 (ja) | 1999-07-27 | 1999-07-27 | 電圧制御発振回路 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3874577B2 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6624873B2 (ja) | 2015-09-30 | 2019-12-25 | エイブリック株式会社 | 発振回路 |

-

1999

- 1999-07-27 JP JP21227099A patent/JP3874577B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2001044808A (ja) | 2001-02-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US3237116A (en) | Amplifiers and corrective circuits therefor | |

| JPH0420238B2 (ja) | ||

| AU599296B2 (en) | Temperature stabilized rf detector | |

| US6584380B1 (en) | Approximate third-order function generator, temperature compensation quartz oscillation circuit made by using the same, and temperature compensation method | |

| JP4031630B2 (ja) | オシレータ回路等の電子デバイスによって生成される交流信号の振幅制御 | |

| JPH01108801A (ja) | 温度補償型圧電発振器 | |

| JPS5922433A (ja) | 温度補償用回路 | |

| JP3874577B2 (ja) | 電圧制御発振回路 | |

| JPH0537822A (ja) | ガンマ補正回路 | |

| JP2710507B2 (ja) | 増幅回路 | |

| JPH0563523A (ja) | 波形発生装置 | |

| JP3600187B2 (ja) | エミッタフォロワ回路 | |

| JPH0232719B2 (ja) | ||

| JP2798490B2 (ja) | 発振回路 | |

| JPH0427218Y2 (ja) | ||

| JPS5941636Y2 (ja) | Cmos発振回路 | |

| RU2222048C2 (ru) | Функциональный генератор | |

| JP2974304B1 (ja) | タイマ回路 | |

| JPH0410982B2 (ja) | ||

| JPS6133710Y2 (ja) | ||

| JP2581388B2 (ja) | データ反転回路 | |

| JPS6119141B2 (ja) | ||

| JPH0313115A (ja) | 発振回路 | |

| JP2957796B2 (ja) | 移相回路 | |

| JPH07106872A (ja) | 高スルーレート演算増幅器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050531 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060718 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20060913 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20061010 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20061024 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091102 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121102 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141102 Year of fee payment: 8 |

|

| LAPS | Cancellation because of no payment of annual fees |