JP3768829B2 - 光電変換半導体装置およびその製造方法 - Google Patents

光電変換半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP3768829B2 JP3768829B2 JP2001125746A JP2001125746A JP3768829B2 JP 3768829 B2 JP3768829 B2 JP 3768829B2 JP 2001125746 A JP2001125746 A JP 2001125746A JP 2001125746 A JP2001125746 A JP 2001125746A JP 3768829 B2 JP3768829 B2 JP 3768829B2

- Authority

- JP

- Japan

- Prior art keywords

- photoelectric conversion

- semiconductor layer

- transistor

- layer

- semiconductor device

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Bipolar Integrated Circuits (AREA)

- Light Receiving Elements (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Bipolar Transistors (AREA)

- Element Separation (AREA)

Description

【発明の属する技術分野】

本発明は、光電変換半導体装置およびその製造方法に関するもので、これらの半導体装置の性能の向上を実現するためのものである。

【0002】

【従来の技術】

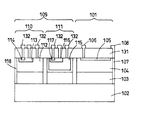

光電変換半導体装置の第1の従来例を図17に示す。図17において、101は光電変換部である。102は第1導電型(例えば、P型)の半導体基板、例えばシリコン中にP型不純物のボロンにより不純物濃度が1×1020 atms/cm3 程度に調整された半導体基板である。103は半導体基板102上に形成された第1導電型の真性半導体層(IntrinsicのIをとってI層)であり、例えばP型不純物としてボロンの不純物濃度が1×1012 atms/cm3 から1×1013 atms/cm3 程度に調整された例えばシリコンを用いた真性半導体層である。104は真性半導体層103上に形成された第2導電型(例えば、N型)の半導体層であり、例えばシリコン中にN型不純物のリンにより調整され形成された第2導電型の半導体層である。105はアノード用に表面を低抵抗化する目的で例えばヒ素を用いて導入された第2導電型拡散層である。

【0003】

上記の半導体基板102、真性半導体層103および半導体層104より、P型層−I層−N型層の連続積層構造を形成し、光電変換用PINダイオードを形成している。106はPINダイオードのアノード電極である。107はカソードへ接続するための第1導電型拡散層である。108はPINダイオードからの信号を取り出すカソード電極である。

【0004】

109はカソード電極108から取り出された、光電変換された信号を制御する制御部であり、110はNPNバイポーラ型トランジスタ、111はPNPバイポーラ型トランジスタである。

【0005】

ここで、112は半導体層104内に形成されたNPNバイポーラ型トランジスタ110のコレクタであり、113は例えば不純物としてボロンを用いて形成されたNPNバイポーラ型トランジスタ110のベースであり、114は例えば不純物としてヒ素を用いて形成されたNPNバイポーラ型トランジスタ110のエミッタである。

【0006】

また、115は例えば不純物としてボロンを用いて形成されたPNPバイポーラ型トランジスタ111のコレクタであり、116は例えば不純物としてリンを用いて形成されたPNPバイポーラ型トランジスタ111のベースであり、117は例えば不純物としてボロンを用いて形成されたPNPバイポーラ型トランジスタ111のエミッタである。

【0007】

118は、光電変換部101、NPNバイポーラ型トランジスタ110およびPNPバイポーラ型トランジスタ111の各素子を分離する拡散分離領域である。

【0008】

131は層間絶縁膜である。132はNPNバイポーラ型トランジスタ110およびPNPバイポーラ型トランジスタ111の、コレクタ、ベースおよびエミッタにつながる電極である。

【0009】

ここで、各層の不純物濃度について説明する。第2導電型の半導体層104の不純物濃度は1016 atms/cm3 台であり、第2導電型拡散層105の不純物濃度は1019 atms/cm3 台であり、第1導電型拡散層107の不純物濃度は1018 atms/cm3 台であり、拡散分離領域118の不純物濃度は1018 atms/cm3 台である。NPN型バイポーラトランジスタ110のコレクタ112、ベース113、エミッタ114の各々の不純物濃度は、それぞれ1017 atms/cm3 台、1018 atms/cm3 台、1019 atms/cm3 台である。PNP型バイポーラトランジスタ111のコレクタ115、ベース116、エミッタ117の不純物濃度は、それぞれ1016 atms/cm3 台、1018 atms/cm3 台、1019 atms/cm3 台である。

【0010】

ここで、光電変換部101に光が入射した場合に、発生した電流がカソード電極108から取り出され、NPNバイポーラ型トランジスタ110およびPNPバイポーラ型トランジスタ111等を組み合わせた回路により信号化処理が施される。

【0011】

光電変換半導体装置の第2の従来例を図18に示す。図18において、光電変換部101は第1の従来例である図17の光電変換半導体装置と同一の構成である。

【0012】

109はカソード電極108から取り出された、光電変換された信号を制御する制御部であり、120はNチャネルMIS型トランジスタ、121はPチャネルMIS型トランジスタである。

【0013】

ここで、NチャネルMIS型トランジスタ120は以下のような構造となっている。122はP型不純物として例えばボロンを用いたP型不純物領域である。123はN型不純物、例えばヒ素を用いてP型不純物領域122内に形成されたソース・ドレインである。124は例えばシリコン酸化膜で形成されたゲート絶縁膜である。125はN型不純物として、例えばリンを含有させた多結晶シリコンを用いてゲート絶縁膜124上に形成されたゲート電極である。

【0014】

また、PチャネルMIS型トランジスタ121は以下のような構造となっている。126はP型不純物、例えばボロンを用いて形成されたソース・ドレインである。124は例えばシリコン酸化膜で形成されたゲート絶縁膜である。125はN型不純物として、例えばリンを含有させた多結晶シリコンを用いて、ゲート絶縁膜124上に形成されたゲート電極である。

【0015】

118は光電変換部101と制御部109とをPN接合を利用して分離する拡散分離領域である。127はNチャネルMIS型トランジスタ120およびPチャネルMIS型トランジスタ121の各素子を、例えばシリコン酸化膜を用いて分離する分離領域である。

【0016】

131は層間絶縁膜である。132はNチャネルMIS型トランジスタ120およびPチャネルMIS型トランジスタ121の、ドレインおよびソースにつながる電極である。

【0017】

ここで、各層の不純物濃度について説明する。NチャネルMIS型トランジスタ120のP型不純物領域122の不純物濃度は1017 atms/cm3 台、ドレイン・ソース123の不純物濃度は1019 atms/cm3 台である。PチャネルMIS型トランジスタ121のドレイン・ソース126の不純物濃度は1019 atms/cm3 台である。

【0018】

ここで、光電変換部101に光が入射した場合に、発生した電流がカソード電極108から取り出され、NチャネルMIS型トランジスタ120およびPチャネルMIS型トランジスタ121等を組み合わせた回路により信号化処理が施される。

【0019】

【発明が解決しようとする課題】

コンパクトディスク等の光ディスクのデータ読み出し装置においては、光ディスクの高速読み出しに対する市場の要求が近年強くなってきている。この市場の要求を満たすために、この光ディスクのデータ読み出し装置の読み取り部に使用され、光信号を電気信号に変換する光電変換装置においては、周波数特性の高周波化の実現が必須となってきた。

【0020】

図17および図18に示した、従来例による光電変換装置によれば、半導体基板102に含有されたP型不純物が真性半導体層103側に、後の製造工程を経ることにより拡散し、半導体基板102と真性半導体層103の接触部分に不純物プロファイルのなだらか部分が形成されてしまい、光等が入射した際に空乏層中で発生するキャリアによる電流の他に、この部分で発生したキャリアが遅れて空乏層へ拡散する電流成分が形成されてしまい、時間分解能が低下するという課題があった。

【0021】

したがって、光電変換装置の特性の高周波化を実現するために、半導体基板102におけるP型不純物の濃度を調整したり、真性半導体層103の厚みの調整、半導体層104の厚みの調整等により、PINダイオードの応答性能を向上させたり、配線抵抗成分の低抵抗化をするという手段が用いられていた。

【0022】

しかし、これらの改善はPINダイオードの高周波特性の改善には効果があるものの、制御部109に形成されたバイポーラ型トランジスタ110,111の特性やMIS型トランジスタ120,121の特性に対しては、バイポーラ型トランジスタ110,111のコレクタと半導体基板102との間のPN接合、またはMIS型トランジスタ120,121のソース・ドレインと半導体基板102との間のPN接合での漏れ電流や耐圧と言った素子分離特性に悪影響を及ぼし、さらに寄生容量の増加、寄生トランジスタの形成等の悪影響を及ぼす。これらの影響により、光電変換部101で変換された電気信号レベルの低下等を招き、制御部(信号化処理部)109での信号処理精度や処理速度と言った性能の劣化や歩留まり低下の原因ともなっていた。

【0023】

したがって、本発明の目的は、トランジスタ性能の向上とPINダイオードの特性向上との両立を図ることができる半導体装置およびその製造方法を提供することである。

【0024】

【課題を解決するための手段】

上記課題を解決するために、本発明では、バイポーラ型トランジスタもしくはMIS型トランジスタの下層に絶縁体層を形成し、パイポーラ型トランジスタもしくはMIS型トランジスタを電気的に半導体基板から分離することにより、これらのトランジスタ性能の向上とPINダイオードの特性向上の両立を図り、これにより、例えば光電変換装置の高性能化を目指したものである。

【0025】

具体的に説明すると、第1の発明の光電変換半導体装置は、第1導電型の半導体基板と、半導体基板上に形成されて不純物濃度が半導体基板より低濃度に調整された真性半導体層と、真性半導体層上に形成されて一部の領域が半導体基板および真性半導体層との積層構造によってフォトダイオードを構成する第2導電型の半導体層と、第2導電型の半導体層における残りの領域に形成されたトランジスタと、トランジスタの形成領域の下層であって、半導体基板と真性半導体層の両方あるいは真性半導体層のみに形成された絶縁体層とを備えている。

【0026】

この構成によれば、トランジスタの下層に絶縁体層を設けたことによって、トランジスタを電気的に半導体基板から分離することができる。その結果、トランジスタの特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、トランジスタの特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0027】

前記トランジスタはバイポーラ型トランジスタであることが好ましい。

【0028】

前記トランジスタはMIS型トランジスタであってもよい。

【0029】

第2の発明の光電変換半導体装置の製造方法は、フォトダイオードとトランジスタとを含む光電変換半導体装置を製造する光電変換半導体装置の製造方法であり、第1導電型の半導体基板上に不純物濃度が半導体基板より低濃度に調整された真性半導体層を積層する工程と、真性半導体層上からフォトダイオード形成領域を避けて半導体基板と真性半導体層の両方、あるいは真性半導体層のみに層状に所定のイオンを注入する工程と、半導体基板を高温熱処理して所定のイオンが注入された領域を絶縁体層に変化させる工程と、真性半導体層上に第2導電型の半導体層を積層して半導体基板、真性半導体層および半導体層の積層構造でフォトダイオードを形成する工程と、半導体層におけるフォトダイオード形成領域以外の領域にトランジスタを形成する工程とを含む。

【0030】

この方法によれば、トランジスタの下層に絶縁体層を設けることによって、トランジスタを電気的に半導体基板から分離することができる。その結果、トランジスタの特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、トランジスタの特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0031】

また、絶縁体層をイオン注入と高温熱処理とにより形成するので、例えばフォトリソグラフィ技術とを組み合わせることにより、イオンを絶縁体層形成したい領域に選択的に注入することができる。また、真性半導体層形成後にイオンの加速エネルギーの調整により意図する深さに注入することができ、高温熱処理による反応で位置精度良く絶縁体層を形成できる。

【0032】

前記トランジスタはバイポーラ型トランジスタであることが好ましい。

【0033】

前記トランジスタはMIS型トランジスタであってもよい。

【0035】

【発明の実施の形態】

以下、図面を参照して、本発明の実施の形態について説明する。

【0036】

最初に、本発明による光電変換半導体装置の実施の形態について説明する。

【0037】

図1は、第1の発明による光電変換半導体装置の実施の形態を示した断面図である。図1において、1は光電変換部である。2は第1導電型(例えば、P型)の半導体基板であり、例えばシリコン中にP型不純物のボロンにより不純物濃度が1×1020 atms/cm3 程度に調整された半導体基板であり、PINダイオードのカソードとしている。3は半導体基板2上に形成された真性半導体層(IntrinsicのIをとってI層)であり、例えば第1導電型で不純物濃度が1×1012 atms/cm3 から1×1013 atms/cm3 程度に調整された、例えばシリコンを用いた真性半導体層である。4は真性半導体層3上に形成された第2導電型(例えば、N型)の半導体層であり、例えばシリコン中にN型不純物のリンにより調整され形成された第2導電型の半導体層である。5はアノード用に表面を低抵抗化する目的で半導体層4に同じ導電型で例えばヒ素を用いて導入された第2導電型拡散層である。

【0038】

上記の半導体基板2、真性半導体層3および半導体層4より、P型層−I層−N型層の連続積層構造を形成し、光電変換用PINダイオードを形成している。6はPINダイオードのアノード電極である。7はカソードからの電位を伝えるための例えばボロンを用いて形成された第1導電型拡散層である。8はPINダイオードのからの信号を取り出すカソード電極である。

【0039】

9はカソード電極8から取り出された、光電変換された信号を制御する制御部であり、10はNPNバイポーラ型トランジスタ、11はPNPバイポーラ型トランジスタである。

【0040】

ここで、12は半導体層4内に例えば不純物としてリンを用いて形成されたNPNバイポーラ型トランジスタ10のコレクタであり、13は例えば不純物としてボロンを用いて形成されたNPNバイポーラ型トランジスタ10のベースであり、14は例えば不純物としてヒ素を用いて形成されたNPNバイポーラ型トランジスタ10のエミッタである。

【0041】

また、15は例えば不純物としてボロンを用いて形成されたPNPバイポーラ型トランジスタ11のコレクタであり、16は例えば不純物としてリンを用いて形成されたPNPトランジスタ11のベースであり、17は例えば不純物としてボロンを用いて形成されたPNPバイポーラ型トランジスタ11のエミッタである。

【0042】

18は、光電変換部1、NPNバイポーラ型トランジスタ10、PNPバイポーラ型トランジスタ11の各素子を、例えばP型不純物としてボロンを用いてPN接合を形成して分離する拡散分離領域である。

【0043】

19はNPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の下層に形成された、例えばシリコン酸化膜からなる絶縁体層である。

【0044】

ここで形成される絶縁体層19は、半導体基板2と真性半導体層3の両方に形成、あるいは真性半導体層3のみに形成されるように調整している。

【0045】

31は例えばシリコン酸化膜を用いた層間絶縁膜である。32は例えばアルミニウムを用いて形成した各電極であり、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11のコレクタ、ベース、エミッタにつながる。

【0046】

ここで、各層の不純物濃度について説明する。第2導電型の半導体層4の不純物濃度は1016 atms/cm3 台であり、第2導電型拡散層5の不純物濃度は1019 atms/cm3 台であり、第1導電型拡散層7の不純物濃度は1018 atms/cm3 台であり、拡散分離領域8の不純物濃度は1018 atms/cm3 台である。NPN型バイポーラトランジスタ10のコレクタ12、ベース13、エミッタ14の各々の不純物濃度は、それぞれ1017 atms/cm3 台、1018 atms/cm3 台、1019 atms/cm3 台である。PNP型バイポーラトランジスタ11のコレクタ15、ベース16、エミッタ17の不純物濃度は、それぞれ1016 atms/cm3 台、1018 atms/cm3 台、1019 atms/cm3 台である。

【0047】

この実施の形態では、例えば、光電変換部1に光が入射した場合に、発生した電流がカソード電極8から取り出され、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11等を組み合わせた回路により信号化処理が施される。

【0048】

この実施の形態の光電変換半導体装置によれば、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の下層に絶縁体層19を設けたことによって、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11を電気的に半導体基板2から分離することができる。その結果、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0049】

図2は、第2の発明による光電変換半導体装置の実施の形態を示した断面図である。図2において、光電変換部1は第1の発明の実施の形態である図1と同一の構成である。

【0050】

2は第1導電型(例えば、P型)の半導体基板であり、例えばシリコン中にP型不純物のボロンにより不純物濃度が1×1020 atms/cm3 程度に調整された半導体基板であり、PINダイオードのカソードとしている。3は半導体基板2上に形成された真性半導体層(IntrinsicのIをとってI層)であり、例えば第1導電型で不純物濃度が1×1012 atms/cm3 から1×1013 atms/cm3 程度に調整された、例えばシリコンを用いた真性半導体層である。4は真性半導体層3上に形成された第2導電型(例えば、N型)の半導体層であり、例えばシリコン中にN型不純物のリンにより調整され形成された半導体層である。5はアノード用に表面を低抵抗化する目的で半導体層4に同じ導電型で例えばヒ素を用いて導入された第2導電型拡散層である。

【0051】

上記の半導体基板2、真性半導体層3および半導体層4より、P型層−I層−N型層の連続積層構造を形成し、光電変換用PINダイオードを形成している。6はPINダイオードのアノード電極である。7はカソードからの電位を伝えるための例えばボロンを用いて形成された第1導電型拡散層である。8はPINダイオードのからの信号を取り出すカソード電極である。

【0052】

9はカソード電極8から取り出された、光電変換された信号を制御する制御部であり、20はNチャネルMIS型トランジスタ、21はPチャネルMIS型トランジスタである。

【0053】

ここで、NチャネルMIS型トランジスタ20は以下のような構造となっている。22はP型不純物として例えばボロンを用いたP型不純物領域である。23はN型不純物、例えばヒ素を用いてP型不純物領域22内に形成されたソース・ドレインである。24は例えばシリコン酸化膜で形成されたゲート絶縁膜である。25はN型不純物として、例えばリンを含有させた多結晶シリコンを用いてゲート絶縁膜24上に形成されたゲート電極である。

【0054】

また、PチャネルMIS型トランジスタ21は以下のような構造となっている。26はP型不純物、例えばボロンを用いて形成されたソース・ドレインである。24は例えばシリコン酸化膜で形成されたゲート絶縁膜である。25はN型不純物として、例えばリンを含有させた多結晶シリコンを用いて、ゲート絶縁膜24上に形成されたゲート電極である。

【0055】

18は光電変換部1と制御部9とをPN接合を利用して分離する拡散分離領域である。27はNチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の各素子を、例えばシリコン酸化膜を用いて分離する分離領域である。

【0056】

19はNチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の下層に形成された、例えばシリコン酸化膜からなる絶縁体層である。

【0057】

ここで形成される絶縁体層19は半導体基板2と真性半導体層3の両方に形成、あるいは真性半導体層3のみに形成されるように調整している。

【0058】

31は、例えばシリコン酸化膜を用いた層間絶縁膜であり、32は、例えばアルミニウムを用いて形成した各電極であり、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21のドレインおよびソースにつながる。

【0059】

ここで、各層の不純物濃度について説明する。NチャネルMIS型トランジスタ20のP型不純物領域22の不純物濃度は1017 atms/cm3 台、ドレイン・ソース23の不純物濃度は1019 atms/cm3 台である。PチャネルMIS型トランジスタ21のドレイン・ソース26の不純物濃度は1019 atms/cm3 台である。

【0060】

この実施の形態では、例えば、光電変換部1に光が入射した場合に、発生した電流がカソード電極8から取り出され、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21等を組み合わせた回路により信号化処理が施される。

【0061】

この実施の形態の光電変換半導体装置によれば、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の下層に絶縁体層19を設けたことによって、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21を電気的に半導体基板2から分離することができる。その結果、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0062】

次に、本発明による光電変換半導体装置の製造方法の実施の形態について、工程順断面図を用いて説明する。

【0063】

図3から図9までの各図は、第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図であり、第1の発明の光電変換半導体装置を製造する方法を示す。

【0064】

まず、図3に示すように、半導体基板2は、第1導電型、例えばシリコンを用いP型不純物として例えばボロンを用いて不純物濃度が1×1020 atms/cm3 程度に調整されている。そして、半導体基板2上に真性半導体層3を積層形成した。真性半導体層3は、例えば第1導電型で不純物濃度が1×1012 atms/cm3 から1×1013 atms/cm3 程度に調整された例えばシリコンからなる。

【0065】

ここで、符号1で示した領域は後に光電変換部となる部分であり、符号10で示した領域は後にNPNバイポーラ型トランジスタとなる部分であり、符号11で示した領域は後にPNPバイポーラ型トランジスタとなる部分である。

【0066】

つぎに、図4に示すように、上記真性半導体層3上にフォトレジスト等を用いて光電変換部1となる領域以外(バイポーラ型トランジスタ10,11が形成される領域)の全部あるいは一部の領域にイオン注入されるように開口されたマスクパターン28を形成し、このマスクパターン28を用いて矢印29で示すように、選択的にイオン注入を行うことにより例えば酸素イオン30をイオン注入した。

【0067】

なお、全部あるいは一部の領域というのは、複数個あるトランジスタのすべてについて下層に絶縁体層を形成するか、あるいは一部のトランジスタの下層にのみ絶縁体層を形成するという意味である。トランジスタの高性能化を目指し、浅く絶縁層を形成した場合、バイポーラ型トランジスタのコレクタ拡散層やMIS型トランジスタのドレイン・ソース拡散層が浅くなり、抵抗が上昇し、電流が減少することが考えられる。したがって、電流量優先で設計された回路素子に対しては、絶縁体層を下層に形成しない場合がある。

【0068】

このとき、イオン注入される酸素イオン30は、半導体基板2と真性半導体層3の両方、あるいは真性半導体層3のみにイオン注入されるようにイオン注入時の加速エネルギーを調整している。

【0069】

つぎに、図5に示すように、図4でイオン注入のマスクに用いたマスクパターン28を酸素プラズマ処理等により選択的に除去し、その後例えば、アルゴンガスまたは窒素ガス等の不活性ガスを用いた1000℃程度の高温熱処理により、酸素イオン30を半導体基板2として用いた例えばシリコンとを反応させ、また真性半導体層3として用いた例えばシリコンとを反応させ、それらをシリコン酸化膜化させ、絶縁体層19とした。

【0070】

ここで、不活性ガスを用いて高温熱処理を行うのは、図4でイオン注入を行った時に上記真性半導体層3の表面に形成されたダメージ層をアニーリングするためであり、真性半導体層3上に次工程で例えば単結晶シリコンを低欠陥密度で形成しようとする構成のためには不可欠である。

【0071】

つぎに、図6に示すように、上記真性半導体層3上に例えばシランガスを用いたエピタキシャル法により、第2導電型のN型として例えばリンを不純物として単結晶シリコンからなる第2導電型の半導体層4を形成した。

【0072】

つぎに、図7に示すように、上記第2導電型の半導体層4内に、PN接合型素子分離層として第2導電型とは異なる導電型で例えばボロンを用いたP型不純物で拡散分離領域18を形成した。この拡散分離領域18は、光電変換部1とNPNバイポーラ型トランジスタ10とPNPバイポーラ型トランジスタ11とを分離するように形成される。

【0073】

また、PNPバイポーラ型トランジスタ11のコレクタ15とするために、P型不純物領域(15)を例えばボロンを不純物として用い形成し、光電変換部1のカソードとするために第1導電型不純物を用い第1導電型拡散層7を形成した。NPNバイポーラ型トランジスタ10のコレクタ12としては、半導体層4がそのまま使用される。

【0074】

つぎに、図8に示すように、NPNバイポーラ型トランジスタ10のベース13とエミッタ14、PNPバイポーラ型トランジスタ11のベース16とエミッタ17、光電変換部1のアノードとするための第2導電形拡散層5、カソードとすべく第1導電形拡散層7の各層を形成した。

【0075】

つぎに、図9に示すように、NPNバイポーラ型トランジスタ10、PNPバイポーラ型トランジスタ11および光電変換部1上に、例えばCVD法によるシリコン酸化膜を用いて層間絶縁膜31を形成し、上記層間絶縁膜31にフォトエッチング技術等により接続孔33を形成し、例えばアルミニウムによる電極32、アノード電極6およびカソード電極8を作成した。

【0076】

この実施の形態の光電変換半導体装置の製造方法によれば、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の下層に絶縁体層19を設けたことによって、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11を電気的に半導体基板2から分離することができる。その結果、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、NPNバイポーラ型トランジスタ10およびPNPバイポーラ型トランジスタ11の特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0077】

また、絶縁体層をイオン注入と高温熱処理とにより形成するので、例えばフォトリソグラフィ技術とを組み合わせることにより、イオンを絶縁体層形成したい領域に選択的に注入することができる。また、真性半導体層形成後にイオンの加速エネルギーの調整により意図する深さに注入することができ、高温熱処理による反応で位置精度良く絶縁体層を形成できる。

【0078】

図10から図16までの各図は、第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図であり、第2の発明の光電変換半導体装置を製造する方法を示す。

【0079】

まず、図10に示すように、半導体基板2は、第1導電型、例えばシリコンを用いP型不純物として例えばボロンを用いて不純物濃度が1×1020 atms/cm3 程度に調整されている。そして、半導体基板2上に真性半導体層3を積層形成した。真性半導体層3は、例えば第1導電型で不純物濃度が1×1012 atms/cm3 から1×1013 atms/cm3 程度に調整された例えばシリコンからなる。

【0080】

ここで、符号1で示した領域は後に光電変換部となる部分であり、符号20で示した領域はNチャネルMOS型トランジスタとなる部分であり、符号21で示した領域はPチャネルMOS型トランジスタとなる部分である。

【0081】

つぎに、図11に示すように、上記真性半導体層3上にフォトレジスト等を用いて光電変換部1となる領域以外(MIS型トランジスタ20,21が形成される領域)の全部あるいは一部の領域にイオン注入されるように開口されたマスクパターン28を形成し、このマスクパターン28を用いて矢印29で示すように、選択的にイオン注入を行うことにより例えば酸素イオン30をイオン注入した。

【0082】

このとき、イオン注入される酸素イオン30は、半導体基板2と真性半導体層3の両方、あるいは真性半導体層3のみにイオン注入されるようにイオン注入時の加速エネルギーを調整している。

【0083】

つぎに、図12に示すように、図11でイオン注入のマスクに使用したマスクパターン28を酸素プラズマ処理等により選択的に除去し、その後例えばアルゴンガスまたは窒素ガス等の不活性ガスを用いた1000℃程度の高温熱処理により、酸素イオン30を半導体基板2として用いた例えばシリコンとを反応させ、また真性半導体層3として用いた例えばシリコンとを反応させ、それらをシリコン酸化膜化させ、絶縁体層19とした。

【0084】

ここで、不活性ガスを用いて高温熱処理を行うのは、図11でイオン注入を行った時に上記真性半導体層3の表面に形成されたダメージ層をアニーリングするためであり、真性半導体層3上に次工程で例えば単結晶シリコンを低欠陥密度で形成しようとする構成のためには不可欠である。

【0085】

つぎに、図13に示すように、上記真性半導体層3上に例えばシランガスを用いたエピタキシャル法により、第2導電型のN型として例えばリンを不純物として単結晶シリコンからなる第2導電型の半導体層4を形成した。

【0086】

つぎに、図14に示すように、上記第2導電型の半導体層4内にPN接合を利用した拡散分離領域18を、第2導電型とは異なる導電型で例えばボロンを用いたP型不純物で形成した。

【0087】

また、NチャネルMIS型トランジスタ20の形成領域としてP型層22を例えばボロンを不純物として用い形成した。PチャネルMIS型トランジスタ21の形成領域としては、半導体層4がそのまま使用される。27は上記NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の各素子を例えばシリコン酸化膜を用いて分離する分離領域である。

【0088】

つぎに、図15に示すように、PチャネルMIS型トランジスタ21については、P型不純物、例えばボロンを用いて半導体層4内にソース・ドレイン26を形成し、例えばシリコン酸化膜でゲート絶縁膜24を形成し、N型不純物として、例えばリンを含有させた多結晶シリコンを用いて、ゲート絶縁膜24上に形成されたゲート電極25を形成する。

【0089】

また、NチャネルMIS型トランジスタ20について、N型不純物、例えばヒ素を用いてP型層22内にソース・ドレイン23を形成し、例えばシリコン酸化膜でゲート絶縁膜24を形成し、N型不純物として、例えばリンを含有させた多結晶シリコンを用いて、ゲート絶縁膜24上に形成されたゲート電極25を形成する。

【0090】

つぎに、図16に示すように、NチャネルMIS型トランジスタ20、PチャネルMIS型トランジスタ21および光電変換部1上に、例えばCVD法によるシリコン酸化膜を用いて層間絶縁膜31を形成し、上記層間絶縁膜31にフォトエッチング技術等により接続孔33を形成、例えばアルミニウムによる電極32、アノード電極6およびカソード電極8を作成した。

【0091】

この実施の形態の光電変換半導体装置の製造方法によれば、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の下層に絶縁体層19を設けたことによって、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21を電気的に半導体基板2から分離することができる。その結果、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の特性に影響を与えることなく、PINダイオードの特性向上を図ることができる。逆にPINダイオードの特性に影響を与えることなく、NチャネルMIS型トランジスタ20およびPチャネルMIS型トランジスタ21の特性向上を図ることができる。したがって、トランジスタ性能の向上とPINダイオードの特性向上の両立を図ることができる。

【0092】

また、絶縁体層をイオン注入と高温熱処理とにより形成するので、例えばフォトリソグラフィ技術とを組み合わせることにより、イオンを絶縁体層形成したい領域に選択的に注入することができる。また、真性半導体層形成後にイオンの加速エネルギーの調整により意図する深さに注入することができ、高温熱処理による反応で位置精度良く絶縁体層を形成できる。

【0093】

なお、第1の発明による実施の形態では、バイポーラ型トランジスタを用いて説明し、第2の発明による実施の形態では、MIS型トランジスタを用いて説明したが、バイポーラ型トランジスタとMIS型トランジスタを組み合わせた構成の光電変換半導体装置についても本発明が有効であることは言うまでもない。

【0094】

また、異なる導電型や異なる不純物濃度、異なる材質を組み合わせ積層構造とした基板においても、最上層部が本発明により説明された半導体基板と同様であれば、本発明の構成を用いることにより同様の効果を得ることが可能である。

【0095】

真性半導体層は、上記の実施の形態では、第1導電型であると説明したが、第2導電型であっても、同様の作用効果が得られる。

【0096】

【発明の効果】

本発明による光電変換半導体装置およびその製造方法によれば、半導体基板の不純物濃度や、真性半導体層の厚さ等の例えば光電変換用に形成されたPINダイオードの形成条件に影響を受けることなく、バイポーラ型トランジスタやMIS型トランジスタを形成することが可能となり、これらトランジスタの特性調整が容易となる。これにより、PINダイオードの高性能化が実現でき、例えば光電変換装置における周波数特性の高周波化が容易となり、光電変換装置自体の歩留まり改善も期待できる。

【図面の簡単な説明】

【図1】第1の発明による光電変換半導体装置の実施の形態を示す断面図である。

【図2】第2の発明による光電変換半導体装置の実施の形態を示す断面図である。

【図3】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図4】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図5】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図6】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図7】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図8】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図9】第3の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図10】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図11】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図12】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図13】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図14】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図15】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図16】第4の発明による光電変換半導体装置の製造方法の実施の形態を示す工程順断面図である。

【図17】第1の従来例の光電変換半導体装置の断面図である。

【図18】第2の従来例の光電変換半導体装置の断面図である。

【符号の説明】

1 光電変換部

2 半導体基板

3 真性半導体層

4 半導体層

5 第2導電型拡散層

6 アノード電極

7 第1導電型拡散層

8 カソード電極

9 制御部

10 NPNバイポーラ型トランジスタ

11 PNPバイポーラ型トランジスタ

12 コレクタ

13 ベース

14 エミッタ

15 コレクタ

16 ベース

17 エミッタ

18 拡散分離領域

19 絶縁体層

20 NチャネルMIS型トランジスタ

21 PチャネルMIS型トランジスタ

22 P型不純物領域

23 ソース・ドレイン

24 ゲート絶縁膜

25 ゲート電極

26 ソース・ドレイン

27 分離領域

28 マスクパターン

30 酸素イオン

31 層間絶縁膜

32 電極

33 接続孔

101 光電変換部

102 半導体基板

103 真性半導体層

104 半導体層

105 第2導電型拡散層

106 アノード電極

107 第1導電型拡散層

108 カソード電極

109 制御部

110 NPNバイポーラ型トランジスタ

111 PNPバイポーラ型トランジスタ

112 コレクタ

113 ベース

114 エミッタ

115 コレクタ

116 ベース

117 エミッタ

118 拡散分離領域

120 NチャネルMIS型トランジスタ

121 PチャネルMIS型トランジスタ

122 P型不純物領域

123 ソース・ドレイン

124 ゲート絶縁膜

125 ゲート電極

126 ソース・ドレイン

127 分離領域

131 層間絶縁膜

132 電極

Claims (15)

- 第1導電型の半導体基板と、前記半導体基板上に形成されて不純物濃度が前記半導体基板より低濃度に調整された真性半導体層と、前記真性半導体層上に形成されて一部の領域が前記半導体基板および前記真性半導体層との積層構造によってフォトダイオードを構成する第2導電型の半導体層と、前記第2導電型の半導体層における残りの領域に形成されたトランジスタと、前記トランジスタの形成領域の下層であって、前記半導体基板と前記真性半導体層の両方あるいは前記真性半導体層のみに形成された絶縁体層とを備えた光電変換半導体装置。

- 前記半導体基板および前記真性半導体層の材質がシリコンからなる請求項1記載の光電変換半導体装置。

- 前記絶縁体層が酸化シリコンで形成されている請求項2記載の光電変換半導体装置。

- 前記真性半導体層の不純物濃度が1×10 12 atms/cm 3 から1×10 13 atms/cm 3 である請求項1記載の光電変換半導体装置。

- 前記トランジスタはバイポーラ型トランジスタであることを特徴とする請求項1ないし4のいずれかに記載の光電変換半導体装置。

- 前記トランジスタはMIS型トランジスタであることを特徴とする請求項1ないし4のいずれかに記載の光電変換半導体装置。

- フォトダイオードとトランジスタとを含む光電変換半導体装置の製造方法であって、

第1導電型の半導体基板上に不純物濃度が前記半導体基板より低濃度に調整された真性半導体層を積層する工程と、

前記真性半導体層上からフォトダイオード形成領域を避けて前記半導体基板と前記真性半導体層の両方、あるいは前記真性半導体層のみに層状に所定のイオンを注入する工程と、

前記半導体基板を高温熱処理して前記所定のイオンが注入された領域を絶縁体層に変化させる工程と、

前記真性半導体層上に第2導電型の半導体層を積層して前記半導体基板、前記真性半導体層および前記半導体層の積層構造で前記フォトダイオードを形成する工程と、

前記半導体層における前記フォトダイオード形成領域以外の領域に前記トランジスタを形成する工程とを含む光電変換半導体装置の製造方法。 - 前記所定のイオンは高温熱処理によって前記真性半導体層または前記半導体基板の材料と反応することにより前記真性半導体層または前記半導体基板を絶縁体に変化させる種類が選択されている請求項7記載の光電変換半導体装置の製造方法。

- 前記半導体基板の高温熱処理は不活性ガス雰囲気中で行う請求項7記載の光電変換半導体装置の製造方法。

- 不活性ガスはアルゴンまたは窒素からなる請求項9記載の光電変換半導体装置の製造方法。

- 前記半導体基板および前記真性半導体層の材質がシリコンからなる請求項7記載の光電変換半導体装置の製造方法。

- 前記絶縁体層が酸化シリコンで形成されている請求項11記載の光電変換半導体装置の製造方法。

- 前記真性半導体層の不純物濃度が1×10 12 atms/cm 3 から1×10 13 atms/cm 3 である請求項7記載の光電変換半導体装置の製造方法。

- 前記トランジスタはバイポーラ型トランジスタであることを特徴とする請求項7ないし13のいずれかに記載の光電変換半導体装置の製造方法。

- 前記トランジスタはMIS型トランジスタであることを特徴とする請求項7ないし13のいずれかに記載の光電変換半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001125746A JP3768829B2 (ja) | 2001-04-24 | 2001-04-24 | 光電変換半導体装置およびその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001125746A JP3768829B2 (ja) | 2001-04-24 | 2001-04-24 | 光電変換半導体装置およびその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002324898A JP2002324898A (ja) | 2002-11-08 |

| JP2002324898A5 JP2002324898A5 (ja) | 2005-09-22 |

| JP3768829B2 true JP3768829B2 (ja) | 2006-04-19 |

Family

ID=18974909

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2001125746A Expired - Fee Related JP3768829B2 (ja) | 2001-04-24 | 2001-04-24 | 光電変換半導体装置およびその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3768829B2 (ja) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100861317B1 (ko) | 2007-01-15 | 2008-10-01 | 이진민 | 방사성동위원소 전지 및 그 제조방법 |

| US8691404B2 (en) * | 2009-03-12 | 2014-04-08 | The Curators Of The University Of Missouri | High energy-density radioisotope micro power sources |

| JP2011171764A (ja) * | 2011-05-13 | 2011-09-01 | Renesas Electronics Corp | 固体撮像装置 |

-

2001

- 2001-04-24 JP JP2001125746A patent/JP3768829B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2002324898A (ja) | 2002-11-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6700144B2 (en) | Semiconductor device and method for manufacturing the same | |

| JP2557750B2 (ja) | 光半導体装置 | |

| JPH04226066A (ja) | Bicmos装置及びその製造方法 | |

| JPH04226064A (ja) | 半導体装置用の相互接続体及びその製造方法 | |

| JPH01155653A (ja) | 高電圧併合バイポーラ/cmos集積回路 | |

| JPH0669431A (ja) | Soi基板上にバイポーラトランジスタとcmosトランジスタを製造する方法及びそれらのトランジスタ | |

| JPH1145988A (ja) | BiCMOS内蔵受光半導体装置 | |

| JP3122118B2 (ja) | 半導体装置 | |

| JP2003234423A (ja) | 半導体装置及びその製造方法 | |

| JPH04363046A (ja) | 半導体装置の製造方法 | |

| JP3768829B2 (ja) | 光電変換半導体装置およびその製造方法 | |

| JP3975515B2 (ja) | 受光素子を有する半導体装置とその製造方法 | |

| JP3208307B2 (ja) | 光半導体装置 | |

| US20010055845A1 (en) | Method of production of semiconductor device | |

| JPH11354535A (ja) | 半導体装置およびその製造方法 | |

| JPH09275199A (ja) | 半導体装置及びその製造方法 | |

| JPH10233525A (ja) | アバランシェフォトダイオード | |

| JPH04151874A (ja) | 半導体装置 | |

| JP4660004B2 (ja) | Mos半導体装置の製造方法 | |

| JP4534267B2 (ja) | 半導体装置の製造方法 | |

| JPS61127147A (ja) | 半導体装置 | |

| JPH0897223A (ja) | バイポーラトランジスタ及びその製造方法 | |

| JP2002083877A (ja) | 半導体集積回路装置およびその製造方法 | |

| JPH0387059A (ja) | 半導体集積回路及びその製造方法 | |

| JPH0918050A (ja) | 光半導体装置とその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040615 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050407 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050805 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050816 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051014 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20060131 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20060202 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100210 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100210 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110210 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |