JP3754841B2 - 光起電力素子およびその製造方法 - Google Patents

光起電力素子およびその製造方法 Download PDFInfo

- Publication number

- JP3754841B2 JP3754841B2 JP15704099A JP15704099A JP3754841B2 JP 3754841 B2 JP3754841 B2 JP 3754841B2 JP 15704099 A JP15704099 A JP 15704099A JP 15704099 A JP15704099 A JP 15704099A JP 3754841 B2 JP3754841 B2 JP 3754841B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor

- layers

- film photovoltaic

- bypass diode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F71/00—Manufacture or treatment of devices covered by this subclass

- H10F71/10—Manufacture or treatment of devices covered by this subclass the devices comprising amorphous semiconductor material

- H10F71/107—Continuous treatment of the devices, e.g. roll-to roll processes or multi-chamber deposition

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F19/00—Integrated devices, or assemblies of multiple devices, comprising at least one photovoltaic cell covered by group H10F10/00, e.g. photovoltaic modules

- H10F19/30—Integrated devices, or assemblies of multiple devices, comprising at least one photovoltaic cell covered by group H10F10/00, e.g. photovoltaic modules comprising thin-film photovoltaic cells

- H10F19/31—Integrated devices, or assemblies of multiple devices, comprising at least one photovoltaic cell covered by group H10F10/00, e.g. photovoltaic modules comprising thin-film photovoltaic cells having multiple laterally adjacent thin-film photovoltaic cells deposited on the same substrate

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F19/00—Integrated devices, or assemblies of multiple devices, comprising at least one photovoltaic cell covered by group H10F10/00, e.g. photovoltaic modules

- H10F19/50—Integrated devices comprising at least one photovoltaic cell and other types of semiconductor or solid-state components

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F77/00—Constructional details of devices covered by this subclass

- H10F77/10—Semiconductor bodies

- H10F77/16—Material structures, e.g. crystalline structures, film structures or crystal plane orientations

- H10F77/169—Thin semiconductor films on metallic or insulating substrates

- H10F77/1692—Thin semiconductor films on metallic or insulating substrates the films including only Group IV materials

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E10/00—Energy generation through renewable energy sources

- Y02E10/50—Photovoltaic [PV] energy

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S136/00—Batteries: thermoelectric and photoelectric

- Y10S136/291—Applications

- Y10S136/293—Circuits

Landscapes

- Photovoltaic Devices (AREA)

Description

【発明の属する技術分野】

本発明は、特性が優れ、信頼性の高い光起電力素子およびその製造方法に関する。より詳しくは、集電電極の下部にバイパスダイオードを形成することにより変換効率のロスの少ない良好な特性を有する光起電力素子およびその製造方法に関する。

【0002】

【従来の技術】

アモルファス半導体を用いた薄膜太陽電池は、単結晶や多結晶太陽電池に比較して大面積の太陽電池が作製できることや、半導体の膜厚が薄くて済むこと、任意の基板材料に堆積できることなどの長所があり、有望視されている。

【0003】

アモルファスシリコン太陽電池は例えば、基板上に薄膜のアモルファスシリコンからなるp層、i層、n層を積層して構成される。また、変換効率を向上させるために前記pin接合を2以上の直列に積層するいわゆるダブルセル、トリプルセルも検討されている。前記半導体の光入射側および裏面側には上部電極および下部電極の一対の電極が設けられる。アモルファスシリコン太陽電池においては一般的に半導体自体のシート抵抗が高いため、半導体全面にわたる透明な上部電極を必要とし、通常は、SnO2 やITOのような透明導電膜が用いられる。該透明導電膜は反射防止膜としても機能する。前記上部電極の上に更に光の入射を妨げないように櫛状に形成された集電用のグリッド電極が設けられる。更にグリッド電極の電流を集合させるバスバーが設けられる。

【0004】

ところで、通常、太陽電池を電力の供給源としてみた場合、1枚の太陽電池セル(光起電力素子)だけでは出力電圧が不足する。このため、複数個の太陽電池セルを直列もしくは並列に接続して使用する必要がある。このように複数個のセル(素子)を直列接続して動作させる場合における最大の難点は、建物の影や降雪などにより、セルの一部が太陽光から遮られて発電しなくなった場合、直列化されているその他のセルが発電しているにもかかわらず、直列化モジュールとしては発電が行なわれなくなること、および、正常に発電している他の素子からの総発生電圧が逆方向電圧という形で直接印加されることである。そしてこのような逆方向電圧が素子の耐圧を越える値になった場合には、素子の破壊が起きる可能性がある。そこで、このような発電の問題や素子の破壊を避けるために、直列接続した各素子ごとに、素子と並列で素子の半導体接合とは逆の方向にダイオードを結線する必要がある。このようなダイオードは一般的にバイパスダイオードと呼ばれる。

【0005】

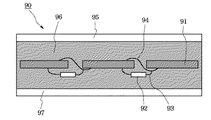

バイパスダイオードを太陽電池に応用した例としては、例えば特開平5−152596号公報で開示されたものがあり、この例はモールドパッケージされたダイオードを太陽電池セルの各々に並列に接続するものである。図9はこのようなバイパスダイオードを使用した太陽電池モジュールの一例を示す概略図である。図中、90はバイパスダイオードが接続された太陽電池モジュール、91は太陽電池セル、92はバイパスダイオード、93は配線、94は太陽電池セル91を直列化するための配線、95はガラス、96は封止用の樹脂、97は裏面プラスチック材料である。ダイオード92の厚みは、通常のアキシャルダイオードであれば約3mmφ程度であるため、封止用樹脂96も厚くする必要がある。

【0006】

このように独立した部品としてのダイオードを太陽電池に付けた場合、ダイオード分の厚みが厚くなることや、配線のために製造工程が複雑になることが考えられるが、またその他の従来技術として太陽電池を構成する半導体にバイパスダイオードを作り込む方法が提案されている。このような提案の例としては特開平4−42974号公報のものが挙げられるが、それは、同一基板上に太陽電池として機能するpn接合とバイパスダイオードとして機能するpn接合とをそれらが並列となるように作り込むものである。

【0007】

【発明が解決しようとする課題】

しかしながら、この従来のバイパスダイオード付き光起電力素子は、▲1▼上述の基板上に成膜されたアモルファス半導体を用いた光起電力素子において、同一基板上にバイパスダイオードを形成するための方法が不明である。▲2▼マスクを必要とする構成および製造方法であるが、そのため製造方法が複雑であり、大きさの自由度が無い。また、▲3▼バイパスダイオード部分が光起電力素子の有効面積のロスになる。言い換えればバイパスダイオードの分、太陽電池の面積を大きくしなければならない。

【0008】

本発明の目的は、上記従来技術の問題点に鑑み、複雑なプロセスを用いずに、成膜により形成する半導体を用いた光起電力素子部分とバイパスダイオード部分を同一基板上に堆積して、バイパスダイオード部分が光起電力素子の有効面積のロスとならず、さらには大きさの自由度が高い、光起電力素子およびその製造方法を提供することにある。

【0009】

【課題を解決するための手段】

この目的を達成するため本発明の薄膜光起電力素子は、薄膜半導体からなる第1の半導体接合層である薄膜光起電力層と、前記薄膜光起電力層の光入射側に間隔を開けて櫛状に設けられた集電電極とを備えた薄膜光起電力素子において、前記薄膜光起電力素子は、薄膜半導体からなる第2の半導体接合層であるバイパスダイオード層を有し、前記バイパスダイオード層は前記集電電極の各下部に存在し且つ前記薄膜光起電力層と並列に接続されるように設けられていて、前記第1の半導体接合層と前記第2の半導体接合層は同一面上に存在し、前記薄膜光起電力層とバイパスダイオード層は平行かつほぼ等しい長さの帯状であり、前記第1の半導体接合層と前記第2の半導体接合層における半導体接合の順方向は互いに逆向きであって、前記薄膜光起電力層および前記バイパスダイオード層は、光入射側においていずれも前記集電電極に接合していることを特徴とする。

【0010】

また、本発明の薄膜光起電力素子の製造方法は、導電性のまたは導電膜を形成した基板上に、薄膜半導体からなる第1の半導体接合層である薄膜光起電力層を所定の間隔を置いて複数箇所に形成する工程と、前記薄膜光起電力層が形成される各個所の間の前記基板上に、順方向が前記第1の半導体接合層とは逆向きであって薄膜半導体からなる第2の半導体接合層であるバイパスダイオード層を、前記第1の半導体接合層と前記第2の半導体接合層が同一面に設けられるように形成する工程と、前記各バイパスダイオード層の上に、前記薄膜光起電力層および前記各バイパスダイオード層に接合するように櫛状の集電電極を形成する工程とを具備することを特徴とする。

【0011】

本発明の薄膜光起電力素子は、バイパスダイオード層を集電電極の下に形成するようにしたため、たとえば基板上に堆積されたpinまたはpn半導体接合を有する薄膜光起電力層とバイパスダイオード層とが同一基板上に成膜によって容易に形成される。したがって素子の表面が平坦化されるとともに、従来は別個の部品であったバイパスダイオードを配線するという工程が省略される。また、製造工程が簡便となり、信頼性や歩留りも良好である。また、バイパスダイオード層は薄膜光起電力層の有効面積のロスとならない。

【0012】

【発明の実施の形態】

本実施形態においては、光起電力素子を構成する半導体材料は結晶系であっても非結晶系であっても良いが、とりわけ基板上に薄膜の半導体が形成されることが好ましい。前記薄膜の半導体は通常の真空成膜プロセスで形成されるが、液相法を用いたプロセスであっても同様な効果が得られる。また該成膜プロセス中に光起電力層とバイパスダイオード層とを同時に形成することも可能であるが、両者を異なる成膜装置を用いて別個に形成してもよい。また基板が長尺であればロールツーロールの成膜方法が可能であり、複数の成膜チャンバ中を基板が搬送されるに従い、半導体層を積層していく方法も生産性向上という点で好ましい。また、枚葉式であっても同様に基板を搬送しながら半導体層を積層する方法もあるが、この方法も好ましい成膜方法である。

【0013】

本実施形態において第1および第2の半導体接合層における各半導体接合層の順方向は互いに逆向きである。すなわち、第2の半導体接合層であるバイパスダイオード層は、第1の半導体接合層である光起電力層とは反対向きのpn接合またはpin接合を構成し、かつ光起電力層と並列となるように形成する。また各層は面一となるように形成される。このとき、基板上に成膜される半導体の特性を変えるためにマスクを用いることができる。具体的には、プラズマCVDによる真空プロセスでアモルファス半導体を形成する場合、真空チャンバの一部、例えば基板の巾方向の集電電極が形成される部分のみに基板を覆うような板を配置することにより、その領域には成膜が起こらないようにすることができる。

【0014】

また本実施形態の光起電力素子は、同一基板上に光起電力層とバイパスダイオード層とを形成することによって作成されるが、バイパスダイオード層は光起電力層に並列に接合される必要がある。そして光起電力層と面一に接合されることが好ましい。また、各層の半導体接合の方向は逆向きであることが必要である。また図1は本実施形態に係る光起電力素子とバイパスダイオードが接続された等価回路を示したものである。図中、11は光起電力層のダイオード成分、12は光起電力層の直流電源成分、13はバイパスダイオード層である。本実施形態において、このような構成は、光起電力層の一方の極とバイパスダイオード層の一方の極とを同一基板上に形成し、他方の極同士を金属電極で接合することで得ることができる。より具体的には、光起電力層およびバイパスダイオード層は、光入射側において、いずれも前記金属電極である集電電極に接合している。

【0015】

この構成を模式的に表わした図が図2である。

図2は本実施形態に係る光起電力装置の半導体層の構成の1例を示す断面模式図である。図2に示すように基板22の上には半導体層21が設けられておりその上に線状の集電電極25が間隔をあけて設けられている。この集電電極25側が受光面側である。半導体層21は、バイパスダイオード層23と光起電力層24とを有する。バイパスダイオード層23と光起電力層24とは、基板22上で交互に隣接して設けられている。また集電電極25は、バイパスダイオード層23とも接続されており、且つ端部にて光起電力層24とも接続している。集電電極25は、バイパスダイオード層23の直上に設けられ、光起電力層24に入光する光をさえぎらないように設けられている。バイパスダイオード層23は、受光面側から基板22側に向って特性の異なる複数の半導体層231,232から構成されている。本図では一例としてp層n層からなる2層構成を示す。光起電力層24もバイパスダイオード層23と同様に特性の異なる複数の半導体層241,242とから構成されており、光起電力層24も1例としてp層n層から構成されている。また半導体層231と241とは半導体特性の異なる層であり、言い換えれば、一方の半導体層がp層の場合、他方の半導体層はn層である。また半導体層232と242も同様に互いに半導体特性の異なる層である。

【0016】

光起電力層とバイパスダイオード層は横方向に隣接して同一基板上に成膜されるが、ロールツーロール法または枚葉式いずれの場合であっても、前記光起電力層とバイパスダイオード層は、平行にかつほぼ等しい長さの帯状に形成される。このように、帯状で平行に成膜し、双方の少なくとも長尺方向の辺の長さをほぼ等しくすることにより、大きな光起電力素子を帯の長尺方向に沿って分割して、帯状の光起電力層と帯状のバイパスダイオード層を所望の数含むような任意の幅の小さな光起電力素子を作成することができる。

【0017】

本実施形態に係る光起電力素子は図2に示す構成以外に第1の半導体接合層を構成する半導体層のうちの少なくとも1層および第2の半導体接合層を構成する半導体層のうちの少なくとも1層を同一材料で同時に形成されるものでもよい。たとえば、第1および第2の半導体接合層はいずれもイントリンジック層を有するpin層である場合、それらのイントリンジック層は両半導体接合層に渡って連続しているものであってもよい。この場合は、第1および第2の半導体接合層は互いにpin接合の積層の順番は異なるが、イントリンジック層(i層)のみは共通に設けられる構成でよい。このような構成は、pin層で構成される第1および第2の各半導体接合層を形成する際、両接合層のi層を、同一材料で同時に形成させたものでもよい。またi層を平坦に形成させ、そして両接合層のうちi層の上に形成される層を面一にすることもできる。

【0018】

あるいは光起電力層である第1の半導体接合層はpinまたはpn接合した半導体層を3つ重ねたトリプルセル構成であり、バイパスダイオード層である第2の半導体接合層はpinまたはpn接合した半導体層を1つのみ有するシングルセル構成であってもよい。この場合、製造方法が簡略化される。たとえば、第1の半導体接合層としてpin接合が3つ積層される場合は、ボトムのp層、ミドルのi層、トップのn層を形成するときにバイパスダイオード層を形成すればよい。つまり、第1の半導体接合層を構成する9つの半導体層のうちの3、5および7層目を、第2の半導体接合層を構成する3つの半導体層のうちの1、2および3層目をそれぞれ同一材料で同時に形成する。つまり第1の半導体接合層の第3層目が第2の半導体層の第1層目と同一材料で同時に形成され、そして第1の半導体接合層の第5層目が第2の半導体層の第2層目と同一材料で同時に形成され、また、第1の半導体接合層の第1層目が第2の半導体層の第3層目と同一材料で同時に形成されている。

【0019】

(第1の半導体接合層)

第1の半導体接合層を構成する半導体層としては、アモルファスシリコン、微結晶シリコン、薄膜多結晶シリコン等の薄膜半導体が挙げられる。pin型のアモルファスシリコン太陽電池に本発明が適される場合、i層を構成する半導体材料としては、a−Si:H、a−Si:F、a−Si:H:F、a−SiGe:H、a−SiGe:F、a−SiGe:H:F、a−SiC:H、a−SiC:F、a−SiC:H:F等のいわゆるIV族およびIV族合金系アモルファス半導体や微結晶半導体が挙げられる。p層またはn層を構成する半導体材料は、前述したi層を構成する半導体材料に価電子制御剤をドーピングすることによって得られる。また原料として、p型半導体を得るための価電子制御剤には周期律表第III族の元素を含む化合物が用いられる。第III族の元素としては、B、Al、Ga、Inが挙げられる。n型半導体を得るための価電子制御剤としては周期律表第V族の元素を含む化合物が用いられる。第V族の元素としては、P、N、As、Sbが挙げられる。

【0020】

アモルファスシリコン半導体層および微結晶シリコン半導体層の成膜法としては、蒸着法、スパッタ法、RFプラズマCVD法、マイクロ波プラズマCVD法、VHFCVD法、ECR法、熱CVD法、LPCVD法等の公知の方法を所望に応じて用いる。工業的に採用されている方法としては、原料ガスをRFプラズマで分解し、基板上に堆積させるRFプラズマCVD法が好んで用いられる。さらに、RFプラズマCVDにおいては、原料ガスの分解効率が約10%と低いことや、堆積速度が1Å/secから10Å/sec程度と遅いことが問題であるが、この点を改良できる成膜法としてマイクロ波プラズマCVD法やVHFプラズマCVD法が注目されている。以上の成膜を行うための反応装置としては、バッチ式の装置や連続成膜装置などの公知の装置が所望に応じて使用できる。本発明の光起電力素子は、分光感度や電圧の向上を目的として半導体接合を2以上積層するいわゆるタンデムセルにも適用することができる。

【0021】

光起電力層とバイパスダイオード層を個別に形成するためには、1つの真空チャンバ内の中に成膜が行われないようにするための防着板(マスク)を設ければ良い。この場合、枚葉式の場合で作成してもよい。また光起電力層の半導体接合層(第1の半導体接合層)はn、i、pの順で成膜し、バイパスダイオード層の半導体接合層(第2の半導体接合層)のみもう一度p、i、nの順で形成する。次に、本実施形態の光起電力素子を有する太陽電池を構成する構成要素について説明する。また、この太陽電池の構成図を図4に示すが、図4の説明は実施例1において後述する。

【0022】

(基板)

本発明において基板は必須ではないが、薄膜半導体を適当な形状、あるいは大きさの基板上に形成することにより、好適な構成が得られる。例えば基板が金属である場合、半導体層や電極層のような薄膜の層を機械的に支持だけでなく電極(第1電極)としても用いることができる。そもそも基板は、導電性のものでも電気絶縁性のものでも良いが、基板の材料が絶縁性のものである場合、基板表面を導電処理することで、電極として利用できる。このような基板は前記半導体層や電極層を成膜するときの加熱温度に耐え得る耐熱性が要求されるが、さらには成膜プロセスがロールツーロールであれば、基板としては長尺であることが要求され、また、テンションをかけて巻き取ることから、伸びが無く寸法安定性が要求される。

【0023】

以上の要求を満たす基板材料の中で好ましい導電性の材料としては、具体的にはFe、Ni、Cr、Al、Mo、Au、Nb、Ta、V、Ti、Pt、Pb、Ti等の金属またはこれらの合金、例えば真鍮、ステンレス鋼等の薄板およびその複合体やカーボンシート、亜鉛メッキ鋼板等が挙げられる。とりわけ、ステンレス鋼は成膜時の加熱温度に対しての耐熱性が良好であり、ロールツーロールのような連続成膜を行う場合にも適し、例えば0.15mm程度と薄くした場合でも強度があるなどの特徴のため、好適な材料である。また、基板材料の中で好ましい電気絶縁性材料としては、ポリエステル、ポリエチレン、ポリカーボネート、セルロースアセテート、ポリプロピレン、ポリ塩化ビニル、ポリ塩化ビニリデン、ポリスチレン、ポリアミド、ポリイミド、エポキシ等の耐熱性合成樹脂のフィルムもしくはシートまたはこれらとガラスファイバ、カーボンファイバ、ホウ素ファイバ、および、ガラス、セラミックスなどが挙げられる。とりわけガラス基板、ポリイミド基板が好適な基板として用いられる。

【0024】

(上部電極)

光起電力層はその光入射側に上部電極を有してもよい。この上部電極は本発明において必須ではないが、第1の半導体接合層の材料がアモルファスシリコンのように抵抗が高い場合には、シート抵抗を下げる目的で形成される。微結晶を含む結晶系のようにシート抵抗が低ければ必ずしも上部電極を設ける必要はない。上部電極は第1の半導体接合層で発生した起電力を取り出すための電極であり、基板側の第1電極と対をなすものである。上部電極はアモルファスシリコンのようにシート抵抗が高い半導体を用いる場合において、基板と水平な方向に電流を取り出すために必要であり、シート抵抗値は300Ω/□以下であることが望ましい。上部電極の膜厚は、抵抗値が十分低く、透明性が損なわれず、また場合によっては光の干渉条件を用いて透過すべき光の波長で反射が最小となるように設計される。例えばITOを上部電極として用いて550nmの光の反射を最小とするためには700Å程度とするのが好ましい。また、前記第2電極は、光入射側に位置し、太陽や白色蛍光灯等からの光を半導体層内に効率良く吸収させるために光の透過率が85%以上であることが望ましい。このような特性を備えた好適な材料としてSnO2 、In2 O3 、ZnO、CdO、CdSnO4 、ITO(In2 O3 +SnO2 )などの金属酸化物が挙げられる。上部電極(第2電極)の形成方法としては、蒸着法、スパッタ法、反応性スパッタ法等の公知の方法が所望に応じて用いられる。

【0025】

(集電電極)

集電電極は半導体層の受光面側に間隔をあけて櫛状に設けられる。更に前述の上部電極を有する光起電力素子においては、上部電極(第2電極)上に櫛状に形成されるものであり、その目的は、第2電極のシート抵抗が高いためにそのままで集電すると直列抵抗が大きくなり、光起電力素子の変換効率が低くなるので、これを改善するために低抵抗の電極として設けるものである。集電電極の配置の仕方としては、集電による電気抵抗とシャドーロスを最小限にするように、集電電極の幅やピッチなどが決定される。集電電極は比抵抗が低く、光起電力素子の直列抵抗とならないことが要求され、望ましい比抵抗は10-2Ωcm〜10-6Ωcmである。集電電極の材料としては、Ti、Cr、Mo、W、Al、Ag、Ni、Cu、Sn、Pt、Cu等の金属またはこれらの合金や半田が用いられる。集電電極の作製法としては、前記金属材料の粉末にポリマのバインダおよびバインダの溶剤を適度な比率で混合してペースト状とした、いわゆる導電性ペーストのスクリーン印刷を用いたり、前記金属材料のメッキ法を用いたり、前記金属材料をワイヤ状にして敷設したりする方法などが挙げられる。

【0026】

集電電極は櫛状であるが、集電電極の形成においては、所望の形状のマスクパターンを用い、スパッタリング法、抵抗加熱法、CVD法等により所望の位置に所望の形状で形成される。あるいは全面に金属層を蒸着した後にエッチングしてパターニングする方法、光CVDにより直接集電電極パターンを形成する方法、集電電極のネガパターンのマスクを形成した後にメッキ法により形成する方法、導電性ペーストを印刷して形成する方法などを用いることでもできる。前記スクリーン印刷法は、ポリエステルやステンレスからなるメッシュに所望のパターニングを施したスクリーンを用いて導電性ペーストを印刷インキとして用いるものであり、集電電極の幅を、最小で50μm位とすることができる。印刷機は市販のスクリーン印刷機が好適に用いられる。スクリーン印刷した導電性ペーストはバインダを架橋させ、溶剤を揮発させるために乾燥炉で加熱する。乾燥炉としては熱風オーブンやIRオーブンが用いられる。

【0027】

集電電極は金属ワイヤで形成することも可能である。その場合、Ti、Cr、Mo、W、Al、Ag、Ni、Cu、Sn、Pt、Cu等の金属ワイヤが好適に用いられ、ワイヤの径は50μm〜200μmが好ましい。金属ワイヤを導電性接着剤を用いて前記第2電極上に接着することにより集電電極が形成される。また、金属ワイヤはあらかじめ導電性接着剤で被覆されていても良い。また集電電極をバイパスダイオード層とを接触するように設けてもよい。その場合、上部電極は、光起電力層と、集電電極の両方と接続していればよい。

【0028】

(バスバー)

本発明においてはバスバーが必要に応じて用いられる。バスバーとは、集電電極を流れる電流を更に一端に集めるための電極である。バスバーの材料としては、Ag、Pt、Cu等の金属やこれらの合金からなるものを用いることができ、形態としては、ワイヤ状や箔状のものを張り付けたり、前記集電電極と同様の導電性ペーストを用いたものでも良い。箔状のものとしては、例えば銅箔や、銅箔にスズメッキしたものであって、場合によっては接着剤付きのものが用いられる。バスバーの形成方法としては、金属ワイヤを導電性接着剤で固定したり、銅箔を張り付けたりする方法を用いることができる。あるいは、集電電極と同様にして形成しても良い。

【0029】

(第2の半導体接合層)

バイパスダイオード層における第2の半導体接合層は前述したように、少なくとも1つのpnまたはpin接合を有する薄膜の半導体層であって前記基板上に堆積されるものであり、第1の半導体接合層とほぼ同様の方法、材料で形成される。第1の半導体接合層と同時に形成してもよく、別に形成しても良い。バイパスダイオードは例えば光起電力素子に入光する光が遮られたときに、直列に接続している他の光起電力素子が発生する動作電流をバイパスする機能を有し、光起電力素子の動作点での電圧において前記動作電流が迂回できる必要がある。このために、バイパスダイオードの動作電流および動作電圧は所望の仕様で決定されるものである。動作電流を増減させるためには例えばバイパスダイオード層の面積を増減させたりあるいは半導体層中の不純物の濃度を増減させれば良い。

【0030】

【実施例】

次に本発明の実施例を説明するが、本発明はこれらの実施例により限定されるものではない。

(実施例1)

図3(a)〜(c)はそれぞれ本発明の実施例に係る3種のバイパスダイオード付き光起電力素子のバイパスダイオード部分を示す模式的断面図である。これらの図に示すように、各光起電力素子30はそれぞれ、光起電力を発生する半導体接合層を有する光起電力層32と、バイパスダイオード層38上に設けられた集電電極34とを有する。バイパスダイオード層38は、光起電力層32の半導体接合層である第1の半導体接合層とは別の第2の半導体接合層である。

【0031】

図3(a)の素子では、光起電力層32およびバイパスダイオード層38の半導体接合層はいずれも1つのpin接合を構成するものとして形成されているとともに、受光面側に上部電極33が設けられている。また、バイパスダイオード層38のイントリンジック層36と光起電力層32のイントリンジック層35は別々に成膜されてたものである。図3(b)の素子では、光起電力層32およびバイパスダイオード層38の半導体接合層はいずれも薄膜による1つのpn接合を構成するものである。また薄膜のシート抵抗が小さい材料を用いているので上部電極は無い。図3(c)の素子では、光起電力層32のイントリンジック層およびバイパスダイオード層38のイントリンジック層37は双方の半導体接合層に渡って連続しており、共通化されるように設けられている。図4(a)および(b)は、図3の構成による光起電力素子の全体を受光面側が表わした模式的平面図および断面図である。図4(b)は、集電電極34に平行な断面を示した模式図である。

【0032】

図3(a)の光起電力素子を次のようにして作製した。まず、十分に脱脂および洗浄を行ったSUS430BA製基板(厚み0.2mm)31を不図示のRFプラズマCVD成膜装置に入れ、n層、i層、p層の順で堆積を行い、光起電力層32の半導体接合層を形成した。ただしこのとき、基板31に対して5mmの間隔を空けて1mm幅の直線状にポリイミド接着テープでマスクしておき、その部分には半導体接合層が形成されないようにした。つまり、光起電力層32の半導体接合層を1mmの間隔を置いて複数箇所に形成した。

【0033】

次に、この半導体接合層が形成された基板31を、不図示の抵抗加熱の蒸着装置に入れ、酸素を導入しながら内圧を1×10-4Torrに保ち、InとSnの合金を抵抗加熱により蒸着して、反射防止効果を兼ねた機能を有する透明なITOの上部電極33を700Å堆積させ、光起電力層32の形成を完了した。

【0034】

次に、基板31上の前記マスクを取り除き、代わりに光起電力層32をマスクした後、前記CVD成膜装置を用い、p層、i層、n層の順に成膜してバイパスダイオード層38を形成した。バイパスダイオード層38のp、i、n層は隣接する光起電力層32と面一となるように形成できた。またバイパスダイオード層38の上にも上部電極33を光起電力層32上の上部電極と面一になるように形成できた。

【0035】

次に、上部電極33の周囲をエッチングし、半導体が露出する領域47を形成した。その後、基板31の一方の端に絶縁テープ45を貼り付けた。

【0036】

次に、ウレタン樹脂にカーボンブラックを分散させた導電性樹脂で被覆された直径100μmの銅ワイヤを、バイパスダイオード層38の上に、上部電極33に接するようにして配置し、そして1kg/cm2 の圧力をかけながら200℃で10分間加熱することにより、上部電極33および絶縁テープ45上に固定して、集電電極34を形成した。

【0037】

そして、100μmの厚みの銅箔からなるバスバー46を絶縁テープ45と重なるように集電電極34の上に貼り付け、図3(a)のバイパスダイオード付き光起電力素子の作製を完了した。

さらに、同様の方法でこの光起電力素子の試料を10枚作製した。

【0038】

次に、これら試料の樹脂封止(エンカプシュレーション)を行った。つまりまず、基板31の上下にEVA樹脂を積層した。このときバイパスダイオード層も光起電力層もEVAによりおおわれる。またこの、光入射面側のEVAの厚みは250μmとした。さらに光入射側にフッ素樹脂フィルムをEVAにはりあわせるように積層し、裏面側では金属製のプレートをEVAにはりあわせるように積層し、その後、真空ラミネータに投入して加熱圧着させるために150℃で60分間保持し、真空ラミネーションを行った。

【0039】

次に、樹脂封止された各試料の初期特性を、JISC8935のアモルファス太陽電池モジュールの出力測定方法の定めに従って測定した。まず、AM1.5グローバルの太陽光スペクトルで100mW/cm2 の光量の疑似太陽光源(SPIRE社製;以下シミュレータと呼ぶ)を用いて、太陽電池特性を測定し、変換効率を求めた。その結果、得られた特性は良好であり、ばらつきも少なかった。なお、シャドーロスは4.5%であった。

【0040】

次に、これらの試料の信頼性試験を、JISC8938のアモルファス太陽電池モジュールの環境試験方法および耐久性試験方法に定められた温湿度サイクル試験A−2に基づいて行った。すなわちまず、試料を温湿度が制御できる恒温恒湿器に投入し、−40℃から+85℃(相対湿度85%)に変化させるサイクル試験を10回繰り返し行った。次に、試験終了後の試料を観察した。その結果、ラミネーション材料の剥離や膨れは無く、良好な外観であった。

【0041】

以上のように、本実施例の光起電力素子によれば、バイパスダイオード部分を光起電力層に一体化させ、集電電極34の下にバイパスダイオード層38を設けるようにしたため、シャドーロスを低減し、かつ平坦化して、ラミネーション材料を薄くすることができるとともに、さらに良好な信頼性を得ることができた。

【0042】

(比較例1)

次に、比較のため、図9の従来のバイパスダイオードを用いた光起電力素子91を実施例1とほぼ同様にして作製した。すなわち、実施例1と同様にして基板(不図示)上に上部電極(不図示)までを形成し、さらに集電電極(不図示)およびバスバー(不図示)を形成して、光起電力素子91を作製した。

【0043】

次に、光起電力素子91にダイオード92を結線してから、実施例1と同様にしてラミネーションを行って、太陽電池モジュール90を形成した。このとき、ラミネーション材料の厚みを250μm、500μm、1mm、3mmと変化させた。1mm以下では、ダイオード部分で充填不良が起こり、3mmでは良好であった。

【0044】

以上から、実施例1のバイパスダイオード付き光起電力素子によれば、従来の光起電力素子91より薄く太陽電池モジュールを形成することができ、ラミネーション材料が少なくて済んだ。

【0045】

(実施例2)

本実施例では、図4に示した構成のバイパスダイオード付き光起電力素子30を直列化した不図示の光起電力素子を作製した。すなわち、まず、図4の30に示す構成のバイパスダイオード付き光起電力素子を10枚作製し、次に、各光起電力素子のバスバー46を順次隣りの光起電力素子の基板31にインタコネクタで接続することにより、光起電力素子を10枚直列にして直列化光起電力素子を形成した。

【0046】

次に、この直列化光起電力素子の樹脂封止(エンカプシュレーション)を以下のように行った。まず、各基板31の上下つまり受光面側とその反対側にEVAを積層した。このとき、光入射面側のEVAの厚みは250μmとした。さらに、光入射側にフッ素樹脂フィルムを積層し、裏面側に金属製のプレートを積層した後、真空ラミネータに投入し、150℃で60分間保持して真空ラミネーションを行った。

【0047】

次に、樹脂封止された直列化光起電力素子の初期特性をJISC8935のアモルファス太陽電池モジュールの出力測定方法の定めに従って測定した。すなわち、まず、AM1.5グローバルの太陽光スペクトルで100mW/cm2の光量の疑似太陽光源(SPIRE社製;以下シミュレータと呼ぶ)を用いて太陽電池特性を測定し、そして、変換効率を求めた。この結果、特性は良好であり、ばらつきも少なかった。

【0048】

次に、信頼性試験を、JISC8938のアモルファス太陽電池モジュールの環境試験方法および耐久性試験方法に定められたホットスポット試験A−1に基づいて行った。すなわちまず、試料にソーラシミュレータにより100mW/cm2の光を照射し、10直列のモジュール(直列化光起電力素子)のうち1枚の光起電力素子のみが影となるようにした。このようにして10分放置した後に太陽電池特性を初期と同様にしてシミュレータを用いて測定したところ、初期の変換効率に対して有意な劣化は生じていなかった。

【0049】

以上から、本実施例の光起電力素子による太陽電池は、良好な特性を有し、部分的な影の影響によるホットスポットのダメージを防ぐことができ、信頼性も高いことがわかる。

【0050】

(比較例2)

次に、比較のため、バイパスダイオードの無い従来の不図示の光起電力素子を実施例1とほぼ同様にして作製した。すなわち、まず、実施例1と同様にして基板上に上部電極までを形成し、次に、粘着材付きの絶縁層を基板の両端に貼り付け、その後、実施例1と同様にして集電電極を形成した。さらに銅箔のバスバーを積層し、光起電力素子の作製を完了した。

【0051】

次に、このようにして得られた光起電力素子を10枚直列化した。そして、この直列化した光起電力素子のエンカプシュレーションを、実施例1と同様にして行った。

【0052】

次に、エンカプシュレーションした光起電力素子の初期特性を実施例1と同様の手順で測定し、さらに、信頼性試験を実施例2と同様にして行い、評価した。試験終了後の特性を測定したところ、効率が約7.5%下がっていた。効率が下がった原因を解析した結果、影の部分で発電しない光起電力素子に逆バイアスが印加されることにより影の部分の光起電力素子がシャントしたためであった。

【0053】

(実施例3)

図5は本発明の第3の実施例に係る光起電力素子を示す断面図である。同図に示すように、この光起電力素子50における光起電力層52はトリプルセル構成であって、その半導体接合層はpin接合した半導体層を3つ重ねたものであり、バイパスダイオード層53はシングルセル構成であって、その半導体接合層はpin接合した半導体層を1つのみ有するものである。光起電力層52およびバイパスダイオード層53は横方向に隣接して同一基板51上に形成され、それらの半導体接合層における半導体接合の順方向は互いに逆向きであり、光起電力層52およびバイパスダイオード層53は光入射側において、いずれも集電電極54に接合している。また光起電力層52をpn接合からなるトリプルセル構成とし、バイパスダイオード層もpn接合からなるシンプルセル構成とした光起電力素子も同様に作成した。

【0054】

図6および図7は、光起電力素子50をロールツーロール法でトリプルセル成膜装置60により作製する方法を示す。図6(a)はロールツーロール法の成膜装置の断面模式図である。図6(a)に示すように、成膜用のチャンバ62〜70は、この順で並べられているが、n層用がチャンバ62、65、68、i層用がチャンバ63、66、69、p層用が64、67、70であり、トリプルセルが成膜できるように配置されている。図7はマスク(ジャマ板)を設けたチャンバー内を基板が通過する様子を示す断面模式図である。ボトム層のp層とミドル層のi層とトップ層のn層を形成するための真空チャンバ64、66、68以外のチャンバには、図7に示すように、真空チャンバ72内にプラズマを遮るためのジャマ板73があり、基板51の一部を成膜しないようになっている。ジャマ板73は、複数の集電電極54に対応した位置に集電電極54とほぼ同じ幅となるように配置される。この構造により、光起電力層52の半導体接合層を形成するとともに基板51の一部にはボトム層のp層とミドル層のi層とトップ層のn層が成膜されてバイパスダイオード層53が基板上に形成されるようになっている。つまり、光起電力層52の半導体接合層を構成する9つの半導体層のうちの3、5および7層目を、バイパスダイオード層53の半導体接合層を構成する3つの半導体層のうちの1、2および3層目とそれぞれ同一材料で同時に形成する。

【0055】

この装置を用いて図5の光起電力素子50を製造した。つまり、まず、図6に示すように、長尺でコイル状に巻かれたSUS430の基板51を、成膜装置の送り出しチャンバ61にセットし、反対側の巻取りチャンバ71まで一定のスピードで搬送しながら、図6(b)に示すように、基板51上に光起電力層52およびバイパスダイオード層53を形成した。次に、不図示の別の真空チャンバを用いて光起電力層52上のみに上部電極を形成した。この成膜後、長尺基板51を20cmごとに切断してシート状とした。その後、切断された各基板の周囲の上部電極を、実施例1と同様にしてエッチング除去し、さらに集電電極54およびバスバーを形成した。

【0056】

次に、このようにして得られた10枚の光起電力素子50のエンカプシュレーションを、実施例1と同様にして行い、10枚の光起電力素子の試料を作製した。

【0057】

次に、得られた各試料の初期特性を実施例1と同様の手順で測定したところ、変換効率は8.5%±1.5%と良好であり、シャドーロスも4.5%と少なく、ばらつきも少なかった。

【0058】

(実施例4)

本実施例では、図8(a)に示す構成のバイパスダイオード付き光起電力素子80を作製し、さらにこれを任意の幅に分割して切りはなし図8(b)に示す光起電力素子81を作製した。

【0059】

まず、実施例1と同様の方法で上部電極83までを形成し、分割する部分の上部電極83と基板周囲の上部電極83をエッチングして、半導体を露出した領域87を形成した。次に、集電電極84を実施例1と同様にして固定した。さらに集電電極84とバスバー89とを銀ペーストで固定して、図8(a)に示す構成のバイパスダイオード付き光起電力素子80を完成した。

【0060】

次に、作製した光起電力素子80の変換効率を測定した。その後、エッチングラインの部分でセルを4分割して、図8(b)に示すような光起電力素子81を作製した。各光起電力素子81の変換効率を測定した。

【0061】

光起電力素子80と81の変換効率を比較したところ、分割前後での変換効率にはほとんど差が無く、分割によるダメージはなかった。したがって、以上のようにして、任意の幅で分割できるバイパスダイオード付き光起電力素子が得られることがわかった。

【0062】

【発明の効果】

以上説明したように本発明によれば、集電電極の下部に、第2の半導体接合を有するバイパスダイオード層を設けるようにしたため、シャドーロスが少なく変換効率の高い光起電力素子を、複雑なプロセスを用いずに、成膜により形成することができる。

【0063】

また、光起電力層とバイパスダイオード層とを平行に帯状にほぼ等しい長さで形成するようにしたため、光起電力素子を任意の幅で分割することができる。

【0064】

また、第1の半導体接合層を構成するイントリンジック層と第2の半導体接合層を形成するイントリンジック層とが連続するようにしたため、光起電力素子を簡便に製造することができる。

【0065】

さらに、第1の半導体接合層を、pinまたはpn接合した半導体層を3つ重ねたトリプルセル構成とし、第2の半導体接合層をシングルセル構成としたため、光起電力素子を簡便に製造することができる。

【図面の簡単な説明】

【図1】 本発明の光起電力素子の等価回路を示す図である。

【図2】 本発明係る光起電力装置の半導体層の構成の一例を模式的示す断面図である。

【図3】 本発明に従った3種類の光起電力素子の構成を模式的に示す図である。

【図4】 図3の光起電力素子の全体を示す平面図および断面図である。

【図5】 本発明の第3の実施例に係る光起電力素子の構成を模式的に示す図である。

【図6】 本発明の第3の実施例に係る光起電力素子の製造方法を模式的に示す図である。

【図7】 図6の製造方法で用いる製造装置の一部を模式的に示す図である。

【図8】 本発明の第4の実施例に係る分割して光起電力素子を得る方法を模式的に示す図である。

【図9】 従来の光起電力素子を直列化した構成を模式的に示す図である。

【符号の説明】

11:光起電力層のダイオード成分、12:光起電力層の直流電源成分、13:バイパスダイオード、21:半導体層、22,31,51:基板、23(231,232),38,53:バイパスダイオード層、24(241,242),32,52:光起電力層、25,34,54,84:集電電極、30,50,80,90:光起電力素子、33,83:上部電極、35,36,37:イントリンジック層、45:絶縁テープ、46,89:バスバー、47,87:半導体を露出した領域、60:トリプルセル成膜装置、61:送り出しチャンバ、62〜70:成膜用のチャンバ、71:巻取りチャンバ、72:真空チャンバ、73:ジャマ板、90:太陽電池モジュール、91:太陽電池セル、92:バイパスダイオード、93,94:配線、95:ガラス、96:封止用の樹脂、97:裏面プラスチック材料。

Claims (9)

- 薄膜半導体からなる第1の半導体接合層である薄膜光起電力層と、前記薄膜光起電力層の光入射側に間隔を開けて櫛状に設けられた集電電極とを備えた薄膜光起電力素子において、前記薄膜光起電力素子は、薄膜半導体からなる第2の半導体接合層であるバイパスダイオード層を有し、前記バイパスダイオード層は前記集電電極の各下部に存在し且つ前記薄膜光起電力層と並列に接続されるように設けられていて、前記第1の半導体接合層と前記第2の半導体接合層は同一面上に存在し、前記薄膜光起電力層とバイパスダイオード層は平行かつほぼ等しい長さの帯状であり、前記第1の半導体接合層と前記第2の半導体接合層における半導体接合の順方向は互いに逆向きであって、前記薄膜光起電力層および前記バイパスダイオード層は、光入射側においていずれも前記集電電極に接合していることを特徴とする薄膜光起電力素子。

- 前記第1および第2の半導体接合層はいずれもイントリンジック層を有し、かつそれらのイントリンジック層は両半導体接合層に渡って連続していることを特徴とする請求項1に記載の薄膜光起電力素子。

- 前記薄膜光起電力層はトリプルセル構成であって、その半導体接合層はpinまたはpn接合した半導体層を3つ重ねたものであり、前記バイパスダイオード層はシングルセル構成であって、その半導体接合層はpinまたはpn接合した半導体層を1つのみ有するものであることを特徴とする請求項1または2のいずれか1項に記載の薄膜光起電力素子。

- 前記薄膜光起電力層およびバイパスダイオード層は横方向に隣接して同一基板上に形成されたものであることを特徴とする請求項1〜3のいずれか1項に記載の薄膜光起電力素子。

- 前記第1および第2の半導体接合層における半導体接合の順方向は互いに逆向きであり、前記薄膜光起電力層およびバイパスダイオード層は、光入射側において、いずれも前記集電電極に接合していることを特徴とする請求項1〜4のいずれか1項に記載の薄膜光起電力素子。

- 導電性のまたは導電膜を形成した基板上に、薄膜半導体からなる第1の半導体接合層である薄膜光起電力層を所定の間隔を置いて複数箇所に形成する工程と、前記薄膜光起電力層が形成される各個所の間の前記基板上に、順方向が前記第1の半導体接合層とは逆向きであって薄膜半導体からなる第2の半導体接合層であるバイパスダイオード層を、前記第1の半導体接合層と前記第2の半導体接合層が同一面に設けられるように形成する工程と、前記各バイパスダイオード層の上に、前記薄膜光起電力層および前記各バイパスダイオード層に接合するように櫛状の集電電極を形成する工程とを具備することを特徴とする薄膜光起電力素子の製造方法。

- 前記薄膜光起電力層およびバイパスダイオード層を形成する際、前記第1の半導体接合層を構成する半導体層のうちの少なくとも1層および前記第2の半導体接合層を構成する半導体層のうちの少なくとも1層を同一材料で同時に形成することを特徴とする請求項6に記載の薄膜光起電力素子の製造方法。

- 前記第1および第2の半導体接合層をいずれも1つのpin接合を構成するものとして形成し、その際、両接合層のi層を、同一材料で同時に形成することを特徴とする請求項7に記載の薄膜光起電力素子の製造方法。

- 前記第1の半導体接合層を、pin接合した半導体層を3つ重ねたものとして形成するとともに、前記第2の半導体接合層を、1つのpin接合した半導体層として形成し、その際、前記第1の半導体接合層を構成する9つの半導体層のうちの3、5および7層目を、前記第2の半導体接合層を構成する3つの半導体層のうちの1、2および3層目とそれぞれ同一材料で同時に形成することを特徴とする請求項7に記載の薄膜光起電力素子の製造方法。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP15704099A JP3754841B2 (ja) | 1998-06-11 | 1999-06-03 | 光起電力素子およびその製造方法 |

| US09/327,569 US6184458B1 (en) | 1998-06-11 | 1999-06-08 | Photovoltaic element and production method therefor |

| EP99111326A EP0971417A3 (en) | 1998-06-11 | 1999-06-10 | Photovoltaic element and production method therefor |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17801098 | 1998-06-11 | ||

| JP10-178010 | 1998-06-11 | ||

| JP15704099A JP3754841B2 (ja) | 1998-06-11 | 1999-06-03 | 光起電力素子およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000068548A JP2000068548A (ja) | 2000-03-03 |

| JP3754841B2 true JP3754841B2 (ja) | 2006-03-15 |

Family

ID=26484622

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP15704099A Expired - Fee Related JP3754841B2 (ja) | 1998-06-11 | 1999-06-03 | 光起電力素子およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US6184458B1 (ja) |

| EP (1) | EP0971417A3 (ja) |

| JP (1) | JP3754841B2 (ja) |

Families Citing this family (65)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8138413B2 (en) * | 2006-04-13 | 2012-03-20 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US8222513B2 (en) | 2006-04-13 | 2012-07-17 | Daniel Luch | Collector grid, electrode structures and interconnect structures for photovoltaic arrays and methods of manufacture |

| US8664030B2 (en) | 1999-03-30 | 2014-03-04 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US20090111206A1 (en) | 1999-03-30 | 2009-04-30 | Daniel Luch | Collector grid, electrode structures and interrconnect structures for photovoltaic arrays and methods of manufacture |

| US8076568B2 (en) * | 2006-04-13 | 2011-12-13 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US7507903B2 (en) | 1999-03-30 | 2009-03-24 | Daniel Luch | Substrate and collector grid structures for integrated series connected photovoltaic arrays and process of manufacture of such arrays |

| US7898054B2 (en) * | 2000-02-04 | 2011-03-01 | Daniel Luch | Substrate structures for integrated series connected photovoltaic arrays and process of manufacture of such arrays |

| US20110067754A1 (en) * | 2000-02-04 | 2011-03-24 | Daniel Luch | Substrate structures for integrated series connected photovoltaic arrays and process of manufacture of such arrays |

| US8198696B2 (en) | 2000-02-04 | 2012-06-12 | Daniel Luch | Substrate structures for integrated series connected photovoltaic arrays and process of manufacture of such arrays |

| US7898053B2 (en) * | 2000-02-04 | 2011-03-01 | Daniel Luch | Substrate structures for integrated series connected photovoltaic arrays and process of manufacture of such arrays |

| TW569653B (en) * | 2001-07-10 | 2004-01-01 | Fujikura Ltd | Multilayer wiring board assembly, multilayer wiring board assembly component and method of manufacture thereof |

| US6680432B2 (en) * | 2001-10-24 | 2004-01-20 | Emcore Corporation | Apparatus and method for optimizing the efficiency of a bypass diode in multijunction solar cells |

| US6864414B2 (en) * | 2001-10-24 | 2005-03-08 | Emcore Corporation | Apparatus and method for integral bypass diode in solar cells |

| WO2003054926A2 (en) * | 2001-10-24 | 2003-07-03 | Emcore Corporation | An apparatus and method for integral bypass diode in solar cells |

| EP1367653A1 (en) | 2002-05-27 | 2003-12-03 | Centro De Investigaciones Energeticas Medioambientales Y Tecnologicas (C.I.E.M.A.T.) | Method for preparing transparent and conducting sheets on polymers |

| DE10239845C1 (de) * | 2002-08-29 | 2003-12-24 | Day4 Energy Inc | Elektrode für fotovoltaische Zellen, fotovoltaische Zelle und fotovoltaischer Modul |

| JP2004140120A (ja) * | 2002-10-16 | 2004-05-13 | Canon Inc | 多結晶シリコン基板 |

| US6784358B2 (en) * | 2002-11-08 | 2004-08-31 | The Boeing Co. | Solar cell structure utilizing an amorphous silicon discrete by-pass diode |

| JP2004228333A (ja) * | 2003-01-23 | 2004-08-12 | Canon Inc | 光起電力セル、及びその製造方法 |

| FR2850489B1 (fr) * | 2003-01-24 | 2005-05-06 | Dgtec | Procede de realisation d'un module photovoltaique et module photovoltaique realise par ce procede |

| DE102004013833B4 (de) * | 2003-03-17 | 2010-12-02 | Kyocera Corp. | Verfahren zur Herstellung eines Solarzellenmoduls |

| US7153722B2 (en) * | 2003-06-06 | 2006-12-26 | Canon Kabushiki Kaisha | Method and apparatus for manufacturing photovoltaic device |

| JP2005142268A (ja) * | 2003-11-05 | 2005-06-02 | Canon Inc | 光起電力素子およびその製造方法 |

| CN100536148C (zh) * | 2004-06-04 | 2009-09-02 | 新南创新私人有限公司 | 薄膜太阳能电池的互连 |

| US20070144577A1 (en) * | 2005-12-23 | 2007-06-28 | Rubin George L | Solar cell with physically separated distributed electrical contacts |

| US7498508B2 (en) * | 2006-02-24 | 2009-03-03 | Day4 Energy, Inc. | High voltage solar cell and solar cell module |

| US8822810B2 (en) | 2006-04-13 | 2014-09-02 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US9236512B2 (en) | 2006-04-13 | 2016-01-12 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US9865758B2 (en) | 2006-04-13 | 2018-01-09 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US8884155B2 (en) | 2006-04-13 | 2014-11-11 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US8729385B2 (en) | 2006-04-13 | 2014-05-20 | Daniel Luch | Collector grid and interconnect structures for photovoltaic arrays and modules |

| US9006563B2 (en) | 2006-04-13 | 2015-04-14 | Solannex, Inc. | Collector grid and interconnect structures for photovoltaic arrays and modules |

| KR20080021428A (ko) * | 2006-09-04 | 2008-03-07 | 엘지전자 주식회사 | 바이패스 다이오드를 포함하는 광기전력 변환장치 및 그제조방법 |

| WO2008039461A2 (en) * | 2006-09-27 | 2008-04-03 | Thinsilicon Corp. | Back contact device for photovoltaic cells and method of manufacturing a back contact |

| US7410542B2 (en) * | 2006-10-10 | 2008-08-12 | Paul Terrance Nolan | Variable environment, scale-able, roll to roll system and method for manufacturing thin film electronics on flexible substrates |

| US20080092944A1 (en) * | 2006-10-16 | 2008-04-24 | Leonid Rubin | Semiconductor structure and process for forming ohmic connections to a semiconductor structure |

| WO2008150769A2 (en) * | 2007-05-31 | 2008-12-11 | Thinsilicon Corporation | Photovoltaic device and method of manufacturing photovoltaic devices |

| US20090293955A1 (en) * | 2007-11-07 | 2009-12-03 | Qualcomm Incorporated | Photovoltaics with interferometric masks |

| AU2007362562A1 (en) * | 2007-12-18 | 2009-06-25 | Day4 Energy Inc. | Photovoltaic module with edge access to PV strings, interconnection method, apparatus, and system |

| US20100043863A1 (en) * | 2008-03-20 | 2010-02-25 | Miasole | Interconnect assembly |

| US8912429B2 (en) * | 2008-03-20 | 2014-12-16 | Hanergy Holding Group Ltd. | Interconnect assembly |

| US20110197947A1 (en) | 2008-03-20 | 2011-08-18 | Miasole | Wire network for interconnecting photovoltaic cells |

| US20090308860A1 (en) * | 2008-06-11 | 2009-12-17 | Applied Materials, Inc. | Short thermal profile oven useful for screen printing |

| NL2001815C2 (en) * | 2008-07-17 | 2010-01-19 | Stichting Energie | Reversed dye-sensitized photovoltaic cell. |

| BRPI0822954A2 (pt) * | 2008-07-28 | 2015-06-23 | Day4 Energy Inc | Célula fotovoltaica de silício cristalino com emissor seletivo produzida com processo de retroataque de precisão em baixa temperatura e de passivação |

| US20110247688A1 (en) * | 2008-09-12 | 2011-10-13 | Lg Chem, Ltd. | Front electrode for solar cell having minimized power loss and solar cell containing the same |

| EP2332177A4 (en) * | 2008-09-29 | 2012-12-26 | Thinsilicon Corp | MONOLITHICALLY INTEGRATED SOLAR MODULE |

| US20100096006A1 (en) * | 2008-10-16 | 2010-04-22 | Qualcomm Mems Technologies, Inc. | Monolithic imod color enhanced photovoltaic cell |

| US8080729B2 (en) * | 2008-11-24 | 2011-12-20 | Palo Alto Research Center Incorporated | Melt planarization of solar cell bus bars |

| WO2010129163A2 (en) * | 2009-05-06 | 2010-11-11 | Thinsilicon Corporation | Photovoltaic cells and methods to enhance light trapping in semiconductor layer stacks |

| WO2010144421A2 (en) * | 2009-06-10 | 2010-12-16 | Thinsilicon Corporation | Photovoltaic modules and methods of manufacturing photovoltaic modules having multiple semiconductor layer stacks |

| US20110114156A1 (en) * | 2009-06-10 | 2011-05-19 | Thinsilicon Corporation | Photovoltaic modules having a built-in bypass diode and methods for manufacturing photovoltaic modules having a built-in bypass diode |

| TWI453928B (zh) * | 2009-06-10 | 2014-09-21 | Solarbase Group Inc | 太陽能模組及製造具有串聯半導體層堆疊之太陽能模組之方法 |

| US8356640B1 (en) | 2010-01-14 | 2013-01-22 | Mia Solé | Apparatuses and methods for fabricating wire current collectors and interconnects for solar cells |

| US9061344B1 (en) | 2010-05-26 | 2015-06-23 | Apollo Precision (Fujian) Limited | Apparatuses and methods for fabricating wire current collectors and interconnects for solar cells |

| US10026859B2 (en) | 2010-10-04 | 2018-07-17 | Beijing Apollo Ding Rong Solar Technology Co., Ltd. | Small gauge wire solar cell interconnect |

| US8951824B1 (en) | 2011-04-08 | 2015-02-10 | Apollo Precision (Fujian) Limited | Adhesives for attaching wire network to photovoltaic cells |

| ITUD20110171A1 (it) * | 2011-10-24 | 2013-04-25 | Applied Materials Italia Srl | Metodo ed impianto di controllo in retroazione ad anello chiuso per la stampa di uno schema multistrato |

| US9120190B2 (en) | 2011-11-30 | 2015-09-01 | Palo Alto Research Center Incorporated | Co-extruded microchannel heat pipes |

| US10371468B2 (en) | 2011-11-30 | 2019-08-06 | Palo Alto Research Center Incorporated | Co-extruded microchannel heat pipes |

| US8875653B2 (en) | 2012-02-10 | 2014-11-04 | Palo Alto Research Center Incorporated | Micro-extrusion printhead with offset orifices for generating gridlines on non-square substrates |

| US10128391B2 (en) | 2016-06-22 | 2018-11-13 | Beijing Apollo Ding Rong Solar Technology Co., Ltd. | Photovoltaic module with flexible wire interconnection |

| US11271126B2 (en) | 2019-03-21 | 2022-03-08 | Beijing Apollo Ding Rong Solar Technology Co., Ltd. | Photovoltaic panels with folded panel edges and methods of forming the same |

| DE102019129349A1 (de) * | 2019-10-30 | 2021-05-06 | Heliatek Gmbh | Photovoltaisches Element mit verbesserter Effizienz bei Verschattung, und Verfahren zur Herstellung eines solchen photovoltaischen Elements |

| US12336305B1 (en) | 2023-10-13 | 2025-06-17 | Tandem PV | Photovoltaic cells with bypass diodes |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5664475A (en) * | 1979-08-23 | 1981-06-01 | Unisearch Ltd | Solar battery with branching diode |

| US4846896A (en) * | 1987-07-08 | 1989-07-11 | Mitsubishi Denki Kabushiki Kaisha | Solar cell with integral reverse voltage protection diode |

| JPH02135786A (ja) * | 1988-11-16 | 1990-05-24 | Mitsubishi Electric Corp | 太陽電池セル |

| JP2573083B2 (ja) | 1990-06-06 | 1997-01-16 | シャープ株式会社 | バイパスダイオード付太陽電池 |

| JP2593957B2 (ja) * | 1990-11-09 | 1997-03-26 | シャープ株式会社 | バイパスダイオード付太陽電池 |

| JP2837296B2 (ja) * | 1991-10-17 | 1998-12-14 | シャープ株式会社 | 太陽電池 |

| JP3193750B2 (ja) | 1991-11-29 | 2001-07-30 | シャープ株式会社 | 太陽電池モジュール |

| JP2855299B2 (ja) * | 1992-04-15 | 1999-02-10 | キヤノン株式会社 | 太陽電池モジュール |

| JP3032422B2 (ja) * | 1994-04-28 | 2000-04-17 | シャープ株式会社 | 太陽電池セルとその製造方法 |

| JP3331268B2 (ja) * | 1994-12-26 | 2002-10-07 | シャープ株式会社 | 太陽電池素子及びその製造方法 |

| JPH0964397A (ja) * | 1995-08-29 | 1997-03-07 | Canon Inc | 太陽電池および太陽電池モジュール |

-

1999

- 1999-06-03 JP JP15704099A patent/JP3754841B2/ja not_active Expired - Fee Related

- 1999-06-08 US US09/327,569 patent/US6184458B1/en not_active Expired - Lifetime

- 1999-06-10 EP EP99111326A patent/EP0971417A3/en not_active Withdrawn

Also Published As

| Publication number | Publication date |

|---|---|

| US6184458B1 (en) | 2001-02-06 |

| EP0971417A2 (en) | 2000-01-12 |

| JP2000068548A (ja) | 2000-03-03 |

| EP0971417A3 (en) | 2005-02-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3754841B2 (ja) | 光起電力素子およびその製造方法 | |

| US6613973B2 (en) | Photovoltaic element, producing method therefor, and solar cell modules | |

| EP0113434B2 (en) | Photovoltaic device | |

| JP2009529236A (ja) | 薄膜型太陽電池及びその製造方法 | |

| JP5410050B2 (ja) | 太陽電池モジュール | |

| JP5171490B2 (ja) | 集積型薄膜太陽電池 | |

| US20060260673A1 (en) | Photovoltaic element and method of producing photovoltaic element | |

| JP3323573B2 (ja) | 太陽電池モジュール及びその製造方法 | |

| CN86102164A (zh) | 增加有效面积的光电池 | |

| WO1992007386A1 (en) | Monolithic solar cell array and method for its manufacture | |

| JPH0577308B2 (ja) | ||

| JP3653800B2 (ja) | 集積化薄膜太陽電池の製造方法 | |

| CN113169241A (zh) | 光伏模组 | |

| US12484366B2 (en) | Solar cell, method for manufacturing the same, and solar cell module comprising the same | |

| JPH0563218A (ja) | 太陽電池及びその製造方法 | |

| JP4403654B2 (ja) | 薄膜太陽電池 | |

| JP3078936B2 (ja) | 太陽電池 | |

| WO2010026850A1 (ja) | 集積型薄膜太陽電池 | |

| JP3721620B2 (ja) | 並列型集積化太陽電池 | |

| JP2000150929A (ja) | 光起電力素子およびその製造方法 | |

| CN1241039A (zh) | 光伏元件及其制备方法 | |

| JPH0636429B2 (ja) | ヘテロ接合光電素子及びヘテロ接合光電装置 | |

| JP2000068534A (ja) | 光起電力素子およびその製造方法 | |

| CN115000191A (zh) | 一种新型氧化硅复合钝化层化合物异质结接触硅太阳电池 | |

| JP2001068696A (ja) | 薄膜光電変換モジュール |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050921 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051111 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20051207 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20051219 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20081222 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20091222 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20101222 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20111222 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20121222 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |