JP3663301B2 - ショットキーバリア半導体装置およびその製法 - Google Patents

ショットキーバリア半導体装置およびその製法 Download PDFInfo

- Publication number

- JP3663301B2 JP3663301B2 JP22845598A JP22845598A JP3663301B2 JP 3663301 B2 JP3663301 B2 JP 3663301B2 JP 22845598 A JP22845598 A JP 22845598A JP 22845598 A JP22845598 A JP 22845598A JP 3663301 B2 JP3663301 B2 JP 3663301B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- semiconductor

- region

- semiconductor layer

- schottky barrier

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は半導体基板上の動作層とする半導体層上にショットキーバリアを形成する金属層が設けられるショットキーバリア半導体装置およびその製法に関する。さらに詳しくは、リーク電流が少なく、かつ、順方向電圧の低いショットキーバリア半導体装置およびその製法に関する。

【0002】

【従来の技術】

ショットキーバリアダイオード(SBD)は、スイッチング特性が高速で、順方向損失が小さいため、高周波用の整流回路に広く用いられている。従来のSBDは、たとえば図6に断面説明図が示されるような構造になっている。すなわち、図6において、1はたとえばシリコンなどからなるn+ 形の半導体基板で、2は半導体基板1の上にエピタキシャル成長された、たとえばn- 形の動作層となる半導体層、3はモリブデン(Mo)などからなり、ショットキーバリアを形成する金属層、4は金属層3の外周近傍の半導体層2の表面側にp+ 形ドーパントが拡散されて、ショットキー接合の周辺部での耐圧を向上させるために形成されたガードリングである。5は半導体層2の表面に熱酸化法またはCVD法などにより形成された、たとえばSiO2 などからなる絶縁膜である。

【0003】

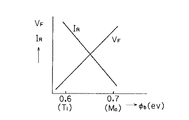

この金属層3と半導体層2とのショットキー接合により得られるSBDの順方向電圧VF や逆方向のリーク電流IR の特性は、金属材料と半導体層との固有の障壁値により、図7に示されるように変化する。この種のショットキー接合を得るための金属材料としては、取扱い易さ、経済性、信頼性などの点からTiやMoなどが実用的に用いられるが、それらの材料の障壁値に応じて、順方向電圧および逆方向のリーク電流が定まる。そして、順方向電圧と逆方向のリーク電流との間には相反関係があり、リーク電流が小さい材料は順方向電圧が高くなり、順方向電圧の低い材料は逆方向のリーク電流が大きくなり、リーク電流および順方向電圧の両方を共に低くすることができない。

【0004】

一方、特公昭59−35183号公報には、ショットキーバリア半導体装置の逆方向リーク電流を低くすることにより逆方向の耐圧を高くするため、図8に示されるような構造が開示されている。すなわち、図8において、1〜5は図6と同じ部分を示し、6は、動作層とするn- 形の半導体層2の表面に島状または短冊状に設けられるp+ 形の半導体領域で、半導体層2側に形成される空乏層により逆方向のリーク電流を減少させることにより耐圧を向上させる構造である。

【0005】

【発明が解決しようとする課題】

前述のように、従来のショットキーバリアを形成する実用的な金属材料を使用するショットキーバリア特性は、その材料に応じた順方向電圧およびリーク電流の特性を有しており、その相反特性を避けることができない。また、逆方向のリーク電流を低下させるため、前述の動作層とする半導体層の表面にその半導体層と異なる導電形(たとえばn形半導体層に対するp形領域)の半導体領域を形成すると、そのp形領域は動作領域にならないため、半導体層の動作領域の面積が小さくなる。面積が小さくなると、金属層と半導体基板の裏面に設けられる電極との間の直列抵抗が増大し、結局は順方向電圧が高くなるという問題がある。ショットキーバリア半導体装置は、その順方向電圧が低いことに特徴があるが、近年の電子機器の軽薄短小化および省電力で低電圧駆動化に伴い、チップ面積を大きくしないで、順方向電圧および逆方向リーク電流の両方をなお一層低下させた高性能のショットキーバリア半導体装置が要望されている。

【0006】

また、たとえば特公昭59−35183号公報にも示されるように、従来は逆方向耐圧を高くすることが課題の1つであり、逆方向の耐圧を高くするためには、p形の拡散領域の下端と半導体層2の下端との距離を大きくする必要がある。そのため、一層順方向の直列抵抗が大きくなり、順方向電圧が高くなるという問題がある。一方、近年ではショットキーバリア半導体装置もICなどと共に電源の2次側の低い電圧で使用されるケースが多くなり、逆方向耐圧もたとえば30V程度の数十Vを満たせばよい反面、前述のように、電子機器の省電力化、低電圧駆動化に伴って、より一層順方向電圧が低く、リーク電流の小さいショットキーバリア半導体装置が要望されている。

【0007】

本発明はこのような問題を解決するためになされたもので、逆方向のリーク電流を小さくしながら順方向電圧が低い、省電力で低電圧駆動が可能なショットキーバリア半導体装置およびその製法を提供することを目的とする。

【0008】

【課題を解決するための手段】

本発明によるショットキーバリア半導体装置は、高不純物濃度の第1導電形の半導体基板と、該半導体基板上にエピタキシャル成長される低不純物濃度の第1導電形の半導体層と、該半導体層の表面側に少なくとも2以上の領域に亘り隣接して設けられる第2導電形の半導体領域と、前記半導体層および前記第2導電形の半導体領域の表面に設けられるショットキーバリアを形成する金属層とからなり、前記第2導電形の半導体領域が形成されないで動作領域となる前記低不純物濃度の第1導電形の半導体層の厚さが、前記第2導電形の半導体領域の上面と前記半導体基板の上面との距離より小さくなるように形成され、かつ、前記隣接する第2導電形の半導体領域の間隔と、該第2導電形の半導体領域の底面および前記第1導電形の半導体層の底面の間隔との比が1:1〜2になるように前記第2導電形領域が形成されている。

【0009】

この構造にすることにより、動作層とする第1導電形の半導体層に第2導電形の半導体領域が形成されることにより、その空乏層により逆方向のリーク電流が阻止されてリーク電流を抑制することができ、動作領域となる低不純物濃度の半導体層はその厚さが薄くなって直列抵抗が減少し順方向電圧を低下させることができる。

【0010】

前記第2導電形の半導体領域が形成されないで動作領域となる第1導電形の半導体層の表面の一部が除去される構造にすれば、表面を選択的に酸化してエッチングしたり、直接選択的にエッチングすることにより、第1導電形の半導体層を簡単にしかも制御よく薄くすることができる。

【0011】

前記第2導電形の半導体領域が形成されないで動作領域となる第1導電形半導体層の前記半導体基板側に第1導電形の高不純物濃度の埋込領域が形成されることにより、さらに前記低不純物濃度の半導体層が薄くされることにより、より一層直列抵抗を下げることができて順方向電圧を低下させることに寄与する。

【0012】

本発明のショットキーバリア半導体装置の製法は、(a)高不純物濃度の第1導電形の半導体基板上に低不純物濃度の第1導電形の半導体層をエピタキシャル成長し、(b)該エピタキシャル成長された半導体層の動作領域の表面にマスクを形成して第2導電形の不純物を導入することにより、2以上の第2導電形の半導体領域を形成し、(c)該第2導電形の半導体領域の表面を被覆して前記第1導電形の半導体層を露出させる耐酸化性のマスクを、前記半導体層が設けられた基板の表面に形成して酸化することにより、前記第1導電形の半導体層の露出面を酸化し、(d)前記耐酸化性マスクおよび前記酸化により形成された酸化膜を除去し、(e)前記酸化膜の除去により露出する第1導電形の半導体層および前記第2導電形の半導体領域上にショットキーバリアを形成する金属層を設けるショットキーバリア半導体装置の製法であって、隣接する前記第2導電形の半導体領域の間隔と、該第2導電形の半導体領域の底面および前記第1導電形の半導体層の底面の間隔との比が1:1〜2になるように前記第2導電形の半導体領域を形成することを特徴とする。

【0013】

前記隣接する第2導電形の半導体領域の間隔と、該第2導電形の半導体領域の底面および前記第1導電形の半導体層の底面の間隔との比が1:1〜2になるように前記第2導電形の半導体領域を形成することことにより、リーク電流を防止する空乏層を最大限に設けると共に、第1導電形の半導体層が所望の耐圧に耐え得る最低限の厚さになり、より一層リーク電流を防止しながら直列抵抗を下げることができて順方向電圧を低下させることに寄与する。

【0014】

【発明の実施の形態】

つぎに、図面を参照しながら本発明のショットキーバリア半導体装置およびその製法について説明をする。

【0015】

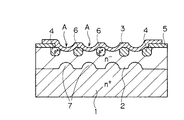

本発明のショットキーバリア半導体装置は、その一実施形態の断面説明図が図1(a)に示されるように、たとえばn+ 形である高不純物濃度の第1導電形の半導体基板1上にn- 形である低不純物濃度の第1導電形の半導体層2がエピタキシャル成長され、その半導体層2の表面側に少なくとも2以上の領域に亘り、p+ 形である第2導電形の半導体領域6が隣接して設けられ、半導体層2の動作領域の表面にショットキーバリアを形成する金属層3が設けられている。そして、前記隣接する第2導電形の半導体領域6が形成されないで動作領域となる低不純物濃度の第1導電形の半導体層2の厚さhが、第2導電形の半導体領域6の上面と半導体基板1の上面(半導体層2の底面)との距離gより小さくなるように形成されている。

【0016】

半導体基板1は、たとえば不純物濃度が1×1019cm-3程度のn+ 型のシリコンからなり、厚さがたとえば200〜250μm程度に形成されている。半導体基板1の上に設けられる半導体層2は、不純物濃度がたとえば1×1015cm-3程度のn- 型のシリコン半導体層で、たとえば4〜6.5μm程度の厚さにエピタキシャル成長されている。

【0017】

半導体層2の動作領域となる部分の外周部の表面にガードリング4とするp+ 形領域が1.5〜2μm程度の深さに設けられている。このガードリング4と同時に動作層とする半導体層2の表面に図1(b)に平面図が示されるように、p+ 形の半導体領域6がマトリクス状に形成されている(図では9個示されているが、実際には数百個程度形成される)。このp+ 形の半導体領域6は、マトリクス状でなくても短冊状でもよいが、マトリクス状に設けることにより、動作領域の面積の減少を最低限にしながら、動作領域における空乏層を最大限に広げることができるため好ましい。半導体領域6のの大きさは、たとえば2μm四方程度の大きさで、深さはガードリング4と同じ1.5〜2μm程度の深さに形成される。また、その間隔wは隣接する半導体領域6のpn接合の空乏層が接する程度の幅に形成され、たとえば空乏層の広がる幅が1.5μm程度であれば、2.5〜3.5μm程度に形成される。

【0018】

一方、p+ 形の半導体領域6の下層の半導体層2の厚さ(深さ)dは大きいほど耐圧を高くすることができるが、数十Vの耐圧が得られる程度の最低限の深さになるように形成されることが好ましい。具体的には、空乏層の広がり(1.5μm程度)の下側にさらに1〜3μm程度の厚さが確保されるように、2.5〜4.5μm程度になるように形成される。すなわち、p+ 形の半導体領域6の間隔wと、p+ 形の半導体領域6の下側の半導体層2の深さdとの比が1:1〜2程度になるように形成されることが好ましい。

【0019】

さらに、p+ 形の半導体領域6で挟まれる動作領域Aであるn- 型の半導体層2の表面は凹部14が形成されており、その表面と半導体基板1の上面との距離hは、p+ 形の半導体領域6の表面と半導体基板1の表面との距離gより1〜1.5μm程度小さくなっている。この凹部14は、たとえばp+ 形の半導体領域6の表面にチッ化シリコンなどの耐酸化性のマスクを形成して酸化させることによりn- 型の半導体層2の露出している表面側のみを酸化させ、その後にエッチングにより酸化膜を除去したり、マスクをして直接エッチングをすることもできる。酸化膜を形成してその酸化膜をエッチングすることが、オーバーエッチングの虞れもなく、正確な厚さで酸化膜を形成しやすく、凹部14の深さもコントロールしやすいため好ましい。

【0020】

金属層3は、半導体層とショットキーバリア(ショットキー接合)を形成するためのもので、p+ 形の半導体領域6が形成された半導体層2の動作領域Aの外周のガードリング4の一部より外側には絶縁膜5を形成しておき、動作領域Aの表面上に(p+ 形の半導体領域6も含めて)スパッタリング、真空蒸着などにより0.5〜1μm程度の厚さに形成されている。この金属層3としては、前述のようにその材料により障壁値が異なるが、たとえばチタン(Ti)またはモリブデン(Mo)などが用いられる。この金属層3の表面には、さらに銀(Ag)またはアルミニウム(Al)などの図示しないオーバーメタルがスパッタリング、真空蒸着などの方法により、1〜5μm程度の厚さに設けられ、金属層3と完全に電気的に接続されて電極パッドとされている。また、図示されていないが、半導体基板1の裏面にはNiやAuなどからなる電極が形成される。

【0021】

つぎに、図1に示されるショットキーバリア半導体装置の製法について図2を参照しながら説明をする。

【0022】

まず、図2(a)に示されるように、たとえば不純物濃度が1×1019cm-3程度のn+ 形半導体基板の表面に不純物濃度がたとえば1×1015cm-3程度のn- 型のシリコン半導体層を4〜6.5μm程度の厚さにエピタキシャル成長する。

【0023】

つぎに、図2(b)に示されるように、半導体層2の表面にCVD法などによりSiO2 などからなる絶縁膜を設け、第2導電形の半導体領域6を形成する部分のみを開口したマスク11を形成し、ボロン(B)などの不純物を導入して拡散することにより、p+ 形の半導体領域6をその深さが1.5〜2μm程度でその大きさが2μm角程度になるように形成する。

【0024】

ついで、マスク11を除去し、さらにチッ化シリコン膜などの耐酸化性絶縁膜を同様にCVD法などにより成膜し、前述のp+ 形の半導体領域6のみが被覆され、p+ 形の半導体領域6により挟まれるn- 形半導体層2が露出されるようにホトリソグラフィ技術によりパターニングすることにより、耐酸化性のマスク12を形成する。そして、酸化性雰囲気で1000〜1200℃程度で250〜350分程度の熱処理をすることにより、図2(c)に示されるように、1〜1.5μm程度の厚さの酸化膜13を形成する。

【0025】

ついで、図2(d)に示されるように、耐酸化性マスク12および前記酸化により形成された酸化膜13をフッ酸などのエッチング液により除去し、p+ 形の半導体領域6により挟まれるn- 形半導体層2の露出面に凹部14を形成する。

【0026】

その後、酸化膜の除去により露出するn- 形半導体層2およびp+ 形の半導体領域6の表面にショットキーバリアを形成する金属、たとえばTiまたはMoをスパッタリングにより0.5〜1μm程度の厚さに成膜してガードリング4の周囲まで覆われるようにパターニングをすることにより金属層3を形成することにより、図1に示されるショットキーバリアダイオードが得られる。その後、図示されていないが、表面側にさらにAgまたはAlなどのオーバーコート膜が設けられ、また半導体基板1の裏面にNiやAuなどからなる電極がそれぞれスパッタリングなどにより形成される。

【0027】

図1に示される構造のショットキーバリアダイオードの順方向電圧VF に対する順方向電流IF の関係を図4に、逆方向電圧VR に対するリーク電流IR の関係を図5に、それぞれ従来の図6に示される構造の特性Q1および図8に示される構造の特性Q2と対比して本発明の特性Pで示す。図4から明らかなように、順方向電圧については、従来の図8に示される構造の特性Q2が電流が多くなると順方向電圧も高くなるのに対して、本発明の特性Pは、電流が多くなっても順方向電圧の上昇はそれ程大きくならない。また、逆方向電圧に対するリーク電流の本発明の特性Pは、従来の図8に示される構造の特性Q2と殆ど差がなく、リーク電流に関しても高特性を維持していることが分る。

【0028】

本発明によれば、動作層とする第1導電形の半導体層の表面側に第2導電形の半導体領域6が複数個隣接して設けられているため、その間に形成される空乏層により、逆方向電圧に対するリーク電流を阻止することができ、逆方向のリーク電流を非常に小さくすることができる。一方、第2導電形の半導体領域6により挟まれる動作領域Aとなる第1導電形の半導体層2は、その表面がエッチングなどにより除去されて凹部14が形成されているため、図に示される構造の上下に設けられる電極間の抵抗の大きい半導体層2が薄くなり、直列抵抗が小さくなる。そのため、第2導電形の半導体領域6が設けられることにより、面積が小さくなって直列抵抗が増加してもその増加分を相殺して直列抵抗を小さくすることができる。その結果、リーク電流を小さくしながら順方向電圧を低くすることができるショットキーバリア半導体装置が得られる。

【0029】

また、前述の製法によれば、エッチングは酸化膜だけを選択的にエッチングすることができるため、オーバーエッチングの虞れがなく、また、n形層とp形層とでエッチングレートが異なっていてもそれに伴う段差が形成されず、滑らかな凹部14を形成することができる。しかも、酸化膜の厚さは酸化時間により精度よくコントロールすることができ、正確な深さの凹部14を簡単に形成することができる。

【0030】

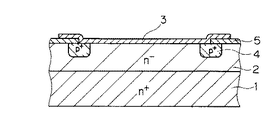

図3は、さらに順方向電圧を低くする他の実施形態の断面説明図である。すなわち、前述の図1に示される例で、第1導電形の半導体層の表面の凹部14を形成することにより、動作領域Aの半導体層の厚さを薄くし、それにより直列抵抗を低下させたが、図3に示される例は、動作領域の表面に凹部14を形成すると共に、さらに動作領域Aにおける半導体層2の半導体基板1側に、n+ 形である高不純物濃度の埋込領域7が形成されることにより、n- 形の半導体層2を動作領域Aのみで一層小さくしている。すなわち、動作領域Aの部分は、p+ 形の半導体領域6がなく、高不純物濃度の埋込領域7が設けられても、逆方向耐圧を低下させる要因はない。したがって、半導体層2をエピタキシャル成長する前に、半導体基板1のこの部分にn形不純物を導入しておき、半導体層2をエピタキシャル成長する際の拡散により、高さが1〜2μm程度の高不純物濃度の埋込領域7を形成することができる。その結果、図1の例よりさらに順方向電圧が低く、リーク電流の小さいショットキーバリア半導体装置が得られる。

【0031】

【発明の効果】

本発明によれば、動作層とする第1導電形の半導体層に、第2導電形の半導体領域が隣接して複数個設けられているため、その空乏層の広がりによりリーク電流を防止することができ、しかも、第2導電形の半導体領域を設けることによる動作領域の面積の減少に伴う抵抗の増加を第1導電形の半導体層の動作領域の厚さを薄くすることにより相殺しているため、直列抵抗を小さくすることができ、順方向電圧を低くすることができる。その結果、低い順方向電圧で、リーク電流も小さい高特性のショットキーバリア半導体装置が得られ、電子機器の軽薄短小化および省電力化に大きく寄与する。

【図面の簡単な説明】

【図1】本発明のショットキーバリア半導体装置の一実施形態の説明図である。

【図2】図1のショットキーバリア半導体装置の製造工程を示す断面説明図である。

【図3】本発明のショットキーバリア半導体装置の他の実施形態の断面説明図である。

【図4】図1のショットキーバリア半導体装置のVF −IF 特性を示す図である。

【図5】図1のショットキーバリア半導体装置のVR −IR 特性を示す図である。

【図6】従来のショットキーバリア半導体装置の断面説明図である。

【図7】半導体層と金属層との間の障壁値と順方向電圧VF および逆方向のリーク電流IR との関係図である。

【図8】従来のショットキーバリア半導体装置の他の構造の断面説明図である。

【符号の説明】

1 半導体基板

2 n- 形半導体層

3 金属層

6 p+ 形半導体領域

7 埋込領域

14 凹部

Claims (4)

- 高不純物濃度の第1導電形の半導体基板と、該半導体基板上にエピタキシャル成長される低不純物濃度の第1導電形の半導体層と、該半導体層の表面側に少なくとも2以上の領域に亘り隣接して設けられる第2導電形の半導体領域と、前記半導体層および前記第2導電形の半導体領域の表面に設けられるショットキーバリアを形成する金属層とからなり、前記第2導電形の半導体領域が形成されないで動作領域となる前記低不純物濃度の第1導電形の半導体層の厚さが、前記第2導電形の半導体領域の上面と前記半導体基板の上面との距離より小さくなるように形成され、かつ、前記隣接する第2導電形の半導体領域の間隔と、該第2導電形の半導体領域の底面および前記第1導電形の半導体層の底面の間隔との比が1:1〜2になるように前記第2導電形領域が形成されてなるショットキーバリア半導体装置。

- 前記第2導電形の半導体領域が形成されないで動作領域となる第1導電形の半導体層の表面の一部が除去されることにより、前記第1導電形の半導体層が薄くされてなる請求項1記載のショットキーバリア半導体装置。

- 前記第2導電形の半導体領域が形成されないで動作領域となる第1導電形半導体層の前記半導体基板側に第1導電形の高不純物濃度の埋込領域が形成されることにより、前記低不純物濃度の半導体層が薄くされてなる請求項2記載のショットキーバリア半導体装置。

- (a)高不純物濃度の第1導電形の半導体基板上に低不純物濃度の第1導電形の半導体層をエピタキシャル成長し、(b)該エピタキシャル成長された半導体層の動作領域の表面にマスクを形成して第2導電形の不純物を導入することにより、2以上の第2導電形の半導体領域を形成し、(c)該第2導電形の半導体領域の表面を被覆して前記第1導電形の半導体層を露出させる耐酸化性のマスクを、前記半導体層が設けられた基板の表面に形成して酸化することにより、前記第1導電形の半導体層の露出面を酸化し、(d)前記耐酸化性マスクおよび前記酸化により形成された酸化膜を除去し、(e)前記酸化膜の除去により露出する第1導電形の半導体層および前記第2導電形の半導体領域上にショットキーバリアを形成する金属層を設けるショットキーバリア半導体装置の製法であって、隣接する前記第2導電形の半導体領域の間隔と、該第2導電形の半導体領域の底面および前記第1導電形の半導体層の底面の間隔との比が1:1〜2になるように前記第2導電形の半導体領域を形成することを特徴とするショットキーバリア半導体装置の製法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22845598A JP3663301B2 (ja) | 1998-08-12 | 1998-08-12 | ショットキーバリア半導体装置およびその製法 |

| US09/368,897 US6307244B1 (en) | 1998-08-12 | 1999-08-06 | Schottky barrier semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP22845598A JP3663301B2 (ja) | 1998-08-12 | 1998-08-12 | ショットキーバリア半導体装置およびその製法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2000058874A JP2000058874A (ja) | 2000-02-25 |

| JP3663301B2 true JP3663301B2 (ja) | 2005-06-22 |

Family

ID=16876765

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP22845598A Expired - Fee Related JP3663301B2 (ja) | 1998-08-12 | 1998-08-12 | ショットキーバリア半導体装置およびその製法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3663301B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103646967A (zh) * | 2013-11-14 | 2014-03-19 | 中航(重庆)微电子有限公司 | 一种沟槽式肖特基二极管结构及其制备方法 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5047133B2 (ja) * | 2008-11-19 | 2012-10-10 | 昭和電工株式会社 | 半導体装置の製造方法 |

-

1998

- 1998-08-12 JP JP22845598A patent/JP3663301B2/ja not_active Expired - Fee Related

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103646967A (zh) * | 2013-11-14 | 2014-03-19 | 中航(重庆)微电子有限公司 | 一种沟槽式肖特基二极管结构及其制备方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2000058874A (ja) | 2000-02-25 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8143655B2 (en) | Trench schottky barrier diode with differential oxide thickness | |

| JP3287269B2 (ja) | ダイオードとその製造方法 | |

| US7078780B2 (en) | Schottky barrier diode and method of making the same | |

| JP2005532698A (ja) | トレンチ型ショットキ・バリア・ダイオード | |

| JP2004521480A (ja) | トレンチショットキー整流器 | |

| US6936905B2 (en) | Two mask shottky diode with locos structure | |

| JP3588256B2 (ja) | ショットキーバリアダイオード | |

| US6307244B1 (en) | Schottky barrier semiconductor device | |

| JP2012004197A (ja) | 半導体装置及びその製造方法 | |

| CN111129166B (zh) | 氧化镓基半导体结构及其制备方法 | |

| JP3663301B2 (ja) | ショットキーバリア半導体装置およびその製法 | |

| JP3581027B2 (ja) | ショットキーバリア半導体装置 | |

| JP3623687B2 (ja) | ショットキバリアダイオード及びその製造方法 | |

| TW202335308A (zh) | 寬能隙半導體元件與其製造方法 | |

| JP3625380B2 (ja) | ショットキーバリア半導体装置およびその製法 | |

| JP2000312013A (ja) | ショットキーバリア半導体装置 | |

| JPH11145155A (ja) | 半絶縁ポリシリコン(sipos)膜を用いた電力半導体装置の製造方法 | |

| JPH0864845A (ja) | ショットキーバリアダイオードおよびその製造方法 | |

| JP2003282864A (ja) | ショットキーバリアダイオードの製造方法 | |

| JPH04365378A (ja) | 半導体集積回路 | |

| JP2547468B2 (ja) | 半導体装置およびその製造方法 | |

| JPH10125937A (ja) | ショットキーバリア半導体装置 | |

| JP2000022177A (ja) | ショットキーバリアダイオード | |

| JPH0464458B2 (ja) | ||

| JPH10117002A (ja) | ショットキーバリア半導体装置およびその製法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20031216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040706 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040803 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041004 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041116 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050117 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050308 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050328 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |