JP3655247B2 - 同期整流回路及び電源装置 - Google Patents

同期整流回路及び電源装置 Download PDFInfo

- Publication number

- JP3655247B2 JP3655247B2 JP2002040918A JP2002040918A JP3655247B2 JP 3655247 B2 JP3655247 B2 JP 3655247B2 JP 2002040918 A JP2002040918 A JP 2002040918A JP 2002040918 A JP2002040918 A JP 2002040918A JP 3655247 B2 JP3655247 B2 JP 3655247B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- mosfet

- power supply

- switch element

- semiconductor switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Description

【発明の属する技術分野】

本発明は、電源装置に係り、特に、電子機器等に用いる同期整流回路及び電源装置に関する。

【0002】

【従来の技術】

従来技術の電子機器等に用いる電源装置として、図16に示す電源装置が知られている。図16に示す電源装置では、直流入力電源60から入力コンデンサ61を備えた入力部51に入力した直流電力を駆動部70が出力する制御信号に基づいてスイッチング部52でスイッチングし、ダイオード63や出力フィルタ55を備えた出力部53から負荷66に電力を供給する。また、負荷66へ出力した電圧や電流を検出部67で検出し、この検出値と設定部68で設定した負荷66の制御目標値とを比較演算部69で比較して、駆動部70から比較結果に基づいた制御信号をスイッチング部52に出力する。このようにして負荷に供給される電力が制御目標値と一致するように制御する。

【0003】

このような従来技術の電源装置の具体的な回路構成を図17に示す。図17に示すように、スイッチング部52は、能動素子(例えばトランジスタやMOSFET等)62で構成されている。出力部53は、ダイオード63と、チョークコイル64及びコンデンサ65で構成された出力フィルタ55とで構成されている。制御部54は、比較演算部69,設定部68,駆動部70で構成されている。さらに、制御部54は図示しない発振回路を備えており、駆動部70からパルス信号を能動素子62に出力する。これにより能動素子62に印加される直流入力電源60からの直流電圧Vinがスイッチングされる。

【0004】

能動素子62がオンの場合には、直流電力はチョークコイル64及びコンデンサ65にチャージされると共に負荷66へ供給される。能動素子62がオフの場合は、チョークコイル64及びコンデンサ65にチャージされていたエネルギーがダイオード63を介して負荷66に供給される。

【0005】

このとき、制御部54では、比較演算部69において検出部67で検出した出力電圧Voをモニタし、これと設定部68で設定された制御目標値と比較し、駆動部70から比較結果に基づいた制御信号をスイッチング部52に出力する。これにより能動素子62がオンオフ制御され、負荷に供給される電力が制御目標値と一致するように制御される。このときの出力電圧V0は次の(数1)式で示される。

【0006】

V0=VIN×(TON/T) …(数1)

(数1)式中、VINは入力直流電圧、Tは駆動部70が出力するパルス信号の周期、TONは周期Tのうち能動素子62が導通の時間を示す。すなわち、TON/Tはデューティ比を示す。

【0007】

別の従来技術として、図19に示す転流側にMOSFET3を使用した同期整流方式の電源装置がある。この従来技術は図20に示すように、ダイオードの電流−電圧特性が非線形性であるのに対し、MOSFETの電流−電圧特性がゲート電圧によっては線形性になり、電圧降下がダイオードより小さいことを利用している。

【0008】

この図19に示す電源装置は、スイッチング用のMOSFET2を備え、このMOSFET2のゲート端子に、制御回路8から制御信号を入力する。MOSFET2が導通状態の場合は、入力電力はチョークコイル4を通ってコンデンサ5に充電されると共に負荷6に供給される。次にMOSFET2が非導通状態になると、チョークコイル4に蓄えられていた磁気エネルギーが放出され、コンデンサ5及び負荷6を経由して転流電流が検出抵抗7,寄生ダイオード3Aを流れる。このとき、検出抵抗7により電圧降下が生じるが、この電圧降下を検出電圧として比較器80で基準電圧電源82から出力される基準電圧Vrefと比較する。そして、検出電圧が基準電圧よりも高い場合には比較器80はハイレベルを出力し、駆動回路81を介してMOSFET3を導通させる。

【0009】

さらに別の従来技術が実開平6−44396号公報に開示されていて、ダイオードに生じる電力損失PDが大きくなる問題を解決するため、MOSFETを並列に接続してオン抵抗を1/2にする。これを図22に示す。

【0010】

また特開2001−161072号公報に、出力電流により、並列接続した

MOSFETのうち、オンになるMOSFET数を段階的に変える従来技術が開示されている。これを図24に示す。図24に示す同期整流回路は、基準電圧電源82,122の電圧に応じて少なくとも1つを選択して駆動する。Vref1<Vref2のとき、複数のスイッチ素子が全て同一特性、すなわち流せる電流の大きさが同じ場合において、検出値が小さいとき、すなわち軽負荷時には1つのスイッチング素子MOSFET3を駆動し、検出値が大きくなる、すなわち重負荷になるに従って駆動するスイッチング素子を増やすことができる。このため、軽負荷時には1つのスイッチング素子のみを駆動することにより、無駄な駆動電力の消費を防ぎ、重負荷時には複数のスイッチング素子を駆動することによりスイッチ素子1個当たりの損失を小さくできる。従って軽負荷時から重負荷時に亘って、電源効率を向上できる。

【0011】

【発明が解決しようとする課題】

前記図16に示した従来技術の出力部53の転流側には、図17に示すように受動素子であるダイオード63を使用するのが通常である。ダイオード63は、図18に示すような電流−電圧特性を有しており、電流がある所定値以上になると、順方向電圧が飽和状態になる。この飽和電圧は、高速ダイオードにおいては0.9V〜1.3V、ショットキーダイオードでは0.45V〜0.55V程度となっている。このように、ダイオード63の順方向電圧が飽和することにより電力損失が生じ、電源変換効率を悪化させる問題があった。さらに、電力損失が大きく素子のジャンクション温度が上昇するため、出力電流を大きくする程、ダイオード63を多くし、2個や3個等を並列接続し、1素子当たりの電力損失を分散させ、ジャンクション温度を抑制する必要がある。

【0012】

また、前記図19に示す電源回路の変換効率(出力電圧/入力電圧)ηは図

21に示す如く、出力電流Ioの増加と共に低下する。これは、下記(数2)式に示すMOSFETの電力損失PFETがオン抵抗Ron一定の下、ドレイン電流IDの2乗の比例して増加するためである。

【0013】

PFET=Ron×ID2=(Ron×ID)×ID …(数2)

さらに、MOSFETの電圧降下(Ron×ID)とダイオードの電圧降下

VFとを比較すると、Ron×ID<VFとなるのが一般的である。従って、出力電流が大きくなるほど下記(数3)式に示すダイオードに生じる電力損失PDが大きくなる。

【0014】

PD=VF×I …(数3)

また、前記図22に示す電源装置では、2個のMOSFETを常に同時に駆動するため、駆動電力が2倍必要となり、図23に示すように定格出力時の効率を改善できても、軽負荷時の損失が相対的に増加し、効率が低下する問題がある。

【0015】

本発明は、軽負荷時から重負荷時に亘って、連続的な制御ができ、さらにチップ数の増加がないため、ピンに伴う寄生容量や実装面積の増加がない電源装置を提供することを目的とする。

【0016】

【課題を解決するための手段】

本発明は、上記目的を達成するために、出力側から戻る戻り電流を同期整流するスイッチ素子と、前記のスイッチ素子と直列に接続すると共に前記戻り電流を検出する検出手段とを含む同期整流回路であって、前記検出手段の検出値に応じて前記のスイッチ素子のゲート電圧を変えて駆動する駆動手段を備えた。

【0017】

同期整流回路は、例えば入力電力をスイッチングし、入力電力がオンのときに入力電力を蓄えながら負荷へ出力し、入力電力がオフのときには蓄えた電力を負荷へ出力するような電源装置に用いられる。同期整流回路は、例えば出力側、すなわち負荷側から戻る戻り電流、すなわち、例えば入力電力がオンの際に流れる整流電流や入力電力がオフのときに流れる転流電流を同期整流するスイッチ素子を備えている。このスイッチ素子は制御信号に基づいて制御され、例えば制御信号がハイレベルの場合にオンにし、ローレベルの場合はオフにする。

【0018】

また、前記のスイッチ素子は、検出手段と直列に接続している。従って、例えば制御信号によりスイッチ素子がオンされた場合には検出手段を流れる電流が該スイッチ素子にも流れ、制御信号によりスイッチ素子がオフされた場合には検出手段を流れる電流は該スイッチ素子には流れない。このスイッチ素子には、ユニポーラトランジスタ、例えばMOSFETやバイポーラトランジスタや、IGBTを用いることができる。

【0019】

検出手段は、スイッチ素子と直列に接続しており、出力側からの戻り電流、すなわち整流電流又は転流電流を検出する。この検出手段は、例えば抵抗を用いることができる。電流がこの検出手段を流れることにより、流れた電流に応じた電圧を検出できる。

【0020】

このような同期整流回路において、駆動手段は、検出手段の検出値に応じてスイッチ素子を駆動する。検出値が小さい場合、すなわち軽負荷時にはゲート電圧を低くし、検出値が大きくなるに従って、すなわち重負荷になるに従ってゲート電圧を高くする。このため、軽負荷時にはゲート電圧が低いので、ゲートの充放電損失が低減し、重負荷時にはゲート電圧を高くして、スイッチ素子のオン抵抗を低減し、損失を小さくする。従って、軽負荷時から重負荷時に亘って電源効率を向上できる。

【0021】

【発明の実施の形態】

以下、本願発明の実施例を図面を用いて詳しく説明する。

【0022】

(実施例1)

以下、図面を参照して本実施例を説明する。図1に本実施例に係る電源装置を示す。図1に示すように、電源装置はPチャンネルのMOSFET2を備え、MOSFET2のソース端子に電源側端子が接続し、電源側端子に入力電圧Vinを印加する。MOSFET2のドレイン端子はチョークコイル4の一端とNチャンネルのMOSFET3のドレイン端子とに接続している。チョークコイル4の他端は、コンデンサ(例えば電解コンデンサ)5の一端と負荷6とに接続し、コンデンサ5の他端はGND(接地)端子に接続している。MOSFET3のソース端子は検出抵抗7の一端に接続し、検出抵抗7の他端が、GNDに接続している。検出抵抗7の両端の電圧差をDC−DCコンバータ9に入力し、MOSFET3のゲート電圧を制御する。なお、MOSFET3は、その特性により寄生ダイオード3Aを備えている。

【0023】

次に、本実施例1の動作を説明する。まず、制御回路8が出力する制御信号でMOSFET2が導通(オン)するとドレイン電流IDが流れ、該ドレイン電流IDがチョークコイル4を介してコンデンサ5を充電しながら負荷6へ出力される。

【0024】

次に、MOSFET2が非導通(オフ)になると、チョークコイル4に蓄積されていたエネルギーがコンデンサ5,負荷6を経由して検出抵抗7,MOSFET3の寄生ダイオード3Aを転流電流ISとして流れる。このとき、検出抵抗7の抵抗値R1と転流電流ISとの積とによる電圧降下、検出電圧VS1(=(R1×IS))により、MOSFET3のゲート電圧を変える。転流電流ISが小さい時、すなわち軽負荷時にはMOSFET3のゲート電圧を低くし、転流電流ISが大きくなった時には、ゲート電圧を高くする。ここで、MOSFET3を駆動したときに生じる損失P1は下記(数4)式で計算できる。

【0025】

P1=Ron×(ID1)2+Pdr …(数4)

(数4)式中、ID1はMOSFET3に流れるドレイン電流の実効値、RonはMOSFET3のオン抵抗、Pdrはドライブ電力を示す。ゲート電圧を高くした場合、オン抵抗Ronは低下し、導通損失は低下する。一方、ゲートの充放電損失は増加する。よって、導通損失の低下>ゲート充放電損失の増加を満たす場合、電源効率は向上する。

【0026】

図2に各部の電圧及び電流波形を示す。図2(C),(D),(E)に示すように、電流値が小さいとき、すなわち軽負荷時には下アームMOSのゲート電圧を低くし、電流値が大きいとき、すなわち重負荷時にはゲート電圧を高くする。

【0027】

このように、軽負荷時にゲート電圧を低くすることで、損失を低減できる理由を述べる。軽負荷時の主要な損失成分は、ゲート充放電損失Pdrであるので、ゲート電圧を低くすることで、(4)式のオン抵抗Ronは高くなるが、ゲート充放電損失Pdrを低減できる。ここで、MOSFET3のゲート充放電損失

Pdrは、下記(数5)式の如く計算できる。

【0028】

Pdr=Cg×Vg2×f …(数5)

(数5)式中、Cgはゲート容量、Vgはゲート電圧、fはスイッチング周波数である。

【0029】

次に、重負荷時に、ゲート電圧を高くすることで、損失を低減できる理由を述べる。重負荷時の主要な損失成分は、MOSFET3の導通損失、すなわち、

(数4)式のRon×(ID1)2の項である。ゲート電圧を高くすると、(数5)式に示すようにゲート充放電損失Pdrは大きくなるが、オン抵抗Ronが小さくなるので、全体の損失は小さくなる。したがって、図3に示すように、電流値が大きくなるとともに、ゲート電圧を高くすることにより、軽負荷時から重負荷時に亘って損失を低減でき、ゲート電圧一定で駆動した場合と比べて、電源効率を向上できる。

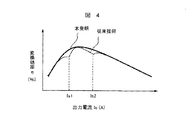

【0030】

図4は、本実施例と、特開2001−161072号公報(図24)に開示の従来技術とを比較したものである。従来技術では、並列接続したMOSFETのうち、オンになるMOSFETの数を段階的に変えるので、切り替えの際に効率が低下し、グラフに窪みができる。出力電流値が大きくなった場合に、オンになるMOSFET数を増やす「しきい電流」を図4に示すように、小さい順に、

Is1,Is2とする。図4に示すように従来技術では、このしきい電流付近で効率が低下する。電流値が大きくなるに従い、オンになるMOSFET数を増やすという従来技術では、制御が段階状になるので、MOSFET数を切り換える際の効率低下を避けることができない。

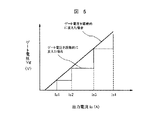

【0031】

一方、本実施例では、ゲート電圧を可変にするので、連続的な制御が可能となり、軽負荷から重負荷まで、高効率を達成できる。本実施例では、電流値に応じて、ゲート電圧を連続的に変えることが望ましいが、ゲート電圧をゼロから段階的に変えても、同様に高い効率を達成できる。図5に示すように、MOSFETに流れる電流がIs1,Is2,Is3,Is4のとき、ゲート電圧をゼロから段階的に高くする。この方法は検出抵抗7の両端の電圧を、DC−DCコンバータ9内で複数の基準電圧と比較して、ゲート電圧を出力する場合に相当する。

【0032】

図6は、ゲート電圧を段階的に切り換えた電源装置である。図6の電源装置は、スイッチング用のMOSFET2を備え、このMOSFET2のゲート端子には、制御回路8から制御信号が入力される。MOSFET2が導通状態の場合は、入力電力はチョークコイル4を通ってコンデンサ5を充電すると共に負荷6に供給される。次にMOSFET2が非導通状態になると、チョークコイル4に蓄えていた磁気エネルギーを放出し、コンデンサ5及び負荷6を経由して転流電流が検出抵抗7,寄生ダイオード3Aに流れる。このとき、検出抵抗7で電圧降下を生じるが、この電圧降下を検出電圧として、比較器80,120で、基準電圧電源82,122が出力する基準電圧Vref1,Vref2とそれぞれ比較する。そして、検出電圧が基準電圧よりも高い場合には比較器80はハイレベルを出力し、駆動回路81,121を介してMOSFET111,112を導通させる。Vref1とVref2には、Vref1<Vref2の関係があるため、低い電流値でMOSFET112がオンになる。MOSFET112のドレイン端子には直流電源115のVdd1が接続し、ソース端子にはダイオード113を介して、増幅器123の電源端子に接続する。Vdd1はMOSFET3を駆動する電源となる。MOSFET3を流れる電流が増加し、検出抵抗7の電圧降下がさらに大きくなると、Vref2以上になり、MOSFET111がオンになる。この場合、MOSFET3を駆動する電源は直流電源114のVdd2となる。但し、Vdd2>Vdd1の関係があり、ダイオード113はMOSFET111がオンになったときに、Vdd1→MOSFET111→MOSFET112→Vdd2の経路で短絡電流が流れないように挿入する。以上述べたように、電流値に応じて、段階的にゲート電圧を切り換える場合は、MOSFET3,10のゲートドライブ回路が簡易になる。

【0033】

実施例1では、MOSFET3に流れる電流を検出する手段として、検出抵抗7を用いたが、MOSFET3のソース,ドレイン間の電圧を検出し、この電圧に応じてMOSFET3のゲート電圧を制御しても良い。MOSFET3のソース,ドレイン間の電圧を検出すれば、電流検出に伴う損失が無いため、効率が向上する。

【0034】

ゲート電圧を、電流値により可変とする方法は、図1の下アームMOSFET3だけでなく、上アームMOSFET2に対しても有効である。図7は上アームと下アームMOSFETのゲート電圧とを可変とした場合の電圧,電流波形である。図7(C),(D)に示すように、MOSFET2およびMOSFET3のドレイン電流が大きくなるに従い、図7(A),(B)に示すようにMOSFET2と

MOSFET3のゲート電圧を高くする。このようにして、下アームMOSFET3だけでなく、上アームMOSFET2の損失も低減できるので、電源効率が向上する。

【0035】

(実施例2)

次に、図8を用いて本実施例を説明する。実施例1と異なる点は、上アーム

MOSFET10がNチャンネルという点である。図8で、MOSFET10がオンのとき、MOSFET10のソース電位は、直流入力電源1の電圧となるので、ゲートには、「入力電源電圧+ゲート電圧」の大きさの電圧を印加する必要があり、制御回路8にはトランスやブートストラップコンデンサなどを用いる。ただし、NチャンネルのMOSFET10はPチャンネルのMOSFET2と比べ、オン抵抗RONが小さいので導通損失が小さく、より電源効率が向上できる。

【0036】

(実施例3)

次に、本実施例を図9を用いて説明する。実施例1と異なる点は、下アーム

MOSFET3と並列にショットキーダイオード18を挿入した点である。図2(E)に示すように、上アームMOSFET2がオフになってから、下アーム

MOSFET3がオンになるまで、上および下アームMOSがともにオフする期間、いわゆるデッドタイムを設ける。デッドタイム中は、下アームMOSFET3の寄生ダイオード3Aに電流が流れる。デッドタイムを設ける理由は、上および下アームMOSFETが同時にオンになる直流入力電源1,上アームMOSFET2,下アームMOSFET3の経路で、大きな貫通電流が流れ損失を発生し、最悪の場合、発熱のためMOSFETが破壊することを防止するためである。ショットキーダイオード18の順方向飽和電圧は寄生ダイオード3Aより小さいため転流電流による損失を低減でき、電源効率を向上できる。

【0037】

(実施例4)

図10を用いて本実施例を説明する。本実施例ではトランスの1次側のスイッチング素子がオンのときチョークコイルにエネルギーを蓄えながら出力し、スイッチング素子がオフのときに、チョークコイルに蓄えたエネルギーを放出するいわゆるフォワード型の電源装置である。

【0038】

本実施例の電源装置は、トランス11を備えている。トランス11の1次巻線11Aの一端は、直流入力電源1のプラス側が接続し、他端はMOSFET12のドレイン端子が接続している。MOSFET12のゲート端子は制御回路8が接続しており、ソース端子は直流入力電源1のマイナス側に接続している。

MOSFET12のゲート端子に制御回路8により制御信号を入力してトランス11の1次巻線11Aに印加される直流電圧をスイッチングする。これにより、トランス11の2次巻線11B側に、交流電圧が誘起される。

【0039】

2次巻線11Bの一端は、MOSFET13のドレインとチョークコイル4の一端に接続しており、2次巻線11Bの他端はMOSFET14のドレインに接続している。チョークコイル4の他端はコンデンサ5の一端と、負荷6の一端とに接続し、コンデンサ5の他端、および負荷6の他端はMOSFET13およびMOSFET14に直列に接続した検出抵抗7に接続している。

【0040】

次に、本実施例の動作を説明する。制御回路8から、MOSFET12のゲート端子に、所定周期でオンオフを繰り返す制御信号を出力する。そして、MOSFET12がオンになるとドレイン電流IDがトランス11の1次巻線11Aを流れ、2次巻線11Bに電圧が誘起される。この誘起された電圧による電流がチョークコイル4に蓄積されながらコンデンサ5により平滑されて出力電流Ioとして負荷側へ流れる。また、負荷側から整流電流I1がMOSFET14とその寄生ダイオード14Aとを流れる。

【0041】

次に、MOSFET12がオフになると、チョークコイル4に蓄積されたエネルギーがコンデンサ5,負荷6を経由して転流電流I2としてMOSFET13とその寄生ダイオード13Aとを流れる。

【0042】

整流時には、MOSFET14の検出抵抗7の抵抗値Rsと整流電流I1との積による電圧降下、すなわち検出電圧VS(=Rs×I1)により、MOSFET14をドライブするゲート電圧を制御する。軽負荷時はゲート電圧を低くし、重負荷時はゲート電圧を高くする。転流時についても、同様にMOSFET13に直列接続した検出抵抗7の両端の電圧に応じて、ゲート電圧を制御する。

【0043】

図11に本実施例の各素子の電圧,電流波形を示す。検出抵抗7の電流値により、MOSFET13とMOSFET14とのゲート電圧を変えることで、電源効率を向上できる。図18では2次側のMOSFET13,14のみゲート電圧を可変としたが、1次側のMOSFET12も、1次側に電流検出抵抗を配置し、検出した電流値に応じてゲート電圧を同様に可変とすればさらに電源効率が上がる。

【0044】

(実施例5)

図12を用いて本実施例を説明する。本実施例は、トランスの1次側のスイッチング素子がオンのときにトランスにエネルギーを蓄え、スイッチング素子がオフのときに出力側へ電力を送る所謂フライバック型の電源装置である。なお、図12の符号は図10の電源装置と同一部分については同一符号を付す。

【0045】

図12に示す電源装置が図10に示す電源装置と異なる点は、トランス11の1次巻線11Aと2次巻線11Bとの極性が異なる点、チョークコイル4と転流用のMOSFETが無い点である。すなわち、図12に示す電源装置は、MOSFET12がオンのときにトランス11にエネルギーを蓄え、MOSFET12がオフのときに出力側へ電力を送る。

【0046】

次に、本実施例の電源装置の動作を説明する。制御回路8からMOSFET12のゲート端子に所定周期でオンオフを繰り返す制御信号を出力する。MOSFET12がオンになるとドレイン電流IDがトランス11の1次巻線11Aを流れ、2次巻線11Bに電圧が誘起される。次にMOSFET12がオフになると、2次巻線11Bに蓄積されたエネルギーがコンデンサ5により平滑されて出力電流Ioとして負荷側へ出力される。また、負荷側から整流電流I1がMOSFET15とその寄生ダイオード15Aとを流れる。

【0047】

整流時には、MOSFET14の検出抵抗7の抵抗値Rsと整流電流I1との積による電圧降下、すなわち検出電圧VS(=Rs×I1)により、MOSFET14をドライブするゲート電圧を選択する。軽負荷時はゲート電圧を低くし、重負荷時はゲート電圧を高くする。

【0048】

図13に各素子の電圧,電流波形を示す。検出抵抗7の電流値により、MOSFET15のゲート電圧を変えて、電源効率が向上する。

【0049】

(実施例6)

図14を用いて本実施例を説明する。本実施例は、トランスの1次側に複数のスイッチング素子を備え、これらのスイッチング素子を所定のタイミングで交互にオンオフさせることによりトランスの使用効率を高めることができる所謂多石方式(ハーフブリッジ方式)の電源装置である。なお、図14で、図10に示す電源装置と同一部分については同一符号を付す。

【0050】

図14に示すように本実施例の電源装置は、1次巻線11Aと、中点(センタータップ)を設けた2次巻線11B,11Cとを具備したトランス11を備えている。トランス11の1次巻線11Aの一端は、MOSFET103のソース端子及びMOSFET104のドレイン端子が接続している。MOSFET103のドレイン端子は直流入力電源1のプラス側及びコンデンサ101の一端に接続している。コンデンサ101の他端は1次巻線11Aの他端とコンデンサ102の一端とに接続している。コンデンサ102の他端はMOSFET104のソース端子に接続すると共に接地している。

【0051】

MOSFET103,104のゲート端子は制御回路8が接続している。制御回路8は、MOSFET103,104を所定のタイミングで交互にオンオフさせる制御信号を出力する。これにより、トランス11の1次巻線11Aに極性が異なる電圧が交互に印加される。すなわち、1次巻線11A側の回路は、所謂ハーフブリッジ型のインバータ回路となっている。

【0052】

2次巻線11Bと11C接続点である中点は、チョークコイル4の一端に接続しており、チョークコイル4の他端は負荷6及びコンデンサ5の一端に接続している。コンデンサ5の他端はMOSFET16および17に直列に接続した検出抵抗7に接続する。

【0053】

次に、本実施例動作を説明する。まず、制御回路8からMOSFET103,104のゲート端子に所定の制御信号、すなわちMOSFET103,104を所定周期で交互にオンオフさせる制御信号を出力する。MOSFET103がオンになると、直流入力電源1→MOSFET103→トランス11の1次巻線11A→コンデンサ102の経路で電流が流れ、MOSFET104がオンになると、直流入力電源1→コンデンサ101→トランス11の1次巻線11A→MOSFET104の経路で電流が流れる。

【0054】

従って、1次巻線11Aに流れる電流の向き(1次巻線11Aに印加される電圧の向き)は、MOSFET103がオンの場合とMOSFET104がオンの場合とで逆向きとなる。この1次側電流IDは、トランス11のインダクタンスのために次第に増加する波形となる。

【0055】

これにより、トランス11の1次巻線11Aには、一定のオフ期間Toffを挟んで、極性の異なる電圧(一次側トランス電圧Vp)が交互に印加されて互いに逆向きの電流が交互に流れる。トランス11の1次巻線11Aに上記のように電圧が印加されると、2次巻線11B,11Cに2次側巻線電圧が発生する。

【0056】

MOSFET103がオンのときには、図14のトランス11の2次巻線11Bの中点→チョークコイル4→コンデンサ5及び負荷6→MOSFET16、およびその寄生ダイオード16Aの経路で電流I1が流れる。

【0057】

一方、MOSFET104がオンのときには、図14で、トランス11の2次巻線11Bの中点→チョークコイル4→コンデンサ5及び負荷6→MOSFET17、およびその寄生ダイオード17Aの経路で電流I2が流れる。

【0058】

なお、MOSFET103,104が共にオフの時には、トランス11の2次巻線11B,11Cに電圧が誘起されないため、チョークコイル4に蓄えたエネルギーにより、チョークコイル4→コンデンサ5及び負荷6→MOSFET16,17→2次巻線11B,11Cの中点の経路で電流I1,I2が同時に各々流れる。

【0059】

MOSFET103がオンの時には、MOSFET16の検出抵抗7の抵抗値Rs、と整流電流I1との積による電圧降下、すなわち検出電圧VS(=Rs×I1)により、ゲート電圧値を制御する。具体的には、MOSFET16に流れる電流が小さい場合、すなわち軽負荷時には、MOSFET16のゲート電圧を低くし、MOSFET16に流れる電流が大きい場合、すなわち重負荷時には、MOSFET16のゲート電圧を高くする。軽負荷時、および重負荷時の各素子の電圧,電流波形を図15に示す。検出抵抗7の電流値により、MOSFET16および17のゲート電圧を変えて、電源効率を向上できる。

【0060】

【発明の効果】

以上説明したように、本発明によれば、出力電流検出手段の検出値に応じて、半導体スイッチング素子をドライブする電圧を可変にしたので、軽負荷から重負荷にかけて、電源効率を向上できる。

【図面の簡単な説明】

【図1】実施例1の電源装置の概略構成図である。

【図2】実施例1における各部の電流及び電圧の波形図である。

【図3】実施例1の出力電流と電源効率との関係の説明図である。

【図4】実施例1と従来技術の出力電流と電源効率との関係を示す図である。

【図5】実施例1の出力電流とゲート電圧との関係を示す図である。

【図6】実施例1のべつの電源装置の概略構成図である。

【図7】実施例1の各部の電流及び電圧の波形図である。

【図8】実施例2の電源装置の概略構成図である。

【図9】実施例3の電源装置の概略構成図である。

【図10】実施例4の電源装置の概略構成図である。

【図11】実施例4の各部の電流及び電圧の波形図である。

【図12】実施例5の電源装置の概略構成図である。

【図13】実施例5における各部の電流及び電圧の波形図である。

【図14】実施例6の電源装置の概略構成図である。

【図15】実施例6における各部の電流及び電圧の波形図である。

【図16】従来技術の電源装置の概略構成図である。

【図17】従来技術の電源装置の回路構成図である。

【図18】ダイオードの電圧降下と電流の関係の説明図である。

【図19】従来技術の電源装置の概略構成図である。

【図20】ダイオードとMOSFETの電圧降下と電流の関係の説明図である。

【図21】従来技術の電源装置の出力電流と電源効率との関係の説明図である。

【図22】従来技術の電源装置の概略構成図である。

【図23】従来技術の出力電流と電源効率との関係の説明図である。

【図24】従来技術の電源装置の概略構成図である。

【符号の説明】

1…直流入力電源、2,3,10,12,13,14,15,16,17,

103,104,111,112…MOSFET、3A,12A,13A,14A,15A,16A,17A…寄生ダイオード、4,64…チョークコイル、5,65,101,102…コンデンサ、6…負荷、7…検出抵抗、8…制御回路、9…DC−DCコンバータ、11…トランス、11A…1次巻線、11B,11C…2次巻線、18…ショットキーダイオード、21…AD変換器、51…入力部、52…スイッチング部、53…出力部、54…制御部、55…出力フィルタ、60…直流入力電源、61…入力コンデンサ、62…能動素子、63,113…ダイオード、66…負荷、67…検出部、68…設定部、69…比較演算部、70…駆動部、80,120…比較器、81,121…駆動回路、82,122…基準電圧電源、114,115…直流電源、123…増幅器。

Claims (7)

- 出力側から戻る戻り電流を同期整流する半導体スイッチ素子と、戻り電流を検出する検出手段と、前記半導体スイッチ素子の制御端子に加える駆動電圧を発生する手段とを具備した同期整流回路において、

前記検出手段が、前記半導体スイッチ素子に直列に接続した抵抗と、該抵抗の両端の電位差を検出するものであって、

前記検出手段の検出値が大きくなるに従って、前記駆動電圧を発生する手段が、前記半導体スイッチ素子の制御端子駆動電圧を連続的に変化あるいは多段階に変化させて、制御端子駆動電圧を高くすることを特徴とする同期整流回路。 - 請求項1に記載の同期整流回路において、前記半導体スイッチ素子がMOSFETであって、前記検出手段が前記直列に接続した抵抗に代えて、前記MOSFETのソースとドレインとの間の電圧を検出することを特徴とする同期整流回路。

- 1次巻線と該1次巻線と同一極性の2次巻線とを備えたトランスと、前記トランスの1次巻線に印加される電力をスイッチングするスイッチング手段と、前記トランスの1次巻線に電力が印加されているときに、前記2次巻線に誘起された電力を蓄積すると共に平滑して出力側へ出力する平滑手段と、出力側から戻る戻り電流を同期整流する並列に接続した半導体スイッチ素子と、前記戻り電流を検出する検出手段と、前記半導体スイッチ素子の制御端子に加える駆動電圧を発生する手段とを有する電源装置において、

前記検出手段が、前記半導体スイッチ素子に直列に接続した抵抗と、該抵抗の両端の電位差を検出するものであって、

前記検出手段の検出値が大きくなるに従って、前記駆動電圧を発生する手段が、前記半導体スイッチ素子の制御端子駆動電圧を連続的に変化あるいは多段階に変化させて、制御端子駆動電圧を高くすることを特徴とする電源装置。 - 1次巻線と該1次巻線の極性と異なる2次巻線とを備えたトランスと、前記トランスの1次巻線に印加される電力をスイッチングするスイッチング手段と、前記2次巻線に誘起された電力を平滑して出力側へ出力する平滑手段と、出力側から戻る戻り電流を同期整流する半導体スイッチ素子と、前記戻り電流を検出する検出手段と、前記半導体スイッチ素子の制御端子に加える駆動電圧を発生する手段とを有する電源装置において、

前記検出手段が、前記半導体スイッチ素子に直列に接続した抵抗と、該抵抗の両端の電位差を検出するものであって、

前記検出手段の検出値が大きくなるに従って、前記駆動電圧を発生する手段が、前記半導体スイッチ素子の制御端子駆動電圧を連続的に変化あるいは多段階に変化させて、制御端子駆動電圧を高くすることを特徴とする電源装置。 - 1次巻線と、中点が設けた2次巻線とを備えたトランスと、前記トランスの1次巻線に一方向の電圧を印加した後に前記電圧の印加を所定時間停止し、前記1次巻線に他方向の電圧を印加した後に電圧の印加を所定時間停止することを繰り返す電圧印加手段と、前記トランスの2次巻線の両端と、この両端を互いに接続する接続点との間に配置した一対のスイッチ手段と、前記2次巻線の中点と前記接続点との間に配置し、前記中点と接続点との間の電力を平滑して出力側へ出力する平滑手段と、出力側から戻る戻り電流を検出する一対の検出手段と、前記半導体スイッチ素子の制御端子に加える駆動電圧を発生する手段とを有する電源装置において、

前記検出手段が、前記半導体スイッチ素子に直列に接続した抵抗と、該抵抗の両端の電位差を検出するものであって、

前記検出手段の検出値が大きくなるに従って、前記駆動電圧を発生する手段が、前記半導体スイッチ素子の制御端子駆動電圧を連続的に変化あるいは多段階に変化させて、制御 端子駆動電圧を高くすることを特徴とする電源装置。 - 請求項3から5の何れかに記載の電源装置において、前記半導体スイッチ素子がMOSFETであって、前記検出手段が前記直列に接続した抵抗に代えて、前記MOSFETのソースとドレインとの間の電圧を検出することを特徴とする電源装置。

- 請求項3から5の何れかに記載の電源装置において、前記半導体スイッチ素子がIGBTであることを特徴とする電源装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002040918A JP3655247B2 (ja) | 2002-02-19 | 2002-02-19 | 同期整流回路及び電源装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002040918A JP3655247B2 (ja) | 2002-02-19 | 2002-02-19 | 同期整流回路及び電源装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003244946A JP2003244946A (ja) | 2003-08-29 |

| JP2003244946A5 JP2003244946A5 (ja) | 2005-01-27 |

| JP3655247B2 true JP3655247B2 (ja) | 2005-06-02 |

Family

ID=27781460

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002040918A Expired - Fee Related JP3655247B2 (ja) | 2002-02-19 | 2002-02-19 | 同期整流回路及び電源装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3655247B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102611303A (zh) * | 2011-01-20 | 2012-07-25 | 江西开昂新能源科技有限公司 | 一种软开关dc-dc变换器 |

| CN110574273A (zh) * | 2017-06-30 | 2019-12-13 | 新电元工业株式会社 | 控制电路以及理想二极管电路 |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3916163B2 (ja) * | 2004-02-19 | 2007-05-16 | ローム株式会社 | 電流方向検出回路及びそれを備えたスイッチングレギュレータ |

| JP2005304210A (ja) * | 2004-04-14 | 2005-10-27 | Renesas Technology Corp | 電源ドライバ装置及びスイッチング電源装置 |

| JP4980588B2 (ja) | 2005-06-21 | 2012-07-18 | ローム株式会社 | 降圧型スイッチングレギュレータ、その制御回路、ならびにそれを用いた電子機器 |

| DE102005033477B4 (de) | 2005-07-18 | 2016-02-04 | Austriamicrosystems Ag | Schaltungsanordnung und Verfahren zum Konvertieren einer Wechselspannung in eine gleichgerichtete Spannung |

| US7737773B2 (en) | 2006-08-31 | 2010-06-15 | Sharp Kabushiki Kaisha | Semiconductor device, step-down chopper regulator, and electronic equipment |

| JP4738442B2 (ja) | 2008-05-28 | 2011-08-03 | 株式会社東芝 | Dc−dcコンバータ |

| JP5376512B2 (ja) * | 2009-05-21 | 2013-12-25 | スパンション エルエルシー | 電源装置 |

| JP5540754B2 (ja) * | 2010-02-15 | 2014-07-02 | 株式会社デンソー | Dc−dcコンバータの制御装置 |

| JP5749478B2 (ja) * | 2010-12-03 | 2015-07-15 | 株式会社タムラ製作所 | スイッチング電源装置 |

| JP5986921B2 (ja) * | 2012-12-27 | 2016-09-06 | 日立アプライアンス株式会社 | 点灯装置 |

| JP6424349B2 (ja) * | 2014-09-30 | 2018-11-21 | 株式会社エヌエフ回路設計ブロック | スイッチング電源装置 |

| CN111416505B (zh) * | 2020-04-14 | 2021-05-11 | 上海顺久电子科技有限公司 | 一种开关电源转换器 |

-

2002

- 2002-02-19 JP JP2002040918A patent/JP3655247B2/ja not_active Expired - Fee Related

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102611303A (zh) * | 2011-01-20 | 2012-07-25 | 江西开昂新能源科技有限公司 | 一种软开关dc-dc变换器 |

| CN102611303B (zh) * | 2011-01-20 | 2015-08-05 | 江西开昂新能源科技有限公司 | 一种软开关dc-dc变换器 |

| CN110574273A (zh) * | 2017-06-30 | 2019-12-13 | 新电元工业株式会社 | 控制电路以及理想二极管电路 |

| US11057032B2 (en) | 2017-06-30 | 2021-07-06 | Shindengen Electric Manufacturing Co., Ltd. | Control circuit and ideal diode circuit |

| CN110574273B (zh) * | 2017-06-30 | 2021-11-16 | 新电元工业株式会社 | 控制电路以及理想二极管电路 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003244946A (ja) | 2003-08-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI390826B (zh) | 直流/直流轉換器及其方法 | |

| US6710582B2 (en) | DC-DC converter and electronic device using the same | |

| KR101357070B1 (ko) | 고효율 전력 변환기 시스템 | |

| US20100259240A1 (en) | Bridgeless PFC converter | |

| US20090039711A1 (en) | Dual-Polarity Multi-Output DC/DC Converters and Voltage Regulators | |

| US7304463B2 (en) | DC-DC converter | |

| JP3475943B2 (ja) | スイッチング電源装置 | |

| JP2010536318A (ja) | 時分割マルチ出力dc/dcコンバータ及び電圧レギュレータ | |

| JP3655247B2 (ja) | 同期整流回路及び電源装置 | |

| JPH09504160A (ja) | パルス幅変調dc/dcブーストコンバータ | |

| JP2012050330A (ja) | Dc/dc電力変換装置 | |

| US11606037B2 (en) | Detection circuit and switching converter | |

| US6825641B2 (en) | High efficiency electrical switch and DC-DC converter incorporating same | |

| JP3528920B2 (ja) | スイッチング電源装置 | |

| US7184279B2 (en) | Solid state switching circuit | |

| WO2023231633A1 (zh) | 一种填谷电路的驱动电路、电源模组和电子设备 | |

| US20130257393A1 (en) | Switching power supply apparatus | |

| JPH11332226A (ja) | 同期整流型dc−dcコンバータ | |

| JP3055121B2 (ja) | チョッパ型dc−dcコンバータ | |

| JP2015228760A (ja) | スイッチング電源装置 | |

| JP4064879B2 (ja) | 同期整流回路及び電源装置 | |

| JP4328417B2 (ja) | 電源回路 | |

| JP2001224173A (ja) | 同期整流回路及び電源装置 | |

| JPH05219738A (ja) | 多重出力スイッチングレギュレータ | |

| JPH05137326A (ja) | フライバツク型スイツチングレギユレータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040218 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20040309 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040218 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20041207 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20041214 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050215 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050302 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 3655247 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080311 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090311 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090311 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100311 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110311 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120311 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130311 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130311 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140311 Year of fee payment: 9 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |