JP2018536994A - 薄いはんだストップ層を備える電子部品及び製造方法 - Google Patents

薄いはんだストップ層を備える電子部品及び製造方法 Download PDFInfo

- Publication number

- JP2018536994A JP2018536994A JP2018527165A JP2018527165A JP2018536994A JP 2018536994 A JP2018536994 A JP 2018536994A JP 2018527165 A JP2018527165 A JP 2018527165A JP 2018527165 A JP2018527165 A JP 2018527165A JP 2018536994 A JP2018536994 A JP 2018536994A

- Authority

- JP

- Japan

- Prior art keywords

- stop layer

- support

- solder stop

- component

- electronic component

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Ceased

Links

- 229910000679 solder Inorganic materials 0.000 title claims abstract description 94

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 15

- 238000000034 method Methods 0.000 claims abstract description 31

- 239000000463 material Substances 0.000 claims description 45

- 239000004020 conductor Substances 0.000 claims description 17

- 239000012778 molding material Substances 0.000 claims description 13

- 229910052710 silicon Inorganic materials 0.000 claims description 10

- 239000010703 silicon Substances 0.000 claims description 10

- 229910052751 metal Inorganic materials 0.000 claims description 9

- 239000002184 metal Substances 0.000 claims description 9

- 238000000151 deposition Methods 0.000 claims description 2

- 238000005476 soldering Methods 0.000 claims description 2

- 238000005304 joining Methods 0.000 claims 2

- 239000000758 substrate Substances 0.000 claims 1

- 239000010410 layer Substances 0.000 description 63

- 229920002120 photoresistant polymer Polymers 0.000 description 8

- 239000011241 protective layer Substances 0.000 description 8

- 238000001465 metallisation Methods 0.000 description 7

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 6

- 238000010438 heat treatment Methods 0.000 description 5

- 238000005240 physical vapour deposition Methods 0.000 description 5

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 229910052732 germanium Inorganic materials 0.000 description 4

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 4

- 238000005516 engineering process Methods 0.000 description 3

- 238000007639 printing Methods 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000010949 copper Substances 0.000 description 2

- 230000001419 dependent effect Effects 0.000 description 2

- 239000003989 dielectric material Substances 0.000 description 2

- 230000004907 flux Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 239000010931 gold Substances 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- HCHKCACWOHOZIP-UHFFFAOYSA-N Zinc Chemical compound [Zn] HCHKCACWOHOZIP-UHFFFAOYSA-N 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 1

- 230000015572 biosynthetic process Effects 0.000 description 1

- 229910052804 chromium Inorganic materials 0.000 description 1

- 239000011651 chromium Substances 0.000 description 1

- 238000010276 construction Methods 0.000 description 1

- 238000007796 conventional method Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 230000001939 inductive effect Effects 0.000 description 1

- 239000013067 intermediate product Substances 0.000 description 1

- 239000000155 melt Substances 0.000 description 1

- 150000002739 metals Chemical class 0.000 description 1

- 230000007935 neutral effect Effects 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 239000000615 nonconductor Substances 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000003672 processing method Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 239000010948 rhodium Substances 0.000 description 1

- MHOVAHRLVXNVSD-UHFFFAOYSA-N rhodium atom Chemical compound [Rh] MHOVAHRLVXNVSD-UHFFFAOYSA-N 0.000 description 1

- 238000004528 spin coating Methods 0.000 description 1

- 238000010897 surface acoustic wave method Methods 0.000 description 1

- 229910052718 tin Inorganic materials 0.000 description 1

- 239000011135 tin Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

- 239000011701 zinc Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L24/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L24/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/48—Manufacture or treatment of parts, e.g. containers, prior to assembly of the devices, using processes not provided for in a single one of the subgroups H01L21/06 - H01L21/326

- H01L21/4814—Conductive parts

- H01L21/4846—Leads on or in insulating or insulated substrates, e.g. metallisation

- H01L21/4853—Connection or disconnection of other leads to or from a metallisation, e.g. pins, wires, bumps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/50—Assembly of semiconductor devices using processes or apparatus not provided for in a single one of the subgroups H01L21/06 - H01L21/326, e.g. sealing of a cap to a base of a container

- H01L21/56—Encapsulations, e.g. encapsulation layers, coatings

- H01L21/565—Moulds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/28—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection

- H01L23/31—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape

- H01L23/3107—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed

- H01L23/3121—Encapsulations, e.g. encapsulating layers, coatings, e.g. for protection characterised by the arrangement or shape the device being completely enclosed a substrate forming part of the encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49811—Additional leads joined to the metallisation on the insulating substrate, e.g. pins, bumps, wires, flat leads

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49838—Geometry or layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/488—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor consisting of soldered or bonded constructions

- H01L23/498—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers

- H01L23/49866—Leads, i.e. metallisations or lead-frames on insulating substrates, e.g. chip carriers characterised by the materials

- H01L23/49894—Materials of the insulating layers or coatings

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/11—Manufacturing methods

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/14—Structure, shape, material or disposition of the bump connectors prior to the connecting process of a plurality of bump connectors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

- H01L2224/0237—Disposition of the redistribution layers

- H01L2224/02375—Top view

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/023—Redistribution layers [RDL] for bonding areas

- H01L2224/0239—Material of the redistribution layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/02—Bonding areas; Manufacturing methods related thereto

- H01L2224/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L2224/0401—Bonding areas specifically adapted for bump connectors, e.g. under bump metallisation [UBM]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/1012—Auxiliary members for bump connectors, e.g. spacers

- H01L2224/10122—Auxiliary members for bump connectors, e.g. spacers being formed on the semiconductor or solid-state body to be connected

- H01L2224/10145—Flow barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/1012—Auxiliary members for bump connectors, e.g. spacers

- H01L2224/10152—Auxiliary members for bump connectors, e.g. spacers being formed on an item to be connected not being a semiconductor or solid-state body

- H01L2224/10175—Flow barriers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/113—Manufacturing methods by local deposition of the material of the bump connector

- H01L2224/1131—Manufacturing methods by local deposition of the material of the bump connector in liquid form

- H01L2224/1132—Screen printing, i.e. using a stencil

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/1147—Manufacturing methods using a lift-off mask

- H01L2224/1148—Permanent masks, i.e. masks left in the finished device, e.g. passivation layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/118—Post-treatment of the bump connector

- H01L2224/11848—Thermal treatments, e.g. annealing, controlled cooling

- H01L2224/11849—Reflowing

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/131—Material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/13198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/13199—Material of the matrix

- H01L2224/13294—Material of the matrix with a principal constituent of the material being a liquid not provided for in groups H01L2224/132 - H01L2224/13291

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L2224/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

- H01L2224/13001—Core members of the bump connector

- H01L2224/13099—Material

- H01L2224/13198—Material with a principal constituent of the material being a combination of two or more materials in the form of a matrix with a filler, i.e. being a hybrid material, e.g. segmented structures, foams

- H01L2224/13298—Fillers

- H01L2224/13299—Base material

- H01L2224/133—Base material with a principal constituent of the material being a metal or a metalloid, e.g. boron [B], silicon [Si], germanium [Ge], arsenic [As], antimony [Sb], tellurium [Te] and polonium [Po], and alloys thereof

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/1605—Shape

- H01L2224/16057—Shape in side view

- H01L2224/16058—Shape in side view being non uniform along the bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/1605—Shape

- H01L2224/16057—Shape in side view

- H01L2224/16059—Shape in side view comprising protrusions or indentations

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16135—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip

- H01L2224/16145—Disposition the bump connector connecting between different semiconductor or solid-state bodies, i.e. chip-to-chip the bodies being stacked

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16227—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bond pad of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

- H01L2224/16238—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation the bump connector connecting to a bonding area protruding from the surface of the item

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/8119—Arrangement of the bump connectors prior to mounting

- H01L2224/81192—Arrangement of the bump connectors prior to mounting wherein the bump connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

- H01L2224/818—Bonding techniques

- H01L2224/81801—Soldering or alloying

- H01L2224/81815—Reflow soldering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/02—Bonding areas ; Manufacturing methods related thereto

- H01L24/04—Structure, shape, material or disposition of the bonding areas prior to the connecting process

- H01L24/05—Structure, shape, material or disposition of the bonding areas prior to the connecting process of an individual bonding area

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L24/10—Bump connectors ; Manufacturing methods related thereto

- H01L24/12—Structure, shape, material or disposition of the bump connectors prior to the connecting process

- H01L24/13—Structure, shape, material or disposition of the bump connectors prior to the connecting process of an individual bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/181—Encapsulation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/38—Effects and problems related to the device integration

- H01L2924/384—Bump effects

- H01L2924/3841—Solder bridging

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Power Engineering (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Ceramic Engineering (AREA)

- Geometry (AREA)

- Wire Bonding (AREA)

- Electric Connection Of Electric Components To Printed Circuits (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

Abstract

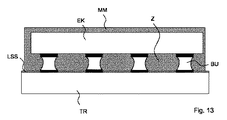

【選択図】図13

Description

−上側面及び上側面上にメタライズされた接触面を備えた支持体を準備する工程と、

−上側面上にレジスト層を配置し、レジスト層の材料が接触表面上に残留したままとなり、かつ接触面がない表面の領域にレジスト層の材料が存在しないように、レジスト層を構造化する工程と、

−はんだストップ層を支持体の上側面上に堆積させる工程と、

−レジスト層の残存材料を、接触面を覆うはんだストップ層の材料と共に除去する工程と、を含む。

EB:電子部品

EK:電子コンポーネント

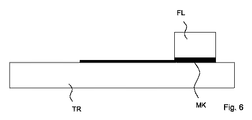

FL:フォトレジスト

KF:接触面

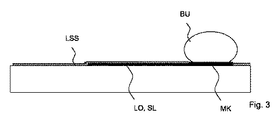

LO:はんだ付け可能表面

LP:はんだペースト

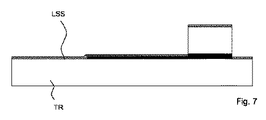

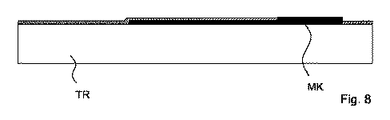

LSS:はんだストップ層

MK:メタライズされた接触面

MM:モールド材

O:支持体の上側面

SL:信号導体

TR:支持体

UBM:アンダーバンプメタライゼーション

Z:隙間

Claims (17)

- 電子部品(EB)であって、

−上側面(O)を備える支持体(TR)と、

−前記上側面(O)上のメタライズされた接触面(MK)と、

−前記上側面(O)の一部分を覆うが、前記接触面(MF)を覆わない、はんだストップ層(LSS)と、を備え、

−前記はんだストップ層(LSS)は、200nm以下の厚さを有する、電子部品。 - 前記はんだストップ層(LSS)は、30nm〜80nmの厚さを有する、請求項1に記載の部品。

- 前記メタライズされた接触面(MK)上にバンプ球(BU)を更に含む、請求項1又は2に記載の部品。

- 下側面に接触面(KF)を備える電子コンポーネント(EK)と、前記2つの接触面(MK、KF)を接合するバンプ接合体(BU)と、を更に含む、請求項1〜3のいずれか一項に記載の部品。

- 前記支持体(TR)の少なくとも一部分及び前記電子コンポーネント(EK)を被覆するモールド材(MM)を更に含む、請求項4に記載の部品。

- 前記モールド材(MM)は、前記電子コンポーネント(EK)と前記支持体(TR)との間の隙間(Z)もまた充填する、請求項5に記載の部品。

- −前記支持体(TR)の前記上側面(O)の前記接触面(MK)と相互接続された第1の信号導体(SL)と、

−前記支持体(TR)の前記上側面(O)の第2の信号導体(SL)と、を含み、

−2つの信号導体(SL)は、少なくとも部分的に前記はんだストップ層(LSS)によって被覆され、

−前記2つの信号導体(SL)間の電気抵抗は、100MΩ以上の値である、請求項1〜6のいずれか一項に記載の部品。 - 前記はんだストップ層(LSS)は、主成分としてケイ素を含むか、又はケイ素からなる、請求項1〜7のいずれか一項に記載の部品。

- 前記支持体(TR)の前記上側面(O)上に、40μm以上の高さを有する部品構造体が配置されている、請求項1〜8のいずれか一項に記載の部品。

- 電子部品(EB)の製造方法であって、

−上側面(O)及び前記上側面(O)上にメタライズされた接触面(MK)を備える支持体(TR)を準備する工程と、

−前記上側面(O)上にレジスト層(FL)を配置し、前記レジスト層(FL)の材料が前記接触面(MK)上に残留したままとなり、かつ前記接触面(MK)がない前記表面(O)の領域に前記レジスト層(FL)の前記材料が存在しないように、前記レジスト層(FL)を構造化する工程と、

−はんだストップ層(LSS)を前記支持体(TR)の前記上側面(O)上に堆積させる工程と、

−前記レジスト層(FL)の前記残留材料を、前記接触面(MK)を覆う前記はんだストップ層(LSS)の前記材料と共に除去する工程と、を含む、方法。 - 前記はんだストップ層(LSS)は、200nm以下の値の厚さを有する、請求項10に記載の方法。

- 前記はんだストップ層(LSS)は、20nm〜80nmの厚さを有する、請求項11に記載の方法。

- 前記はんだストップ層(LSS)は、主成分としてケイ素を含むか、又はケイ素からなる、請求項10〜12のいずれか一項に記載の方法。

- 前記電子部品(EB)は、更なるはんだ付け可能な金属表面(LO)を前記上側面上に有し、前記はんだストップ層(LSS)は、前記更なるはんだ付け可能な金属表面(LO)上に直接堆積される、請求項10〜13のいずれか一項に記載の方法。

- 前記はんだストップ層(LSS)は、PVD又はCVDを使用して塗布される、請求項10〜14のいずれか一項に記載の方法。

- −はんだペースト(LP)を少なくとも前記接触面(MK)上に配置する工程と、

−下側面に接触面(MK、KF)を備える電子コンポーネント(EK)を前記支持体(TR)の前記上側面(O)上に配置する工程と、

−前記部品(EB)をリフローはんだ付けし、前記2つの接触面(MK、KF)をバンプ接合体(BU)を使用して接合する工程と、を更に含む、請求項11〜15のいずれか一項に記載の方法。 - −前記電子コンポーネント(EK)をモールド材(MM)により包み込む工程を更に含み、

−前記モールド材(MM)は、前記コンポーネント(EK)と前記支持体(TR)との間の前記領域もまた充填する、請求項16に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102015120647.1A DE102015120647B4 (de) | 2015-11-27 | 2015-11-27 | Elektrisches Bauelement mit dünner Lot-Stopp-Schicht und Verfahren zur Herstellung |

| DE102015120647.1 | 2015-11-27 | ||

| PCT/EP2016/070973 WO2017088998A1 (de) | 2015-11-27 | 2016-09-06 | Elektrisches bauelement mit dünner lot-stopp-schicht und verfahren zu seiner herstellung |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2018536994A true JP2018536994A (ja) | 2018-12-13 |

| JP2018536994A5 JP2018536994A5 (ja) | 2019-09-26 |

Family

ID=56883787

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018527165A Ceased JP2018536994A (ja) | 2015-11-27 | 2016-09-06 | 薄いはんだストップ層を備える電子部品及び製造方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US20180331062A1 (ja) |

| EP (1) | EP3381052A1 (ja) |

| JP (1) | JP2018536994A (ja) |

| KR (1) | KR20180088798A (ja) |

| CN (1) | CN108369935A (ja) |

| BR (1) | BR112018010666A8 (ja) |

| DE (1) | DE102015120647B4 (ja) |

| WO (1) | WO2017088998A1 (ja) |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| FI130166B (en) | 2019-03-08 | 2023-03-23 | Picosun Oy | Solder mask |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03218644A (ja) * | 1990-01-24 | 1991-09-26 | Sharp Corp | 回路基板の接続構造 |

| JPH098082A (ja) * | 1995-06-15 | 1997-01-10 | At & T Ipm Corp | ハンダボンディングの方法 |

| JP2007311456A (ja) * | 2006-05-17 | 2007-11-29 | Fujikura Ltd | 接合基材の製造方法 |

| US20110285011A1 (en) * | 2010-05-18 | 2011-11-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Cu pillar bump with l-shaped non-metal sidewall protection structure |

| CN103958393A (zh) * | 2011-11-10 | 2014-07-30 | 株式会社优利电子 | Mems传感器封装及其方法 |

| WO2015083043A1 (en) * | 2013-12-04 | 2015-06-11 | International Business Machines Corporation | Flip-chip electronic device with carrier having heat dissipation elements free of solder mask |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6294840B1 (en) * | 1999-11-18 | 2001-09-25 | Lsi Logic Corporation | Dual-thickness solder mask in integrated circuit package |

| US6645791B2 (en) * | 2001-04-23 | 2003-11-11 | Fairchild Semiconductor | Semiconductor die package including carrier with mask |

| JP2006500769A (ja) * | 2002-09-20 | 2006-01-05 | ハネウェル・インターナショナル・インコーポレーテッド | 低k材料用の中間層接着促進剤 |

| KR20050087840A (ko) * | 2002-12-20 | 2005-08-31 | 에이저 시스템즈 인크 | 구리 상호 접속 구조체로의 본딩 구조체 및 방법 |

| US6790759B1 (en) * | 2003-07-31 | 2004-09-14 | Freescale Semiconductor, Inc. | Semiconductor device with strain relieving bump design |

| US7294451B2 (en) * | 2003-11-18 | 2007-11-13 | Texas Instruments Incorporated | Raised solder-mask-defined (SMD) solder ball pads for a laminate electronic circuit board |

| US7132303B2 (en) * | 2003-12-18 | 2006-11-07 | Freescale Semiconductor, Inc. | Stacked semiconductor device assembly and method for forming |

| KR100626617B1 (ko) * | 2004-12-07 | 2006-09-25 | 삼성전자주식회사 | 반도체 패키지용 배선 기판의 볼 랜드 구조 |

| JP5031403B2 (ja) * | 2007-03-01 | 2012-09-19 | 京セラケミカル株式会社 | 封止用エポキシ樹脂組成物、樹脂封止型半導体装置及びその製造方法 |

| US7812460B2 (en) * | 2008-05-30 | 2010-10-12 | Unimicron Technology Corp. | Packaging substrate and method for fabricating the same |

| US8922004B2 (en) * | 2010-06-11 | 2014-12-30 | Taiwan Semiconductor Manufacturing Company, Ltd. | Copper bump structures having sidewall protection layers |

| TWI575684B (zh) * | 2011-06-13 | 2017-03-21 | 矽品精密工業股份有限公司 | 晶片尺寸封裝件 |

| US10192804B2 (en) * | 2012-07-09 | 2019-01-29 | Taiwan Semiconductor Manufacturing Company, Ltd. | Bump-on-trace packaging structure and method for forming the same |

| CN104637967A (zh) * | 2015-02-13 | 2015-05-20 | 苏州晶方半导体科技股份有限公司 | 封装方法及封装结构 |

| US9859234B2 (en) * | 2015-08-06 | 2018-01-02 | Invensas Corporation | Methods and structures to repair device warpage |

-

2015

- 2015-11-27 DE DE102015120647.1A patent/DE102015120647B4/de active Active

-

2016

- 2016-09-06 JP JP2018527165A patent/JP2018536994A/ja not_active Ceased

- 2016-09-06 KR KR1020187011776A patent/KR20180088798A/ko not_active Application Discontinuation

- 2016-09-06 CN CN201680062169.7A patent/CN108369935A/zh active Pending

- 2016-09-06 EP EP16762778.5A patent/EP3381052A1/de not_active Withdrawn

- 2016-09-06 US US15/776,019 patent/US20180331062A1/en not_active Abandoned

- 2016-09-06 WO PCT/EP2016/070973 patent/WO2017088998A1/de active Application Filing

- 2016-09-06 BR BR112018010666A patent/BR112018010666A8/pt not_active Application Discontinuation

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03218644A (ja) * | 1990-01-24 | 1991-09-26 | Sharp Corp | 回路基板の接続構造 |

| JPH098082A (ja) * | 1995-06-15 | 1997-01-10 | At & T Ipm Corp | ハンダボンディングの方法 |

| US5620131A (en) * | 1995-06-15 | 1997-04-15 | Lucent Technologies Inc. | Method of solder bonding |

| JP2007311456A (ja) * | 2006-05-17 | 2007-11-29 | Fujikura Ltd | 接合基材の製造方法 |

| US20110285011A1 (en) * | 2010-05-18 | 2011-11-24 | Taiwan Semiconductor Manufacturing Company, Ltd. | Cu pillar bump with l-shaped non-metal sidewall protection structure |

| CN103958393A (zh) * | 2011-11-10 | 2014-07-30 | 株式会社优利电子 | Mems传感器封装及其方法 |

| JP2015504373A (ja) * | 2011-11-10 | 2015-02-12 | ユー エレクトロニクス シーオー. エルティディ. | Memsセンサパッケージング及びその方法 |

| WO2015083043A1 (en) * | 2013-12-04 | 2015-06-11 | International Business Machines Corporation | Flip-chip electronic device with carrier having heat dissipation elements free of solder mask |

| JP2017504189A (ja) * | 2013-12-04 | 2017-02-02 | インターナショナル・ビジネス・マシーンズ・コーポレーションInternational Business Machines Corporation | フリップチップ・タイプの電子デバイス、およびフリップチップ・タイプの電子デバイスを製造するための方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| BR112018010666A8 (pt) | 2019-02-26 |

| DE102015120647A1 (de) | 2017-06-01 |

| EP3381052A1 (de) | 2018-10-03 |

| DE102015120647B4 (de) | 2017-12-28 |

| BR112018010666A2 (pt) | 2018-11-13 |

| KR20180088798A (ko) | 2018-08-07 |

| CN108369935A (zh) | 2018-08-03 |

| WO2017088998A1 (de) | 2017-06-01 |

| US20180331062A1 (en) | 2018-11-15 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5624649B2 (ja) | 基板に取り付けられたスタッドバンプを伴う、フリップチップパッケージング用の可融性入出力相互接続システムおよび方法 | |

| US6897142B2 (en) | Formation of solder balls having resin member as reinforcement | |

| US6559528B2 (en) | Semiconductor device and method for the fabrication thereof | |

| JP4660643B2 (ja) | プリ半田構造を形成するための半導体パッケージ基板及びプリ半田構造が形成された半導体パッケージ基板、並びにこれらの製法 | |

| TWI498976B (zh) | 晶圓級封裝整合及方法 | |

| US8431478B2 (en) | Solder cap bump in semiconductor package and method of manufacturing the same | |

| US9293433B2 (en) | Intermetallic compound layer on a pillar between a chip and substrate | |

| US9806045B2 (en) | Interconnection structure including a metal post encapsulated by solder joint having a concave outer surface | |

| KR101235498B1 (ko) | 집적 수동 컴포넌트를 구비한 집적 회로를 패키징하기 위한 방법 및 시스템 | |

| TW201403726A (zh) | 金屬柱導線直連元件、金屬柱導線直連封裝結構、金屬柱導線直連元件的製作方法 | |

| JP3563635B2 (ja) | 半導体集積回路装置およびその製造方法 | |

| JP2004281540A (ja) | 電子装置及びその製造方法、チップキャリア、回路基板並びに電子機器 | |

| JP2018536994A (ja) | 薄いはんだストップ層を備える電子部品及び製造方法 | |

| US10403591B2 (en) | Chip package assembly with enhanced interconnects and method for fabricating the same | |

| JP2021034600A (ja) | 半導体装置 | |

| KR101758999B1 (ko) | 반도체 디바이스 및 그 제조 방법 | |

| JP2003046026A (ja) | 半導体装置及びその製造方法 | |

| US20120126397A1 (en) | Semiconductor substrate and method thereof | |

| JP2004014854A (ja) | 半導体装置 | |

| TWI522308B (zh) | 具微機電元件之封裝結構及其製法 | |

| US6415973B1 (en) | Method of application of copper solution in flip-chip, COB, and micrometal bonding | |

| US7015132B2 (en) | Forming an electrical contact on an electronic component | |

| WO2018198544A1 (ja) | 半導体装置の製造方法および半導体装置 | |

| JP2021022604A (ja) | 電子装置、および電子装置の製造方法 | |

| JP5482170B2 (ja) | 半導体装置、半導体装置の製造方法、回路基板及び回路基板の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20190814 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190814 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20200820 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200923 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201223 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210216 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20210517 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210519 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210803 |

|

| A045 | Written measure of dismissal of application [lapsed due to lack of payment] |

Free format text: JAPANESE INTERMEDIATE CODE: A045 Effective date: 20211221 |