JP2016178334A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2016178334A JP2016178334A JP2016115416A JP2016115416A JP2016178334A JP 2016178334 A JP2016178334 A JP 2016178334A JP 2016115416 A JP2016115416 A JP 2016115416A JP 2016115416 A JP2016115416 A JP 2016115416A JP 2016178334 A JP2016178334 A JP 2016178334A

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor device

- electrode

- pad electrode

- wiring electrode

- mounting substrate

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/81—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a bump connector

Abstract

【解決手段】実装基板8と、実装基板8上に配置された信号配線電極12と、実装基板8上に若しくは実装基板8を貫通して配置されたパワー配線電極6と、信号配線電極12と電気的に接合可能なゲートパッド電極GPおよびパワー配線電極6と電気的に接合可能なソースパッド電極SPを有する半導体デバイス16と、信号配線電極12とゲートパッド電極GPとの間に配置された第1金属粒子接合層18Gと、パワー配線電極6とソースパッド電極SPとの間に配置された第2金属粒子接合層18Sとを備え、半導体デバイス16が実装基板8上にフリップチップ接続された半導体装置1およびその製造方法。

【選択図】図2

Description

(半導体装置の構成)

第1の実施の形態に係る半導体装置1の模式的平面パターン構成は、図1に示すように表され、図1のI−I線に沿う模式的断面構造は、図2に示すように表される。図1は、図2において、実装基板8上に配置された半導体デバイス16のドレイン電極36側から見た平面パターン構成に対応している。

銀ナノペーストは、例えば、粒径約30nm〜約100nmの銀ナノ粒子を所定の溶媒に拡散させたものである。溶媒としては、例えばテルピネオール等の極性溶媒、テトラデカン等の炭化水素系溶媒、水系溶媒、ケトン系溶媒等が適用される。

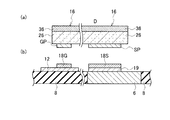

第1の実施の形態に係る半導体装置1の製造方法の一工程であって、半導体デバイス16のフリップチップ接合前の状態を示す模式的断面構造は、図3(a)に示すように表され、図3(a)に対応する実装基板8の模式的断面構造は、図3(b)に示すように表される。

第1の実施の形態に係る半導体装置の製造方法の一工程であって、加圧工程を示す模式的断面構造は、図6に示すように表される。

(半導体装置の構成)

第2の実施の形態に係る半導体装置1の模式的平面パターン構成は、図7に示すように表され、図7のII−II線に沿う模式的断面構造は、図8に示すように表される。図7は、図8において、実装基板8上に配置された半導体デバイス16のドレイン電極36側から見た平面パターン構成に対応している。

第2の実施の形態に係る半導体装置1の製造方法の一工程であって、半導体デバイス16のフリップチップ接合前の状態を示す模式的断面構造は、図9(a)に示すように表され、図9(a)に対応する実装基板8の模式的断面構造は、図9(b)に示すように表される。

第2の実施の形態に係る半導体装置の製造方法の一工程であって、加圧工程を示す模式的断面構造は、図12に示すように表される。

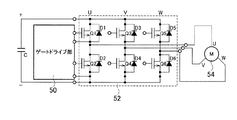

次に、図14を参照して、第1〜第2の実施の形態に係る半導体装置1を用いて構成した3相インバータについて説明する。

第1〜第2の実施の形態に係る半導体装置1に適用する半導体デバイス16の例として、SiC・MOSFETの模式的断面構造は、図15に示すように、n−高抵抗層からなる半導体基板26と、半導体基板26の表面側に形成されたpベース領域28と、pベース領域28の表面に形成されたソース領域30と、pベース領域28間の半導体基板26の表面上に配置されたゲート絶縁膜32と、ゲート絶縁膜32上に配置されたゲート電極38と、ソース領域30に接続されたソース電極34と、半導体基板26の表面と反対側の裏面に配置されたn+ドレイン領域24と、n+ドレイン領域24に接続されたドレイン電極36とを備える。

第1〜第2の実施の形態に係る半導体装置の製造方法の一工程であって、半導体基板26上にペースト層18を塗布するためのマスク25を配置した状態を示す模式的平面パターン構成は、図17(a)に示すように表され、図17(a)のIII−III線に沿う模式的断面構造は、図17(b)に示すように表される。

図23〜図25を参照して、比較例について簡単に説明する。

上記のように、実施の形態および変形例によって記載したが、この開示の一部をなす論述および図面は例示的なものであり、この発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例および運用技術が明らかとなろう。

2…ヒートスプレッダー

4…柱状電極

6、13…パワー配線電極

8…実装基板

12…信号配線電極

16…半導体デバイス

18…ペースト層

18G、18S…金属粒子接合層

19…銀メッキ層

20…溶媒

20a…シェル

22…銀ナノ粒子

24…n+ドレイン領域

25…マスク

25a…開口部

26…半導体基板

27…スキージ(ヘラ部材)

28…pベース領域

30…ソース領域

32…ゲート絶縁膜

34…ソース電極

36…ドレイン電極

36a…ドレイン電極接合層

38…ゲート電極

44…層間絶縁膜

50…ゲートドライブ部

52…パワーモジュール部

54…三相モータ部

120…プレス加工機

C…コンデンサ

D1〜D6…ダイオード

GP…ゲートパッド電極

SP…ソースパッド電極

Claims (26)

- 実装基板と、

前記実装基板上に配置された信号配線電極と、

前記実装基板上若しくは前記実装基板を貫通して配置されたパワー配線電極と、

前記信号配線電極と電気的に接合可能なゲートパッド電極と、前記パワー配線電極と電気的に接合可能なソースパッド電極とを有するパワーデバイスと、

前記信号配線電極と前記ゲートパッド電極との間に配置され、複数の金属微粒子と前記複数の金属微粒子を被覆する酸化防止膜とを有し、前記酸化防止膜が破砕した面において、前記複数の金属微粒子間が密着された状態で析出される金属により相互に接続されてなる第1金属粒子接合層と、

前記パワー配線電極と前記ソースパッド電極との間に配置され、複数の金属微粒子と前記複数の金属微粒子を被覆する酸化防止膜とを有し、前記酸化防止膜が破砕した面において、前記複数の金属微粒子間が密着された状態で析出される金属により相互に接続されてなる第2金属粒子接合層と

を備え、

前記パワーデバイスが前記実装基板上にフリップチップ接続されたことを特徴とする半導体装置。 - 前記パワーデバイスは、SiC系FETまたはGaN系FETであることを特徴とする請求項1に記載の半導体装置。

- 前記酸化防止膜は、前記複数の金属微粒子の表面を被覆する有機殻であることを特徴とする請求項1に記載の半導体装置。

- 前記複数の金属微粒子は、半田よりも高融点な銀ナノ粒子、金ナノ粒子またはニッケルナノ粒子のいずれかであって、

前記銀ナノ粒子、前記金ナノ粒子または前記ニッケルナノ粒子のいずれかを所定の溶媒中に分散させた金属ナノ粒子ペースト層とされていることを特徴とする請求項3に記載の半導体装置。 - 前記金属ナノ粒子ペースト層は、前記所定の溶媒中に前記銀ナノ粒子を分散させた銀ナノペーストであることを特徴とする請求項4に記載の半導体装置。

- 前記銀ナノペーストは、前記銀ナノ粒子の濃度が80質量%〜95質量%であることを特徴とする請求項5に記載の半導体装置。

- 前記銀ナノペーストは、前記銀ナノ粒子の粒径が30nm〜100nmであることを特徴とする請求項5または6に記載の半導体装置。

- 前記銀ナノ粒子は、加圧によって前記有機殻の少なくとも一部が破砕されることにより、前記銀ナノペースト中で密着した状態となることを特徴とする請求項4〜7のいずれか1項に記載の半導体装置。

- 前記所定の溶媒は、極性溶媒、炭化水素系溶媒、水系溶媒またはケトン系溶媒のいずれかであることを特徴とする請求項4または5に記載の半導体装置。

- 前記パワー配線電極上の前記第2金属粒子接合層と接する界面には、さらに銀メッキ層が形成されていることを特徴とする請求項1に記載の半導体装置。

- 前記パワーデバイスは、前記ゲートパッド電極および前記ソースパッド電極の配置面と対向する面に配置されたドレイン電極をさらに有し、

前記ドレイン電極上には柱状電極を介して第1のヒートスプレッダーが配置されることを特徴とする請求項1〜10のいずれか1項に記載の半導体装置。 - 前記実装基板の、前記パワーデバイスの搭載面と対向する面には、第2のヒートスプレッダーが配置されることを特徴とする請求項1〜11のいずれか1項に記載の半導体装置。

- 前記パワーデバイスは、300℃〜400℃での高温動作が可能であることを特徴とする請求項1〜12のいずれか1項に記載の半導体装置。

- 前記パワー配線電極は、数百アンペアの大電流を通電可能であることを特徴とする請求項1〜13のいずれか1項に記載の半導体装置。

- 実装基板上に信号配線電極を形成する工程と、

前記実装基板上に若しくは前記実装基板を貫通してパワー配線電極を形成する工程と、

前記信号配線電極と電気的に接合可能なゲートパッド電極と、前記パワー配線電極と電気的に接合可能なソースパッド電極とを有するパワーデバイスを形成する工程と、

前記信号配線電極もしくは前記ゲートパッド電極の一方若しくは両方に、複数の金属微粒子と前記複数の金属微粒子を被覆する酸化防止膜とを有し、前記酸化防止膜が破砕した面において、前記複数の金属微粒子間が密着された状態で析出される金属により相互に接続されてなる第1金属粒子接合層を形成する工程と、

前記パワー配線電極もしくは前記ソースパッド電極の一方若しくは両方に、複数の金属微粒子と前記複数の金属微粒子を被覆する酸化防止膜とを有し、前記酸化防止膜が破砕した面において、前記複数の金属微粒子間が密着された状態で析出される金属により相互に接続されてなる第2金属粒子接合層を形成する工程と、

前記パワーデバイスを前記実装基板上にフリップチップ接続する工程と

を有することを特徴とする半導体装置の製造方法。 - 前記第1金属粒子接合層を形成する工程は、前記複数の金属微粒子を含む第1ペースト層を前記信号配線電極もしくは前記ゲートパッド電極の一方若しくは両方に塗布する工程を有し、

前記第2金属粒子接合層を形成する工程は、前記複数の金属微粒子を含む第2ペースト層を前記パワー配線電極もしくは前記ソースパッド電極の一方若しくは両方に塗布する工程を有することを特徴とする請求項15に記載の半導体装置の製造方法。 - 前記パワーデバイスを前記実装基板上にフリップチップ接続する工程は、

前記第1ペースト層を介して前記信号配線電極と前記ゲートパッド電極とを当接させ、当該当接状態において前記第1ペースト層を所定温度で焼成し、前記信号配線電極と前記ゲートパッド電極とを接合する工程と、

前記第2ペースト層を介して前記パワー配線電極と前記ソースパッド電極とを当接させ、当該当接状態において前記第2ペースト層を所定温度で焼成し、前記パワー配線電極と前記ソースパッド電極とを接合する工程と

を有することを特徴とする請求項15または16に記載の半導体装置の製造方法。 - 前記第2ペースト層を前記パワー配線電極もしくは前記ソースパッド電極の一方若しくは両方に塗布する工程は、

前記パワー配線電極もしくは前記ソースパッド電極の一方若しくは両方に、当該各電極位置に合わせた開口部を有するマスクを位置合わせして重ね合わせる工程と、

当該マスクの上に前記第2ペースト層を堆積する工程と、

スキージによって前記第2ペースト層を前記開口部に充填する工程と、

前記マスクを取り除く工程と

を有することを特徴とする請求項16に記載の半導体装置の製造方法。 - 前記ペースト層の焼成を行う前に、前記実装基板と前記パワーデバイスとを対向する方向に押圧して、前記ペースト層に所定の圧力を加える工程をさらに有することを特徴とする請求項17に記載の半導体装置の製造方法。

- 前記所定の圧力は、2MPa〜30MPaであることを特徴とする請求項19に記載の半導体装置の製造方法。

- 前記第1ペースト層および前記第2ペースト層は、所定の溶媒中に銀ナノ粒子を分散させた銀ナノペーストであることを特徴とする請求項16に記載の半導体装置の製造方法。

- 前記銀ナノペーストは、前記銀ナノ粒子の濃度が80質量%〜95質量%であることを特徴とする請求項21に記載の半導体装置の製造方法。

- 前記銀ナノペーストは、前記銀ナノ粒子の粒径が30nm〜100nmであることを特徴とする請求項21または22に記載の半導体装置の製造方法。

- 前記銀ナノペーストの焼成温度は、200℃〜400℃であることを特徴とする請求項21〜23のいずれか1項に記載の半導体装置の製造方法。

- 前記パワーデバイスは、SiC系FETまたはGaN系FETであることを特徴とする請求項15に記載の半導体装置の製造方法。

- 前記パワーデバイスは、前記ゲートパッド電極および前記ソースパッド電極の配置面と対向する面に配置されたドレイン電極を備え、

前記ドレイン電極上に柱状電極を介してヒートスプレッダーを配置する工程をさらに有することを特徴とする請求項15〜25のいずれか1項に記載の半導体装置の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016115416A JP6387048B2 (ja) | 2016-06-09 | 2016-06-09 | 半導体装置の製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016115416A JP6387048B2 (ja) | 2016-06-09 | 2016-06-09 | 半導体装置の製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011217477A Division JP2013077745A (ja) | 2011-09-30 | 2011-09-30 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016178334A true JP2016178334A (ja) | 2016-10-06 |

| JP6387048B2 JP6387048B2 (ja) | 2018-09-05 |

Family

ID=57071330

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016115416A Active JP6387048B2 (ja) | 2016-06-09 | 2016-06-09 | 半導体装置の製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6387048B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019180913A1 (ja) * | 2018-03-23 | 2019-09-26 | 三菱マテリアル株式会社 | 電子部品実装モジュールの製造方法 |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001225180A (ja) * | 2000-02-18 | 2001-08-21 | Ebara Corp | 金属の接合方法 |

| JP2004107728A (ja) * | 2002-09-18 | 2004-04-08 | Ebara Corp | 接合材料及び接合方法 |

| JP2004128357A (ja) * | 2002-10-04 | 2004-04-22 | Ebara Corp | 電極配設基体及びその電極接合方法 |

| JP2005136375A (ja) * | 2003-10-09 | 2005-05-26 | Hitachi Ltd | 電子部品の実装方法,半導体モジュール及び半導体装置 |

| JP2006202938A (ja) * | 2005-01-20 | 2006-08-03 | Kojiro Kobayashi | 半導体装置及びその製造方法 |

| JP2007251076A (ja) * | 2006-03-20 | 2007-09-27 | Hitachi Ltd | パワー半導体モジュール |

| JP2007281090A (ja) * | 2006-04-04 | 2007-10-25 | Kansai Electric Power Co Inc:The | ワイドギャップ複合半導体装置 |

| JP2008218474A (ja) * | 2007-02-28 | 2008-09-18 | Shinkawa Ltd | ボンディング装置及び方法 |

| US20100102327A1 (en) * | 2008-02-26 | 2010-04-29 | International Rectifier Corporation (El Segundo, Ca) | Semiconductor device and passive component integration in a semiconductor package |

| JP2010161265A (ja) * | 2009-01-09 | 2010-07-22 | Denso Corp | 電子装置 |

| JP2013077745A (ja) * | 2011-09-30 | 2013-04-25 | Rohm Co Ltd | 半導体装置およびその製造方法 |

-

2016

- 2016-06-09 JP JP2016115416A patent/JP6387048B2/ja active Active

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001225180A (ja) * | 2000-02-18 | 2001-08-21 | Ebara Corp | 金属の接合方法 |

| JP2004107728A (ja) * | 2002-09-18 | 2004-04-08 | Ebara Corp | 接合材料及び接合方法 |

| JP2004128357A (ja) * | 2002-10-04 | 2004-04-22 | Ebara Corp | 電極配設基体及びその電極接合方法 |

| JP2005136375A (ja) * | 2003-10-09 | 2005-05-26 | Hitachi Ltd | 電子部品の実装方法,半導体モジュール及び半導体装置 |

| JP2006202938A (ja) * | 2005-01-20 | 2006-08-03 | Kojiro Kobayashi | 半導体装置及びその製造方法 |

| JP2007251076A (ja) * | 2006-03-20 | 2007-09-27 | Hitachi Ltd | パワー半導体モジュール |

| JP2007281090A (ja) * | 2006-04-04 | 2007-10-25 | Kansai Electric Power Co Inc:The | ワイドギャップ複合半導体装置 |

| JP2008218474A (ja) * | 2007-02-28 | 2008-09-18 | Shinkawa Ltd | ボンディング装置及び方法 |

| US20100102327A1 (en) * | 2008-02-26 | 2010-04-29 | International Rectifier Corporation (El Segundo, Ca) | Semiconductor device and passive component integration in a semiconductor package |

| JP2010161265A (ja) * | 2009-01-09 | 2010-07-22 | Denso Corp | 電子装置 |

| JP2013077745A (ja) * | 2011-09-30 | 2013-04-25 | Rohm Co Ltd | 半導体装置およびその製造方法 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2019180913A1 (ja) * | 2018-03-23 | 2019-09-26 | 三菱マテリアル株式会社 | 電子部品実装モジュールの製造方法 |

| US11476127B2 (en) | 2018-03-23 | 2022-10-18 | Mitsubishi Materials Corporation | Manufacturing method of electronic-component-mounted module |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6387048B2 (ja) | 2018-09-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9716054B2 (en) | Semiconductor device | |

| US9673163B2 (en) | Semiconductor device with flip chip structure and fabrication method of the semiconductor device | |

| JP2013077745A (ja) | 半導体装置およびその製造方法 | |

| CN101593709B (zh) | 含烧结接头的模块 | |

| JP6265693B2 (ja) | 半導体装置およびその製造方法 | |

| WO2016152258A1 (ja) | 半導体装置 | |

| JP6077773B2 (ja) | パワーモジュール半導体装置 | |

| CN109216313A (zh) | 具有包括钎焊的导电层的芯片载体的模制封装 | |

| US8637379B2 (en) | Device including a semiconductor chip and a carrier and fabrication method | |

| WO2018194153A1 (ja) | 電力用半導体モジュール、電子部品および電力用半導体モジュールの製造方法 | |

| CN103579154B (zh) | 包括叠层的电气器件封装以及其制造方法 | |

| JP5930980B2 (ja) | 半導体装置およびその製造方法 | |

| US11862542B2 (en) | Dual side cooling power module and manufacturing method of the same | |

| WO2023221970A1 (zh) | 功率模块、电源系统、车辆及光伏系统 | |

| JP2014120639A (ja) | パワーモジュール半導体装置 | |

| JP2014120638A (ja) | パワーモジュール半導体装置およびその製造方法 | |

| JP2014053403A (ja) | パワーモジュール半導体装置 | |

| JP6387048B2 (ja) | 半導体装置の製造方法 | |

| JPWO2020105476A1 (ja) | 半導体装置 | |

| JP4039258B2 (ja) | 電力用半導体装置 | |

| US10236244B2 (en) | Semiconductor device and production method therefor | |

| JP2014053406A (ja) | 半導体装置およびその製造方法 | |

| JP2017103290A (ja) | 半導体装置およびその製造方法、パワーモジュール並びに車両 | |

| US9362221B2 (en) | Surface mountable power components | |

| WO2023017680A1 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170206 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170307 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170501 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171031 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171225 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180605 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180706 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180724 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180810 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6387048 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |