JP2015114238A - ピークホールド回路およびピークホールド方法 - Google Patents

ピークホールド回路およびピークホールド方法 Download PDFInfo

- Publication number

- JP2015114238A JP2015114238A JP2013257299A JP2013257299A JP2015114238A JP 2015114238 A JP2015114238 A JP 2015114238A JP 2013257299 A JP2013257299 A JP 2013257299A JP 2013257299 A JP2013257299 A JP 2013257299A JP 2015114238 A JP2015114238 A JP 2015114238A

- Authority

- JP

- Japan

- Prior art keywords

- input

- voltage

- constant current

- output

- switch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 title claims description 12

- 239000003990 capacitor Substances 0.000 claims abstract description 44

- 229920006395 saturated elastomer Polymers 0.000 description 8

- 238000010586 diagram Methods 0.000 description 5

- 230000000052 comparative effect Effects 0.000 description 4

- 201000000464 cone-rod dystrophy 2 Diseases 0.000 description 3

- 201000006754 cone-rod dystrophy Diseases 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

Images

Landscapes

- Measurement Of Current Or Voltage (AREA)

Abstract

Description

一端に正極の電源電圧が入力され、他端から所定の定電流を出力する定電流回路と、

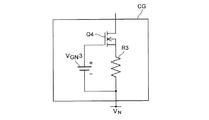

一端が前記定電流回路の出力に接続され、他端に負極の電源電圧が入力され、前記定電流回路が出力する定電流より小さい規定の電流を流す電流生成部と、

一端が前記定電流回路の出力に接続されるスイッチと、

一端が前記スイッチの他端に接続され、他端が接地されているコンデンサと、

第1の入力が前記スイッチの他端と前記コンデンサの一端とに接続され、出力が第2の入力に接続されたオペアンプと、

第1の入力に入力される電圧と、第2の入力に入力されるオペアンプの出力電圧とを比較し、この比較結果に基づいて前記スイッチを制御するコンパレータと、

を備える。

外部から入力された入力電圧が、所定の電圧未満の場合、前記入力電圧を前記所定の電圧だけマイナス側にシフトさせた電圧を前記コンパレータの前記第1の入力に出力し、前記入力電圧が前記所定の電圧以上の場合、前記入力電圧に応じた電圧を前記コンパレータの前記第1の入力に出力する電圧シフト部を更に備える。

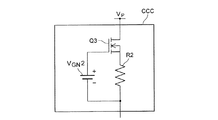

ドレインに前記正極の電源電圧が入力され、ゲートに第2の基準電位が入力され、ソースが前記スイッチの一端及び前記電流生成部の一端に接続された定電流用MOSトランジスタを備え、

前記電流生成部が供給する電流の大きさは、前記定電流用MOSトランジスタが動作状態を維持できる範囲の電流値である。

前記電流生成部が供給する電流の大きさは、前記定電流用MOSトランジスタが動作状態を維持できる範囲の電流の下限値である。

前記定電流回路は、アノードに前記正極の電源電圧が入力され、カソードが前記スイッチの一端及び前記電流生成部の一端に接続された第1の定電流ダイオードである。

前記電流生成部は、アノードが前記定電流回路の出力に接続され、カソードが接地された第2の定電流ダイオードである。

前記電圧シフト部は、

一端から前記入力電圧が入力される第1の抵抗と、

一端が前記第1の抵抗の他端に接続され、前記第1の抵抗より抵抗値が小さい第2の抵抗と、

前記コンパレータの第1の入力の電圧が前記オペアンプの出力電圧未満の場合、前記第2の抵抗の他端に負の基準電位が入力されるように制御し、前記コンパレータの第1の入力の電圧が前記オペアンプの出力電圧以上の場合、前記第2の抵抗の他端に負の基準電位が入力されないように制御する切替部と、

を備える。

前記切替部は、前記コンパレータの出力電圧を反転して出力するインバータと、ゲートが前記インバータの出力に接続され、ソースに前記負の基準電位が入力され、ドレインが前記第2の抵抗の他端に接続されたシフト用MOSトランジスタと、を備える。

ドレインが前記コンデンサの一端と前記オペアンプの第1の入力とに接続され、ソースが接地され、ゲートに供給されるリセット信号に応じて制御されるスルー用MOSトランジスタを更に備える。

前記スイッチは、前記コンパレータの第1の入力に入力される電圧が前記オペアンプの出力以上の場合、前記コンデンサの一端と前記定電流回路の出力との間を導通させる。

一端に正極の電源電圧が入力され、他端から所定の定電流を出力する定電流回路と、一端が前記定電流回路の出力に接続され、他端に負極の電源電圧が入力され、前記定電流回路が出力する定電流より小さい規定の電流を流す電流生成部と、一端が前記定電流回路の出力に接続されるスイッチと、一端が前記スイッチの他端に接続され、他端が接地されているコンデンサと、第1の入力が前記スイッチの他端と前記コンデンサの一端とに接続され、出力が第2の入力に接続されたオペアンプと、第1の入力に電圧が入力され第2の入力が前記オペアンプの出力に接続されたコンパレータと、を備えるピークホールド回路が実行するピークホールド方法であって、

前記コンパレータが、前記コンパレータの第1の入力に入力される電圧と、前記コンパレータの第2の入力に入力されるオペアンプの出力電圧とを比較し、この比較結果に基づいて前記スイッチを制御するステップと、

前記オペアンプが、このオペアンプの第1の入力の電圧に応じた電圧を出力するステップと、

を有する。

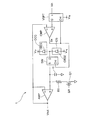

図6に示すように、比較例におけるピークホールド回路100は、一端に正極の電源電圧が入力された定電流回路CCCと、ドレインが定電流回路CCCの他端に接続されたスイッチSWとを備える。ピークホールド回路100は、更に、一端がスイッチSWのソースと接続されたコンデンサCと、コンデンサCの一端に接続された抵抗R1と、ドレインが抵抗R1の他端に接続されソースが接地に接続されゲートにリセット信号SRが入力されるNMOSトランジスタQ1とを備える。

そこで、以下では、高速応答の信号を高精度にピークホールドすることを可能とする本実施形態に係るピークホールド回路およびピークホールド方法について説明する。以下、本発明に係る実施形態について図面に基づいて説明する。

更に、ピークホールド回路1は、第1の入力(非反転入力端子)がスイッチSWの他端S、コンデンサCの一端及び抵抗R1の一端に接続され出力が第2の入力(反転入力端子)に接続されたオペアンプAMPを備える。

VSFT 電圧シフト部

CMP コンパレータ

SW スイッチ

CCC 定電流回路

CG 電流生成部

CRD1 第1の定電流ダイオード

CRD2 第2の定電流ダイオード

C コンデンサ

R1、R2、R3 抵抗

Q1、Q2、Q3、Q4 NMOSトランジスタ

AMP オペアンプ

RIN 第1の抵抗

ROFF 第2の抵抗

SP 切替部

INV インバータ

VGN、VGN2、VGN3 基準電圧源

Claims (11)

- 一端に正極の電源電圧が入力され、他端から所定の定電流を出力する定電流回路と、

一端が前記定電流回路の出力に接続され、他端に負極の電源電圧が入力され、前記定電流回路が出力する定電流より小さい規定の電流を流す電流生成部と、

一端が前記定電流回路の出力に接続されるスイッチと、

一端が前記スイッチの他端に接続され、他端が接地されているコンデンサと、

第1の入力が前記スイッチの他端と前記コンデンサの一端とに接続され、出力が第2の入力に接続されたオペアンプと、

第1の入力に入力される電圧と、第2の入力に入力されるオペアンプの出力電圧とを比較し、この比較結果に基づいて前記スイッチを制御するコンパレータと、

を備えるピークホールド回路。 - 外部から入力された入力電圧が、所定の電圧未満の場合、前記入力電圧を前記所定の電圧だけマイナス側にシフトさせた電圧を前記コンパレータの前記第1の入力に出力し、前記入力電圧が前記所定の電圧以上の場合、前記入力電圧に応じた電圧を前記コンパレータの前記第1の入力に出力する電圧シフト部を更に備える

請求項1に記載のピークホールド回路。 - 前記定電流回路は、

ドレインに前記正極の電源電圧が入力され、ゲートに第2の基準電位が入力され、ソースが前記スイッチの一端及び前記電流生成部の一端に接続された定電流用MOSトランジスタを備え、

前記電流生成部が供給する電流の大きさは、前記定電流用MOSトランジスタが動作状態を維持できる範囲の電流値である

請求項1または2に記載のピークホールド回路。 - 前記電流生成部が供給する電流の大きさは、前記定電流用MOSトランジスタが動作状態を維持できる範囲の電流の下限値である

請求項3に記載のピークホールド回路。 - 前記定電流回路は、アノードに前記正極の電源電圧が入力され、カソードが前記スイッチの一端及び前記電流生成部の一端に接続された第1の定電流ダイオードである

請求項1または2に記載のピークホールド回路。 - 前記電流生成部は、アノードが前記定電流回路の出力に接続され、カソードが接地された第2の定電流ダイオードである

を備える請求項1から5のいずれか一項に記載のピークホールド回路。 - 前記電圧シフト部は、

一端から前記入力電圧が入力される第1の抵抗と、

一端が前記第1の抵抗の他端に接続され、前記第1の抵抗より抵抗値が小さい第2の抵抗と、

前記コンパレータの第1の入力の電圧が前記オペアンプの出力電圧未満の場合、前記第2の抵抗の他端に負の基準電位が入力されるように制御し、前記コンパレータの第1の入力の電圧が前記オペアンプの出力電圧以上の場合、前記第2の抵抗の他端に負の基準電位が入力されないように制御する切替部と、

を備える請求項2に記載のピークホールド回路。 - 前記切替部は、前記コンパレータの出力電圧を反転して出力するインバータと、ゲートが前記インバータの出力に接続され、ソースに前記負の基準電位が入力され、ドレインが前記第2の抵抗の他端に接続されたシフト用MOSトランジスタと、を備える

請求項7に記載のピークホールド回路。 - ドレインが前記コンデンサの一端と前記オペアンプの第1の入力とに接続され、ソースが接地され、ゲートに供給されるリセット信号に応じて制御されるスルー用MOSトランジスタを更に備える

請求項1から8のいずれか一項に記載のピークホールド回路。 - 前記スイッチは、前記コンパレータの第1の入力に入力される電圧が前記オペアンプの出力以上の場合、前記コンデンサの一端と前記定電流回路の出力との間を導通させる

請求項1から9のいずれか一項に記載のピークホールド回路。 - 一端に正極の電源電圧が入力され、他端から所定の定電流を出力する定電流回路と、一端が前記定電流回路の出力に接続され、他端に負極の電源電圧が入力され、前記定電流回路が出力する定電流より小さい規定の電流を流す電流生成部と、一端が前記定電流回路の出力に接続されるスイッチと、一端が前記スイッチの他端に接続され、他端が接地されているコンデンサと、第1の入力が前記スイッチの他端と前記コンデンサの一端とに接続され、出力が第2の入力に接続されたオペアンプと、第1の入力に電圧が入力され第2の入力が前記オペアンプの出力に接続されたコンパレータと、を備えるピークホールド回路が実行するピークホールド方法であって、

前記コンパレータが、前記コンパレータの第1の入力に入力される電圧と、前記コンパレータの第2の入力に入力されるオペアンプの出力電圧とを比較し、この比較結果に基づいて前記スイッチを制御するステップと、

前記オペアンプが、前記オペアンプの第1の入力の電圧に応じた電圧を出力するステップと、

を有するピークホールド方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013257299A JP6223805B2 (ja) | 2013-12-12 | 2013-12-12 | ピークホールド回路およびピークホールド方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2013257299A JP6223805B2 (ja) | 2013-12-12 | 2013-12-12 | ピークホールド回路およびピークホールド方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2015114238A true JP2015114238A (ja) | 2015-06-22 |

| JP6223805B2 JP6223805B2 (ja) | 2017-11-01 |

Family

ID=53528158

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013257299A Active JP6223805B2 (ja) | 2013-12-12 | 2013-12-12 | ピークホールド回路およびピークホールド方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP6223805B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019118079A (ja) * | 2017-12-27 | 2019-07-18 | 株式会社クボタ | 端末装置 |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2838585B2 (ja) | 1990-09-19 | 1998-12-16 | 株式会社西日本流体技研 | 回流水槽の定在波打ち消し装置 |

| US11527774B2 (en) | 2011-06-29 | 2022-12-13 | Space Charge, LLC | Electrochemical energy storage devices |

| US9853325B2 (en) | 2011-06-29 | 2017-12-26 | Space Charge, LLC | Rugged, gel-free, lithium-free, high energy density solid-state electrochemical energy storage devices |

| US11996517B2 (en) | 2011-06-29 | 2024-05-28 | Space Charge, LLC | Electrochemical energy storage devices |

| WO2019173626A1 (en) | 2018-03-07 | 2019-09-12 | Space Charge, LLC | Thin-film solid-state energy-storage devices |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01141366A (ja) * | 1987-11-27 | 1989-06-02 | Matsushita Electric Ind Co Ltd | ピーク検出回路 |

| JPH114033A (ja) * | 1997-06-11 | 1999-01-06 | Fujitsu Ltd | 発光素子駆動回路 |

| JPH11242059A (ja) * | 1998-02-26 | 1999-09-07 | Fujitsu Ten Ltd | ピークホールド回路 |

| JP2002082139A (ja) * | 2000-09-05 | 2002-03-22 | Advantest Corp | 電源電圧監視回路 |

| JP2004198335A (ja) * | 2002-12-20 | 2004-07-15 | Seiko Instruments Inc | 電圧検出回路 |

| JP2007170881A (ja) * | 2005-12-20 | 2007-07-05 | Nippon Inter Electronics Corp | 電圧監視回路、ゲートドライバー回路およびスイッチング電源回路 |

-

2013

- 2013-12-12 JP JP2013257299A patent/JP6223805B2/ja active Active

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01141366A (ja) * | 1987-11-27 | 1989-06-02 | Matsushita Electric Ind Co Ltd | ピーク検出回路 |

| JPH114033A (ja) * | 1997-06-11 | 1999-01-06 | Fujitsu Ltd | 発光素子駆動回路 |

| JPH11242059A (ja) * | 1998-02-26 | 1999-09-07 | Fujitsu Ten Ltd | ピークホールド回路 |

| JP2002082139A (ja) * | 2000-09-05 | 2002-03-22 | Advantest Corp | 電源電圧監視回路 |

| JP2004198335A (ja) * | 2002-12-20 | 2004-07-15 | Seiko Instruments Inc | 電圧検出回路 |

| JP2007170881A (ja) * | 2005-12-20 | 2007-07-05 | Nippon Inter Electronics Corp | 電圧監視回路、ゲートドライバー回路およびスイッチング電源回路 |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2019118079A (ja) * | 2017-12-27 | 2019-07-18 | 株式会社クボタ | 端末装置 |

| JP7071116B2 (ja) | 2017-12-27 | 2022-05-18 | 株式会社クボタ | 端末装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP6223805B2 (ja) | 2017-11-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6223805B2 (ja) | ピークホールド回路およびピークホールド方法 | |

| US20090315530A1 (en) | Pulse controlled soft start scheme for buck converter | |

| JP5405891B2 (ja) | 電源装置、制御回路、電源装置の制御方法 | |

| JP2011223829A (ja) | 負電圧チャージポンプ回路の制御回路および負電圧チャージポンプ回路、ならびにそれらを用いた電子機器およびオーディオシステム | |

| TWI435522B (zh) | 充電泵控制器及其方法 | |

| US9374007B2 (en) | DC/DC converter | |

| JP2009130879A (ja) | レベルシフト回路 | |

| KR101701613B1 (ko) | 게이트 전위 제어 회로 | |

| CN107168433B (zh) | 输出电路 | |

| JP2014117045A (ja) | チャージポンプ回路 | |

| US9791882B2 (en) | Voltage source | |

| US9559583B2 (en) | Power converter with a wave generator that filters a wave signal to generate an output voltage | |

| US9158318B2 (en) | Power supply apparatus which suprresses output voltage variation | |

| JP6458659B2 (ja) | スイッチング素子の駆動装置 | |

| JP4630165B2 (ja) | Dc−dcコンバータ | |

| JP5398422B2 (ja) | スイッチング電源装置 | |

| JP2016048490A (ja) | 電源制御回路および電源装置 | |

| US9354647B2 (en) | Adjustable reference current generating circuit and method for driving the same | |

| JP2014057404A (ja) | 過電流検出回路及び電流制限回路 | |

| JP5593104B2 (ja) | リップルコンバータ | |

| JP5881664B2 (ja) | 電源装置、制御回路、電源装置の制御方法 | |

| JP6421707B2 (ja) | 電源回路 | |

| JP2014079047A (ja) | Dc/dcコンバータ | |

| JP2017509304A (ja) | Dc/dcコンバータ及びdc/dcコンバータの駆動方法 | |

| JP2008011585A (ja) | スイッチングレギュレータ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160512 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20170216 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20170228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170317 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170905 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20171004 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6223805 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |