JP2014123733A - 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ - Google Patents

誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ Download PDFInfo

- Publication number

- JP2014123733A JP2014123733A JP2013261008A JP2013261008A JP2014123733A JP 2014123733 A JP2014123733 A JP 2014123733A JP 2013261008 A JP2013261008 A JP 2013261008A JP 2013261008 A JP2013261008 A JP 2013261008A JP 2014123733 A JP2014123733 A JP 2014123733A

- Authority

- JP

- Japan

- Prior art keywords

- integrated circuit

- die

- interface layer

- support

- dies

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H10W72/00—

-

- H10W20/01—

-

- H10W20/031—

-

- H10W70/09—

-

- H10W70/60—

-

- H10W70/611—

-

- H10W70/614—

-

- H10W70/65—

-

- H10W74/014—

-

- H10W74/019—

-

- H10W72/01304—

-

- H10W72/01325—

-

- H10W72/01351—

-

- H10W72/0198—

-

- H10W72/072—

-

- H10W72/07232—

-

- H10W72/073—

-

- H10W72/07332—

-

- H10W72/07337—

-

- H10W72/074—

-

- H10W72/241—

-

- H10W72/252—

-

- H10W72/324—

-

- H10W72/325—

-

- H10W72/352—

-

- H10W72/354—

-

- H10W74/117—

-

- H10W74/15—

-

- H10W90/00—

-

- H10W90/724—

-

- H10W90/734—

-

- H10W99/00—

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Production Of Multi-Layered Print Wiring Board (AREA)

- Wire Bonding (AREA)

- Structures Or Materials For Encapsulating Or Coating Semiconductor Devices Or Solid State Devices (AREA)

Abstract

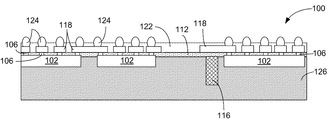

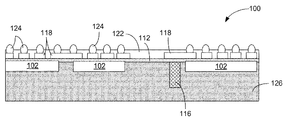

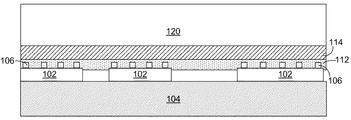

【解決手段】 本願開示の実施態様は、界面層により集積回路基板に接続された1個もしくはそれ以上のダイを有する集積回路(IC)パッケージの技術及び構成に向けられている。一実施態様において、界面層は、1個もしくはそれ以上のコンポーネント、例えばダイ及び集積回路基板、の間で面外方向に電気信号を伝えるように構成された異方性部分を包含してよい。さらに別の実施態様において、界面層は、2個のコンポーネントの間のインターコネクトとして働く異方性部分、誘電性もしくは絶縁性部分、及び誘電性もしくは絶縁性部分により包囲され、同一もしくは別のコンポーネントとの間のインターコネクトとして働く1個もしくはそれ以上のインターコネクトを包含してよい。その他の実施態様記載及び/又はクレームされてもよい。

【選択図】 図1

Description

本願開示の実施態様は、正確なコンポーネント対コンポーネントアライメントを有する集積回路(IC)パッケージの技術及び構成を表す。以下の記載において、当業者が自分体の仕事の骨子を他の当業者に伝達するために通常使用する用語を用いて、説明に役立つ実施の様々な面が述べられよう。しかしながら、記載された態様のごく一部に関して本願発明を実施してよいことは当業者には明らかであろう。実施例の完全な理解をもたらすため、説明のために、特定番号、材料及び構成が述べられる。ただし、その特定の詳細なしに本発明を実施してよいことは当業者に明らかとなろう。別の例において、実施例をわかり難くしないように、周知の態様は省略ないし単純化する。

112 界面層

122 集積回路基板

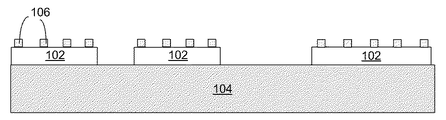

102 ダイ

106、124 インターコネクト構造

118 インターコネクト要素118

112 中間層

Claims (20)

- 集積回路基板、

ダイ、及び

前記ダイと前記集積回路基板との間に置かれた界面層、

を有する集積回路パッケージであって、

界面層は、ダイと集積回路基板との間で、界面層により形成された面に対して面外方向に電気信号を伝えるよう構成した異方性導電部分を有する、

前記集積回路パッケージ。 - 集積回路基板とダイとの間に置かれたインターコネクト構造をさらに有する請求項1に記載の集積回路パッケージであって、界面層はインターコネクト構造の一部を包囲し、インターコネクト構造はダイと集積回路基板との間に電気信号を送るように構成されている、前記集積回路パッケージ。

- 界面層が異方性導電フィルムを有する、請求項1に記載の集積回路パッケージ。

- 前記ダイは第1のダイであり、装置はさらに第2のダイを有し、界面層は対抗する第1と第2の表面を有し、第1のダイと第2のダイのうち少なくとも一方は第1の表面に接続され、集積回路基板は第2の表面に接続されている、請求項1に記載の集積回路パッケージ。

- 第1のダイを集積回路基板に接続する第1のインターコネクト構造、及び第2のダイを集積回路基板に接続する第2のインターコネクト構造をさらに有し、界面層は第1のインターコネクト構造と第2のインターコネクト構造との間に置かれている、請求項4に記載の集積回路パッケージ。

- 界面層の異方性導電部分に結合された電子部品をさらに有する請求項1に記載の装置であって、異方性導電部分は電子部品から集積回路基板へ電気信号を伝えるよう構成されている、前記装置。

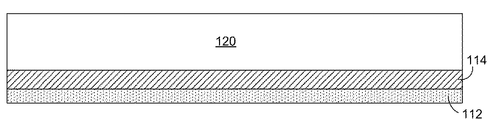

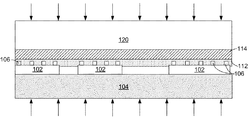

- 1個もしくはそれ以上のダイを第1の支持体上で位置決めすることすること、ただし前記1個もしくはそれ以上のダイは第1の表面と第1の表面に対抗する第2の表面を有する;

1個もしくはそれ以上のダイの第1の表面に界面層を置くこと、ただし界面層は第2の支持体に結合されている;

第1の支持体と第2の支持体との間で1個もしくはそれ以上のダイ及び界面層を一緒に圧縮すること;

1個もしくはそれ以上のダイから第1の支持体を解放すること;及び

型取り材料を1個もしくはそれ以上のダイの第2の表面に塗布すること、

を有する集積回路パッケージを製造する方法。 - 第1の支持体と第2の支持体との間の1個もしくはそれ以上のダイを圧縮している間、界面層を硬化させることをさらに含む、請求項7に記載の方法。

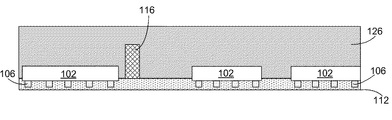

- 型取り材料を1個もしくはそれ以上のダイの第2の表面に塗布する過程は、第2の支持体を裏返すこと、及び第2の支持体が裏返される間、1個もしくはそれ以上のダイの第2の表面に型取り材料を塗布することを有する、請求項7に記載の方法。

- 第2の支持体が裏返される間に界面層に電子部品を結合することをさらに含む請求項9に記載の方法であって、型取り材料の塗布はさらに電子部品への型取り材料を塗布することをさらに含む、前記方法。

- 電子部品の界面層への結合は、電子部品を界面層の誘電性部分の上へ置くことを有し、当該方法はさらに誘電性部分を通って電子部品へ至るビアを作ることをさらに含む、請求項10に記載の方法。

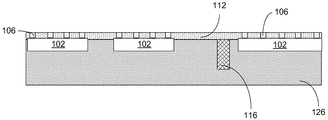

- 界面層を置く前に、1個もしくはそれ以上のダイの少なくとも1個の第1の表面に第1のインターコネクト構造を形成すること;

界面層から第2の支持体を解放すること;及び

第1のインターコネクト構造を露出させるように界面層を平坦化すること、

を含む請求項7に記載の方法。 - 界面層は、界面層によって形成された平面に対して面外方向に電気信号を伝えるように構成された異方性部分を有する、請求項7に記載の方法。

- 1個もしくはそれ以上のダイは少なくとも2個のダイを有し、界面層は前記少なくとも2個のダイの表面と結合した異方性導電フィルムを有する、請求項7に記載の方法。

- 当該方法は、異方性導電フィルムに集積回路基板を直接結合することをさらに含み、異方性導電フィルムは、集積回路基板と少なくとも2個のダイのうち1個もしくはそれ以上との間に電気信号を送るように構成されている、請求項14に記載の方法。

- マザーボード;

マザーボードに搭載されたコミュニケーションチップ;及び

マザーボードに搭載されたプロセッサ

を有するコンピューティングデバイスであって、

プロセッサもしくはコミュニケーションチップは、

集積回路基板;

ダイ;及び

ダイと集積回路基板との間に置かれた界面層

を有し、界面層は、ダイと集積回路基板との間に、界面層によって形成された平面に対して面外方向に電気信号を送るように構成された異方性導電部分を有する、

コンピューティングデバイス。 - 集積回路基板とダイとの間に配置されたインターコネクト構造をさらに有する請求項16に記載のコンピューティングデバイスであって、界面層はインターコネクト構造の一部を包囲し、インターコネクト構造はダイと集積回路基板との間に電気信号を伝えるように構成されている、コンピューティングデバイス。

- 界面層が異方性導電性フィルムを有する、請求項16に記載のコンピューティングデバイス。

- ダイは第1のダイであり、プロセッサもしくはコミュニケーションチップは第2のダイをさらに有し、界面層は対向する第1及び第2の表面を有し、第1のダイ及び第2のダイの少なくとも1個は第1の表面に接続され、集積回路基板は第2の表面に接続されている、請求項16に記載のコンピューティングデバイス。

- 界面層の異方性導電性部分に結合した電子部品をさらに有する、請求項16に記載のコンピューティングデバイスであって、異方性導電性部分は電子部品から集積回路基板に電気信号を伝えるように構成されている、コンピューティングデバイス。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US13/719,836 | 2012-12-19 | ||

| US13/719,836 US9543197B2 (en) | 2012-12-19 | 2012-12-19 | Package with dielectric or anisotropic conductive (ACF) buildup layer |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017054431A Division JP2017108189A (ja) | 2012-12-19 | 2017-03-21 | 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2014123733A true JP2014123733A (ja) | 2014-07-03 |

Family

ID=50929961

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2013261008A Pending JP2014123733A (ja) | 2012-12-19 | 2013-12-18 | 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ |

| JP2017054431A Pending JP2017108189A (ja) | 2012-12-19 | 2017-03-21 | 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017054431A Pending JP2017108189A (ja) | 2012-12-19 | 2017-03-21 | 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US9543197B2 (ja) |

| JP (2) | JP2014123733A (ja) |

| CN (2) | CN107195614A (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9524958B2 (en) * | 2013-06-27 | 2016-12-20 | STATS ChipPAC Pte. Ltd. | Semiconductor device and method of individual die bonding followed by simultaneous multiple die thermal compression bonding |

| US9791470B2 (en) * | 2013-12-27 | 2017-10-17 | Intel Corporation | Magnet placement for integrated sensor packages |

| US10109784B2 (en) * | 2016-03-01 | 2018-10-23 | Qualcomm Incorporated | Sensor device |

| WO2019106846A1 (ja) * | 2017-12-01 | 2019-06-06 | 日立化成株式会社 | 半導体装置の製造方法、仮固定材用樹脂組成物、及び仮固定材用積層フィルム |

| US11805602B2 (en) * | 2020-09-04 | 2023-10-31 | Intel Corporation | Chip assemblies |

| US11996384B2 (en) | 2020-12-15 | 2024-05-28 | Pulseforge, Inc. | Method and apparatus for debonding temporarily bonded wafers in wafer-level packaging applications |

| US20230078395A1 (en) * | 2021-09-10 | 2023-03-16 | Intel Corporation | Devices and methods to minimize die shift in embedded heterogeneous architectures |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01302734A (ja) * | 1988-05-30 | 1989-12-06 | Canon Inc | 電気回路装置 |

| WO2001042893A1 (en) * | 1999-12-10 | 2001-06-14 | Hitachi, Ltd | Semiconductor module |

| JP2004128286A (ja) * | 2002-10-04 | 2004-04-22 | Sony Corp | チップ状電子部品及びその製造方法、その製造に用いる疑似ウェーハ及びその製造方法、並びに実装構造 |

| JP2007165928A (ja) * | 2007-02-19 | 2007-06-28 | Renesas Technology Corp | 半導体モジュール |

| WO2007148724A1 (ja) * | 2006-06-23 | 2007-12-27 | Hitachi Chemical Company, Ltd. | 半導体デバイスの製造方法及び接着フィルム |

| JP2009527893A (ja) * | 2005-11-29 | 2009-07-30 | エヌエックスピー ビー ヴィ | 柔軟介入物接触を有するバンプなしフリップチップ組立体 |

| US20110316146A1 (en) * | 2010-06-24 | 2011-12-29 | Stats Chippac, Ltd. | Semiconductor Device and Method of Forming Anisotropic Conductive Film Between Semiconductor Die and Build-Up Interconnect Structure |

| JP2012109306A (ja) * | 2010-11-15 | 2012-06-07 | Shinko Electric Ind Co Ltd | 半導体パッケージの製造方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0327043U (ja) * | 1989-07-26 | 1991-03-19 | ||

| US6342434B1 (en) * | 1995-12-04 | 2002-01-29 | Hitachi, Ltd. | Methods of processing semiconductor wafer, and producing IC card, and carrier |

| TW449844B (en) | 1997-05-17 | 2001-08-11 | Hyundai Electronics Ind | Ball grid array package having an integrated circuit chip |

| KR100514558B1 (ko) | 1998-09-09 | 2005-09-13 | 세이코 엡슨 가부시키가이샤 | 반도체 장치 및 그 제조방법, 회로기판 및 전자기기 |

| JP2001085715A (ja) * | 1999-09-09 | 2001-03-30 | Canon Inc | 半導体層の分離方法および太陽電池の製造方法 |

| KR20030060898A (ko) * | 2000-09-25 | 2003-07-16 | 이비덴 가부시키가이샤 | 반도체소자,반도체소자의 제조방법,다층프린트배선판 및다층프린트배선판의 제조방법 |

| DE60325669D1 (de) * | 2002-05-17 | 2009-02-26 | Semiconductor Energy Lab | Verfahren zum Transferieren eines Objekts und Verfahren zur Herstellung eines Halbleiterbauelements |

| US20060013680A1 (en) * | 2004-07-16 | 2006-01-19 | Tessera, Inc. | Chip handling methods and apparatus |

| JP4776188B2 (ja) * | 2004-08-03 | 2011-09-21 | 古河電気工業株式会社 | 半導体装置製造方法およびウエハ加工用テープ |

| JP4979918B2 (ja) * | 2004-09-24 | 2012-07-18 | ボンドテック株式会社 | 加圧方法及び加圧装置 |

| US20060196600A1 (en) * | 2005-03-03 | 2006-09-07 | Gi-Jung Nam | Apparatus and method for bonding anisotropic conductive film using laser beam |

| JP4473807B2 (ja) | 2005-10-27 | 2010-06-02 | パナソニック株式会社 | 積層半導体装置及び積層半導体装置の下層モジュール |

| US20110228506A1 (en) * | 2006-02-10 | 2011-09-22 | Kong-Chen Chen | Electronic assembly with detachable components |

| US7871865B2 (en) * | 2007-01-24 | 2011-01-18 | Analog Devices, Inc. | Stress free package and laminate-based isolator package |

| JP4361572B2 (ja) * | 2007-02-28 | 2009-11-11 | 株式会社新川 | ボンディング装置及び方法 |

| JP5460984B2 (ja) * | 2007-08-17 | 2014-04-02 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| US8049292B2 (en) * | 2008-03-27 | 2011-11-01 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and method for manufacturing semiconductor device |

| JP5496598B2 (ja) * | 2008-10-31 | 2014-05-21 | 信越化学工業株式会社 | シリコン薄膜転写絶縁性ウェーハの製造方法 |

| JP2010177604A (ja) * | 2009-02-02 | 2010-08-12 | Renesas Electronics Corp | 半導体製造方法及び製造装置 |

| US8267143B2 (en) * | 2009-04-16 | 2012-09-18 | Suss Microtec Lithography, Gmbh | Apparatus for mechanically debonding temporary bonded semiconductor wafers |

| JP5732631B2 (ja) * | 2009-09-18 | 2015-06-10 | ボンドテック株式会社 | 接合装置および接合方法 |

| TWI534938B (zh) * | 2010-02-25 | 2016-05-21 | 尼康股份有限公司 | Substrate separation device, manufacturing method of semiconductor device, load lock device, substrate bonding device and substrate separation method |

| US8435804B2 (en) * | 2010-12-29 | 2013-05-07 | Gtat Corporation | Method and apparatus for forming a thin lamina |

| JP6149277B2 (ja) * | 2011-03-30 | 2017-06-21 | ボンドテック株式会社 | 電子部品実装方法、電子部品実装システムおよび基板 |

| CN102310262A (zh) * | 2011-08-23 | 2012-01-11 | 南通富士通微电子股份有限公司 | 加热块装置 |

| JP6043058B2 (ja) * | 2011-11-07 | 2016-12-14 | デクセリアルズ株式会社 | 接続装置、接続構造体の製造方法、チップスタック部品の製造方法及び電子部品の実装方法 |

-

2012

- 2012-12-19 US US13/719,836 patent/US9543197B2/en not_active Expired - Fee Related

-

2013

- 2013-12-18 JP JP2013261008A patent/JP2014123733A/ja active Pending

- 2013-12-18 CN CN201710357074.4A patent/CN107195614A/zh active Pending

- 2013-12-18 CN CN201310697943.XA patent/CN103887278B/zh not_active Expired - Fee Related

-

2017

- 2017-01-09 US US15/401,717 patent/US20170179099A1/en not_active Abandoned

- 2017-03-21 JP JP2017054431A patent/JP2017108189A/ja active Pending

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH01302734A (ja) * | 1988-05-30 | 1989-12-06 | Canon Inc | 電気回路装置 |

| WO2001042893A1 (en) * | 1999-12-10 | 2001-06-14 | Hitachi, Ltd | Semiconductor module |

| JP2004128286A (ja) * | 2002-10-04 | 2004-04-22 | Sony Corp | チップ状電子部品及びその製造方法、その製造に用いる疑似ウェーハ及びその製造方法、並びに実装構造 |

| JP2009527893A (ja) * | 2005-11-29 | 2009-07-30 | エヌエックスピー ビー ヴィ | 柔軟介入物接触を有するバンプなしフリップチップ組立体 |

| WO2007148724A1 (ja) * | 2006-06-23 | 2007-12-27 | Hitachi Chemical Company, Ltd. | 半導体デバイスの製造方法及び接着フィルム |

| JP2007165928A (ja) * | 2007-02-19 | 2007-06-28 | Renesas Technology Corp | 半導体モジュール |

| US20110316146A1 (en) * | 2010-06-24 | 2011-12-29 | Stats Chippac, Ltd. | Semiconductor Device and Method of Forming Anisotropic Conductive Film Between Semiconductor Die and Build-Up Interconnect Structure |

| JP2012109306A (ja) * | 2010-11-15 | 2012-06-07 | Shinko Electric Ind Co Ltd | 半導体パッケージの製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US9543197B2 (en) | 2017-01-10 |

| CN103887278A (zh) | 2014-06-25 |

| CN107195614A (zh) | 2017-09-22 |

| US20140167217A1 (en) | 2014-06-19 |

| JP2017108189A (ja) | 2017-06-15 |

| CN103887278B (zh) | 2017-09-22 |

| US20170179099A1 (en) | 2017-06-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| USRE50796E1 (en) | Semiconductor package having spacer layer | |

| US11075166B2 (en) | Microelectronic structures having multiple microelectronic devices connected with a microelectronic bridge embedded in a microelectronic substrate | |

| JP2017108189A (ja) | 誘電性又は異方性導電性フィルム(acf)ビルドアップレイヤーを有するパッケージ | |

| JP6293918B2 (ja) | 受動マイクロ電子デバイスをパッケージ本体内部に配置したマイクロ電子パッケージ | |

| JP6124164B2 (ja) | 低コストなパッケージの反りの解決法 | |

| CN112310050A (zh) | 多管芯超细节距片块架构和制造方法 | |

| TW201430973A (zh) | 用於具有晶粒對中介層晶圓第一接合的半導體裝置封裝的方法和系統 | |

| TWI872086B (zh) | 超薄橋接與多晶粒超細間距補塊架構及其製造方法 | |

| TWI548009B (zh) | 用於針對晶圓上晶片組件的暫時性晶圓模製的方法 | |

| US20250192101A1 (en) | No mold shelf package design and process flow for advanced package architectures | |

| US12027496B2 (en) | Film in substrate for releasing z stack-up constraint | |

| WO2017039583A1 (en) | Use of sacrificial material to compensate for thickness variation in microelectronic substrates |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20140902 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20141201 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20141204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20141224 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20150128 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150227 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150929 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151224 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160628 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160926 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20161122 |