JP2010141684A - 波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 - Google Patents

波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 Download PDFInfo

- Publication number

- JP2010141684A JP2010141684A JP2008316955A JP2008316955A JP2010141684A JP 2010141684 A JP2010141684 A JP 2010141684A JP 2008316955 A JP2008316955 A JP 2008316955A JP 2008316955 A JP2008316955 A JP 2008316955A JP 2010141684 A JP2010141684 A JP 2010141684A

- Authority

- JP

- Japan

- Prior art keywords

- output

- transistor

- differential

- current source

- pair

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/156—Arrangements in which a continuous pulse train is transformed into a train having a desired pattern

- H03K5/1565—Arrangements in which a continuous pulse train is transformed into a train having a desired pattern the output pulses having a constant duty cycle

Landscapes

- Physics & Mathematics (AREA)

- Nonlinear Science (AREA)

- Pulse Circuits (AREA)

- Manipulation Of Pulses (AREA)

Abstract

【課題】デューティ制御バッファの出力信号のパルスが消滅してしまうという問題を回避する回路を提供する。

【解決手段】入力信号IN1、INB1を受けるデューティ制御バッファ10と、デューティ制御バッファの出力OUT1、OUTB1を受け、デューティの誤差を検出して制御信号VCNT1、VCNTB1を生成するデューティ制御電圧発生部20を備える。デューティ制御バッファ10は、入力信号を差動で受ける第1の差動対と第2の差動対を備えた差動段と、第1の差動対の出力対と第2の差動対の出力対がそれぞれ接続され、前記第1、第2の差動対の出力対と電源との間に接続された負荷素子対と、第1、第2の差動対にそれぞれ駆動電流を供給する電流源段とを備え、第1の差動対のトランジスタ対の電流駆動能力が異なり、第2の差動対のトランジスタ対の電流駆動能力が異なる不平衡差動対よりなる。

【選択図】図2

【解決手段】入力信号IN1、INB1を受けるデューティ制御バッファ10と、デューティ制御バッファの出力OUT1、OUTB1を受け、デューティの誤差を検出して制御信号VCNT1、VCNTB1を生成するデューティ制御電圧発生部20を備える。デューティ制御バッファ10は、入力信号を差動で受ける第1の差動対と第2の差動対を備えた差動段と、第1の差動対の出力対と第2の差動対の出力対がそれぞれ接続され、前記第1、第2の差動対の出力対と電源との間に接続された負荷素子対と、第1、第2の差動対にそれぞれ駆動電流を供給する電流源段とを備え、第1の差動対のトランジスタ対の電流駆動能力が異なり、第2の差動対のトランジスタ対の電流駆動能力が異なる不平衡差動対よりなる。

【選択図】図2

Description

本発明は、波形合成回路及び方法と、該波形合成回路を備えたデューティ補正回路及びデューティ補正方法に関する。

遅延同期ループ(Delay Lock Loop)等に用いられるデューティ補正回路として、例えば図1に示すような構成が知られている。図1は、特許文献1の図2に基づくものである。図1において、回路ブロック、信号名、参照符号等は特許文献1の図2と相違している(rst信号、reset端子は省略されている)。

図1を参照すると、相補の入力信号IN1、INB1を差動入力するデューティ制御バッファ(Duty control buffer)10と、デューティ制御バッファ10から差動で出力される信号OUT1、OUTB1を入力し、OUT1、OUTB1のデューティ誤差を感知し、デューティ誤差に対応する第1、第2のデューティ制御電圧信号VCNT1、VCNTB1を差動で出力するデューティ制御電圧発生部(Duty control voltage generator)20とを備えている。デューティ制御電圧発生部20において、OUT1、OUTB1の電位を積分し、デューティが崩れた分(Highレベル期間とLowレベル期間の時間差)を第1、第2のデューティ制御電圧信号VCNT1、VCNTBの電位差に変換し、デューティ制御バッファ10では、第1、第2のデューティ制御電圧信号VCNT1、VCNTB1の電位差をOUT1とOUTB1それぞれの中心電圧(オフセット)の差電圧に変換することでデューティの補正が行われる。

以下に本発明による分析を与える。なお、以下の問題点は、比較例として詳細に説明される。

図1に示した構成において、デューティ制御バッファの出力信号OUT1、OUTB1の波形鈍り(立ち上がり、立ち下がりの遷移時間)等が小さい場合、デューティの誤差を補正するために、OUT1、OUTB1の中心電圧の電位差を大きくしても、デューティを充分に補正できず、OUT1、OUTB1のパルス自体が消滅してしまう場合がある。

また、OUT1、OUTB1を差動で受ける差動回路(図1では不図示)において、製造バラツキ等で発生する差動対のオフセットによってデューティの劣化が生じる。

本発明は、上記した1つ又は複数の問題を解決するものである。

本願で開示される発明は、概略以下の構成とされる。

本発明によれば、入力信号を受け、前記入力信号の遷移に応じた立ち上がり遷移を遅らせるか速めた第1の信号を生成する第1の回路と、前記入力信号を受け、前記入力信号の遷移に応じた立ち下がり遷移を遅らせるか速めた第2の信号を生成する第2の回路と、

を備え、前記第1の信号と前記第2の信号を合成した信号波形を出力する。本発明においては、入力信号を受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がりの少なくとも1方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に所定の大小関係を有する第1の差動出力信号を生成する第1の差動回路と、前記入力信号を第1の差動回路と共通に受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がり遷移のうち前記一方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に、前記第1の差動出力信号における大小関係とは逆の大小関係を有する第2の差動出力信号を生成する第2の差動回路と、

を備え、前記第1の差動出力信号と前記第2の差動出力信号の正転出力信号同士と反転出力信号同士を合成した信号波形を出力する回路が提供される。

を備え、前記第1の信号と前記第2の信号を合成した信号波形を出力する。本発明においては、入力信号を受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がりの少なくとも1方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に所定の大小関係を有する第1の差動出力信号を生成する第1の差動回路と、前記入力信号を第1の差動回路と共通に受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がり遷移のうち前記一方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に、前記第1の差動出力信号における大小関係とは逆の大小関係を有する第2の差動出力信号を生成する第2の差動回路と、

を備え、前記第1の差動出力信号と前記第2の差動出力信号の正転出力信号同士と反転出力信号同士を合成した信号波形を出力する回路が提供される。

本発明によれば、デューティ補正において、出力信号のパルス自体が消滅してしまうという問題を回避することができる。

また本発明によれば、デューティが補正された出力信号を差動で受ける差動回路のオフセットによってデューティの劣化が生じるという問題を回避することができる。

本発明の実施の形態について説明する。本発明においては、入力信号(IN1、INB1)を受けるデューティ制御バッファは、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がりの少なくとも1方の遷移に関して、正転出力信号(OUT1)の前記遷移の時間と反転出力信号(OUTB1)の前記遷移の時間の間に所定の大小関係を有する第1の差動出力信号を生成する第1の差動対(NA1、NA2)と、前記入力信号を第1の差動対と共通に受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がり遷移のうち少なくとも前記一方の遷移に関して、正転出力信号(OUT1)の前記遷移の時間と反転出力信号(OUTB1)の前記遷移の時間の間に、前記第1の差動出力信号における大小関係とは逆の大小関係を有する第2の差動出力信号を生成する第2の差動対(NB1、NB2)と、を備え、前記第1の差動出力信号と前記第2の差動出力信号の正転出力信号同士と反転出力信号同士を合成した信号波形を出力する。第1、第2の差動対の共通接続された出力対と電源との間に接続された負荷素子対(RL11、RL12)と、前記第1、第2の差動対に対して制御信号(VCNT1、VCNTB1)に応じたそれぞれ駆動電流を供給する電流源段とを備えている。制御信号は、OUT1/OUTB1を受け、デューティを補正するための電圧を生成するデューティ補正電圧生成部から出力され、デューティ誤差に対応した電圧が供給される。

第1、第2の差動対は、不平衡差動対とされ、例えばトランジスタ対の電流駆動能力が異なるとされる。第1の差動対(NA1、NA2)が、出力の立ち下がり遷移に関して、正転出力信号(OUT1)の遷移時間を反転出力信号(OUTB1)の遷移時間に対して遅らせる場合、第2の差動対(NB1、NB2)は、出力の立ち上がり遷移に関して、正転出力信号の遷移時間を反転出力信号の遷移時間に対して遅らせる。

まず、本発明の比較例を説明しておく。図2は、図1のデューティ制御バッファ10の出力に信号分配用のデストリビューションバッファ(Distribution buffer)30を接続した図である。なお、デストリビューションバッファ30は特許文献1には図示されない。デストリビューションバッファ30は、デューティ制御バッファ10の出力OUT1、OUTB1を差動で受けOUT2、OUTB2を差動で出力する。

図3に、図2のデューティ制御バッファの構成例(比較例)を示す。なお、図3は、本発明者によって、本発明との比較のために、作成されたものである。図3を参照すると、比較例のデューティ制御バッファは、一端がGND(グランド)に接続された定電流源ICS1と、共通に接続されたソースが定電流源ICS1の他端に接続されゲートが入力端子IN1、INB1にそれぞれ接続されたNMOSトランジスタN1、N2と、NMOSトランジスタN1、N2のドレインと電源VDD間にそれぞれ接続された抵抗(負荷抵抗)RL1、RL2(抵抗値は等しい)と、ソースがGNDに共通に接続され、ドレインがNMOSトランジスタN1、N2のドレインにそれぞれ接続され、ゲートが端子VCNTB1、VCNT1に接続されたNMOSトランジスタN7、N8とを備え、抵抗RL1と、NMOSトランジスタN1、N7のドレインの接続点と、抵抗RL2と、NMOSトランジスタN2、N8のドレインの接続点は、出力端子OUTB1、OUTBにそれぞれ接続されている。

NMOSトランジスタN1、N2は差動対を構成し、出力OUT1は入力IN1と同相、出力OUTB1は入力INB1と同相となる。すなわち、IN1がHigh、INB1がLowのとき、OUT1=High、OUTB1=Lowとなる。IN1がLow、INB1がHighのとき、OUT1=Low、OUTB1=Highとなる。

NMOSトランジスタN7、N8はそれぞれ負荷抵抗RL1、RL2に接続された電流源を構成し、ゲートにVCNTB1、VCNT1の値に応じて、OUTB1、OUT1のオフセット(振幅の中心電圧)を可変させる。IN1がHighのとき、NMOSトランジスタN1はオンし、抵抗RL1には、NMOSトランジスタN1のドレイン電流ID1と、VCNTB1をゲートに受けるNMOSトランジスタN7のドレイン電流ID7を合わせた電流が流れ、OUTB1には、電源電圧VDDから抵抗RL1による電圧降下分差し引いた電圧VDD−RL1×(ID1+ID7)がLowレベル出力電圧(VOL)として現れる。

IN1がLowのとき、NMOSトランジスタN1はオフし、抵抗RL1には、VCNTB1をゲートに受けるNMOSトランジスタN7のドレイン電流ID7が流れ、OUTB1には、電源電圧VDDから抵抗RL1による電圧降下分差し引いた電圧VDD−RL1×ID7がHighレベル出力電圧(VOH)として現れる。

INB1がHighのとき、NMOSトランジスタN2はオンし、抵抗RL2には、NMOSトランジスタN2のドレイン電流ID2と、VCNT1をゲートに受けるNMOSトランジスタN8のドレイン電流ID8を合わせた電流が流れ、OUT1には、電源電圧VDDから抵抗RL2による電圧降下分差し引いた電圧VDD−RL2×(ID2+ID8)がLowレベル出力電圧(VOL)として現れる。

INB1がLowのとき、NMOSトランジスタN2はオフし、抵抗RL2には、VCNT1をゲートに受けるNMOSトランジスタN8のドレイン電流ID8が流れ、OUT1には、電源電圧VDDから抵抗RL2による電圧降下分差し引いた電圧VDD−RL2×ID8がHighレベル出力電圧(VOH)として現れる。

OUT1について、

VOH=VDD−RL2×(ID8)

VOL=VDD−RL2×(ID2+ID8)、

OUTB1について、

VOH=VDD−RL1×(ID7)

VOL=VDD−RL1×(ID1+ID7)

VOH=VDD−RL2×(ID8)

VOL=VDD−RL2×(ID2+ID8)、

OUTB1について、

VOH=VDD−RL1×(ID7)

VOL=VDD−RL1×(ID1+ID7)

VOHとVOLの差電圧ΔV=VOH−VOL、

中心電圧VC=(VOH+VOL)/2

を用いると、出力のHighレベル出力電圧VOHとLowレベル出力電圧VOLは以下のように表される。

中心電圧VC=(VOH+VOL)/2

を用いると、出力のHighレベル出力電圧VOHとLowレベル出力電圧VOLは以下のように表される。

VOH=VC+ΔV/2、

VOL=VC―ΔV/2

VOL=VC―ΔV/2

デューティ制御バッファ10は、デューティ制御電圧信号VCNT1、VCNTB1間の差電圧をOUT1とOUTB1それぞれの中心電圧VC(OUT1)、VC(OUTB1)の差電圧に変換する。すなわち、VCNT1、VCNTB1の値に対応して、OUT1とOUTB1にオフセットを与える。

OUT1とOUTB1のそれぞれの中心電圧VCに差電圧が発生すると、OUT1、OUTB1のそれぞれが持つ波形鈍り(立ち上がり時間、立ち下がり時間)によって、OUT1、OUTB1が時間軸上で互いにクロスする点(タイミング)が変動する。デューティ制御バッファ10とデューティ制御電圧発生部20において、OUT1とOUTB1のデューティが揃うまで、すなわち、VCNT1とVCNTB1の電位差がなくなるまで、帰還制御が行なわれる。

(a) VCNTB1>VCNT1の場合、NMOSトランジスタN7のドレイン電流ID7は、NMOSトランジスタN8のドレイン電流ID8よりも大きい。したがって、ドレイン電流ID7による抵抗RL1の電圧降下のほうが、ドレイン電流ID8による抵抗RL2の電圧降下よりも大きくなり、OUTB1のHighレベル出力電圧VOHは、OUT1のHighレベル出力電圧VOHよりも低くなり、また、OUTB1のLowレベル出力電圧VOLは、OUT1のLowレベル出力電圧VOLよりも低くなる。すなわち、OUTB1の中心電圧VC(OUT1)は、OUT1の中心電圧VC(OUTB1)よりも低くなる。

(b) VCNTB1<VCNT1の場合、NMOSトランジスタN8のドレイン電流ID8は、NMOSトランジスタN7のドレイン電流ID7よりも大きい。ドレイン電流ID8による抵抗RL2の電圧降下のほうが、ドレイン電流ID7による抵抗RL1の電圧降下よりも大きくなり、OUTB1のHighレベル出力電圧VOHは、OUT1のHighレベル出力電圧VOHよりも高くなり、OUTB1のLowレベル出力電圧VOLは、OUT1のLowレベル出力電圧VOLよりも高くなる。すなわち、OUTB1の中心電圧VC(OUTB1)は、OUT1の中心電圧VC(OUT1)よりも高くなる。

図4は、図2のデューティ制御電圧発生部20の構成例を示す図である。デューティ制御電圧発生部20は、OUT1、OUTB1の電位をそれぞれ積分し、デューティが崩れた分(HighレベルとLowレベルの時間期間(時間幅)の差)をVCNT1、VCNTB1の電位差に変換する。デューティ制御電圧発生部20は、一端がGNDに接続された定電流源ICS2と、共通接続されたソースが定電流源ICS2の他端に接続され、ゲートが端子OUT1、OUTB1にそれぞれ接続されたNMOSトランジスタN3、N4と、電源VDDにソースが接続されドレインとゲートが接続され、その接続点がNMOSトランジスタN3のドレインに接続されたPMOSトランジスタP1と、電源VDDにソースが接続されドレインとゲートが接続され、その接続点がNMOSトランジスタN4のドレインに接続されたPMOSトランジスタP2と、電源VDDにソースが接続され、ゲートがPMOSトランジスタP1のゲートに接続されたPMOSトランジスタP3と、電源VDDにソースが接続され、ゲートがPMOSトランジスタP2のゲートに接続されたPMOSトランジスタP4と、PMOSトランジスタP3のドレインとGND間に並列に接続された容量C1と抵抗RL3と、PMOSトランジスタP4のドレインとGND間に並列に接続された容量C2と抵抗RL4と、を備えている。容量C1とC2は容量値が等しく、抵抗RL3、RL4の抵抗値は等しい。PMOSトランジスタP1、P3は第1のカレントミラーを構成し、NMOSトランジスタN3のドレイン電流のミラー電流がPMOSトランジスタP3のドレインから抵抗RL3に流れる。PMOSトランジスタP2、P4は第2のカレントミラーを構成し、NMOSトランジスタN4のドレイン電流のミラー電流がPMOSトランジスタP4のドレインから抵抗RL4に流れる。抵抗RL3、RL4の端子間電圧を蓄積する容量C1、C2の端子電圧がVCNT1、VCNTB1としてデューティ制御バッファ10への第1、第2のデューティ制御電圧として供給される。

OUT1のHighレベル期間がOUTB1のHighレベル期間(OUT1のLowレベル期間)よりも長い場合(デューティ>50%)、OUT1とOUTB1のHighレベル期間の差に対応する積分結果が、VCNT1、VCNTB1間に生成され、VCNTB1<VCNT1となる。前述したように、VCNTB1<VCNT1のとき、デューティ制御バッファ10(図2参照)の出力OUTB1の中心電圧は、OUT1の中心電圧よりも高くなる。すなわち、抵抗RL2の電圧降下の増大により、OUT1のHighレベル出力電圧、Lowレベル出力電圧はともに低くなり、抵抗RL1の電圧降下の減少により、OUTB1のHighレベル出力電圧、Lowレベル出力電圧はともに高くなる。このため、OUTB1のHighレベルとOUT1のLowレベルの電位差は拡大し、OUT1のHighレベルとOUTB1のLowレベルの電位差は縮小する。時間軸上で、OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間は広がり、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間は狭まる。

一方、OUT1のHighレベル期間の方がOUTB1のHighレベル期間(OUT1のLowレベル期間)よりも短い場合(デューティ<50%)、OUT1、OUTB1のHighレベル期間の差の期間に対応する積分結果が、VCNTB1、VCNT1間に生成され、VCNTB1>VCNT1となる。前述したように、VCNTB1>VCNT1のとき、OUTB1の中心電圧は、OUT1の中心電圧よりも低くなる。すなわち、OUTB1のHighレベル出力電圧、Lowレベル出力電圧はともに低くなり、OUT1のHighレベル出力電圧、Lowレベル出力電圧はともに高くなる。このため、OUTB1のHighレベルとOUT1のLowレベルの電位差は縮小し、OUT1のHighレベルとOUTB1のLowレベルの電位差は拡大する。時間軸上で、OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間は狭まり、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間は広がる。

図5は、図2のディストリビューションバッファ30の構成例を示す図である。図5を参照すると、一端がGNDに接続された定電流源ICS3と、共通ソースが定電流源ICS3の他端に接続され、ゲートにOUT1、OUTB1を入力し差動対を構成するNMOSトランジスタN5、N6と、NMOSトランジスタN5、N6のドレインと電源VDD間に接続された抵抗RL5、RL6(差動対の負荷抵抗)とを備えている。OUT1の電圧がNMOSトランジスタN5の閾値電圧を超え、OUTB1の電圧がNMOSトランジスタN5の閾値電圧以下のとき、NMOSトランジスタN5がオン、NMOSトランジスタN6はオフし、OUT2はHigh、OUTB2はLowとなる。OUT1の電圧がNMOSトランジスタN5の閾値電圧以下、OUTB1の電圧がNMOSトランジスタN5の閾値電圧を越えるとき、NMOSトランジスタN5がオフ、NMOSトランジスタN6がオンし、OUT2はLow、OUTB2はHighとなる。

図6、図7は、図2乃至図5を参照して説明した比較例のデューティ補正回路において、入力波形のデューティが劣化していない場合と、劣化した場合の各ノードの波形を示したものである。

図6の波形図において、(a)、(b)、(c)、(d)は、図2の構成において入力信号IN1/INB1のデューティが50%のときの、入力信号IN1/INB1、デューティ制御バッファ10の出力OUT1、OUTB1、ディストリビューションバッファ30の出力OUT2、OUTB2、デューティ制御電圧VCNT1、VCNTB1の電圧波形を示している。IN1、INB1のデューティが50%のとき、デューティ制御電圧VCNT1とVCNTB1は同一電圧Voとされ、デューティ制御バッファ10の出力OUT1、OUTB1の中心電圧は等しく、OUT1の立ち下がりとOUTB1の立ち上がりの時間軸上の交点から、OUT1の立ち上がりとOUTB1の立ち下がりの時間軸上の交点までの時間と、OUT1の立ち上がりとOUTB1の立ち下がりの時間軸上の交点からOUT1の立ち下がりとOUTB1の立ち上がりの時間軸上の交点までの時間は等しくなり、デューティは50%となる。

図7の波形図は、IN1のHighレベル期間(W2)がLowレベル期間(W1)よりも長い(OUTB1のLowレベル期間はHighレベル期間よりも短い)場合の図である(IN1のデューティ>50%)。図3のデューティ制御バッファ10のOUT1、OUTB1はIN1、INB1と同相であることから、OUT1のデューティ>50%となる。OUT1のHighレベル期間とLowレベル期間の時間差(W2−W1)を、VCNT1、VCNTB1の電位差に変換する。VCNT1=V1>Vo、VCNTB1=V2<V0となる。

VCNT1、VCNTB1を受けるデューティ制御バッファ10(図2参照)において、OUT1のHighレベル電圧、Lowレベル電圧、及び中心電圧は下がり、OUTB1のHighレベル電圧、Lowレベル電圧、中心電圧は上がる。

OUT1の立ち下がりとOUTB1の立ち上がりのクロスポイントからOUT1の立ち上がりとOUTB1の立ち下がりのクロスポイントまでの幅は、W1からW0に広がる。OUT1の立ち上がりとOUTB1の立ち下がりのクロスポイントから、OUT1の立ち下がりとOUTB1の立ち上がりのクロスポイントまでの幅は、W2からW0に狭まる。

OUT1、OUT1Bを受けるデストリビューションバッファ30の差動(相補)出力OUT2、OUTB2のHighレベル期間とLowレベル期間はともに、W0となり、デューティは50%となる。なお、図7では、簡単のため、デューティ>50%のIN1の波形の各サイクルの真下(同一サイクル内)に、それぞれデューティ補正後の波形OUT1/OUTB1、OUT2/OUTB2(デューティ=50%)が図示されているが、デューティ制御電圧発生部20からの積分結果であるデューティ制御電圧VCNT1、VCNTB1による帰還制御は、一般に複数サイクルにわたって行われる。また、図7では、デューティ制御電圧VCNT1>VCNTB1とされ、OUT1のデューティが50%となるように制御が行われる。OUT1/OUTB1、OUT2/OUTB2がデューティ=50%に近づくにしたがって、デューティ制御電圧VCNT1、VCNTB1の電圧値は等しくなるように変化し、デューティ=50%でVCNT1=VCNTB1となる。

図2乃至図5を参照して説明した比較例においては、図8に示すように、OUT1、OUTB1の立ち上がり時間、立ち下がり時間が小さい場合には、デューティ制御電圧VCNT1、VCNTB1によりOUT1とOUTB1の中心電圧の差を大きくしても、デューティを補正しきれず、OUT1、OUTB1の中心電圧の電位差は、それぞれのエッジがクロスすることができない状態まで変動する場合がある。図8において、図7と同様、IN1のHighレベル期間(W2)がLowレベル期間(W1)よりも長い(デューティ>50%)。デューティ制御電圧発生部20において、OUT1、OUTB1のHighレベル期間とLowレベル期間の時間差(W2−W1)を、VCNT1、VCNTB1の電位差に変換する。その結果、VCNT1>VCNTB1となる。VCNT1、VCNTB1を受けるデューティ制御バッファ10(図2参照)において、OUT1の中心電圧は下がり、OUTB1の中心電圧は上がる。OUTB1のLowレベル出力電圧VOLは、OUT1のHighレベル出力電圧VOHよりも高い。このため、時間軸上で、OUT1の立ち下がりとOUTB1の立ち上がりがクロスすることはない。また、時間軸上で、OUT1の立ち上がりとOUTB1の立ち下がりがクロスすることはない。この結果、デストリビューションバッファ30の出力OUTB2は、High固定、OUT2は、Low固定となり、信号(クロックパルス)は消滅する。

またOUT1、OUTB1は、図7(b)に示すように、デューティ補正のために、Highレベル、Lowレベルの振幅がアンバランスとなる。このOUT1、OUTB1は、デストリビューションバッファ30に供給される。一般に、図5に示した差動型のバッファ回路は、プロセスのバラツキ等により、例えばNMOSトランジスタN5とN6において、互いのトランジスタの閾値が変動する場合がある。閾値の変動によって、差動型のバッファ回路の信号検知能力が変化し、例えば、LowレベルからHighレベルを検知する能力が、HighレベルからLowレベルを検知する能力に対して劣化する場合がある。同相のバッファ(例えばOUT1、OUTB1のHigh、Lowに対してOUT2、OUT2Bから同相のHigh、Lowを出力する)において、Highレベルを出力する速度がLowレベルを出力する速度よりも遅くなり、これによってデューティの劣化が発生する。

図9は、この場合のタイミング波形を表した図である。図9においても、図7と同様、IN1のHighレベル期間(W2)がLowレベル期間(W1)よりも長い(デューティ>50%)。デューティ制御電圧発生部20において、OUT1、OUTB1のHighレベル期間とLowレベル期間の時間差(W2−W1)を、VCNT1、VCNTB1の電位差に変換する。なお、OUT1はIN1と同相、OUTB1はINB1と同相である。OUT1、OUTB1は、デューティ補正によってHighレベル、Lowレベルの振幅がアンバランスになっている。OUT1、OUTB1を差動で受けるデストリビューションバッファ30は、例えば上述したように、製造プロセスのバラツキ等により、Highレベルを検知する能力がLowレベルを検知する能力に対して劣化しているものと仮定する。すると、Highレベルを出力する速度がLowレベルを出力する速度に対して遅くなるため、デストリビューションバッファ30の出力OUT2、OUTB2から、デューティのずれた信号が出力されることになる(図9の(c)参照)。デューティ制御バッファ10の出力OUT1がHigh、OUTB1がLowの期間の振幅は小さくなり、次段のデストリビューションバッファ30の差動対のオフセットにより、デューティ制御バッファ10でデューティ50%に補正したOUT1、OUTB1のデューティが再度変動してしまっている。すなわち、OUT2のHighレベル期間はW0からW4に短縮し、Lowレベル期間はW0からW3に伸長し、OUT2はデューティ=W4/(W3+W4)となる。これは、デューティ制御バッファ10でOUT1のHighレベル、OUTB1のLowレベルの差電圧を小さくしているために生じている。

このように、比較例において、OUT1/OUTB1の波形鈍が小さい場合、OUT1/OUTB1の中心電圧の差を大きくしても、デューティが完全に補正できず、またクロックパルスが消滅してしまう。さらに、次段のバッファのオフセットが原因して、デューティ50%に補正したOUT1/OUTB1のデューティが再度変動してしまう場合が生じる。以上、比較例の問題点を詳細に説明した。以下に、本発明の実施例を説明する。

本発明によれば、デューティ補正回路において信号の波形鈍りの変化で発生するデューティ補正能力の低下と誤動作を防止する。また製造バラツキ等で発生する差動回路のオフセットによって発生するデューティ劣化を大幅に低減する。以下、本発明の一実施例の構成を説明する。なお、本発明におけるデューティ補正回路の全体は、図2の構成と同様である。デューティ制御電圧発生部20、デストリビューションバッファ30は、図4、図5にそれぞれ示した構成とされる。

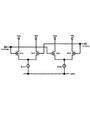

図10は、本発明の一実施例のデューティ制御バッファ(図2の10)の構成を示す図である。図2を参照すると、このデューティ制御バッファは、IN1、INB2に入力対が接続され、出力対が電源VDDに負荷抵抗RL1、RL2を介して接続される差動段(Differential stage)1と、差動段1とGND間に接続され、デューティ制御電圧VCNTB1、VCNT1を受け、差動段1に対して、電流端子SA1、SA2、SB1、SB2から電流を供給する電流源段(Current source stage)2とを備えている。差動段1の出力対と抵抗RL1、RL2との接続点はそれぞれ出力端子OUTB1、OUT1と接続されている。

図11は、図10の差動段1の構成の一例を示す図である。図11を参照すると、この差動段は、共通接続されたソースが電流端子SA1に接続され、ゲートがIN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続されたNMOSトランジスタNA1、NA2と、共通接続されたソースが電流端子SA2に接続され、ゲートがOUTB1、OUT1にそれぞれ接続され、ドレインがOUT1、OUTB1にそれぞれ接続されたNMOSトランジスタNA3、NA4と、共通接続されたソースが電流端子SB1に接続され、ゲートがIN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続されたNMOSトランジスタNB1、NB2と、共通接続されたソースが電流端子SB2に接続され、ゲートがOUTB1、OUT1にそれぞれ接続され、ドレインがOUT1、OUTB1にそれぞれ接続されたNMOSトランジスタNB3、NB4と、を備えている。

NMOSトランジスタNA3、NA4は、それぞれラッチ回路として作用する。OUTB1がHighのとき、NMOSトランジスタNA3がオンし、OUT1をLowとし、OUT1がHighのとき、NMOSトランジスタNA4がオンし、OUTB1をLowとする。NMOSトランジスタNB3、NB4もそれぞれラッチ回路として作用し、OUTB1がHighのとき、NMOSトランジスタNB3がオンし、OUT1をLowとし、OUT1がHighのとき、NMOSトランジスタNB4がオンし、OUTB1をLowとする。

NMOSトランジスタNA2とNA3のW/L(ゲート幅/ゲート長)を1(単位)とした場合、NMOSトランジスタNA1とNA4の(W/L)はn倍とする(但し、n>1)。NMOSトランジスタNA2がOUT1をHighからLowへ駆動する電流駆動能力は、NMOSトランジスタNA1がOUTB1をHighからLowへ駆動する電流駆動能力の(1/n)倍とされる。NMOSトランジスタNA1〜NA4の回路において、OUT1の立ち下がり時間(HighからLowへの遷移時間)は、OUTB1の立ち下がり時間(HighからLowへの遷移時間)よりも遅れる。

NMOSトランジスタNB1とNB4の(W/L)を1(単位)とした場合、NMOSトランジスタNB2とNB3の(W/L)はm倍とする(但し、m>1)。NMOSトランジスタNB1がOUTB1をHighからLowへ駆動する電流駆動能力は、NMOSトランジスタNB2がOUT1をHighからLowへ駆動する電流駆動能力の(1/m)倍とされる。トランジスタNB1〜NB4の回路において、OUTB1のHighからLowへの立ち下がり時間(HighからLowへの遷移時間)は、OUT1のHighからLowへの立ち下がり時間(HighからLowへの遷移時間)よりも遅れる。

図12は、図10の電流源段(Current source stage)の構成を示す図である。図12を参照すると、一端がGNDに接続された定電流源ICSA1、ICSA2、ICSA3、ICSA4と、NMOSトランジスタNC1、NC2、ND1、ND2とを備えている。NMOSトランジスタNC1、NC2のゲートはVCNTB1、VCNT1にそれぞれ接続され、ドレインはSA1、SB1に接続され、ソースは定電流源ICSA1、ICSB1の他端にそれぞれ接続されている。NMOSトランジスタNC1、NC2のソース間には抵抗RSC1が接続されている。NMOSトランジスタND1、ND2のゲートはVCNTB1、VCNT1にそれぞれ接続され、ドレインはSA2、SB2に接続され、ソースは定電流源ICSA2、ICSB2の他端にそれぞれ接続されている。NMOSトランジスタND1、ND2のソース間には抵抗RSD1が接続されている。電圧VCNTB1が下がり、電圧VCNT1が上がると、トランジスタNC1に流れる電流(ドレイン電流)は減少し、トランジスタNC2に流れる電流は増大し、トランジスタND1に流れる電流(ドレイン電流)は減少し、トランジスタND2に流れる電流は増大する。逆に電圧VCNTB1が上がり、電圧VCNT1が下がると、トランジスタNC1に流れる電流(ドレイン電流)は増大し、トランジスタNC2に流れる電流は減少し、トランジスタND1に流れる電流(ドレイン電流)は増大し、トランジスタND2に流れる電流は減少する。

定電流源ICSA2の電流値を1とした場合、定電流源ICSA1の電流値をr倍とする(但し、r>1)。

定電流源ICSB2の電流を1とした場合、定電流源ICSB1の電流値をs倍とする(但し、s>1)。n、m、r、sの絶対値は、デューティ補正能力の限界を設定するために、任意に設定できる。

また、nとmの相対比(例えばn/m)と、rとsの相対値(例えばr/s)は、デューティ補正を行うべき入力信号のHigh、Lowレベルのうちいずれか一方のデューティ補正能力を、他方に対して上げるために、任意に設定できる。

例えば(n/m)>1または(r/s)>1の場合、Lowレベル期間がHighレベル期間に対して大きい場合に、有効である。

また、(n/m)<1または(r/s)<1の場合、上記とは逆に、デューティ劣化が発生した場合に、有効である。

すなわち、予め、High/Lowに対するデューティ劣化の方向が判明している場合に有効である。

また、nとrの相対比(例えばn/r)と、mとsの相対値(例えばm/s)は、出力OUT1、OUTB1の波形鈍りを調整し、デューティ補正能力の強度を調整するために任意に設定できる。

例えば、

(A)(n/r)>1または(m/s)>1の場合、波形鈍り(立ち上がり、立ち下がり)を小さくすることができる。

(A)(n/r)>1または(m/s)>1の場合、波形鈍り(立ち上がり、立ち下がり)を小さくすることができる。

(B)(n/r)<1または(m/s)<1の場合、出力信号OUT1、OUTB1の波形鈍りを大きくすることができる。

これは、入力端子IN1、INB1に差動で入力されるクロック信号の周波数の変化に対してより有効に作用する。例えば(A)の場合、高周波クロックの場合に有効である。また(B)の場合、低周波クロックに有効である。

通常、n=m=r=sとする。また、変数の絶対値としては、動作周波数を500MHz〜3GHzの差動信号を想定した場合、2〜6の範囲が適切な例として挙げられる。

以下では、n=m=r=s=4とした場合について説明する。上述した、図10と図11のトランジスタと電流の比を与えた結果として、トランジスタNA1、NA2、NA3、NA4で構成された回路は、入力端子IN1、INB1から入力される信号に対して、OUT1のHighからLowへの遷移時間(立ち下がり時間)を遅らせる作用がある。なお、NMOSトランジスタNA1〜NA4の回路の出力において、OUTB1の立ち下がりはOUT1の立ち下がりよりも速く、OUT1の立ち上がりはOUTB1の立ち上がりよりも速い。

また、NMOSトランジスタNB1、NB2、NB3、NB4で構成された回路は、IN1、INB1から入力される信号に対して、OUTB1のHighからLowへの遷移時間(立ち下がり時間)を遅らせる作用がある。なお、NMOSトランジスタNB1〜NB4の回路の出力において、OUT1の立ち下がりはOUTB1の立ち下がりよりも速く、OUTB1の立ち上がりはOUT1の立ち上がりよりも速い。

図18は、本実施例の動作を説明するためのタイミング波形図である。図18には、入力IN1、INB1にデューティ変動がない場合(デューティ=50%)の動作が示されている。この場合、デューティ制御電圧発生部20の出力VCNT1、VCNTB1は等しい。

図18において、(a)、(b)は入力波形IN、INB1と、NMOSトランジスタNA1〜NA4の回路で生成されるOUT1、OUTB1を表している。OUT1のHighからLowへの立ち下がり遷移は遅れる。また、OUTB1のLowからHighへの立ち上がり変化は遅れる。OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間がW0からW1に短縮し、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間はW0からW2に伸長している。

図18(c)、(d)は入力波形IN、INB1と、NMOSトランジスタNB1〜NB4の回路で生成される波形OUT1、OUTB1を表している。OUT1のLowからHighへの立ち上がり遷移は遅れる。OUTB1のHighからLowへの立ち下がり遷移は遅れる。OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間がW0からW3に伸長し、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間はW0からW4に短縮している。

図18(e)、(f)、(g)は、NMOSトランジスタNA1〜NA4の回路で生成される波形と、NMOSトランジスタNB1〜NB4の回路で生成される波形の合成を説明するための図である。(e)は、NMOSトランジスタNA1〜NA4の回路で生成される波形OUT1、OUTB1((b)と同じ)、(f)は、NMOSトランジスタNB1〜NB4の回路で生成される波形OUT1、OUTB1((d)と同じ)、(g)は帰還による合成されたOUT1/OUTB1の波形をそれぞれ表している。

図18(h)は、デューティ制御電圧VCNT1、VCNTB1である。(e)と(f)のOUT1同士、OUTB1同士を合成(実際には抵抗RL1、RL2に流れる電流の電流加算)することで、(g)の波形が得られる。

NMOSトランジスタNA1〜NA4の回路からの立ち下がりの遅れたOUT1と、NMOSトランジスタNB1〜NB4の回路からの立ち上がりの遅れたOUT1とを合成し、結果として、デューティ劣化のない出力波形となる。なお、NMOSトランジスタNA1〜NA4の回路からのOUT1と、NMOSトランジスタNB1〜NB4の回路からのOUT1の合成は、負荷抵抗RL2で行われ、合成結果が抵抗RL2の端子電圧として出力される。NMOSトランジスタNA1〜NA4の回路からのOUTB1と、NMOSトランジスタNB1〜NB4の回路からのOUTB1の合成は、負荷抵抗RL1で行われ、合成結果が抵抗RL1の端子電圧として出力される。

図19は、前述した比較例の問題点を想定した動作を説明するためのタイミング波形図である。図19において、(a)、(b)は入力信号IN、INB1と、NMOSトランジスタNA1〜NA4の回路で生成されるOUT1、OUTB1を表している。NMOSトランジスタNA1からNA4の回路はOUT1のHighからLowへの変化を遅れさせる。すなわち、図19(b)に示すように、OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間がW1からW5に短縮し(W5<W1)、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間はW2からW6(W6>W2)に伸長している。

図19(c)、(d)は入力信号IN、INB1と、NMOSトランジスタNB1〜NB4の回路で生成される波形OUT1、OUTB1を表している。またNMOSトランジスタNB1からNB4の回路はOUT1のLowからHighへの変化を遅らせる。図19(d)に示すように、OUT1の立ち下がりとOUTB1の立ち上がりの交点からOUT1の立ち上がりとOUTB1の立ち下がりの交点までの期間がW1からW7(W7>W1))に伸長し、OUT1の立ち上がりとOUTB1の立ち下がりの交点からOUT1の立ち下がりとOUTB1の立ち上がりの交点までの期間はW2からW8(W2>W8)に短縮している。なお、図19(a)と(c)は同一波形である。

NMOSトランジスタNA1からNA4の回路の出力(図19(e))とNB1からNB4の回路の出力(図19(f))を合成することで、出力OUT1、OUTB1からはデューティ劣化のない波形が出力される(図19(g))。なお、図19(h)のVCNT1、VCNTB1は、図4のデューティ制御電圧発生部20から出力される。IN1(したがってOUT1)のデューティが50%よりも大であるため、前述したように、デューティ制御電圧発生部20から出力されるデューティ制御電圧はVCNT1>VCNTB1となる。この場合、図12の電流源段において、電流端子SA1、SA2の電流値が減少し、電流端子SB1、SB2の電流値は増大する。この結果、NMOSトランジスタNA1、NA2からなる差動対の駆動電流が減少し、NMOSトランジスタNB1、NB2からなる差動対の駆動電流は増大する。よって、NA1〜NA4の回路は、OUT1の立ち下がり時間の遅れを小さくし、OUTB1の立ち下がり時間の遅れを増やす。また、NMOSトランジスタNB1〜NB4の回路は、OUT1の立ち下がり時間を短縮し、OUTB1の立ち下がり時間の遅れを小さくするように帰還制御が行われる。

前述した比較例では、デューティ補正の効果を得るために、信号振幅の中心電圧に差分を与える構成とされている。すなわち、OUT1、OUTB1にオフセットを設け、Highレベル出力電圧と、Lowレベル電圧を可変させ、振幅を可変させている。

これに対し、本発明においては、OUT1のHighからLowに変化する信号を遅れさせる回路と、LowからHighに変化する信号を遅れさせる回路を設け、それを合成させる。デューティ補正能力は、入力波形鈍りに関係なく、上述した変数(n、m、r、s)の組み合わせで決定することができるため、比較例のように、出力信号が消滅するという不具合は発生しない。

また、前述した比較例では、Highレベル出力電圧と、Lowレベル電圧の振幅を可変させているが、本実施例では、OUT1、OUTB1のHigh/Lowレベルの振幅は一定であるため、比較例のように、後段のバッファの入力オフセットの影響で、デューティ劣化を起こす不具合も発生しない。また、変数(n、m、r、s)の組み合わせによって、低周波から高周波への適用や、予めHigh/Lowのデューティ変動の方向が決まっている場合への有効的な適用も可能である。

図13は、図2のデューティ制御バッファ10の別の実施例の構成を示す図である。図13を参照すると、デューティ制御バッファは、共通接続されたソースが電流端子SA1に接続され、ゲートが入力端子IN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続されたNMOSトランジスタNA1、NA2と、共通接続されたソースが電流端子SB1に接続され、ゲートが入力端子IN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続されたNMOSトランジスタNB1、NB2と、を備えている。なお、本実施例において、NMOSトランジスタNA1、NA2、NB1、NB2のディメンジョン(W/L)は、図11に示した前記実施例で説明したものと同様とされる。

図14は、図2のデューティ制御バッファ10の別の実施例の構成を示す図である。図14を参照すると、ソースが電流端子SA1に共通接続されたNMOSトランジスタNA1、NA2、NA3、NA4を備え、NMOSトランジスタNA1、NA2のゲートはIN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続され、NMOSトランジスタNA3、NA4のゲートはOUTB1、OUT1にそれぞれ接続され、ドレインがOUT1、OUTB1にそれぞれ接続されている。ソースが電流端子SB1に共通接続されたNMOSトランジスタNB1、NB2、NB3、NB4を備え、NMOSトランジスタNB1、NB2のゲートはIN1、INB1にそれぞれ接続され、ドレインがOUTB1、OUT1にそれぞれ接続され、NMOSトランジスタNB3、NB4のゲートはOUTB1、OUT1にそれぞれ接続され、ドレインがOUT1、OUTB1にそれぞれ接続されている。なお、本実施例において、NMOSトランジスタNA1、NA2、NB1、NB2のディメンジョン(W/L)は、図11に示した前記実施例で説明したものと同様とされる。

図15は、図14、図15の電流端子SA1、SB1に電流を供給する電流源の構成を示す図である。一端がGNDに接続された定電流源ICSA1、ICSAB1と、ソースが定電流源ICSA1、ICSAB1の他端にそれぞれ接続され、抵抗RSC1を介して接続され、ゲートがVCNTB1、VCNT1にそれぞれ接続され、ドレインがSA1、SB1に接続されたNMOSトランジスタNC1、NC2を備えている。OUT1、OUTB1の負荷抵抗RL1、RL2に流れる電流の総和は定電流源ICSA1、ICSB1の電流値の和となる。

図16は、図14、図15の電流端子SA1、SB1に電流を供給する電流源の構成を示す図である。一端がGNDに接続された定電流源ICSA1と、共通接続されたソースが定電流源ICSA1の他端に接続され、ゲートがVCNTB1、VCNT1にそれぞれ接続され、ドレインがSA1、SB1に接続されたNMOSトランジスタNC1、NC2を備えている。OUT1、OUTB1の負荷抵抗RL1、RL2に流れる電流の総和は定電流源ICSA1の電流値となる。

図17は、図10の電流源段の別の構成例を示す図である。図14の差動段の構成から、NMOSトランジスタNA3、NA4、NB3、NB4を削除したものである。図17を参照すると、一端がGNDに接続された定電流源ICSA1、ICSA2と、共通接続されたソースが定電流源ICSA1の他端に接続され、ゲートがVCNTB1、VCNT1にそれぞれ接続され、ドレインがSA1、SB1にそれぞれ接続されたNMOSトランジスタNC1、NC2と、共通接続されたソースが定電流源ICSA2の他端に接続され、ゲートがVCNTB1、VCNT1にそれぞれ接続され、ドレインがSA2、SB2にそれぞれ接続されたNMOSトランジスタND1、ND2と、を備えている。端子SA1、SB1の端子に供給される電流の和は定電流源ICS1の電流値、端子SA2、SB2の端子に供給される電流の和は定電流源ICS2の電流値である。

なお、上記実施例では、デューティ制御バッファ10の差動段、電流源段等をNMOSトランジスタで構成した例に即して説明したが、本発明においてトランジスタの導電型はNMOSに制限されるものでなく、PMOSトランジスタで構成してもよいことは勿論である。この場合、図10、図11等において、電流源段は電源VDD側に接続され、抵抗RL11、RL12はGND側に接続される。

なお、上記の特許文献1の各開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

10 デューティ制御バッファ

20 デューティ制御電圧発生部

30 デストリビューションバッファ

ICSA1、ICSA2、ICSB1、ICSB2 定電流源

N1、N2、N5、N6、N7、N8、NA1、NA2、MNA3、NA4、NB1、NB2、NB3、NB4、NC1、NC2、ND1、ND2、 NMOSトランジスタ

P1、P2、P3、P4 PMOSトランジスタ

RL1、RL2、RL3、RL4、RL5、RL6、RSC1、RSD1 抵抗

20 デューティ制御電圧発生部

30 デストリビューションバッファ

ICSA1、ICSA2、ICSB1、ICSB2 定電流源

N1、N2、N5、N6、N7、N8、NA1、NA2、MNA3、NA4、NB1、NB2、NB3、NB4、NC1、NC2、ND1、ND2、 NMOSトランジスタ

P1、P2、P3、P4 PMOSトランジスタ

RL1、RL2、RL3、RL4、RL5、RL6、RSC1、RSD1 抵抗

Claims (27)

- 入力信号を受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がりの少なくとも1方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に所定の大小関係を有する第1の差動出力信号を生成する第1の差動回路と、

前記入力信号を第1の差動回路と共通に受け、前記入力信号の遷移に応じた出力の立ち下がりと立ち上がり遷移のうち前記一方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に、前記第1の差動出力信号における大小関係とは逆の大小関係を有する第2の差動出力信号を生成する第2の差動回路と、

を備え、前記第1の差動出力信号と前記第2の差動出力信号の正転出力信号同士と反転出力信号同士を合成した信号波形を出力する、ことを特徴とする波形制御回路。 - 前記第1の差動回路が、前記入力信号を差動で受ける第1の差動対を備え

前記第2の差動回路が、前記入力信号を差動で受ける第2の差動対を備え、

前記第1、第2の差動対の出力対の第1の出力同士、第2の出力同士がそれぞれ共通に接続され、

前記第1、第2の差動対の共通接続された出力対と電源との間に接続された負荷素子対と、

前記第1、第2の差動対に対して、制御信号に応じた電流をそれぞれ供給する電流源段と、

を備え、

前記第1、第2の差動対の共通接続された出力対と前記負荷素子対の接続点から前記正転出力信号と前記反転出力信号が出力され、

前記第1の差動対は、電流駆動能力の比が予め定められた所定の値とされるトランジスタ対を備え、

前記第2の差動対は、電流駆動能力の比が予め定められた所定の値とされるトランジスタ対を備えている、ことを特徴とする請求項1記載の波形制御回路。 - 前記第1の差動対が、立ち下がりと立ち上がりの前記一方の遷移に関して、出力対の正転出力信号の遷移時間を反転出力信号の遷移時間に対して遅らせる場合、

前記第2の差動対は、立ち下がりと立ち上がりの他方の遷移に関して、出力対の正転出力信号の遷移時間を反転出力信号の遷移時間に対して遅らせる、ことを特徴とする請求項2記載の波形制御回路。 - 前記第1の差動回路が、第1の電流源で駆動され、電流駆動能力の比が所定の値とされる第1、第2のトランジスタを含む第1の差動対を備え、

前記第2の差動回路が、第2の電流源で駆動され、電流駆動能力の比が所定の値とされる第3、第4のトランジスタを含む第2の差動対を備え、

前記第1、第2の差動対において、

前記第2、第4のトランジスタの制御端子同士が共通接続されて第1の入力端子に接続され、

前記第1、第3のトランジスタの制御端子同士が共通接続されて第2の入力端子に接続され、

前記第2、第4のトランジスタの出力同士が共通接続されて第1の出力端子に接続され、

前記第1、第3のトランジスタの出力同士が共通接続されて第2の出力端子に接続されている、ことを特徴とする請求項1記載の波形制御回路。 - 前記第1、第2のトランジスタの出力をそれぞれ入力し、出力が前記第2、第1のトランジスタの出力に交差接続された第1、第2のラッチ回路と、

前記第3、第4のトランジスタの出力をそれぞれ入力し、出力が前記第4、第3のトランジスタの出力に交差接続された第3、第4のラッチ回路と、

を備えている、ことを特徴とする請求項4記載の波形制御回路。 - 前記第1のラッチ回路が、

前記第1の電流源と前記第1の出力端子間に、前記第2のトランジスタと並列に接続され、制御端子が前記第2の出力端子に接続された第5のトランジスタを備え、

前記第2のラッチ回路が、

前記第1の電流源と前記第2の出力端子間に、前記第1のトランジスタと並列に接続され、制御端子が前記第1の出力端子に接続された第6のトランジスタを備え

前記第3のラッチ回路が、

前記第1の電流源と前記第1の出力端子間に、前記第4のトランジスタと並列に接続され、制御端子が前記第2の出力端子に接続された第7のトランジスタを備え、

前記第4のラッチ回路が、

前記第1の電流源と前記第2の出力端子間に、前記第3のトランジスタと並列に接続され、制御端子が前記第1の出力端子に接続された第8のトランジスタを備えている、ことを特徴とする請求項5記載の波形制御回路。 - 前記第1のラッチ回路が、

第3の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第5のトランジスタを備え、

前記第2のラッチ回路が、

前記第3の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第6のトランジスタを備え、

前記第3のラッチ回路が、

第4の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第7のトランジスタを備え、

前記第4のラッチ回路が、

前記第4の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第8のトランジスタを備えている、ことを特徴とする請求項5記載の波形制御回路。 - 第1の定電流源に共通に接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第9、第10のトランジスタが、前記第1、第2の電流源をなす、ことを特徴とする請求項4乃至6のいずれか1項に記載の波形制御回路。 - 第1、第2の定電流源にそれぞれ接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第1の定電流源と前記第9のトランジスタの接続点と、前記第2の定電流源と前記第10のトランジスタの接続点とは抵抗で接続され、

前記第9、第10のトランジスタが、前記第1、第2の電流源をなすことを特徴とする請求項4乃至6のいずれか1項に記載の波形制御回路。 - 前記第1、第2の定電流源にそれぞれ接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第1の定電流源と前記第9のトランジスタとの接続点と、前記第2の定電流源と前記第10のトランジスタとの接続点は、第1の抵抗で接続され、

前記第9、第10のトランジスタが、それぞれ前記第1、第3の電流源をなし

前記第3、第4の定電流源にそれぞれ接続され、前記第1、第2の制御信号を差動で受ける差動対をなす第11、第12のトランジスタを備え、

前記第3の定電流源と前記第11のトランジスタの接続点と、前記第4の定電流源と前記第12のトランジスタの接続点は第2の抵抗で接続され、

前記第11、第12のトランジスタが、前記第2、第4の電流源をなす、ことを特徴とする請求項7記載の波形制御回路。 - 前記第1の電流源の電流値と前記第2の電流源の電流値が予め定められた所定の値とされる、ことを特徴とする請求項4乃至6、8、9のいずれか1項に記載の波形制御回路。

- 前記第1の電流源と前記第2の電流源の電流値が予め定められた所定の値とされ、

前記第3の電流源と前記第4の電流源の電流値が予め定められた所定の値とされる、ことを特徴とする請求項7又は10に記載の波形制御回路。 - 請求項1乃至12のいずれか1項に記載の波形制御回路を備えたデューティ補正回路。

- 請求項8乃至10のいずれか1項に記載の波形制御回路と、

前記波形制御回路の出力を受け、デューティの誤差を検出し前記第1、第2の制御信号を生成するデューティ補正電圧発生部と、

を備えたデューティ補正回路。 - 前記波形制御回路の出力を差動で受けるバッファ回路を備えた請求項14記載のデューティ補正回路。

- 入力信号を受けるデューティ制御バッファと、

前記デューティ制御バッファの出力を受け、デューティの誤差を検出して制御信号を差動で生成するデューティ補正電圧発生部を備え、

前記デューティ制御バッファが、

前記入力信号を差動で共通に受け、出力対の電流駆動能力が不平衡の第1、第2の差動対を備え

前記第1、第2の差動対の出力対の第1の出力同士、第2の出力同士がそれぞれ接続され、

前記第1、第2の差動対の共通接続された出力対と電源との間に接続された負荷素子対と、

前記第1、第2の差動対に対して制御信号に応じた駆動電流をそれぞれ供給する電流源段と、

を備えている、ことを特徴とするデューティ補正回路。 - 前記第1の差動対が、第1の電流源で駆動される第1、第2のトランジスタを含み、

前記第2の差動対が、第2の電流源で駆動される第3、第4のトランジスタを含み、

前記第1、第2の差動対において、

前記第1、第3のトランジスタの制御端子同士が共通接続されて第1の入力端子に接続され、

前記第2、第4のトランジスタの制御端子同士が共通接続されて第2の入力端子に接続され、

前記第1、第2の入力端子には、前記入力信号が差動で入力され、

前記第1、第3のトランジスタの出力同士が共通接続されて前期出力対の第1の出力端子に接続され、

前記第2、第4のトランジスタの出力同士が共通接続されて前期出力対の第2の出力端子に接続され、

前記第1のトランジスタの電流駆動能力は、前記第2のトランジスタの電流駆動能力よりも大とされる場合、前記第4のトランジスタの電流駆動能力は、前記第3のトランジスタの電流駆動能力よりも大とされる、ことを特徴とする請求項16記載のデューティ補正回路。 - 前記第1、第2のトランジスタの出力を入力し、前記第2、第1の出力端子に出力が接続された第1、第2のラッチ回路と、

前記第3、第4のトランジスタの出力を入力し、前記第2、第1の出力端子に出力が接続された第3、第4のラッチ回路と、

を備えている、ことを特徴とする請求項17記載のデューティ補正回路。 - 前記第1のラッチ回路が、

前記第2のトランジスタと並列に、前記第1の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第5のトランジスタを備え、

前記第2のラッチ回路が、

前記第1のトランジスタと並列に、前記第1の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第6のトランジスタを備え

前記第3のラッチ回路が、

前記第4のトランジスタと並列に、前記第1の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第7のトランジスタを備え、

前記第4のラッチ回路が、

前記第3のトランジスタと並列に、前記第1の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第8のトランジスタを備えている、ことを特徴とする請求項18記載のデューティ補正回路。 - 前記第1のラッチ回路が、

前記第2のトランジスタと並列に、第3の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第5のトランジスタを備え、

前記第2のラッチ回路が、

前記第1のトランジスタと並列に、前記第3の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第6のトランジスタを備え、

前記第3のラッチ回路が、

前記第4のトランジスタと並列に、第4の電流源と前記第1の出力端子間に接続され、制御端子が前記第2の出力端子に接続された第7のトランジスタを備え、

前記第4のラッチ回路が、

前記第3のトランジスタと並列に、前記第4の電流源と前記第2の出力端子間に接続され、制御端子が前記第1の出力端子に接続された第8のトランジスタを備えている、ことを特徴とする請求項18記載のデューティ補正回路。 - 第1の定電流源に接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第9、第10のトランジスタが、それぞれ前記第1、第2の電流源をなす、ことを特徴とする請求項16乃至19のいずれか1項に記載のデューティ補正回路。 - 第1、第2の定電流源でそれぞれ接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第1の定電流源と前記第9のトランジスタの接続点と前記第2の定電流源と前記第10のトランジスタの接続点は抵抗で接続され、

前記第9、第10のトランジスタが、前記第1、第2の電流源をなすことを特徴とする請求項16乃至19のいずれか1項に記載のデューティ補正回路。 - 第1、第2の定電流源でそれぞれ接続され、第1、第2の制御信号を差動で受ける差動対をなす第9、第10のトランジスタを備え、

前記第1の定電流源と前記第9のトランジスタの接続点と前記第2の定電流源と前記第10のトランジスタの接続点は第1の抵抗で接続され、

前記第9、第10のトランジスタが、前記第1、第3の電流源をなし

第3、第4の定電流源でそれぞれ接続され、前記第1、第2の制御信号を差動で受ける差動対をなす第11、第12のトランジスタを備え、

前記第3の定電流源と前記第11のトランジスタの接続点と前記第4の定電流源と前記第12のトランジスタの接続点は第2の抵抗で接続され、

前記第11、第12のトランジスタが、前記第2、第4の電流源をなす、ことを特徴とする請求項20記載のデューティ補正回路。 - 前記デューティ補正電圧発生部が、電流源で駆動され、前記デューティ制御バッファの出力を差動で受ける差動対と、

前記差動対の出力対に流れる電流をそれぞれ受けて折り返す第1、第2のカレントミラーと、

前記第1、第2のカレントミラーの出力にそれぞれ接続された第1、第2の容量とを備え、前記第1、第2の容量の端子電圧を第1、第2の制御信号とする、請求項16乃至23のいずれか1項に記載のデューティ補正回路。 - 入力信号の遷移に応じた出力の立ち下がりと立ち上がりの少なくとも1方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に所定の大小関係を有する第1の差動出力信号を生成し、

前記入力信号の遷移に応じた出力の立ち下がりと立ち上がり遷移のうち少なくとも前記一方の遷移に関して、正転出力信号の前記遷移の時間と反転出力信号の前記遷移の時間の間に、前記第1の差動出力信号の大小関係とは逆の大小関係を有する第2の差動出力信号を生成し、

前記第1の差動出力信号と前記第2の差動出力信号の正転出力信号同士と反転出力信号同士を合成した信号波形を出力する、ことを特徴とするデューティ補正方法。 - 前記入力信号を第1、第2の差動対で差動で受け

前記第1、第2の差動対の出力対の第1の出力同士、第2の出力同士がそれぞれ共通に接続され、前記第1、第2の差動対に対して電流源段から制御信号に応じた電流をそれぞれ供給し、

前記第1の差動対のトランジスタ対の電流駆動能力の比は予め定められた所定の値とされ、

前記第2の差動対のトランジスタ対の電流駆動能力の比は予め定められた所定の値とされ、

前記制御信号に応じて、前記第1の差動対の出力対の第1の出力の遷移を速め、第2の出力の遷移を遅らせる場合、前記第2の差動対の出力対の第1の出力の遷移を遅らせ、第2の出力の遷移を速める、ことを特徴とする、ことを特徴とする請求項25記載のデューティ補正方法。 - 入力信号を受け、前記入力信号の遷移に応じた立ち上がり遷移を遅らせるか速めた第1の信号を生成する第1の回路と、

前記入力信号を受け、前記入力信号の遷移に応じた立ち下がり遷移を遅らせるか速めた第2の信号を生成する第2の回路と、

を備え、前記第1の信号と前記第2の信号を合成した信号波形を出力する、ことを特徴とする波形制御回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008316955A JP2010141684A (ja) | 2008-12-12 | 2008-12-12 | 波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 |

| US12/654,107 US8188779B2 (en) | 2008-12-12 | 2009-12-10 | Duty control buffer circuit and duty correction circuit |

| EP09015315A EP2209210A2 (en) | 2008-12-12 | 2009-12-10 | Duty control buffer circuit and duty correction circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008316955A JP2010141684A (ja) | 2008-12-12 | 2008-12-12 | 波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010141684A true JP2010141684A (ja) | 2010-06-24 |

Family

ID=42084680

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008316955A Withdrawn JP2010141684A (ja) | 2008-12-12 | 2008-12-12 | 波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8188779B2 (ja) |

| EP (1) | EP2209210A2 (ja) |

| JP (1) | JP2010141684A (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012010118A (ja) * | 2010-06-25 | 2012-01-12 | Hitachi Ltd | デューティ補償回路 |

| KR101196449B1 (ko) | 2011-06-20 | 2012-11-01 | 홍익대학교 산학협력단 | 듀얼 피드백 루프를 포함한 하이브리드 듀티 사이클 보정회로 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8004331B2 (en) * | 2009-06-01 | 2011-08-23 | Analog, Devices, Inc. | CMOS clock receiver with feedback loop error corrections |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6950973B2 (en) * | 2002-04-22 | 2005-09-27 | Broadcom Corporation | Dynamic scan circuitry for A-phase |

| KR100540485B1 (ko) | 2003-10-29 | 2006-01-10 | 주식회사 하이닉스반도체 | 듀티 보정 전압 발생 회로 및 방법 |

| US7336114B2 (en) * | 2006-04-05 | 2008-02-26 | Wionics Research | High-speed latching technique and application to frequency dividers |

| KR100892635B1 (ko) * | 2007-04-12 | 2009-04-09 | 주식회사 하이닉스반도체 | 듀티 사이클 보정 회로 |

-

2008

- 2008-12-12 JP JP2008316955A patent/JP2010141684A/ja not_active Withdrawn

-

2009

- 2009-12-10 EP EP09015315A patent/EP2209210A2/en not_active Withdrawn

- 2009-12-10 US US12/654,107 patent/US8188779B2/en not_active Expired - Fee Related

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012010118A (ja) * | 2010-06-25 | 2012-01-12 | Hitachi Ltd | デューティ補償回路 |

| KR101196449B1 (ko) | 2011-06-20 | 2012-11-01 | 홍익대학교 산학협력단 | 듀얼 피드백 루프를 포함한 하이브리드 듀티 사이클 보정회로 |

Also Published As

| Publication number | Publication date |

|---|---|

| US8188779B2 (en) | 2012-05-29 |

| EP2209210A2 (en) | 2010-07-21 |

| US20100148835A1 (en) | 2010-06-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| EP0886379B1 (en) | Voltage-level shifter | |

| JP4084176B2 (ja) | クロックデューティ/スキュー補正機能を有する位相分周回路 | |

| US7173453B2 (en) | Method and circuit for translating a differential signal to complementary CMOS levels | |

| JP2007329924A (ja) | デューティ補正付きレベル変換回路 | |

| US7944262B2 (en) | Duty correction circuit | |

| JP2012070333A (ja) | レベルシフト回路及びそれを用いたスイッチングレギュレータ | |

| JP2007081608A (ja) | 出力バッファ回路 | |

| JP3464372B2 (ja) | 発振器 | |

| JP3205185B2 (ja) | レベル変換回路 | |

| TW200306073A (en) | Level shift circuit | |

| US20140043084A1 (en) | Signal electric potential conversion circuit | |

| CN101043211B (zh) | 互补信号生成电路 | |

| JP4550139B2 (ja) | マルチ位相レベルシフトシステム | |

| JP2010141684A (ja) | 波形合成回路と該回路を備えたデューティ補正回路及びデューティ補正方法 | |

| JP2019022135A (ja) | タイミング発生器および半導体集積回路 | |

| EP1352472B1 (en) | Circuit for receiving and driving a clock-signal | |

| JP2019022136A (ja) | 位相補間器およびタイミング発生器、半導体集積回路 | |

| JP2002368602A (ja) | 信号生成回路 | |

| US6646486B2 (en) | Semiconductor integrated circuit | |

| JP2015033094A (ja) | デューティサイクル補正回路 | |

| US8742807B1 (en) | Low supply voltage analog phase interpolator | |

| JPH1098356A (ja) | 電圧制御発振器 | |

| KR101055788B1 (ko) | 광대역의 공통모드 입력전압 범위를 가지는 차동 증폭회로 및 그 차동 증폭회로를 구비한 입력 버퍼 | |

| US20090167392A1 (en) | Narrow pulse generator | |

| US6940331B2 (en) | Delayed tap signal generating circuit for controlling delay by interpolating two input clocks |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A300 | Application deemed to be withdrawn because no request for examination was validly filed |

Free format text: JAPANESE INTERMEDIATE CODE: A300 Effective date: 20120306 |