JP2010103445A - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP2010103445A JP2010103445A JP2008276056A JP2008276056A JP2010103445A JP 2010103445 A JP2010103445 A JP 2010103445A JP 2008276056 A JP2008276056 A JP 2008276056A JP 2008276056 A JP2008276056 A JP 2008276056A JP 2010103445 A JP2010103445 A JP 2010103445A

- Authority

- JP

- Japan

- Prior art keywords

- film

- semiconductor device

- amorphous silicon

- semiconductor element

- semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/45—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their insulating parts

- H10W20/47—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their insulating parts comprising two or more dielectric layers having different properties, e.g. different dielectric constants

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B41/00—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates

- H10B41/30—Electrically erasable-and-programmable ROM [EEPROM] devices comprising floating gates characterised by the memory core region

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/074—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H10W20/075—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers of multilayered thin functional dielectric layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/01—Manufacture or treatment

- H10W20/071—Manufacture or treatment of dielectric parts thereof

- H10W20/074—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H10W20/076—Manufacture or treatment of dielectric parts thereof of dielectric parts comprising thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10W—GENERIC PACKAGES, INTERCONNECTIONS, CONNECTORS OR OTHER CONSTRUCTIONAL DETAILS OF DEVICES COVERED BY CLASS H10

- H10W20/00—Interconnections in chips, wafers or substrates

- H10W20/40—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes

- H10W20/41—Interconnections external to wafers or substrates, e.g. back-end-of-line [BEOL] metallisations or vias connecting to gate electrodes characterised by their conductive parts

- H10W20/425—Barrier, adhesion or liner layers

Landscapes

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Abstract

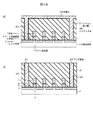

【解決手段】半導体基板2上に形成された半導体素子部100と、半導体素子部100の上部に形成された銅配線225と、半導体素子部100と銅配線225とを電気的に接続するプラグ電極216と、このプラグ電極216が酸化しないようにするシリコン酸化膜223と、半導体素子部100の上部に形成されたアモルファスシリコン膜217と、アモルファスシリコン膜217の上部に形成されたCu拡散防止膜218と、を有した半導体装置1とする。

【選択図】図1

Description

(半導体装置1の構成)

本発明の実施の形態に係る半導体装置1として、一例としてNAND型フラッシュメモリを示す。但し、本発明の実施の形態に係る半導体装置1の半導体素子部は、例えば、MOSFET、MISFET等のトランジスタ等、種々のものに適用可能である。

図2A(a)〜(c)、図2B(d),(e)、図2C(f),(g)、図2D(h),(i)は、本発明の実施の形態に係る半導体装置の製造工程を示す断面図である。

半導体装置に銅配線を使用する場合、銅元素がシリコン酸化膜(層間絶縁膜)へ拡散するのを防止するためシリコン窒化膜やシリコン酸窒化膜等のCu拡散防止膜が設けられている。

しかし、このシリコン窒化膜やシリコン酸窒化膜等を用いる場合、CVDにおける原料ガスにNH3、SiH4、O2を一般的に用いる。原料ガスの分解過程において窒素や水素が発生し、ゲート酸化膜中へも拡散する。その際、ゲート酸化膜中の欠陥と結合し電荷トラップとなりNBTI(Negative Bias Temperature Instability)劣化を加速する。

本発明の実施の形態に係る半導体装置1は、Cu拡散防止膜218の下層(半導体素子部側)にアモルファスシリコン膜217を設けているので、上記示した窒素や水素が半導体素子部側に拡散するのを効果的に抑制できる。

Claims (6)

- 半導体基板上に形成された半導体素子部と、

前記半導体素子部の上部に形成された金属配線部と、

前記半導体素子部と前記金属配線部とを電気的に接続するプラグ電極と、

前記半導体素子部の上部に形成されたアモルファスシリコン膜と、

前記アモルファスシリコン膜の上部に形成された金属拡散防止膜と、

を有することを特徴とする半導体装置。 - 前記アモルファスシリコン膜は、前記金属配線部又は前記プラグ電極と接することなく、その間に、シリコン酸化膜が形成されていることを特徴とする請求項1に記載の半導体装置。

- 前記金属拡散防止膜は、シリコン窒化膜、シリコン炭化膜、シリコン炭窒化膜、又はシリコン酸窒化膜であることを特徴とする請求項1に記載の半導体装置。

- 前記金属配線部は、銅を含む金属配線であることを特徴とする請求項1に記載の半導体装置。

- 前記アモルファスシリコン膜は、膜厚が1nm以上であることを特徴とする請求項1に記載の半導体装置。

- 半導体基板上に半導体素子部を形成する工程と、

前記半導体素子部の上部にアモルファスシリコン膜を形成する工程と、

前記アモルファスシリコン膜の上部に金属拡散防止膜を形成する工程と、

前記半導体素子部と電気的に接続されるプラグ電極、及び、金属配線部を形成する工程と、前記アモルファスシリコン膜と前記プラグ電極または金属配線部が接することなく、その間に、シリコン酸化膜を形成する工程と、を有することを特徴とする半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008276056A JP2010103445A (ja) | 2008-10-27 | 2008-10-27 | 半導体装置及びその製造方法 |

| US12/603,289 US20100102448A1 (en) | 2008-10-27 | 2009-10-21 | Semiconductor device and method of fabricating the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008276056A JP2010103445A (ja) | 2008-10-27 | 2008-10-27 | 半導体装置及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2010103445A true JP2010103445A (ja) | 2010-05-06 |

Family

ID=42116677

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008276056A Pending JP2010103445A (ja) | 2008-10-27 | 2008-10-27 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US20100102448A1 (ja) |

| JP (1) | JP2010103445A (ja) |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07221177A (ja) * | 1994-02-04 | 1995-08-18 | Matsushita Electron Corp | 半導体装置とその製造方法 |

| JPH11297701A (ja) * | 1998-04-14 | 1999-10-29 | Nippon Steel Corp | 半導体装置及びその製造方法 |

| JP2002373937A (ja) * | 2001-06-15 | 2002-12-26 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5818071A (en) * | 1995-02-02 | 1998-10-06 | Dow Corning Corporation | Silicon carbide metal diffusion barrier layer |

| JP2002075992A (ja) * | 2000-09-01 | 2002-03-15 | Fujitsu Ltd | シリコン窒化膜の成膜方法および半導体装置の製造方法および半導体装置 |

| US7091110B2 (en) * | 2002-06-12 | 2006-08-15 | Semiconductor Energy Laboratory Co., Ltd. | Method of manufacturing a semiconductor device by gettering using a anti-diffusion layer |

| US20060255398A1 (en) * | 2003-09-09 | 2006-11-16 | Tower Semiconductor Ltd. | Ultra-violet protected tamper resistant embedded EEPROM |

| US7439176B2 (en) * | 2005-04-04 | 2008-10-21 | Samsung Electronics Co., Ltd. | Semiconductor device multilayer structure, fabrication method for the same, semiconductor device having the same, and semiconductor device fabrication method |

-

2008

- 2008-10-27 JP JP2008276056A patent/JP2010103445A/ja active Pending

-

2009

- 2009-10-21 US US12/603,289 patent/US20100102448A1/en not_active Abandoned

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07221177A (ja) * | 1994-02-04 | 1995-08-18 | Matsushita Electron Corp | 半導体装置とその製造方法 |

| JPH11297701A (ja) * | 1998-04-14 | 1999-10-29 | Nippon Steel Corp | 半導体装置及びその製造方法 |

| JP2002373937A (ja) * | 2001-06-15 | 2002-12-26 | Fujitsu Ltd | 半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100102448A1 (en) | 2010-04-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR101129919B1 (ko) | 반도체 소자 및 그의 형성 방법 | |

| CN101471379B (zh) | 半导体器件及其制造工艺 | |

| US20050153544A1 (en) | Method of fabricating semiconductor device by forming diffusion barrier layer selectively and semiconductor device fabricated thereby | |

| CN101140928A (zh) | 没有栅分隔件应力的半导体器件及其制造方法 | |

| US11328994B2 (en) | Method for fabricating CU interconnection using graphene | |

| JP2008117853A (ja) | 半導体装置およびその製造方法 | |

| JP5141761B2 (ja) | 半導体装置及びその製造方法 | |

| US9412683B2 (en) | Semiconductor device having barrier metal layer | |

| US7268041B2 (en) | Method of forming source contact of flash memory device | |

| JP5178025B2 (ja) | 半導体メモリ素子の製造方法 | |

| US20250132203A1 (en) | Method for manufacturing semiconductor devices | |

| US8288279B1 (en) | Method for forming conductive contact | |

| JP2000228523A (ja) | 電界効果トランジスタおよびその製造方法 | |

| JP2010103445A (ja) | 半導体装置及びその製造方法 | |

| JP4457884B2 (ja) | 半導体装置 | |

| KR20080060928A (ko) | 반도체 소자의 금속배선 구조 및 그의 형성방법 | |

| US20140008799A1 (en) | Method for fabricating metal line and device with metal line | |

| JP2015133382A (ja) | 半導体装置の製造方法 | |

| KR20070030454A (ko) | 반도체 소자 제조방법 | |

| JP5595644B2 (ja) | 半導体装置及びその製造方法 | |

| JP2006080261A (ja) | 半導体装置の構造およびその製造方法 | |

| JP2017123388A (ja) | 半導体装置及びその製造方法 | |

| JP2006173479A (ja) | 半導体装置の製造方法 | |

| JP2008108769A (ja) | 半導体装置の製造方法 | |

| JP2000294629A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20100928 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110215 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110627 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110628 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110629 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110630 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130517 |