JP2010043927A - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP2010043927A JP2010043927A JP2008207680A JP2008207680A JP2010043927A JP 2010043927 A JP2010043927 A JP 2010043927A JP 2008207680 A JP2008207680 A JP 2008207680A JP 2008207680 A JP2008207680 A JP 2008207680A JP 2010043927 A JP2010043927 A JP 2010043927A

- Authority

- JP

- Japan

- Prior art keywords

- node

- signal

- state

- delay circuit

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R31/00—Arrangements for testing electric properties; Arrangements for locating electric faults; Arrangements for electrical testing characterised by what is being tested not provided for elsewhere

- G01R31/26—Testing of individual semiconductor devices

- G01R31/27—Testing of devices without physical removal from the circuit of which they form part, e.g. compensating for effects surrounding elements

- G01R31/275—Testing of devices without physical removal from the circuit of which they form part, e.g. compensating for effects surrounding elements for testing individual semiconductor components within integrated circuits

-

- H10P74/277—

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Semiconductor Integrated Circuits (AREA)

- Tests Of Electronic Circuits (AREA)

- Logic Circuits (AREA)

Abstract

【課題】nMOSトランジスタ及びpMOSトランジスタのそれぞれのリーク電流を正確に測定することのできる半導体集積回路を提供する。

【解決手段】半導体集積回路は、リーク電流によりノードN12をプリチャージするpMOSトランジスタQP13、及び第1の信号を出力するコンパレータ11からなる信号遅延回路10’と、リーク電流によりノードN22をプリチャージするpMOSトランジスタQP23、及び第2の信号を出力するコンパレータ21からなる信号遅延回路20’とを備える。信号遅延回路10’は、信号遅延回路20’がノードN22をプリチャージして第2の信号を出力する間にノードN12をディスチャージする一方、信号遅延回路20’は、信号遅延回路10’がノードN12をプリチャージして第1の信号を出力する間にノードN22をディスチャージする。

【選択図】図5

【解決手段】半導体集積回路は、リーク電流によりノードN12をプリチャージするpMOSトランジスタQP13、及び第1の信号を出力するコンパレータ11からなる信号遅延回路10’と、リーク電流によりノードN22をプリチャージするpMOSトランジスタQP23、及び第2の信号を出力するコンパレータ21からなる信号遅延回路20’とを備える。信号遅延回路10’は、信号遅延回路20’がノードN22をプリチャージして第2の信号を出力する間にノードN12をディスチャージする一方、信号遅延回路20’は、信号遅延回路10’がノードN12をプリチャージして第1の信号を出力する間にノードN22をディスチャージする。

【選択図】図5

Description

本発明は、半導体集積回路に関し、特に半導体基板上に形成されたトランジスタのリーク電流を測定する半導体集積回路に関する。

従来、半導体基板上に形成された半導体集積回路の性能を測定するための種々の測定装置が知られている(特許文献1参照)。特許文献1には、半導体集積回路の試験として、半導体集積回路の伝搬遅延時間を測定して良否を判定するための遅延時間測定回路及び遅延時間測定方法が記載されている。

また、半導体集積回路のトランジスタのリーク電流を測定し、その測定結果に基づいて半導体集積回路の電源電圧や基板バイアスを制御して、半導体集積回路におけるトランジスタの特性のばらつきを抑える構成が知られている。ここで、半導体基板上に形成されたトランジスタの性能を測定する方法として、チップのダイシングラインにプロセスモニタとしての4端子トランジスタを設ける方法が用いられることがある。しかし、この方法では、ダイシングラインのトランジスタに接続してトランジスタの性能を測定する専用の測定装置を外部に設ける必要があり、また、チップを切り分けた後にトランジスタの位置を特定するのが難しいという問題があった。

そのため、トランジスタの性能測定方法として、チップ上に半導体集積回路とともにリングオシレータやディレイチェーンのような形でモニタ回路を置く方法が用いられている(非特許文献1参照)。しかし、非特許文献1に記載されたリングオシレータを用いたトランジスタの測定装置では、nMOSトランジスタ及びpMOSトランジスタによる立ち上がり時間と立ち下がり時間との両方が影響するため、nMOSトランジスタ及びpMOSトランジスタのそれぞれの特性を別々に検出することができない。

特開平11−101851号公報

Tschanz, J.W.; Narendra, S.; Nair, R.; De, V. "Effectiveness of adaptive supply voltage and body bias for reducing impact of parameter variations in low power and high performance microprocessors", IEEE Journal of Solid-State Circuits, May 2003, Volume 38, Issue 5, p.826-829.

本発明は、nMOSトランジスタ及びpMOSトランジスタのそれぞれのリーク電流を正確に測定することのできる半導体集積回路を提供することを目的とする。

本発明の一態様に係る半導体集積回路は、一端を第1のノードに接続されて第1制御信号により導通又は非導通状態が切り替わり前記第1のノードをディスチャージする第1のディスチャージ素子、前記第1のノードと電源との間に接続されてリーク電流により前記第1のノードをプリチャージする第1のプリチャージ素子、及び前記第1のノードの電位を参照電位と比較して第1の信号を出力する第1の信号出力回路からなる第1の信号遅延回路と、一端を第2のノードに接続されて第2制御信号により導通又は非導通状態が切り替わり前記第2のノードをディスチャージする第2のディスチャージ素子、前記第2のノードと電源との間に接続されてリーク電流により前記第2のノードをプリチャージする第2のプリチャージ素子、及び前記第2のノードの電位を参照電位と比較して第2の信号を出力する第2の信号出力回路からなる第2の信号遅延回路と、前記第1及び第2の信号によりパルス幅が決定されるパルス信号を生成するパルス信号生成回路と、前記パルス信号を遅延させて前記第1制御信号を出力する第1の遅延回路と、前記パルス信号の反転信号を遅延させて前記第2制御信号を出力する第2の遅延回路とを備え、前記第1の信号遅延回路は、前記第2の信号遅延回路が前記第2のプリチャージ素子を介して前記第2のノードをプリチャージして前記第2の信号を出力する間に前記第1のディスチャージ素子を介して前記第1のノードをディスチャージする一方、前記第2の信号遅延回路は、前記第1の信号遅延回路が前記第1のプリチャージ素子を介して前記第1のノードをプリチャージして前記第1の信号を出力する間に前記第2のディスチャージ素子を介して前記第2のノードをディスチャージすることを特徴とする。

本発明の他の一態様に係る半導体集積回路は、第3のノードと電源との間に接続されて第3制御信号により導通又は非導通状態が切り替わり前記第3のノードをプリチャージする第3のプリチャージ素子、一端を前記第3のノードに接続されてリーク電流により前記第3のノードをディスチャージする第3のディスチャージ素子、及び前記第3のノードの電位を参照電位と比較して第3の信号を出力する第3の信号出力回路からなる第3の信号遅延回路と、第4のノードと電源との間に接続されて第4制御信号により導通又は非導通状態が切り替わり前記第4のノードをプリチャージする第4のプリチャージ素子、一端を前記第4のノードに接続されてリーク電流により前記第4のノードをディスチャージする第4のディスチャージ素子、及び前記第4のノードの電位を参照電位と比較して第4の信号を出力する第4の信号出力回路からなる第4の信号遅延回路と、前記第3及び第4の信号によりパルス幅が決定されるパルス信号を生成するパルス信号生成回路と、前記パルス信号を遅延させて前記第3制御信号を出力する第3の遅延回路と、前記パルス信号の反転信号を遅延させて前記第4制御信号を出力する第4の遅延回路とを備え、前記第3の信号遅延回路は、前記第4の信号遅延回路が前記第4のディスチャージ素子を介して前記第4のノードをディスチャージして前記第4の信号を出力する間に前記第3のプリチャージ素子を介して前記第3のノードをプリチャージする一方、前記第4の信号遅延回路は、前記第3の信号遅延回路が前記第3のディスチャージ素子を介して前記第3のノードをディスチャージして前記第3の信号を出力する間に前記第4のプリチャージ素子を介して前記第4のノードをプリチャージすることを特徴とする。

本発明によれば、nMOSトランジスタ及びpMOSトランジスタのそれぞれのリーク電流を正確に測定することのできる半導体集積回路を提供することができる。

以下、添付した図面を参照して本発明の実施の形態について説明する。

[第1の実施の形態]

(第1の実施の形態に係る半導体集積回路の構成)

図1は、本発明の実施の形態に係る半導体集積回路の基本構成、すなわち半導体基板上の集積回路が形成されるコアCとそのコアC内に設けられた制御回路の構成を示している。

(第1の実施の形態に係る半導体集積回路の構成)

図1は、本発明の実施の形態に係る半導体集積回路の基本構成、すなわち半導体基板上の集積回路が形成されるコアCとそのコアC内に設けられた制御回路の構成を示している。

図1に示すように、半導体基板上には複数のコアC(本実施の形態ではC1〜C4)が形成されている。また、コアC1〜C4にはそれぞれ制御回路が設けられている。制御回路は、コアCごとのトランジスタの特性を測定する。そして、測定されたトランジスタの特性に基づいてコアCごとに電源電圧や基板バイアスを制御して、トランジスタの特性のばらつきを抑える。本実施の形態においては、nMOSトランジスタのリーク電流の測定を行い、測定されたnMOSトランジスタの特性に基づいて、電源電圧や基板バイアスを制御する構成について説明する。なお、後述する第2の実施の形態において、pMOSトランジスタのリーク電流の測定を行い、測定されたpMOSトランジスタの特性に基づいて、電源電圧や基板バイアスを制御する構成について説明する。このnMOSトランジスタ及びpMOSトランジスタのリーク電流の測定は、組み合わせて実施することも可能である。

図1は、説明のため、コアC内には制御回路の構成のみを示しているが、コアCにはそれぞれ所定の動作を実行するように半導体集積回路が設けられている。このコアCは演算コアに限定されず、メモリマクロ単体やその一部である小さなブロック単位、あるいは演算コア群等を複合した大きなブロック単位であってもよい。

コアC内の制御回路は、nMOSリークモニタ1、pMOSリークモニタ2、発振数カウンタ3、nMOS基板制御回路4、pMOS基板制御回路5、電源電圧制御回路6からなる。

nMOSリークモニタ1は、コアCに形成されたnMOSトランジスタを流れるリーク電流を測定する。また、pMOSリークモニタ2は、コアCに形成されたpMOSトランジスタを流れるリーク電流を測定する。そして、nMOSリークモニタ1及びpMOSリークモニタ2は、各トランジスタのリーク電流量に基づくパルス幅を有するパルス信号を出力する。

発振数カウンタ3は、nMOSリークモニタ1及びpMOSリークモニタ2が出力するパルス信号の所定時間での発振数を計数して、nMOS、pMOSトランジスタのリーク電流量を測定する。nMOS基板制御回路4及びpMOS基板制御回路5は、それぞれnMOS、pMOSトランジスタのリーク電流量の値が所定の値より小さい場合に、半導体基板に順方向の基板バイアスを印加する。一方、nMOS基板制御回路4及びpMOS基板制御回路5は、それぞれnMOS、pMOSトランジスタのリーク電流量の値が所定の値より大きい場合に、半導体基板に逆方向の基板バイアスを印加する。電源電圧制御回路6は、nMOS又はpMOSトランジスタのリーク電流量の値が所定の値より小さい場合に、電源電圧を減少させ、nMOS又はpMOSトランジスタのリーク電流量の値が所定の値より大きい場合に、電源電圧を増加させる。nMOS基板制御回路4、pMOS基板制御回路5及び電源電圧制御回路6は、発振数カウンタ3で計数される各トランジスタのリーク電流量に基づく発振数が一定の値となるように基板バイアス及び電源電圧を制御するように構成されていてもよい。

次に、図2を参照してnMOSリークモニタ1の構成例について説明する。図2は、本実施の形態に係るnMOSリークモニタ1の構成例を示す回路図である。

nMOSリークモニタ1は、信号遅延回路10、20、遅延回路12、22、パルス信号生成回路30及びインバータ40を備えて構成されている。

信号遅延回路10は、pMOSトランジスタQP11、QP12、nMOSトランジスタQN10及びコンパレータ11からなる。

2つのpMOSトランジスタQP11、QP12は直列に接続されている。トランジスタQP12のソースは電源VPRE(電圧Vpre)に接続されており、トランジスタQP11のドレインはノードN12に接続されている。また、2つのトランジスタQP11、QP12のゲートには、ノードN11がそれぞれ接続されている。このノードN11の電位が“L”状態のとき2つのトランジスタQP11、QP12は導通して、ノードN12を電源VPREの電圧Vpreまで充電(プリチャージ)して、ノードN12の電位を上昇させる。

また、nMOSトランジスタQN10は、ドレインがノードN12に接続されており、ゲート及びソースが接地されている。このトランジスタQN10は、ノードN12に接続されたドレイン側から接地されたソース側にリーク電流を流すことによりノードN12を放電(ディスチャージ)して、ノードN12の電位を低下させる。nMOSリークモニタ1は、このnMOSトランジスタQN10のリーク電流量を測定する。ここで、リーク電流が測定されるトランジスタQN10は、コアC内のその他の回路に用いられるトランジスタと同一の工程により形成されており、特性の面でコアC内の他のnMOSトランジスタと一定の関係を有している。

そして、コンパレータ11は、ノードN12及び電源VREF(電位Vref)に接続されたノードN13が入力端子に接続されている。コンパレータ11は、ノードN12の電位がノードN13の電位Vrefよりも高い場合には“H”信号をノードN14に出力する。一方、ノードN12の電位がノードN13の電位Vrefよりも低い場合には“L”信号をノードN14に出力する。

信号遅延回路10は、全体として、ノードN11から入力された信号をnMOSトランジスタQN10のリーク電流量に基づく量だけ遅延させてノードN14に出力する。

遅延回路12は、バッファとしての複数段のインバータにより構成され、後述するパルス信号生成回路30から出力されたノードN32の“H”信号又は“L”信号を所定時間遅延させてノードN11に入力するために用いられる。

ここで、信号遅延回路20は、pMOSトランジスタQP21、QP22、nMOSトランジスタQN20及びコンパレータ21からなる。信号遅延回路20のトランジスタQP21、QP22は信号遅延回路10のトランジスタQP11、QP12と対応し、nMOSトランジスタQN20及びコンパレータ21は、nMOSトランジスタQN10及びコンパレータ11と対応する同様の構成を有しているため、その説明を省略する。

nMOSリークモニタ1において、信号遅延回路10、20は、一方のノード(例えばノードN12)をディスチャージしてトランジスタQN10のリーク電流量を測定している間に、他方のノード(例えばノードN22)のプリチャージを行う。そのため、ノードN12、N22のプリチャージ時間は、nMOSトランジスタQN10、QN20のディスチャージ時間に基づくリーク電流の測定に影響を与えることがない。

また、遅延回路22は、バッファとしての複数段のインバータにより構成され、後述するパルス信号生成回路30から出力されたノードN31の“H”信号又は“L”信号を所定時間遅延させてノードN21に入力するために用いられる。

パルス信号生成回路30は、ノードN14及びノードN24が論理ゲート31及び論理ゲート32の入力端子にそれぞれ接続されたセット/リセットフリップフロップ回路である。パルス信号生成回路30は、ノードN14及びノードN24の信号に基づいてパルス幅が決定されるパルス信号を生成する。このパルス信号は、インバータ40を介してnMOSリークモニタ1の出力信号として出力される。また、論理ゲート31の出力端子に接続されたノードN31は、遅延回路22を介してノードN21に接続されており、論理ゲート32の出力端子に接続されたノードN32は、遅延回路12を介してノードN11に接続されている。

(第1の実施の形態に係る半導体集積回路の動作)

次に、図3を参照してnMOSリークモニタ1の動作について説明する。図3は、本実施の形態に係るnMOSリークモニタ1の動作における各ノードの電位を示すタイミングチャートである。

次に、図3を参照してnMOSリークモニタ1の動作について説明する。図3は、本実施の形態に係るnMOSリークモニタ1の動作における各ノードの電位を示すタイミングチャートである。

nMOSリークモニタ1は、半導体集積回路の動作とともにnMOSトランジスタQN10、QN20のリーク電流の測定を開始する。ある時刻t0において、パルス信号生成回路30の2つの論理ゲート31、32から出力されるノードN31、N32の状態は、前者が“L”状態から“H”状態へ、後者が“H”状態から“L”状態に切り替わるものとする。また、時刻t0において、ノードN11、N22、N24の電位は“H”状態、ノードN12、N14、N21の電位は“L”状態であるものとする。

時刻t1において、ノードN31の“H”状態の電位が遅延回路22により所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“L”状態から“H”状態に変化する。同様に、ノードN32の“L”状態の電位が遅延回路12により所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“H”状態から“L”状態に変化する。ここで、遅延回路12、22による遅延時間はt1−t0である。

ノードN11の電位が“L”状態であるため、pMOSトランジスタQP11、QP12のゲートが“L”状態となる。そのため、pMOSトランジスタQP11、QP12が導通し、電源VPREによりノードN12がプリチャージされ、電位が“H”状態となる。ここで、ノードN12の電位が、ノードN13の電位Vrefを超えたときに、コンパレータ11の出力信号が反転し、ノードN14の電位が“L”状態から“H”状態となる。

一方、ノードN21に与えられた“H”状態の電位により、pMOSトランジスタQP21、QP22が非導通状態となり、ノードN22へのプリチャージが停止する。プリチャージが停止されたノードN22からは、トランジスタQN20を介してリーク電流が流れ、電位が漸減していく。

時刻t2において、ノードN22の電位がノードN23の電位Vrefを下回った時点で、コンパレータ21から出力されているノードN24の“H”状態が“L”状態に反転する。

時刻t3において、ノードN24の電位が“H”状態から“L”状態に変化するとともに、パルス信号生成回路30の出力信号も反転する。すなわち論理ゲート32にはノードN24の“L”状態が与えられて、ノードN32が“L”状態から“H”状態に変化する。論理ゲート31にはノードN32の“H”状態及びノードN14の“H”状態が与えられて、ノードN31が“H”状態から“L”状態に変化する。

時刻t4において、“H”状態に変化したノードN32の電位が遅延回路12により所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“L”状態から“H”状態に変化する。同様に、“L”状態に変化したノードN31の電位が遅延回路22により所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“H”状態から“L”状態に変化する。ここで、遅延回路12、22による遅延時間はt4−t3(=t1−t0)である。

ノードN11に与えられた“H”状態の電位により、pMOSトランジスタQP11、QP12が非導通状態となり、時刻t4以降ノードN12へのプリチャージが停止する。プリチャージが停止されたノードN12からは、トランジスタQN10を介してリーク電流が流れ、電位が漸減していく。

一方、ノードN21の電位が“L”状態であるため、pMOSトランジスタQP21、QP22のゲートが“L”状態となる。そのため、pMOSトランジスタQP21、QP22が導通し、電源VPREによりノードN22がプリチャージされ、電位が“H”状態となる。ここで、ノードN22の電位が、ノードN23の電位Vrefを超えたとき(時刻t4−1)に、コンパレータ21の出力信号が反転し、ノードN24の電位が“L”状態から“H”状態となる。

このように、nMOSリークモニタ1において、信号遅延回路10のノードN12をディスチャージしてトランジスタQN10に流れるリーク電流量を測定している間に、信号遅延回路20のノードN22のプリチャージを行う。ノードN22のプリチャージ時間は、nMOSトランジスタQN10のディスチャージ時間に基づくリーク電流の測定に影響を与えることがない。

時刻t5において、ノードN12の電位がノードN13の電位Vrefを下回った時点でコンパレータ11から出力されているノードN14の“H”状態が“L”状態に反転する。

時刻t6において、ノードN14の電位が“H”状態から“L”状態に変化するとともに、パルス信号生成回路30の出力信号も反転する。すなわち論理ゲート31にはノードN14の“L”状態が与えられて、ノードN31が“L”状態から“H”状態に変化する。論理ゲート32にはノードN31の“H”状態及びノードN24の“H”状態が与えられて、ノードN32が“H”状態から“L”状態に変化する。

時刻t7において、“H”状態に変化したノードN31の電位が遅延回路22により所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“L”状態から“H”状態に変化する。同様に、“L”状態に変化したノードN32の電位が遅延回路12により所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“H”状態から“L”状態に変化する。ここで、遅延回路12、22による遅延時間はt7−t6(=t4−t3=t1−t0)である。

ノードN11の電位が“L”状態であるため、pMOSトランジスタQP11、QP12のゲートが“L”状態となる。そのため、pMOSトランジスタQP11、QP12が導通し、電源VPREによりノードN12がプリチャージされ、電位が“H”状態となる。ここで、ノードN12の電位が、ノードN13の電位Vrefを超えたときに、コンパレータ11の出力信号が反転し、ノードN14の電位が“L”状態から“H”状態となる。

一方、ノードN21に与えられた“H”状態の電位により、pMOSトランジスタQP21、QP22が非導通状態となり、時刻t7以降ノードN22へのプリチャージが停止する。プリチャージが停止されたノードN22からは、トランジスタQN20を介してリーク電流が流れ、電位が漸減していく。

そして、時刻t8において、各ノードの電位は時刻t2と同様の電位の状態となる。以下、時刻t8、t9、t10・・・において、nMOSリークモニタ1は、時刻t2、t3、t4・・・と同様の動作を繰り返す。

これにより、ノードN31の状態は、“H”状態と“L”状態とを繰り返す。そして、このノード31の状態がインバータ40を介してnMOSリークモニタ1の出力信号として出力される。

このリーク電流量の測定において、遅延回路12、22による遅延時間(t7−t6=t4−t3=t1−t0)は、遅延回路12、22の構成により決定され、遅延時間は所定の値となる。また、パルス信号生成回路30の状態の変化に要する時間(t3−t2、t6−t5、t9−t8)も、パルス信号生成回路の構成により決定され、パルス信号生成回路30の状態の変化に要する時間は所定の値となる。

そのため、ノードN31の発振の1周期の半分(時刻t2〜t5)に要する時間は、トランジスタQN10を流れるリーク電流によりノードN12の電位が電位Vrefまで低下する時間(時刻t4〜t5)に基づいて決定される。同様に、ノードN31の発振の1周期の半分(時刻t5〜t8)に要する時間は、トランジスタQN20を流れるリーク電流によりノードN22の電位が電位Vrefまで低下する時間(時刻t7〜t8)に基づいて決定される。よって、nMOSリークモニタ1の出力するパルス信号は、nMOSトランジスタQN10、QN20のリーク電流に基づいて決定される周波数を有することになる。

ここで、nMOSリークモニタ1において、信号遅延回路10のノードN12をディスチャージしてトランジスタQN10に流れるリーク電流量を測定している間に、信号遅延回路20のノードN22のプリチャージが行われている。同様に、信号遅延回路20のノードN22をディスチャージしてトランジスタQN20に流れるリーク電流量を測定している間に、信号遅延回路10のノードN12のプリチャージが行われている。nMOSリークモニタ1は、ノードN12、N22のディスチャージに要する時間に基づいてパルス信号を出力するため、ノードN12、N22のプリチャージに要する時間がnMOSリークモニタ1の出力するパルス信号に反映されることはない。

発振数カウンタ3は、nMOSリークモニタ1が出力するパルス信号の発振数を計数してnMOSトランジスタQN10、QN20のリーク電流量を測定する。nMOS基板制御回路4は、nMOSトランジスタQN10、QN20のリーク電流量の値が所定の値より小さい場合に、半導体基板に印加される基板バイアスを大きくする。一方、nMOS基板制御回路4は、各トランジスタのリーク電流量の値が所定の値以上である場合に、半導体基板に印加される基板バイアスを小さくする。電源電圧制御回路6は、nMOSトランジスタQN10、QN20のリーク電流量の値が所定の値より小さい場合に、電源電圧を減少させ、各トランジスタのリーク電流量の値が所定の値より大きい場合に、電源電圧を増加させる。

(第1の実施の形態に係る半導体集積回路の効果)

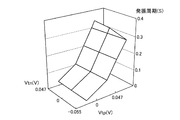

このように、本実施の形態の半導体集積回路は、nMOSトランジスタQN10、QN20のリーク電流に基づいて決定される周波数を有する信号を出力するnMOSリークモニタ1を有する。ここで、図2に示すnMOSリークモニタ1を用いたnMOSトランジスタのリーク電流測定のシミュレーション結果を図4に示す。図4において、軸Vtnは、nMOSリークモニタ1のnMOSトランジスタQN10、QN20のしきい値電圧を示し、軸Vtpは、nMOSリークモニタ1のpMOSトランジスタQP11、QP12又はQP21、QP22のしきい値電圧を示す。軸Vtn、軸Vtpにおいては、しきい値電圧0(V)で示している箇所が各トランジスタに求められるしきい値電圧を有する場合を示し、軸Vtn、軸Vtpはその求められるしきい値電圧からの変動量を示している。また、縦軸は、nMOSリークモニタ1から出力されるパルス信号の発振周期である。

このように、本実施の形態の半導体集積回路は、nMOSトランジスタQN10、QN20のリーク電流に基づいて決定される周波数を有する信号を出力するnMOSリークモニタ1を有する。ここで、図2に示すnMOSリークモニタ1を用いたnMOSトランジスタのリーク電流測定のシミュレーション結果を図4に示す。図4において、軸Vtnは、nMOSリークモニタ1のnMOSトランジスタQN10、QN20のしきい値電圧を示し、軸Vtpは、nMOSリークモニタ1のpMOSトランジスタQP11、QP12又はQP21、QP22のしきい値電圧を示す。軸Vtn、軸Vtpにおいては、しきい値電圧0(V)で示している箇所が各トランジスタに求められるしきい値電圧を有する場合を示し、軸Vtn、軸Vtpはその求められるしきい値電圧からの変動量を示している。また、縦軸は、nMOSリークモニタ1から出力されるパルス信号の発振周期である。

図4に示すように、nMOSリークモニタ1において、nMOSトランジスタQN10、QN20のリーク電流量が変化してしきい値電圧が変動した場合、パルス信号の発振周期は大きく変化する。一方、pMOSトランジスタQP11、QP12又はQP21、QP22のリーク電流が変化してしきい値電圧が変動した場合、パルス信号の発振周期はほとんど変化しない。このため、nMOSリークモニタ1は、pMOSトランジスタQP11、QP12又はQP21、QP22のリーク電流量に関わらず、nMOSトランジスタQN10、QN20のリーク電流量を測定することができる。

また、nMOSリークモニタ1において、2つのnMOSトランジスタQN10、QN20のうち、一方のノードをディスチャージしてトランジスタのリーク電流量を測定している間に、他方のトランジスタが接続されたノードのプリチャージを行っている。そのため、ノードN12、N22のプリチャージ時間は、nMOSトランジスタQN10、QN20のリーク電流の測定に影響を与えることがない。

そして、nMOSリークモニタ1において、pMOSトランジスタQP11、QP12又はQP21、QP22は、直列接続されている。pMOSトランジスタが非導通状態となり、nMOSトランジスタのリーク電流を測定する際、2つのpMOSトランジスタの中間ノードの電圧が下がる。そのため、それぞれのpMOSトランジスタのドレイン−ソース間電圧が減少してpMOSトランジスタからのリーク電流が減る。これとともに、pMOSトランジスタQP11、QP21には基板バイアスがかかり、pMOSトランジスタからのリーク電流をさらに減らすことができる。よって、pMOSトランジスタQP11、QP12又はQP21、QP22からのリーク電流による測定誤差を低減することができる。

本実施の形態に係る半導体集積回路によれば、pMOSトランジスタの影響を受けることなくnMOSトランジスタのリーク電流を正確に測定することができる。

[第2の実施の形態]

(第2の実施の形態に係る半導体集積回路の構成)

次に、本発明に係る半導体集積回路の第2の実施の形態について図5を参照して説明する。図5は、本実施の形態に係るpMOSリークモニタ2の構成例を示す回路図である。

(第2の実施の形態に係る半導体集積回路の構成)

次に、本発明に係る半導体集積回路の第2の実施の形態について図5を参照して説明する。図5は、本実施の形態に係るpMOSリークモニタ2の構成例を示す回路図である。

ここで、第2の実施形態に係るpMOSリークモニタ2の構成は、第1の実施形態に係るnMOSリークモニタ1とほぼ同様である。第2の実施の形態に係るpMOSリークモニタ2において、第1の実施の形態と同一の構成を有する箇所には、同一の符号を付すことによりその説明を省略する。本実施の形態に係るpMOSリークモニタ2は、信号遅延回路10’の構成が、第1の実施の形態に係る信号遅延回路10と異なる。また、遅延回路12、22が奇数段のインバータにより構成されている点においても第1の実施の形態に係る信号遅延回路10と異なる。

信号遅延回路10’は、pMOSトランジスタQP13、nMOSトランジスタQN14、QN15、コンパレータ11及びインバータ14からなる。

pMOSトランジスタQP13は、ドレインがノードN12に接続されており、ゲート及びソースが電源VPRE(電圧Vpre)に接続されている。このトランジスタQP13は、電源VPREに接続されたソース側からノードN12に接続されたドレイン側にリーク電流を流すことによりノードN12を充電(プリチャージ)して、ノードN12の電位を上昇させる。pMOSリークモニタ2は、このpMOSトランジスタQP13のリーク電流量を測定する。ここで、リーク電流が測定されるトランジスタQP13は、コアC内のその他の回路に用いられるトランジスタと同一の工程により形成されており、特性の面でコアC内の他のpMOSトランジスタと一定の関係を有している。

また、2つのnMOSトランジスタQN14、QN15は直列に接続されている。トランジスタQN14のドレインはノードN12に接続されており、トランジスタQN15のソースは接地されている。また、2つのトランジスタQN14、QN15のゲートには、ノードN11がそれぞれ接続されている。このノードN11の電位が“H”状態のとき2つのトランジスタQN14、QN15は導通して、ノードN12を放電(ディスチャージ)して、ノードN12の電位を低下させる。

そして、コンパレータ11は、ノードN12及び電源VREF(電位Vref)に接続されたノードN13が入力端子に接続されている。コンパレータ11は、ノードN12の電位がノードN13の電位Vrefよりも高い場合には“H”信号をインバータ14に出力し、インバータ14は“L”信号をノードN14に出力する。一方、コンパレータ11は、ノードN12の電位がノードN13の電位Vrefよりも低い場合には“L”信号をインバータ14に出力し、インバータ14は“H”信号をノードN14に出力する。

信号遅延回路10’は、全体として、ノードN11から入力された信号をpMOSトランジスタQP13のリーク電流量に基づく量だけ遅延させてノードN14に出力する。

また、奇数段のインバータにより構成された遅延回路12、22は、パルス信号生成回路30から出力されたノードN31、N32の“H”信号又は“L”信号を反転させてノードN11に入力するために用いられる。

ここで、信号遅延回路20’は、pMOSトランジスタQP23、nMOSトランジスタQN24、QN25、コンパレータ21及びインバータ24からなる。信号遅延回路20’のトランジスタQP23は信号遅延回路10’のトランジスタQP13と対応し、nMOSトランジスタQN24、QN25、コンパレータ21及びインバータ24は、nMOSトランジスタQN14、QN15、コンパレータ11及びインバータ14と対応する同様の構成を有しているため、その説明を省略する。

pMOSリークモニタ2において、信号遅延回路10’、20’は、一方のノード(例えばノードN12)をプリチャージしてトランジスタQP13のリーク電流量を測定している間に、他方のノード(例えばノードN22)のディスチャージを行う。そのため、ノードN12、N22の一方のディスチャージ時間は、他方のプリチャージ時間に基づくリーク電流の測定に影響を与えることがない。

(第2の実施の形態に係る半導体集積回路の動作)

次に、図6を参照してpMOSリークモニタ2の動作について説明する。図6は、本実施の形態に係るpMOSリークモニタ2の動作における各ノードの電位を示すタイミングチャートである。

次に、図6を参照してpMOSリークモニタ2の動作について説明する。図6は、本実施の形態に係るpMOSリークモニタ2の動作における各ノードの電位を示すタイミングチャートである。

pMOSリークモニタ2は、半導体集積回路の動作とともにpMOSトランジスタQP13、QP23のリーク電流の測定を開始する。ある時刻t20において、パルス信号生成回路30の2つの論理ゲート31、32から出力されるノードN31、N32の状態は、前者が“L”状態から“H”状態へ、後者が“H”状態から“L”状態に切り替わるものとする。また、時刻t20において、ノードN12、N21、N24の電位は“H”状態、ノードN11、N14、N22の電位は“L”状態であるものとする。

時刻t21において、“H”状態に変化したノードN31の電位が、遅延回路22により反転し、所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“H”状態から“L”状態に変化する。同様に、“L”状態に変化したノードN32の電位が、遅延回路12により反転し、所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“L”状態から“H”状態に変化する。ここで、遅延回路12、22による遅延時間はt21−t20である。

ノードN11に与えられた“H”状態の電位により、nMOSトランジスタQN14、QN15が導通状態となり、ノードN12へのプリチャージが停止する。プリチャージが停止されたノードN12からは、トランジスタQN14、QN15を介して電流が流れ、電位が“H”状態から“L”状態となる。

一方、ノードN21の電位が“L”状態であるため、nMOSトランジスタQN24、QN25のゲートが“L”状態となる。そのため、nMOSトランジスタQN24、QN25は非導通状態となり、pMOSトランジスタQP23のリーク電流によりノードN22がプリチャージされる。

時刻t22において、ノードN22の電位がノードN23の電位Vrefを上回った時点で、インバータ24を介してコンパレータ21から出力されているノードN24の“H”状態が“L”状態に反転する。

時刻t23において、ノードN24の電位が“H”状態から“L”状態に変化するとともに、パルス信号生成回路30の出力信号も反転する。すなわち論理ゲート32にはノードN24の“L”状態が与えられて、ノードN32が“L”状態から“H”状態に変化する。論理ゲート31にはノードN32の“H”状態及びノードN14の“H”状態が与えられて、ノードN31が“H”状態から“L”状態に変化する。

時刻t24において、“H”状態に変化したノードN32の電位が、遅延回路12により反転し、所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“H”状態から“L”状態に変化する。同様に、“L”状態に変化したノードN31の電位が、遅延回路22により反転し、所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“L”状態から“H”状態に変化する。ここで、遅延回路12、22による遅延時間はt24−t23(=t21−t20)である。

ノードN11の電位が“L”状態であるため、nMOSトランジスタQN14、QN15のゲートが“L”状態となる。そのため、nMOSトランジスタQN14、QN15は非導通状態となり、pMOSトランジスタQP13のリーク電流によりノードN12がプリチャージされる。

一方、ノードN21に与えられた“H”状態の電位により、nMOSトランジスタQN24、QN25が導通状態となり、ノードN22へのプリチャージが停止する。プリチャージが停止されたノードN22からは、トランジスタQN24、QN25を介して電流が流れ、電位が“H”状態から“L”状態となる。

このように、pMOSリークモニタ2において、信号遅延回路10’のノードN12をプリチャージしてトランジスタQP13に流れるリーク電流量を測定している間に、信号遅延回路20’のノードN22のディスチャージを行う。ノードN22のディスチャージ時間は、ノードN12のプリチャージ時間に基づくリーク電流の測定に影響を与えることがない。

時刻t25において、ノードN12の電位がノードN13の電位Vrefを上回った時点で、インバータ14を介してコンパレータ11から出力されているノードN14の“H”状態が“L”状態に反転する。

時刻t26において、ノードN14の電位が“H”状態から“L”状態に変化するとともに、パルス信号生成回路30の出力信号も反転する。すなわち論理ゲート31にはノードN14の“L”状態が与えられて、ノードN31が“L”状態から“H”状態に変化する。論理ゲート32にはノードN31の“H”状態及びノードN24の“H”状態が与えられて、ノードN32が“H”状態から“L”状態に変化する。

時刻t27において、“H”状態に変化したノードN31の電位が、遅延回路22により反転し、所定時間だけ遅れてノードN21に与えられる。これによりノードN21が“H”状態から“L”状態に変化する。同様に、“L”状態に変化したノードN32の電位が、遅延回路12により反転し、所定時間だけ遅れてノードN11に与えられる。これによりノードN11が“L”状態から“H”状態に変化する。ここで、遅延回路12、22による遅延時間はt27−t26(=t24−t23=t21−t20)である。

ノードN11に与えられた“H”状態の電位により、nMOSトランジスタQN14、QN15が導通状態となり、ノードN12へのプリチャージが停止する。プリチャージが停止されたノードN12からは、トランジスタQN14、QN15を介して電流が流れ、電位が“H”状態から“L”状態となる。

一方、ノードN21の電位が“L”状態であるため、nMOSトランジスタQN24、QN25のゲートが“L”状態となる。そのため、nMOSトランジスタQN24、QN25は非導通状態となり、pMOSトランジスタQP23のリーク電流によりノードN22がプリチャージされる。

そして、時刻t28において、各ノードの電位は時刻t22と同様の電位の状態となる。以下、時刻t28、t29、t30・・・において、pMOSリークモニタ2は、時刻t22、t23、t24・・・と同様の動作を繰り返す。

これにより、ノードN31の状態は、“H”状態と“L”状態とを繰り返す。そして、このノード31の状態がインバータ40を介してpMOSリークモニタ2の出力信号として出力される。

このリーク電流量の測定において、遅延回路12、22による遅延時間(t27−t26=t24−t23=t21−t20)は、遅延回路12、22の構成により決定され、遅延時間は所定の値となる。また、パルス信号生成回路30の状態の変化に要する時間(t23−t22、t26−t25、t29−t28)も、パルス信号生成回路の構成により決定され、パルス信号生成回路30の状態の変化に要する時間は所定の値となる。

そのため、ノードN31の発振の1周期の半分(時刻t22〜t25)に要する時間は、トランジスタQP13を流れるリーク電流によりノードN12の電位が電位Vrefまで上昇する時間(時刻t24〜t25)に基づいて決定される。同様に、ノードN31の発振の1周期の半分(時刻t25〜t28)に要する時間は、トランジスタQP23を流れるリーク電流によりノードN22の電位が電位Vrefまで上昇する時間(時刻t27〜t28)に基づいて決定される。よってpMOSリークモニタ2の出力するパルス信号は、pMOSトランジスタQP13、QP23のリーク電流に基づいて決定される周波数を有することになる。

ここで、pMOSリークモニタ2において、信号遅延回路10’のノードN12をプリチャージしてトランジスタQP13に流れるリーク電流量を測定している間に、信号遅延回路20’のノードN22のディスチャージが行われている。同様に、信号遅延回路20’のノードN22をプリチャージしてトランジスタQP23に流れるリーク電流量を測定している間に、信号遅延回路10’のノードN12のディスチャージが行われている。pMOSリークモニタ2は、ノードN12、N22のプリチャージに要する時間に基づいてパルス信号を出力するため、ノードN12、N22のディスチャージに要する時間がpMOSリークモニタ2の出力するパルス信号に反映されることはない。

発振数カウンタ3は、pMOSリークモニタ2が出力するパルス信号の発振数を計数してpMOSトランジスタQP13、QP23のリーク電流量を測定する。pMOS基板制御回路5は、pMOSトランジスタQP13、QP23のリーク電流量の値が所定の値より小さい場合に、半導体基板に印加される基板バイアスを大きくする。一方、pMOS基板制御回路5は、各トランジスタのリーク電流量の値が所定の値以上である場合に、半導体基板に印加する基板バイアスを小さくする。電源電圧制御回路6は、pMOSトランジスタQP13、QP23のリーク電流量の値が所定の値より小さい場合に、電源電圧を減少させ、各トランジスタのリーク電流量の値が所定の値より大きい場合に、電源電圧を増加させる。

(第2の実施の形態に係る半導体集積回路の効果)

このように、本実施の形態の半導体集積回路は、pMOSトランジスタQP13、QP23のリーク電流に基づいて決定される周波数を有する信号を出力するpMOSリークモニタ2を有する。ここで、図5に示すpMOSリークモニタ2を用いたpMOSトランジスタのリーク電流測定のシミュレーション結果を図7に示す。

このように、本実施の形態の半導体集積回路は、pMOSトランジスタQP13、QP23のリーク電流に基づいて決定される周波数を有する信号を出力するpMOSリークモニタ2を有する。ここで、図5に示すpMOSリークモニタ2を用いたpMOSトランジスタのリーク電流測定のシミュレーション結果を図7に示す。

図7に示すように、pMOSリークモニタ2において、pMOSトランジスタQP13、QP23のリーク電流量が変化してしきい値電圧が変動した場合、パルス信号の発振周期は大きく変化する。一方、nMOSトランジスタQN14、QN15又はQN24、QN25のリーク電流が変化してしきい値電圧が変動した場合、パルス信号の発振周期はほとんど変化しない。このため、pMOSリークモニタ2は、nMOSトランジスタQN14、QN15又はQN24、QN25のリーク電流量に関わらず、pMOSトランジスタQP13、QP23のリーク電流量を測定することができる。

また、pMOSリークモニタ2において、2つのpMOSトランジスタQP13、QP23のうち、一方のノードをプリチャージしてトランジスタのリーク電流量を測定している間に、他方のトランジスタが接続されたノードのディスチャージを行っている。そのため、ノードN12、N22のディスチャージ時間は、pMOSトランジスタQP13、QP23のリーク電流の測定に影響を与えることがない。

そして、pMOSリークモニタ2において、nMOSトランジスタQN14、QN15又はQN24、QN25は、直列接続されている。これにより第1の実施の形態と同様に、nMOSトランジスタQN14、QN15又はQN24、QN25へのリーク電流による測定誤差を低減することができる。

本実施の形態に係る半導体集積回路によれば、nMOSトランジスタの影響を受けることなくpMOSトランジスタのリーク電流を正確に測定することができる。

以上、本発明の実施の形態を説明したが、本発明はこれらに限定されるものではなく、発明の趣旨を逸脱しない範囲内において種々の変更、追加、組み合わせ等が可能である。例えば、第1の実施の形態のpMOSトランジスタQP11及びQP12、QP21及び22、第2の実施の形態のnMOSトランジスタQN14及びQN15、QN24及びQN25は、直列接続されていたが、これはそれぞれ1つのトランジスタにより構成することもできる。また、パルス信号生成部30には、論理ゲート31、32としてNANDゲートを用いているが、この論理ゲートとしてNORゲートを用いてパルス信号生成部30を構成することも可能である。

1・・・nMOSリークモニタ、 2・・・pMOSリークモニタ、 3・・・発振数カウンタ、 4・・・nMOS基板制御回路、 5・・・pMOS基板制御回路、 6・・・電源電圧制御回路、 10、20・・・信号遅延回路、 11、21・・・コンパレータ、 12、22・・・遅延回路 14、24・・・インバータ、 30・・・パルス信号生成回路、 31、32・・・論理ゲート、 40・・・インバータ。

Claims (5)

- 一端を第1のノードに接続されて第1制御信号により導通又は非導通状態が切り替わり前記第1のノードをディスチャージする第1のディスチャージ素子、前記第1のノードと電源との間に接続されてリーク電流により前記第1のノードをプリチャージする第1のプリチャージ素子、及び前記第1のノードの電位を参照電位と比較して第1の信号を出力する第1の信号出力回路からなる第1の信号遅延回路と、

一端を第2のノードに接続されて第2制御信号により導通又は非導通状態が切り替わり前記第2のノードをディスチャージする第2のディスチャージ素子、前記第2のノードと電源との間に接続されてリーク電流により前記第2のノードをプリチャージする第2のプリチャージ素子、及び前記第2のノードの電位を参照電位と比較して第2の信号を出力する第2の信号出力回路からなる第2の信号遅延回路と、

前記第1及び第2の信号によりパルス幅が決定されるパルス信号を生成するパルス信号生成回路と、

前記パルス信号を遅延させて前記第1制御信号を出力する第1の遅延回路と、

前記パルス信号の反転信号を遅延させて前記第2制御信号を出力する第2の遅延回路と

を備え、

前記第1の信号遅延回路は、前記第2の信号遅延回路が前記第2のプリチャージ素子を介して前記第2のノードをプリチャージして前記第2の信号を出力する間に前記第1のディスチャージ素子を介して前記第1のノードをディスチャージする一方、前記第2の信号遅延回路は、前記第1の信号遅延回路が前記第1のプリチャージ素子を介して前記第1のノードをプリチャージして前記第1の信号を出力する間に前記第2のディスチャージ素子を介して前記第2のノードをディスチャージする

ことを特徴とする半導体集積回路。 - 第3のノードと電源との間に接続されて第3制御信号により導通又は非導通状態が切り替わり前記第3のノードをプリチャージする第3のプリチャージ素子、一端を前記第3のノードに接続されてリーク電流により前記第3のノードをディスチャージする第3のディスチャージ素子、及び前記第3のノードの電位を参照電位と比較して第3の信号を出力する第3の信号出力回路からなる第3の信号遅延回路と、

第4のノードと電源との間に接続されて第4制御信号により導通又は非導通状態が切り替わり前記第4のノードをプリチャージする第4のプリチャージ素子、一端を前記第4のノードに接続されてリーク電流により前記第4のノードをディスチャージする第4のディスチャージ素子、及び前記第4のノードの電位を参照電位と比較して第4の信号を出力する第4の信号出力回路からなる第4の信号遅延回路と、

前記第3及び第4の信号によりパルス幅が決定されるパルス信号を生成するパルス信号生成回路と、

前記パルス信号を遅延させて前記第3制御信号を出力する第3の遅延回路と、

前記パルス信号の反転信号を遅延させて前記第4制御信号を出力する第4の遅延回路と

を備え、

前記第3の信号遅延回路は、前記第4の信号遅延回路が前記第4のディスチャージ素子を介して前記第4のノードをディスチャージして前記第4の信号を出力する間に前記第3のプリチャージ素子を介して前記第3のノードをプリチャージする一方、前記第4の信号遅延回路は、前記第3の信号遅延回路が前記第3のディスチャージ素子を介して前記第3のノードをディスチャージして前記第3の信号を出力する間に前記第4のプリチャージ素子を介して前記第4のノードをプリチャージする

ことを特徴とする半導体集積回路。 - 第3のノードと電源との間に接続されて第3制御信号により導通又は非導通状態が切り替わり前記第3のノードをプリチャージする第3のプリチャージ素子、一端を前記第3のノードに接続されてリーク電流により前記第3のノードをディスチャージする第3のディスチャージ素子、及び前記第3のノードの電位を参照電位と比較して第3の信号を出力する第3の信号出力回路からなる第3の信号遅延回路と、

第4のノードと電源との間に接続されて第4制御信号により導通又は非導通状態が切り替わり前記第4のノードをプリチャージする第4のプリチャージ素子、一端を前記第4のノードに接続されてリーク電流により前記第4のノードをディスチャージする第4のディスチャージ素子、及び前記第4のノードの電位を参照電位と比較して第4の信号を出力する第4の信号出力回路からなる第4の信号遅延回路と、

前記第3及び第4の信号によりパルス幅が決定されるパルス信号を生成するパルス信号生成回路と、

前記パルス信号を遅延させて前記第3制御信号を出力する第3の遅延回路と、

前記パルス信号の反転信号を遅延させて前記第4制御信号を出力する第4の遅延回路と

をさらに備え、

前記第3の信号遅延回路は、前記第4の信号遅延回路が前記第4のディスチャージ素子を介して前記第4のノードをディスチャージして前記第4の信号を出力する間に前記第3のプリチャージ素子を介して前記第3のノードをプリチャージする一方、前記第4の信号遅延回路は、前記第3の信号遅延回路が前記第3のディスチャージ素子を介して前記第3のノードをディスチャージして前記第3の信号を出力する間に前記第4のプリチャージ素子を介して前記第4のノードをプリチャージする

ことを特徴とする請求項1記載の半導体集積回路。 - 前記第1のディスチャージ素子、前記第2のディスチャージ素子、前記第3のプリチャージ素子又は前記第4のプリチャージ素子は、直列接続された複数のトランジスタである

ことを特徴とする請求項1乃至3のいずれか記載の半導体集積回路。 - 前記パルス信号に基づいて、半導体基板に印加される基板バイアスを制御する基板バイアス制御回路をさらに有する

ことを特徴とする請求項1乃至3のいずれか記載の半導体集積回路。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207680A JP4693880B2 (ja) | 2008-08-12 | 2008-08-12 | 半導体集積回路 |

| US12/537,447 US7915932B2 (en) | 2008-08-12 | 2009-08-07 | Semiconductor integrated circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008207680A JP4693880B2 (ja) | 2008-08-12 | 2008-08-12 | 半導体集積回路 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010043927A true JP2010043927A (ja) | 2010-02-25 |

| JP4693880B2 JP4693880B2 (ja) | 2011-06-01 |

Family

ID=41680903

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008207680A Expired - Fee Related JP4693880B2 (ja) | 2008-08-12 | 2008-08-12 | 半導体集積回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7915932B2 (ja) |

| JP (1) | JP4693880B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9041407B2 (en) | 2011-11-28 | 2015-05-26 | Sony Corporation | Oscillation circuit and test circuit |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5185304B2 (ja) | 2010-02-10 | 2013-04-17 | 株式会社東芝 | 半導体集積回路 |

| US10394471B2 (en) * | 2016-08-24 | 2019-08-27 | Qualcomm Incorporated | Adaptive power regulation methods and systems |

| KR102336181B1 (ko) * | 2017-06-07 | 2021-12-07 | 삼성전자주식회사 | 누설 전류 측정 회로, 이를 포함하는 집적 회로 및 시스템 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05250897A (ja) * | 1992-02-28 | 1993-09-28 | Nec Corp | 半導体記憶装置 |

| US6885210B1 (en) * | 2002-04-16 | 2005-04-26 | Transmeta Corporation | System and method for measuring transistor leakage current with a ring oscillator with backbias controls |

| WO2006090125A2 (en) * | 2005-02-24 | 2006-08-31 | Icera Inc. | Detecting excess current leakage of a cmos device |

| JP2008503883A (ja) * | 2004-06-16 | 2008-02-07 | トランスメータ・コーポレーション | 時間依存性絶縁破壊を測定するためのシステムおよび方法 |

| WO2008129625A1 (ja) * | 2007-04-10 | 2008-10-30 | Fujitsu Microelectronics Limited | リーク電流検出回路、ボディバイアス制御回路、半導体装置及び半導体装置の試験方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5815041A (en) * | 1996-04-12 | 1998-09-29 | Silicon Image, Inc. | High-speed and high-precision phase locked loop having phase detector with dynamic logic structure |

| JPH11101851A (ja) | 1997-09-26 | 1999-04-13 | Toshiba Corp | 遅延時間測定回路及び遅延時間測定方法 |

| JP4067838B2 (ja) * | 2002-02-13 | 2008-03-26 | Necエレクトロニクス株式会社 | 位相比較器 |

| KR100806131B1 (ko) * | 2006-05-23 | 2008-02-22 | 삼성전자주식회사 | 패스트 락킹 위상 고정 루프 |

| JP2008102083A (ja) | 2006-10-20 | 2008-05-01 | Toshiba Corp | 半導体集積回路装置及び制御システム |

| US7423456B2 (en) * | 2006-12-01 | 2008-09-09 | Micron Technology, Inc. | Fast response time, low power phase detector circuits, devices and systems incorporating the same, and associated methods |

-

2008

- 2008-08-12 JP JP2008207680A patent/JP4693880B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-07 US US12/537,447 patent/US7915932B2/en not_active Expired - Fee Related

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05250897A (ja) * | 1992-02-28 | 1993-09-28 | Nec Corp | 半導体記憶装置 |

| US6885210B1 (en) * | 2002-04-16 | 2005-04-26 | Transmeta Corporation | System and method for measuring transistor leakage current with a ring oscillator with backbias controls |

| JP2008503883A (ja) * | 2004-06-16 | 2008-02-07 | トランスメータ・コーポレーション | 時間依存性絶縁破壊を測定するためのシステムおよび方法 |

| WO2006090125A2 (en) * | 2005-02-24 | 2006-08-31 | Icera Inc. | Detecting excess current leakage of a cmos device |

| WO2008129625A1 (ja) * | 2007-04-10 | 2008-10-30 | Fujitsu Microelectronics Limited | リーク電流検出回路、ボディバイアス制御回路、半導体装置及び半導体装置の試験方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9041407B2 (en) | 2011-11-28 | 2015-05-26 | Sony Corporation | Oscillation circuit and test circuit |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100039154A1 (en) | 2010-02-18 |

| US7915932B2 (en) | 2011-03-29 |

| JP4693880B2 (ja) | 2011-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5170086B2 (ja) | リーク電流検出回路、ボディバイアス制御回路、半導体装置及び半導体装置の試験方法 | |

| JP5185304B2 (ja) | 半導体集積回路 | |

| US8766663B2 (en) | Implementing linearly weighted thermal coded I/O driver output stage calibration | |

| JP2007329924A (ja) | デューティ補正付きレベル変換回路 | |

| JP4693880B2 (ja) | 半導体集積回路 | |

| US20070146013A1 (en) | Dynamic logic with adaptive keeper | |

| JP4943729B2 (ja) | 半導体集積回路装置とac特性測定システム | |

| KR101719098B1 (ko) | 펄스 폭 측정을 위한 회로 및 방법 | |

| CN105493405B (zh) | 可重构的延迟电路及使用该延迟电路的延迟监测电路、偏差校正电路、偏差测定方法和偏差校正方法 | |

| JP5190767B2 (ja) | モニタ回路およびリソース制御方法 | |

| KR100987892B1 (ko) | 비교기 회로 | |

| US20160056811A1 (en) | Testable power-on-reset circuit | |

| US9404964B2 (en) | Semiconductor integrated circuit | |

| KR20100134935A (ko) | 멀티플렉싱 기능을 갖는 다이내믹 회로, 이를 포함하는 플립-플롭 회로 및 파이프라인 회로 | |

| US20110279149A1 (en) | Method, apparatus, and system for measuring analog voltages on die | |

| US8049547B2 (en) | Semiconductor integrated circuit and signal adjusting method | |

| KR101388833B1 (ko) | 입력 버퍼 회로 | |

| KR20170031013A (ko) | 플립플롭을 위한 장치 | |

| JP2005064701A (ja) | クロック入出力装置 | |

| JP2008102083A (ja) | 半導体集積回路装置及び制御システム | |

| JP4233579B2 (ja) | クロック入出力装置 | |

| KR20060016656A (ko) | 클럭 펄스 제어 장치 | |

| JP2008008664A (ja) | 集積回路 | |

| KR20080108867A (ko) | 반도체 메모리 장치의 입력 버퍼 회로 | |

| KR20140106404A (ko) | 발진 정지 검출 회로 및 전자 기기 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100729 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110201 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110222 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140304 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |