JP2010016180A - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP2010016180A JP2010016180A JP2008174731A JP2008174731A JP2010016180A JP 2010016180 A JP2010016180 A JP 2010016180A JP 2008174731 A JP2008174731 A JP 2008174731A JP 2008174731 A JP2008174731 A JP 2008174731A JP 2010016180 A JP2010016180 A JP 2010016180A

- Authority

- JP

- Japan

- Prior art keywords

- region

- diffusion region

- semiconductor device

- type

- concentration

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Withdrawn

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 151

- 238000009792 diffusion process Methods 0.000 claims abstract description 105

- 239000012535 impurity Substances 0.000 claims abstract description 73

- 239000000758 substrate Substances 0.000 claims abstract description 41

- 230000015556 catabolic process Effects 0.000 claims description 24

- 238000004519 manufacturing process Methods 0.000 abstract description 4

- 239000010410 layer Substances 0.000 description 19

- 230000007423 decrease Effects 0.000 description 12

- 238000010586 diagram Methods 0.000 description 6

- 239000011229 interlayer Substances 0.000 description 5

- 229910000838 Al alloy Inorganic materials 0.000 description 4

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 4

- 229910052814 silicon oxide Inorganic materials 0.000 description 4

- 238000000926 separation method Methods 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000005380 borophosphosilicate glass Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/08—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/0843—Source or drain regions of field-effect devices

- H01L29/0847—Source or drain regions of field-effect devices of field-effect transistors with insulated gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7833—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's

- H01L29/7835—Field effect transistors with field effect produced by an insulated gate with lightly doped drain or source extension, e.g. LDD MOSFET's; DDD MOSFET's with asymmetrical source and drain regions, e.g. lateral high-voltage MISFETs with drain offset region, extended drain MISFETs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/41—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions

- H01L29/423—Electrodes ; Multistep manufacturing processes therefor characterised by their shape, relative sizes or dispositions not carrying the current to be rectified, amplified or switched

- H01L29/42312—Gate electrodes for field effect devices

- H01L29/42316—Gate electrodes for field effect devices for field-effect transistors

- H01L29/4232—Gate electrodes for field effect devices for field-effect transistors with insulated gate

- H01L29/42384—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor

- H01L2029/42388—Gate electrodes for field effect devices for field-effect transistors with insulated gate for thin film field effect transistors, e.g. characterised by the thickness or the shape of the insulator or the dimensions, the shape or the lay-out of the conductor characterised by the shape of the insulating material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

- H01L29/063—Reduced surface field [RESURF] pn-junction structures

- H01L29/0634—Multiple reduced surface field (multi-RESURF) structures, e.g. double RESURF, charge compensation, cool, superjunction (SJ), 3D-RESURF, composite buffer (CB) structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

Abstract

【課題】スイッチング素子において、製造ばらつきに対して所望のサステイン耐量を確保できる半導体装置を提供する。

【解決手段】半導体装置は、第1導電型の半導体基板100上に形成された第2導電型の第1拡散領域101と、第1拡散領域101上に形成された第2拡散領域108と、半導体基板100上で第2拡散領域108から所定の間隔離れた第2導電型の第3拡散領域103と、半導体基板100上に、第3拡散領域103に隣接し且つ第3拡散領域103と電気的に接続された第1導電型の第4拡散領域106と、第1拡散領域101と第3拡散領域103との間の部分上に、絶縁膜104及びその上のゲート電極105とを備える。第1拡散領域101の不純物濃度は、第2拡散領域108に電圧を印加した際に、第1拡散領域101と半導体基板100との接合面から拡張する空乏層が第1拡散領域101の主たる部分全般に形成される濃度より高い濃度である。

【選択図】図1

【解決手段】半導体装置は、第1導電型の半導体基板100上に形成された第2導電型の第1拡散領域101と、第1拡散領域101上に形成された第2拡散領域108と、半導体基板100上で第2拡散領域108から所定の間隔離れた第2導電型の第3拡散領域103と、半導体基板100上に、第3拡散領域103に隣接し且つ第3拡散領域103と電気的に接続された第1導電型の第4拡散領域106と、第1拡散領域101と第3拡散領域103との間の部分上に、絶縁膜104及びその上のゲート電極105とを備える。第1拡散領域101の不純物濃度は、第2拡散領域108に電圧を印加した際に、第1拡散領域101と半導体基板100との接合面から拡張する空乏層が第1拡散領域101の主たる部分全般に形成される濃度より高い濃度である。

【選択図】図1

Description

本発明は半導体装置に関し、特に、高耐圧半導体スイッチング素子と、その制御回路及び保護回路とが同一の基板上に形成された半導体装置に関する。

電力変換機器、電力制御機器等に用いられる電力用半導体装置において、電流のオン・オフを切り換えるための高耐圧パワートランジスタ等のスイッチング素子と、制御回路及び保護回路とを同一基板上に形成することが行なわれている。これにより、電力用半導体装置の小型・軽量化・高機能化を実現し、オフィス機器、家電製品等の各種電子機器のスイッチング電源分野に広く用いられている。制御回路及び保護回路は、トランジスタ素子等の能動素子と、抵抗素子及び容量素子等とから構成される。

このような電力用半導体装置については、電力損失を極力減少させるため、オン時における電圧降下の少ないことが要望されている。特に高耐圧が要求される分野の場合、RESURF(REduced SURface Field)構造を利用したトランジスタ等が適している。

以下、従来例として、特許文献1に示すRESURF構造を利用したMOSFET(Metal Oxide Semiconductor Field Effect Transistor )の構成及び動作を説明する。

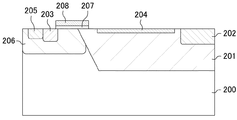

図10は、半導体基板上に形成されたRESURFMOSFETの断面構成を示している。

図10に示すように、半導体装置210は、第1導電型のシリコン(Si)からなる半導体基板200を用いて形成されている。

半導体基板200上には第2導電型の延長ドレイン領域201が形成され、該延長ドレイン領域201の表面部には、第2導電型のドレイン領域202が形成されている。

また、半導体基板200の表面部において、ドレイン領域202との間に延長ドレイン領域201を介在させると共に、ドレイン領域202から所定の間隔を開けて、第2導電型のソース領域203が形成されている。

ドレイン領域202と、ソース領域203との間に位置する部分の延長ドレイン領域201内において、その表面部に、半導体基板200と電気的に接続された第1導電型の埋め込み領域204が形成されている。

また、半導体基板200の表面部に、ソース領域203に対して隣接し且つ電気的に接続された第1導電型のコンタクト領域205が形成されている。更に、半導体基板200の表面部に、ソース領域203及びコンタクト領域205を囲むと共に、延長ドレイン領域201と隣接する第1導電型のウェル領域206が形成されている。

また、延長ドレイン領域201とソース領域203との間の部分のウェル領域206上に、シリコン酸化膜からなる絶縁膜207が形成され、更にその上に、ポリシリコンからなるゲート電極208が形成されている。

以上のように構成された半導体装置210において、ドレイン領域202とソース領域203との間に電圧を印加した状態とし、また、ゲート電極208とソース領域203との間に、ゲート電極208が高電位となるように規定電圧以上の電圧を印加する。このようにすると、ウェル領域206におけるゲート電極208の直下の領域に強反転状態のチャネルが形成され、該チャネルを通じてドレイン領域202とソース領域203との間に電流が流れる。以下、このように電流が流れる状態をオン状態と呼ぶ。

また、半導体装置210において、ゲート電極208とソース領域203との間に印加する電圧を前記の規定電圧よりも低くすると、チャネルが消失し、ウェル領域206と延長ドレイン領域201との間に逆バイアス電圧が印加される。この結果、ウェル領域206と延長ドレイン領域201との間にpn接合が形成され、ドレイン領域202とソース領域203との間に電流は流れない。以下、このように電流が流れない状態をオフ状態と呼ぶ。

ここで、図10に示す半導体装置210の場合、ソース領域203とドレイン領域202との間に位置する部分の延長ドレイン領域201内に埋め込み領域204が形成されている。このため、ドレイン領域202とソース領域203との間に高電圧が印加された場合、延長ドレイン領域201と半導体基板200との接合面に空乏層が形成されるのに加え、埋め込み領域204と延長ドレイン領域201との接合面からも同時に空乏層が形成される。

従って、図10に示す構造を用いると、埋め込み領域204を設けない構造に比べ、延長ドレイン領域201の不純物濃度を高くした場合にも延長ドレイン領域201における空乏層を維持することができる。このような空乏層により、ドレイン領域202とソース領域203との間の電位差を負担することができる。

このように、図10に示すRESURFMOSFET構造の半導体基板200は、高耐圧を維持しながら、延長ドレイン領域201の不純物濃度を高めることによりドレイン領域202とソース領域203との間の電気抵抗(オン抵抗)を低減することができる。

特許2529717号

しかしながら、図10に示す従来の半導体装置210において、サステイン耐量が大幅に低いものが発生することがある。よって、これを解決することが課題となっている。

このような課題に鑑みて、本発明は、電力用半導体装置において、所望の耐圧とサステイン耐量とを共に確保できる半導体装置を提供することを目的とする。

前記の目的を達成するため、本願発明者等はサステイン耐量が低下する原因について検討した。

まず、図11に、本願発明者等の調査による埋め込み領域204を含むドレイン領域202の電気伝導率と耐圧との関係(実線)、及び、該電気伝導率と半導体装置210のサステイン耐量との関係(破線)を示す。サステイン耐量とは、半導体装置210において、オン状態とオフ状態との切り替え時に発生するサージ電圧に対する耐量のことである。

また、ここで言う電気伝導率とは、下記の関係式により定義されるものであり、延長ドレイン領域201の不純物濃度と、埋め込み領域204の不純物濃度との比率を示す指標である。

電気伝導率σ=1×103 ×(1/RSed - 3/RSb) [μS(マイクロジーメンス)]

RSed:埋め込み領域204を含む延長ドレイン領域201のシート抵抗

RSb :埋め込み領域204のシート抵抗

図11に示すように、従来例に示す半導体装置210の耐圧は、延長ドレイン領域201の電気伝導率に依存している。また、該耐圧は、ある所定の値の電気伝導率に対して最大となり、それを外れると低下する。

RSed:埋め込み領域204を含む延長ドレイン領域201のシート抵抗

RSb :埋め込み領域204のシート抵抗

図11に示すように、従来例に示す半導体装置210の耐圧は、延長ドレイン領域201の電気伝導率に依存している。また、該耐圧は、ある所定の値の電気伝導率に対して最大となり、それを外れると低下する。

ここで、電気伝導率は、先に示した通り延長ドレイン領域201及び埋め込み領域204のシート抵抗によって定義される指標である。

従って、図11に示す電気伝導率と耐圧との関係は、延長ドレイン領域201及び埋め込み領域204の不純物濃度が所定の値から外れると耐圧が低下することを示す。このため、従来例である半導体装置201の場合、延長ドレイン領域201及び埋め込み領域204の不純物濃度は、半導体装置210の耐圧が最大になるように調整されている。

これに対し、電気伝導率に対するサステイン耐量の関係を本願発明者等が詳細に調査したところ、耐圧が最大となる前記所定の電気伝導率を境界として、これよりも電気伝導率が低くなると、半導体装置210のサステイン耐量は大幅に低下することがわかった。これは、図11にも示されている。

このことは、延長ドレイン領域201又は埋め込み領域204のシート抵抗がばらついた場合、つまり、延長ドレイン領域201又は埋め込み領域204の不純物濃度がばらついた場合に、サステイン耐量が大幅に低下するおそれがあることを示している。

以上の知見に基づき、本発明に係る半導体装置は、第1導電型の半導体基板の上に形成された第2導電型の第1拡散領域と、第1拡散領域の表面部に形成された第2拡散領域と、半導体基板の表面部において、第2拡散領域との間に第1拡散領域が介在するように、第2拡散領域から所定の間隔だけ離れた位置に形成された第2導電型の第3拡散領域と、半導体基板の表面部において、第3拡散領域に隣接して形成され且つ第3拡散領域と電気的に接続された第1導電型の第4拡散領域と、第1拡散領域と第3拡散領域との間の部分の上に、絶縁膜を介して形成されたゲート電極とを備え、第1拡散領域の不純物濃度は、所定の濃度に設定されており、所定の濃度は、第2拡散領域に電圧を印加した際に、第1拡散領域と半導体基板との接合面から拡張する空乏層が第1拡散領域の主たる部分全般に形成される濃度よりも高い濃度である。

本発明に係る半導体装置によると、以下に説明する通り、高耐圧を維持すると共に、第1拡散領域における不純物濃度のばらつきに起因するサステイン耐量の低下を抑制することができる。

従来、第1拡散領域の不純物濃度は、第1拡散領域と半導体基板との接合面から拡張する空乏層が第1拡散領域の主たる部分全般に形成される濃度として規定されていた。これは、半導体装置がオフである状態において第2拡散領域に所定の電圧を印加したとき、第1拡散領域内が空乏化されることにより第1拡散領域内の電子及び正孔が除かれ、半導体装置の耐圧が最大になるように設定される濃度である。しかし、このような従来の濃度に設定されている場合、本願発明者らによる新たな知見として図11に示す通り、濃度のばらつきが生じるとサステイン耐量が大きく低下することがある。

これに対し、本発明の半導体装置の場合、第1拡散領域の不純物濃度を従来よりも高い濃度に設定している。これにより、第1拡散領域の不純物濃度にばらつきが生じたとしても、サステイン耐量の不純物濃度に対する依存性が比較的小さい範囲に不純物濃度を維持することができ、サステイン耐量の大幅な低下を防ぐことができる。

尚、所定の濃度は、半導体装置の耐圧が最大になる濃度よりも高い濃度であることが好ましい。

前記の通り、半導体装置の耐圧が最大になる濃度付近では、濃度のばらつきによりサステイン耐量が大幅に低下することがある。よって、このような濃度よりも高い濃度範囲に第1拡散領域の不純物濃度を設定するのがよい。

また、所定の濃度は、第1拡散領域の不純物濃度の変化に対する半導体装置のサステイン耐量の変化量が小さくなる濃度よりも高い濃度であることが好ましい。

前記の通り、本願発明者等は、第1拡散領域の不純物濃度として従来設定されていた濃度の付近において、不純物濃度の変化に対するサステイン耐量の変化が相対的に大きい領域と、それに比べてサステイン耐量の変化量が小さい領域とが存在することを見出した。そこで、そのような2つの領域の境界となる不純物濃度よりも高い濃度範囲に第1拡散領域の不純物濃度を設定する。これにより、不純物濃度の低下によるサステイン耐量の大幅な低下を抑制することができる。

以上のような本発明の半導体装置は、RESURF構造を利用した半導体装置全般に利用することができる。その例として、以下にはMOSトランジスタ及び絶縁ゲートバイポーラトランジスタ(IGBT)を挙げる。

つまり、本発明の半導体装置において、第1拡散領域を延長ドレイン領域とし、第2拡散領域を第2導電型のドレイン領域とし、第3拡散領域をソース領域とし、第4拡散領域をコンタクト領域とするMOSトランジスタが構成されていることが好ましい。

このようなMOSトランジスタは、延長ドレイン領域の不純物濃度を従来規定されていた濃度よりも高く設定されている。これにより、サステイン耐量に関して、延長ドレイン領域における不純物濃度のばらつきの許容範囲が大きくなっている。つまり、MOSトランジスタを備える半導体装置において、高耐圧を維持しながらサステイン耐量についても確保することができる。

また、本発明の半導体装置において、第1拡散領域をベース領域とし、第2拡散領域を第1導電型のコレクタ領域とし、第3拡散領域をエミッタ領域とし、第4拡散領域をコンタクト領域とする絶縁ゲートバイポーラトランジスタが構成されていることが好ましい。

このようなIGBTは、ベース領域の不純物濃度を従来規定されていた濃度よりも高く設定されている。これにより、サステイン耐量に関して、ベース領域における不純物濃度のばらつきの許容範囲が大きくなっている。つまり、IGBTを備える半導体装置において、高耐圧を維持しながらサステイン耐量についても確保することができる。

また、本発明の半導体装置において、第1拡散領域をベース/延長ドレイン領域とし、第2拡散領域を第1導電型のコレクタ領域と第2導電型のドレイン領域とからなるコレクタ/ドレイン領域とし、第3拡散領域をエミッタ/ソース領域とし、第4拡散領域をコンタクト領域として、MOSトランジスタと絶縁ゲートバイポーラトランジスタとが共に構成されていることが好ましい。

このように、第2拡散領域の構造を、第1導電型の領域と第2導電型の領域とを有し且つ互いに電気的に接続されている構造とすることにより、前記のMOSトランジスタと前記のIGBTとを一つの半導体装置に共存させることができる。

本発明の技術分野である高耐圧半導体スイッチング素子において、一般に、動作時に生じる電力損失の軽減が求められる。これに関し、MOSトランジスタを用いる場合、MOSトランジスタは動作時の電気抵抗が大きいことから、IGBTを用いる場合に比べてオン状態における電力損失が大きくなってしまう。また、IGBTを用いる場合、MOSトランジスタを用いる場合に比べてオン状態とオフ状態とを切り替える際の電力損失が大きくなってしまう。

以上に対し、MOSトランジスタとIGBTとを一つの半導体装置に混載させた構造とすると、通常の動作時には電気抵抗の低いIGBTを利用し、また、オン状態とオフ状態との切り替えの際には、このような切り替え時の電気損失に関して有利なMOSトランジスタを利用することができる。このため、MOSトランジスタ又はIGBTのいずれか一方のみを有する構造に比べて、これらの両方を共存させた構造とすることにより、電力損失を低減することができる。

また、第1拡散領域の電気伝導率が、180μS以上で且つ210μS以下であることが好ましい。

第1拡散領域の電気伝導率は第1拡散領域の不純物濃度に依存する。本発明の半導体装置における第1拡散領域の電気伝導率がこのような範囲の値となる不純物濃度に設定すると、不純物濃度のばらつきによるサステイン耐量の大幅な低下を抑制し、且つ、従来よりも不純物濃度を高くしたことによる体圧の低下を最小限に抑制することができる。

また、第1拡散領域内に、少なくとも一つの第1導電型の埋め込み領域が配置されていることが好ましい。

このようにすると、第1拡散領域と半導体基板との接合面に加えて、第1拡散領域と埋め込み領域との接合面からも空乏層が拡張する。このため、第1拡散領域の不純物濃度を高くしても、第1拡散領域の空乏化を確実に行なうことができる。特に、第1拡散領域の主たる部分全般の空乏化を行なうことができる。このため、高耐圧を意地死活動作時の電気抵抗を低減することができる。

また、埋込領域は、半導体基板の深さ方向に互いに間隔をおいて複数配置されていることが好ましい。

このようにすると、埋め込み層を設けることによる前記の効果をより顕著に得ることができる。

また、埋込領域を含む前記第1拡散領域の電気伝導率が、180μS以上で且つ210μS以下であることが好ましい。

埋め込み層のシート抵抗と第1拡散領域のシート抵抗とに応じて決まる電気伝導率について、このような範囲となっていると、不純物濃度のばらつきによるサステイン耐量の大幅な低下を抑制し、且つ、従来よりも不純物濃度を高くしたことによる体圧の低下を抑制することができる。

本発明の半導体装置によると、第1拡散領域の不純物濃度を第1拡散領域と半導体基板との接合面から拡張する空乏層が第1拡散領域の主たる部分全般に形成されるように規定される濃度、つまり、半導体装置の耐圧が最大になるように設定される濃度よりも濃く設定することにより、第1拡散領域の不純物濃度が製造上ばらついても、所望のサステイン耐量を確保することができる。

(第1の実施形態)

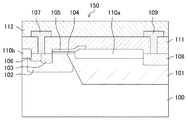

以下に、第1の実施形態に係る半導体装置について、図面を参照して説明する。図1は、本発明に係る半導体装置150、より具体的には半導体基板上に形成されたRESURFMOSFET構造の断面を模式的に示す図である。

以下に、第1の実施形態に係る半導体装置について、図面を参照して説明する。図1は、本発明に係る半導体装置150、より具体的には半導体基板上に形成されたRESURFMOSFET構造の断面を模式的に示す図である。

図1に示すように、本実施形態の半導体装置150は、不純物濃度が1×1014cm-3から1×1017cm-3程度のP型シリコン(Si)からなる半導体基板100を用いて形成されている。

半導体基板100の表面部に、N型延長ドレイン領域101と、不純物濃度が1×1016cm-3から1×1017cm-3程度であるP型ウェル領域102とが形成されている。

P型ウェル領域102の表面部の一部には、高不純物濃度のN型ソース領域103が形成されている。N型延長ドレイン領域101とN型ソース領域103とに挟まれた部分のP型ウェル領域102の表面上には、酸化シリコン(SiO2 )からなるゲート酸化膜104を介してポリシリコンからなるゲート電極105が形成されている。

P型ウェル領域102の表面部には、P型ウェル領域102よりも不純物濃度が高い高不純物濃度のP型コンタクト領域106が形成されている。P型コンタクト領域106及びN型ソース領域103の表面部には、AlSiCu等のアルミニウム合金からなるソース電極107が形成されている。ソース電極107は、P型コンタクト領域106及びN型ソース領域103に対して電気的に共通に接続されている。

また、N型延長ドレイン領域101の表面部には、N型延長ドレイン領域101よりも不純物濃度が高い高不純物濃度のN型ドレイン領域108が形成されている。N型ドレイン領域108は、ゲート電極105を挟んでN型ソース領域103とは反対側に位置する。更に、N型ドレイン領域108上には、AlSiCu等のアルミニウム合金からなるドレイン電極109が形成され、N型ドレイン領域108と電気的に接続されている。

更に、N型延長ドレイン領域101及びP型ウェル領域102の表面部には、半導体基板100上に形成されたトランジスタを分離するための酸化シリコンからなる分離層110a及び110b(これらを合わせて分離層110と呼ぶ場合がある)が形成されている。

N型ソース領域103、ゲート電極105、P型コンタクト領域106、分離層110等を覆うように、酸化シリコンとBPSGとの積層構造を有する層間絶縁膜111が形成されている。該層間絶縁膜111により、ゲート電極105、ソース電極107、ドレイン電極109は互いに電気的に分離されている。ゲート電極105及びソース電極107は、層間絶縁膜111を貫通している。

層間絶縁膜111上には、ゲート電極105とソース電極107を覆うように、窒化シリコン(SiN)からなる保護膜112が形成されている。

ここで、図10に示すような従来のRESURF構造を有するMOSトランジスタの場合、延長ドレイン領域201の不純物濃度は、延長ドレイン領域201と半導体基板200との接合面から拡張する空乏層が、延長ドレイン領域201の主たる部分全般に形成される濃度として規定されていた。このような濃度とした場合に、半導体装置の耐圧が最大となるためである。

これに対し、本実施形態の半導体装置150の場合、N型延長ドレイン領域101の不純物濃度は、半導体装置の耐圧が最大となる前記の不純物濃度よりも高い濃度に設定している。具体的には、本実施形態の場合、N型延長ドレイン領域101の不純物濃度は0.5〜1.0×1016cm-3程度に設定されている。尚、従来の半導体装置の場合、延長ドレイン領域の不純物濃度は例えば0.2〜0.4×1016cm-3の範囲としていた。

図2及び図3に、半導体装置150のN型延長ドレイン領域101における電気伝導率とサステイン耐量の関係及び電気伝導率と耐圧との関係を順に示す。尚、従来技術においても説明した通り、電気伝導率はN型延長ドレイン領域101のシート抵抗により決定される値であり、N型延長ドレイン領域101における不純物濃度を示す指標となる。

また、図2及び3に示す実線の領域は、本実施形態におけるN型延長ドレイン領域101の不純物濃度に対応する電気伝導率の範囲を示す。ここでは、180μS以上で且つ210μS以下の範囲である。これに対し、破線の範囲は、従来使用されてきた不純物濃度に対応する電気伝導率の範囲を示している。

図2に示す通り、従来の濃度範囲とした場合、製造上のばらつき等によってN型延長ドレイン領域101の電気伝導率が変動すると、サステイン耐量が大幅に低下することがある。つまり、従来の濃度範囲において、サステイン耐量は変動が大きい。

これに対し、本実施形態にて設定している濃度範囲の場合、N型延長ドレイン領域101における不純物濃度がばらつき、電気伝導率が変動したとしても、サステイン耐量が大幅に低下することはない。これは、所定の値を境界として、不純物濃度の変化に対するサステイン耐量の変化が相対的に大きい領域と、それに比べてサステイン耐量の変化量が小さい領域とが存在する点に着目し、サステイン耐量の変化量が比較的小さい範囲に濃度範囲を設定しているからである。この結果、不純物濃度のばらつきに関わらず、高耐圧を維持し且つ所望のサステイン耐量を確保することが可能になる。

更に、図3に示す通り、N型延長ドレイン領域101の不純物濃度を前記の範囲の値とすることにより、N型延長ドレイン領域101の不純物濃度を高めたことによる耐圧低下を最小限に抑えることができる。

以上のように、本実施形態の半導体装置150によると、N型延長ドレイン領域101の不純物濃度にばらつきが生じたとしても、高耐圧を維持し、且つ、所望のサステイン容量を確保することができる。

(第2の実施形態)

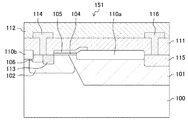

以下、本発明の第2の実施形態に係る半導体装置について、図面を参照しながら説明する。図4は、本発明の第2の実施形態に係る半導体装置151の断面構成を模式的に示す図である。半導体装置151は、半導体基板上に形成された横型構造のIGBTである。

以下、本発明の第2の実施形態に係る半導体装置について、図面を参照しながら説明する。図4は、本発明の第2の実施形態に係る半導体装置151の断面構成を模式的に示す図である。半導体装置151は、半導体基板上に形成された横型構造のIGBTである。

図4に示す通り、半導体装置151は、図1の半導体装置150と類似した構造を有する。よって、以下には相違点を詳しく説明し、同じ構成要素には図1と同じ符号を付すことにより詳しい説明を省略する。

まず、図4において、N型延長ドレイン領域101の表面部には、図1におけるN型ドレイン領域108に変えて、N型延長ドレイン領域101よりも不純物濃度が高い高不純物濃度のP型コレクタ領域115が形成されている。P型コレクタ領域115上には、図1におけるドレイン電極109に代えて、AlSiCu等のアルミニウム合金からなるコレクタ電極116が形成されている。

また、図1におけるN型ソース領域103及びソース電極107に対し、これらと同じ構成部材を、図4の半導体装置151においては、順にエミッタ領域113及びエミッタ電極114と呼ぶ。つまり、名称だけが異なる。

半導体装置151の場合、オン状態において、エミッタ領域113からN型延長ドレイン領域101に向かって電子電流が流れ、該電流がP型コンタクト領域106、N型延長ドレイン領域101及びP型コレクタ領域115により構成されるpnpトランジスタのベース電流となる。ベース電流が流れると、P型コレクタ領域115からN型延長ドレイン領域101に対し、大量の正孔が注入される。この結果、電荷中性条件を満足するために、電子もエミッタ領域113からN型延長ドレイン領域101内に注入される。よって、N型延長ドレイン領域101内における電子濃度及び正孔濃度は共に増加し、P型コレクタ領域115とエミッタ領域113との間のオン抵抗は大幅に低下する。

N型延長ドレイン領域101の不純物濃度を従来よりも高い濃度範囲に設定することにより、サステイン容量の低下を避けるという点については、第1の実施形態の場合と同様である。

以上のようにして、横型構造のIGBTである本実施形態の半導体装置151においても、高耐圧且つ所望のサステイン容量を確保することができると共に、第1の実施形態に係る半導体装置150に比べてオン抵抗を更に低減することができる。

(第3の実施形態)

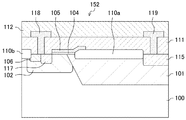

以下、本発明の第3の実施形態に係る半導体装置について、図面を参照しながら説明する。図5〜図7は、本実施形態における半導体装置152の構造を示す図である。半導体装置152は、同一の半導体基板上に、図6に模式的な断面を示す横型構造のMOSトランジスタと、図7に模式的な断面を示す横型構造のIGBTとを、図5に示す平面図のように交互に並べて共存させた構造を有する。尚、図5におけるVI-VI'線による断面が図6に、VII-VII'線による断面が図7に示されている。

以下、本発明の第3の実施形態に係る半導体装置について、図面を参照しながら説明する。図5〜図7は、本実施形態における半導体装置152の構造を示す図である。半導体装置152は、同一の半導体基板上に、図6に模式的な断面を示す横型構造のMOSトランジスタと、図7に模式的な断面を示す横型構造のIGBTとを、図5に示す平面図のように交互に並べて共存させた構造を有する。尚、図5におけるVI-VI'線による断面が図6に、VII-VII'線による断面が図7に示されている。

ここで、図6に示すMOSトランジスタの構造は、図1に示す第1の実施形態の半導体装置150の構造と同様であり、図7に示すIGBTの構造は、図4に示す第2の実施形態の半導体装置151の構造と同様である。

但し、図1におけるN型ソース領域103及び図4におけるエミッタ領域113について、本実施形態では、交互に並ぶMOSトランジスタ及びIGBTに亘って形成されたエミッタ/ソース領域117となっている。エミッタ/ソース領域117及びP型コンタクト領域106上に共通して接続された電極として、ソース電極107及びエミッタ電極114に代えて、エミッタ/ソース電極118が設けられている。

また、N型延長ドレイン領域101よりも不純物濃度が高い高不純物濃度のN型ドレイン領域108と、P型コレクタ領域115とについては、それぞれ図1と図4とに示すものと同様である。但し、図5に示す通り、本実施形態の半導体装置152においてN型ドレイン領域108とP型コレクタ領域115とは半導体基板100の主面方向に交互に並んで配置されており、これらを互いに電気的に接続させるようにコレクタ/ドレイン電極119が形成されている。該コレクタ/ドレイン電極119は、AlSiCu等のアルミニウム合金からなる。

以上に述べた以外の構成要素については、図5〜図7において、図1及び4と同じ符号を付すことにより詳しい説明を省略する。

図5〜図7に示す通り、本実施形態の半導体装置152では、N型延長ドレイン領域101の表面部に、N型ドレイン領域108とP型コレクタ領域115とがコレクタ/ドレイン電極119によって電気的に接続された状態に形成されている。このようにして、RESURF構造を有するMOSトランジスタとIGBTとの2つのトランジスタが電気的に並列接続された状態に搭載されている。

このため、半導体装置152は、通常のオン状態においては導通時電力損失に関して有利なIGBTを利用すると共に、オン状態とオフ状態との切り替えの際には、切り替え時の電力損失に関して有利なMOSトランジスタを選択的に利用することができる。

従って、本実施形態の半導体装置152を用いると、第1の実施形態の半導体装置150及び第2の実施形態の半導体装置151のいずれに比べても、電力損失を低減することができる。

また、N型延長ドレイン領域101の不純物濃度を従来よりも高い濃度範囲に設定することにより、サステイン容量の低下を避けるという点については、第1の実施形態の場合と同様である。

(第4の実施形態)

以下、本発明の第4の実施形態に係る半導体装置について、図面を参照しながら説明する。図8は、本実施形態の半導体装置153の断面構造を模式的に示す図である。

以下、本発明の第4の実施形態に係る半導体装置について、図面を参照しながら説明する。図8は、本実施形態の半導体装置153の断面構造を模式的に示す図である。

図8に示す半導体装置153は、図1に示す第1の実施形態の半導体装置150に対し、N型延長ドレイン領域101の表面部に形成されたP型埋め込み領域120を追加した構造である。P型埋め込み領域120は、厚さが1.0μm程度であり且つ不純物濃度が1×1016cm-3から1×1017cm-3程度である。更に、P型埋め込み領域120は、半導体基板100と電気的に接続されており、基板面に対してほぼ並行に延びるように形成されている。

他の構成要素については、図1に示すものと同様であるから、同じ符号を用いることにより、詳しい説明を省略する。更に、

N型延長ドレイン領域101の表面部にP型埋め込み領域120を備えることにより、図8の半導体装置153によると、オフ状態においてドレイン電極109とソース電極107との間に高電圧が加えられた場合、N型延長ドレイン領域101と半導体基板100との接合面に加え、N型延長ドレイン領域101とP型埋め込み領域120との接合面からも空乏層が拡張する。このため、N型延長ドレイン領域101の不純物濃度を高くしてもN型延長ドレイン領域101の全体を空乏化させることができ、ドレイン電極109とソース電極107との間の電位差を前記の空乏層により負担することができる。

N型延長ドレイン領域101の表面部にP型埋め込み領域120を備えることにより、図8の半導体装置153によると、オフ状態においてドレイン電極109とソース電極107との間に高電圧が加えられた場合、N型延長ドレイン領域101と半導体基板100との接合面に加え、N型延長ドレイン領域101とP型埋め込み領域120との接合面からも空乏層が拡張する。このため、N型延長ドレイン領域101の不純物濃度を高くしてもN型延長ドレイン領域101の全体を空乏化させることができ、ドレイン電極109とソース電極107との間の電位差を前記の空乏層により負担することができる。

従って、本実施形態の半導体装置153は、第1の実施形態の半導体装置150に比べてN型延長ドレイン領域101の不純物濃度を高めることができ、これにより動作時の電気抵抗を低減することができる。

尚、本実施形態の変形例として、図9に示すように、N型延長ドレイン領域101の表面部に代えて、表面から所定の深さの位置にP型埋め込み領域120を形成することもできる。このようにすると、N型延長ドレイン領域101とP型埋め込み領域120との接合面の面積が増加する。このため、オフ状態においてドレイン電極109とソース電極107との間に高電圧が加えられた場合に、前記接合面からの空乏層がより拡張されやすくなる。この結果として、図9に示す半導体装置153aは、図8に示す半導体装置153に比べて更にN型延長ドレイン領域101の不純物濃度を高くすることができ、より電気抵抗を低減することができる。

更に、N型延長ドレイン領域101内に、半導体基板100と電気的に接続されたP型埋め込み領域120を、互いに所定の間隔をおいて複数形成しても良い。このようにすると、更にN型延長ドレイン領域101の不純物濃度を高くすることができ、電気抵抗を更に低減することができる。

また、本実施形態において、例えばP型埋め込み領域120の不純物濃度が3.0×1016cm-3である場合、N型延長ドレイン領域101の不純物濃度は、2.0×1016cm-3以上で且つ2.1×1016cm-3以下であることが好ましい。このようにすると、N型延長ドレイン領域101の電気伝導率を180μSから210μSの範囲に設定することができる。尚、従来の同様の構造の半導体装置の場合には、N型延長ドレイン領域の不純物濃度を2.3〜2.5×1016cm-3の範囲としていた。

従って、図2及び図3に示すように、N型延長ドレイン領域101の不純物濃度を所定の濃度よりも高くしたことによる半導体装置の耐圧低下を最小限に抑えることができる。

また、本実施形態においては、第1の実施形態に係る半導体装置150に対してP型埋め込み領域120を追加した場合を説明した。しかし、第2の実施形態の半導体装置151等についても、N型延長ドレイン領域101内にP型埋め込み領域120を形成することにより同様の効果を実現することができる。

本発明の半導体装置は、製造時におけるばらつきに対する許容範囲を広げ、高耐圧半導体スイッチング素子の高耐圧を維持しつつ、所望のサステイン耐量を確保することができるため、スイッチング電源装置等に有用である。

100 半導体基板

101 延長ドレイン領域

102 P型ウェル領域

103 N型ソース領域

104 ゲート酸化膜

105 ゲート電極

106 P型コンタクト領域

107 ソース電極

108 N型ドレイン領域

109 ドレイン電極

110 分離層

110a 分離層

111 層間絶縁膜

112 保護膜

113 エミッタ領域

114 エミッタ電極

115 P型コレクタ領域

116 コレクタ電極

117 エミッタ/ソース領域

118 エミッタ/ソース電極

119 コレクタ/ドレイン電極

120 P型埋め込み領域

150 半導体装置

151 半導体装置

152 半導体装置

153 半導体装置

153a 半導体装置

101 延長ドレイン領域

102 P型ウェル領域

103 N型ソース領域

104 ゲート酸化膜

105 ゲート電極

106 P型コンタクト領域

107 ソース電極

108 N型ドレイン領域

109 ドレイン電極

110 分離層

110a 分離層

111 層間絶縁膜

112 保護膜

113 エミッタ領域

114 エミッタ電極

115 P型コレクタ領域

116 コレクタ電極

117 エミッタ/ソース領域

118 エミッタ/ソース電極

119 コレクタ/ドレイン電極

120 P型埋め込み領域

150 半導体装置

151 半導体装置

152 半導体装置

153 半導体装置

153a 半導体装置

Claims (10)

- 第1導電型の半導体基板の上に形成された第2導電型の第1拡散領域と、

前記第1拡散領域の表面部に形成された第2拡散領域と、

前記半導体基板の表面部において、前記第2拡散領域との間に前記第1拡散領域が介在するように、前記第2拡散領域から所定の間隔だけ離れた位置に形成された第2導電型の第3拡散領域と、

前記半導体基板の表面部において、前記第3拡散領域に隣接して形成され且つ前記第3拡散領域と電気的に接続された第1導電型の第4拡散領域と、

前記第1拡散領域と前記第3拡散領域との間の部分の上に、絶縁膜を介して形成されたゲート電極とを備え、

前記第1拡散領域の不純物濃度は、所定の濃度に設定されており、

前記所定の濃度は、前記第2拡散領域に電圧を印加した際に、前記第1拡散領域と前記半導体基板との接合面から拡張する空乏層が前記第1拡散領域の主たる部分全般に形成される濃度よりも高い濃度であることを特徴とする半導体装置。 - 請求項1において、

前記所定の濃度は、前記半導体装置の耐圧が最大になる濃度よりも高い濃度であることを特徴とする半導体装置。 - 請求項1において、

前記所定の濃度は、前記第1拡散領域の不純物濃度の変化に対する前記半導体装置のサステイン耐量の変化量が小さくなる濃度よりも高い濃度であることを特徴とする半導体装置。 - 請求項1〜3のいずれか一つにおいて、

前記第1拡散領域を延長ドレイン領域とし、

前記第2拡散領域を第2導電型のドレイン領域とし、

前記第3拡散領域をソース領域とし、

前記第4拡散領域をコンタクト領域とするMOSトランジスタが構成されていることを特徴とする半導体装置。 - 請求項1〜3のいずれか一つにおいて、

前記第1拡散領域をベース領域とし、

前記第2拡散領域を第1導電型のコレクタ領域とし、

前記第3拡散領域をエミッタ領域とし、

前記第4拡散領域をコンタクト領域とする絶縁ゲートバイポーラトランジスタが構成されていることを特徴とする半導体装置。 - 請求項1〜3のいずれか一つにおいて、

前記第1拡散領域をベース/延長ドレイン領域とし、

前記第2拡散領域を第1導電型のコレクタ領域と第2導電型のドレイン領域とからなるコレクタ/ドレイン領域とし、

前記第3拡散領域をエミッタ/ソース領域とし、

前記第4拡散領域をコンタクト領域として、MOSトランジスタと絶縁ゲートバイポーラトランジスタとが共に構成されていることを特徴とする半導体装置。 - 請求項1〜6のいずれか一つにおいて、

前記第1拡散領域の電気伝導率が、180μS以上で且つ210μS以下であることを特徴とする半導体装置。 - 請求項1〜7のいずれか一つにおいて、

前記第1拡散領域内に、少なくとも一つの第1導電型の埋め込み領域が配置されていることを特徴とする半導体装置。 - 請求項8において、

前記埋込領域は、前記半導体基板の深さ方向に互いに間隔をおいて複数配置されていることを特徴とする半導体装置。 - 請求項8又は9において、

前記埋込領域を含む前記第1拡散領域の電気伝導率が、180μS以上で且つ210μS以下であることを特徴とする半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008174731A JP2010016180A (ja) | 2008-07-03 | 2008-07-03 | 半導体装置 |

| PCT/JP2009/001759 WO2010001513A1 (ja) | 2008-07-03 | 2009-04-16 | 半導体装置 |

| US12/473,604 US20100001315A1 (en) | 2008-07-03 | 2009-05-28 | Semiconductor device |

| TW098121446A TW201003896A (en) | 2008-07-03 | 2009-06-25 | Semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008174731A JP2010016180A (ja) | 2008-07-03 | 2008-07-03 | 半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010016180A true JP2010016180A (ja) | 2010-01-21 |

| JP2010016180A5 JP2010016180A5 (ja) | 2010-07-29 |

Family

ID=41463690

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008174731A Withdrawn JP2010016180A (ja) | 2008-07-03 | 2008-07-03 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20100001315A1 (ja) |

| JP (1) | JP2010016180A (ja) |

| TW (1) | TW201003896A (ja) |

| WO (1) | WO2010001513A1 (ja) |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6277785B2 (ja) * | 2014-03-07 | 2018-02-14 | 富士電機株式会社 | 半導体装置 |

| JP2019075536A (ja) * | 2017-10-11 | 2019-05-16 | 株式会社村田製作所 | パワーアンプモジュール |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| SE453622B (sv) * | 1983-12-08 | 1988-02-15 | Asea Ab | Halvledarkomponent for generering av optisk stralning |

| US4811075A (en) * | 1987-04-24 | 1989-03-07 | Power Integrations, Inc. | High voltage MOS transistors |

| JP3395473B2 (ja) * | 1994-10-25 | 2003-04-14 | 富士電機株式会社 | 横型トレンチmisfetおよびその製造方法 |

| JPH08236754A (ja) * | 1995-02-22 | 1996-09-13 | Fuji Electric Co Ltd | pチャネル型高耐圧MOSFET |

| US6168983B1 (en) * | 1996-11-05 | 2001-01-02 | Power Integrations, Inc. | Method of making a high-voltage transistor with multiple lateral conduction layers |

| JP4815740B2 (ja) * | 2003-12-09 | 2011-11-16 | トヨタ自動車株式会社 | 半導体装置とそれを利用したレベルシフト回路 |

| JP3888997B2 (ja) * | 2003-12-12 | 2007-03-07 | 松下電器産業株式会社 | 半導体装置 |

| JP4972855B2 (ja) * | 2004-08-04 | 2012-07-11 | 富士電機株式会社 | 半導体装置およびその製造方法 |

| US7262476B2 (en) * | 2004-11-30 | 2007-08-28 | Agere Systems Inc. | Semiconductor device having improved power density |

| JP2006210563A (ja) * | 2005-01-27 | 2006-08-10 | Matsushita Electric Ind Co Ltd | 半導体装置 |

| US7759696B2 (en) * | 2005-10-20 | 2010-07-20 | Panasonic Corporation | High-breakdown voltage semiconductor switching device and switched mode power supply apparatus using the same |

| JP2007318062A (ja) * | 2006-04-27 | 2007-12-06 | Matsushita Electric Ind Co Ltd | 高耐圧半導体スイッチング素子 |

| JP5148852B2 (ja) * | 2006-09-07 | 2013-02-20 | 新日本無線株式会社 | 半導体装置 |

| JP2008124421A (ja) * | 2006-10-17 | 2008-05-29 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2008153495A (ja) * | 2006-12-19 | 2008-07-03 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

-

2008

- 2008-07-03 JP JP2008174731A patent/JP2010016180A/ja not_active Withdrawn

-

2009

- 2009-04-16 WO PCT/JP2009/001759 patent/WO2010001513A1/ja active Application Filing

- 2009-05-28 US US12/473,604 patent/US20100001315A1/en not_active Abandoned

- 2009-06-25 TW TW098121446A patent/TW201003896A/zh unknown

Also Published As

| Publication number | Publication date |

|---|---|

| WO2010001513A1 (ja) | 2010-01-07 |

| US20100001315A1 (en) | 2010-01-07 |

| TW201003896A (en) | 2010-01-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5340961B2 (ja) | 半導体装置 | |

| JP4772843B2 (ja) | 半導体装置及びその製造方法 | |

| JP2008130775A (ja) | 半導体装置 | |

| JP6739372B2 (ja) | 半導体装置 | |

| US8592893B2 (en) | Power semiconductor device | |

| JP2007123570A (ja) | 半導体装置 | |

| JP2019114643A (ja) | 半導体装置およびその製造方法 | |

| JP4971848B2 (ja) | 低スイッチング損失、低ノイズを両立するパワーmos回路 | |

| CN110098124A (zh) | 功率半导体器件和用于制造功率半导体器件的方法 | |

| JP4761691B2 (ja) | 半導体装置 | |

| KR20090107024A (ko) | Pn접합 및 모스 커패시터 하이브리드 리설프 트랜지스터 | |

| JP2009105177A (ja) | 半導体装置 | |

| JP2012015279A (ja) | 半導体装置及びその製造方法 | |

| JP5493435B2 (ja) | 高耐圧半導体装置および高電圧集積回路装置 | |

| WO2010001513A1 (ja) | 半導体装置 | |

| US9035386B2 (en) | Semiconductor structure and method for manufacturing the same | |

| JP2003031821A (ja) | 半導体装置 | |

| JP2008270367A (ja) | 半導体装置 | |

| JP2012004466A (ja) | 半導体装置 | |

| JP7338242B2 (ja) | 半導体装置 | |

| JP2008205494A (ja) | 半導体装置 | |

| US11508841B2 (en) | Semiconductor device | |

| JP2012182199A (ja) | 半導体装置 | |

| JP7000912B2 (ja) | 半導体装置 | |

| WO2019088241A1 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100611 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110228 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120202 |

|

| A761 | Written withdrawal of application |

Free format text: JAPANESE INTERMEDIATE CODE: A761 Effective date: 20120911 |