JP2010016101A - 積層型電子部品の製造方法 - Google Patents

積層型電子部品の製造方法 Download PDFInfo

- Publication number

- JP2010016101A JP2010016101A JP2008173423A JP2008173423A JP2010016101A JP 2010016101 A JP2010016101 A JP 2010016101A JP 2008173423 A JP2008173423 A JP 2008173423A JP 2008173423 A JP2008173423 A JP 2008173423A JP 2010016101 A JP2010016101 A JP 2010016101A

- Authority

- JP

- Japan

- Prior art keywords

- external terminal

- internal electrode

- ceramic

- electronic component

- distance

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

- 238000000034 method Methods 0.000 title claims abstract description 17

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 15

- 239000000919 ceramic Substances 0.000 claims abstract description 46

- 238000007747 plating Methods 0.000 claims abstract description 36

- 230000002950 deficient Effects 0.000 claims abstract description 20

- 238000000605 extraction Methods 0.000 abstract 1

- 238000010030 laminating Methods 0.000 abstract 1

- 239000010410 layer Substances 0.000 description 22

- 239000003985 ceramic capacitor Substances 0.000 description 16

- 239000003990 capacitor Substances 0.000 description 11

- 239000004020 conductor Substances 0.000 description 11

- 150000001875 compounds Chemical class 0.000 description 5

- 238000003384 imaging method Methods 0.000 description 5

- 238000005259 measurement Methods 0.000 description 4

- 238000010304 firing Methods 0.000 description 3

- 229910052737 gold Inorganic materials 0.000 description 3

- 239000000956 alloy Substances 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000011230 binding agent Substances 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 230000007547 defect Effects 0.000 description 2

- 238000007772 electroless plating Methods 0.000 description 2

- 238000009713 electroplating Methods 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 229910000679 solder Inorganic materials 0.000 description 2

- 229910052718 tin Inorganic materials 0.000 description 2

- 229910002367 SrTiO Inorganic materials 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 229910052797 bismuth Inorganic materials 0.000 description 1

- 239000003054 catalyst Substances 0.000 description 1

- 238000000576 coating method Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 239000002003 electrode paste Substances 0.000 description 1

- -1 for example Substances 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910052745 lead Inorganic materials 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000003960 organic solvent Substances 0.000 description 1

- 238000005498 polishing Methods 0.000 description 1

- 238000007517 polishing process Methods 0.000 description 1

- 230000002250 progressing effect Effects 0.000 description 1

- 238000007650 screen-printing Methods 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000005549 size reduction Methods 0.000 description 1

- 239000002904 solvent Substances 0.000 description 1

- 229910052725 zinc Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/30—Stacked capacitors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/005—Electrodes

- H01G4/012—Form of non-self-supporting electrodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01G—CAPACITORS; CAPACITORS, RECTIFIERS, DETECTORS, SWITCHING DEVICES, LIGHT-SENSITIVE OR TEMPERATURE-SENSITIVE DEVICES OF THE ELECTROLYTIC TYPE

- H01G4/00—Fixed capacitors; Processes of their manufacture

- H01G4/002—Details

- H01G4/228—Terminals

- H01G4/232—Terminals electrically connecting two or more layers of a stacked or rolled capacitor

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/43—Electric condenser making

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10T—TECHNICAL SUBJECTS COVERED BY FORMER US CLASSIFICATION

- Y10T29/00—Metal working

- Y10T29/43—Electric condenser making

- Y10T29/435—Solid dielectric type

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

- Ceramic Capacitors (AREA)

Abstract

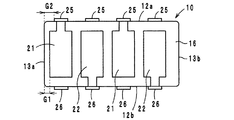

【解決手段】複数のセラミック層を積層してセラミック素体を形成するとともに、引出し部がセラミック素体の側面12a,12bに露出した内部電極21,22をセラミック素体の内部に形成し、側面12a,12bにめっきにより内部電極21,22の露出部と電気的に接続された帯状の外部端子電極25,26を形成する積層型電子部品の製造方法。端面13aに最も近い外部端子電極21から端面13aまでの距離G2を測定し、測定された距離G2が所定の基準値を満たさない場合、そのセラミック素体を不良品として選別除去する。

【選択図】図4

Description

複数のセラミック層を積層し、互いに対向する第1主面及び第2主面と、互いに対向する第1側面及び第2側面と、互いに対向する第1端面及び第2端面と、を有するセラミック素体を形成するとともに、このセラミック素体の内部に、第1側面において該第1側面よりも短い幅の露出部を有する内部電極を形成する工程と、

第1側面上にめっきにより前記内部電極の露出部と電気的に接続された下地めっき膜を有する帯状の外部端子電極を形成する工程と、

第1端面に最も近い外部端子電極から第1端面までの距離を測定し、測定された距離が所定の基準値を満たさない場合、そのセラミック素体を不良品として選別除去する工程と、

を備えたことを特徴とする。

本発明の第1実施例によって製造された積層型セラミックコンデンサアレイについて説明する。この積層型セラミックコンデンサアレイは、図1〜図3に示すように、複数のセラミック層14〜19を積層してセラミック素体10を形成するとともに、このセラミック素体10の内部に第1内部電極21及び第2内部電極22と第1内部導体23及び第2内部導体24を形成したものである。

G1:第1内部電極の容量部と第1端面との距離(サイドギャップ)

G2:第1外部端子電極と第1端面との距離

W1:第1内部電極の中心線Cと容量部側辺との距離

D1:第1内部電極の中心線Cと第1外部端子電極の一方側辺との距離

D2:第1内部電極の中心線Cと第1外部端子電極の他方側辺との距離

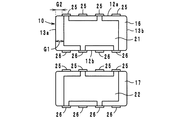

なお、特許文献2に示されているように、外部端子電極25,26をペーストの塗布、焼付けによって形成する方法では、距離G2をサイドギャップG1に置き換えて選別を行うことができない。従来のペースト塗布工法では、内部電極21,22の中心線Cに対して外部端子電極25,26がずれて形成されやすい。これは、ペースト塗布精度に限界があり、目的とする位置に精度よくペーストを塗布することが困難なためである。それゆえ、(G1+W1)=(G2+D1)とみなすことが困難である。例えば、図6に示すようなサイドギャップ不良品であっても、良品と誤認してしまうおそれがある。換言すれば、図5と比較した場合、サイドギャップG1がともに不良であっても距離G2が大きくて良品と判別されるおそれがある。

図7は、多端子型の低ESL積層型セラミックコンデンサの二つのセラミック層を示す。この積層型セラミックコンデンサにおいて、第1及び第2内部電極21,22はそれぞれ露出部を有する複数の引出し部を備えている。そして、第1及び第2内部電極21,22のそれぞれの露出部は第1及び第2側面12a,12bのそれぞれにおいてオフセットされて配置されている。このような積層型セラミックコンデンサにおいても、外部端子電極25,26を素体10の側面12a,12b上にめっきにより形成することにより、外部端子電極25,26から素体10の端面13a,13bまでの距離G2を測定することでサイドギャップG1の良否を選別することができる。

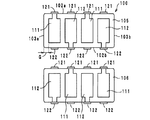

図8は、2端子型の積層型セラミックコンデンサの二つのセラミック層を示す。この積層型セラミックコンデンサにおいて、第1及び第2内部電極21,22は長い露出部を有し、第1及び第2側面12a,12bに比較的広い面積の第1及び第2外部端子電極25,26が形成されている。このような積層型セラミックコンデンサにおいても、外部端子電極25,26を素体10の側面12a,12b上にめっきにより形成することにより、外部端子電極25,26から素体10の端面13a,13bまでの距離G2を測定することでサイドギャップG1の良否を選別することができる。

なお、本発明に係る積層型電子部品の製造方法は前記実施例に限定するものではなく、その要旨の範囲内で種々に変更することができることは勿論である。

11a,11b…主面

12a,12b…側面

13a,13b…端面

21,22…内部電極

25,26…外部端子電極

G1…サイドギャップ

G2…外部端子電極−端面間距離

Claims (2)

- 複数のセラミック層を積層し、互いに対向する第1主面及び第2主面と、互いに対向する第1側面及び第2側面と、互いに対向する第1端面及び第2端面と、を有するセラミック素体を形成するとともに、このセラミック素体の内部に、第1側面において該第1側面よりも短い幅の露出部を有する内部電極を形成する工程と、

第1側面上にめっきにより前記内部電極の露出部と電気的に接続された下地めっき膜を有する帯状の外部端子電極を形成する工程と、

第1端面に最も近い外部端子電極から第1端面までの距離を測定し、測定された距離が所定の基準値を満たさない場合、そのセラミック素体を不良品として選別除去する工程と、

を備えたことを特徴とする積層型電子部品の製造方法。 - 前記内部電極は互いにセラミック層を介して対向する第1内部電極と第2内部電極とからなり、第1内部電極と第2内部電極は一のセラミック層上に隣接して配置されていること、を特徴とする請求項1に記載の積層型電子部品の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008173423A JP5347350B2 (ja) | 2008-07-02 | 2008-07-02 | 積層型電子部品の製造方法 |

| US12/485,963 US8383195B2 (en) | 2008-07-02 | 2009-06-17 | Production method for laminated electronic component |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008173423A JP5347350B2 (ja) | 2008-07-02 | 2008-07-02 | 積層型電子部品の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010016101A true JP2010016101A (ja) | 2010-01-21 |

| JP5347350B2 JP5347350B2 (ja) | 2013-11-20 |

Family

ID=41464587

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008173423A Active JP5347350B2 (ja) | 2008-07-02 | 2008-07-02 | 積層型電子部品の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US8383195B2 (ja) |

| JP (1) | JP5347350B2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012114395A (ja) * | 2010-11-25 | 2012-06-14 | Samsung Electro-Mechanics Co Ltd | 積層型セラミックスキャパシタ |

| WO2014132823A1 (ja) * | 2013-02-28 | 2014-09-04 | デクセリアルズ株式会社 | 静電容量デバイス、共振回路及び電子機器 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR101761938B1 (ko) * | 2012-04-26 | 2017-07-26 | 삼성전기주식회사 | 적층 세라믹 전자 부품 |

| KR102057909B1 (ko) * | 2013-06-14 | 2019-12-20 | 삼성전기주식회사 | 적층 세라믹 커패시터 및 적층 세라믹 커패시터의 실장 기판 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05226178A (ja) * | 1992-02-18 | 1993-09-03 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサおよびその製造法 |

| JPH08330178A (ja) * | 1995-06-05 | 1996-12-13 | Murata Mfg Co Ltd | 積層セラミックコンデンサの製造方法 |

| JP2004312023A (ja) * | 2003-04-08 | 2004-11-04 | Avx Corp | めっきターミネーション |

| JP2005175165A (ja) * | 2003-12-10 | 2005-06-30 | Murata Mfg Co Ltd | 積層セラミックコンデンサおよびその製造方法 |

| JP2008117990A (ja) * | 2006-11-07 | 2008-05-22 | Murata Mfg Co Ltd | 積層コンデンサ |

Family Cites Families (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH1022183A (ja) | 1996-07-01 | 1998-01-23 | Murata Mfg Co Ltd | 電子部品の製造方法 |

| US6380619B2 (en) * | 1998-03-31 | 2002-04-30 | Tdk Corporation | Chip-type electronic component having external electrodes that are spaced at predetermined distances from side surfaces of a ceramic substrate |

| JP3528719B2 (ja) * | 1999-11-18 | 2004-05-24 | 株式会社村田製作所 | 表面実装型電子部品及びその製造方法 |

| US7463474B2 (en) * | 2002-04-15 | 2008-12-09 | Avx Corporation | System and method of plating ball grid array and isolation features for electronic components |

| US7177137B2 (en) * | 2002-04-15 | 2007-02-13 | Avx Corporation | Plated terminations |

| US7576968B2 (en) * | 2002-04-15 | 2009-08-18 | Avx Corporation | Plated terminations and method of forming using electrolytic plating |

| US6960366B2 (en) * | 2002-04-15 | 2005-11-01 | Avx Corporation | Plated terminations |

| US7152291B2 (en) * | 2002-04-15 | 2006-12-26 | Avx Corporation | Method for forming plated terminations |

| US6982863B2 (en) * | 2002-04-15 | 2006-01-03 | Avx Corporation | Component formation via plating technology |

| TWI260657B (en) * | 2002-04-15 | 2006-08-21 | Avx Corp | Plated terminations |

| JP2004047707A (ja) | 2002-07-11 | 2004-02-12 | Murata Mfg Co Ltd | 積層セラミックコンデンサアレイ |

| US7345868B2 (en) * | 2002-10-07 | 2008-03-18 | Presidio Components, Inc. | Multilayer ceramic capacitor with terminal formed by electroless plating |

| US7329976B2 (en) * | 2005-04-27 | 2008-02-12 | Kyocera Corporation | Laminated electronic component |

| KR100944099B1 (ko) * | 2005-10-28 | 2010-02-24 | 가부시키가이샤 무라타 세이사쿠쇼 | 적층형 전자부품 및 그 제조방법 |

| JP4900382B2 (ja) * | 2006-02-27 | 2012-03-21 | 株式会社村田製作所 | 積層型電子部品およびその製造方法 |

| WO2007105395A1 (ja) * | 2006-03-14 | 2007-09-20 | Murata Manufacturing Co., Ltd. | 積層型電子部品の製造方法 |

| JP5289794B2 (ja) * | 2007-03-28 | 2013-09-11 | 株式会社村田製作所 | 積層型電子部品およびその製造方法 |

-

2008

- 2008-07-02 JP JP2008173423A patent/JP5347350B2/ja active Active

-

2009

- 2009-06-17 US US12/485,963 patent/US8383195B2/en active Active

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05226178A (ja) * | 1992-02-18 | 1993-09-03 | Taiyo Yuden Co Ltd | 積層セラミックコンデンサおよびその製造法 |

| JPH08330178A (ja) * | 1995-06-05 | 1996-12-13 | Murata Mfg Co Ltd | 積層セラミックコンデンサの製造方法 |

| JP2004312023A (ja) * | 2003-04-08 | 2004-11-04 | Avx Corp | めっきターミネーション |

| JP2005175165A (ja) * | 2003-12-10 | 2005-06-30 | Murata Mfg Co Ltd | 積層セラミックコンデンサおよびその製造方法 |

| JP2008117990A (ja) * | 2006-11-07 | 2008-05-22 | Murata Mfg Co Ltd | 積層コンデンサ |

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012114395A (ja) * | 2010-11-25 | 2012-06-14 | Samsung Electro-Mechanics Co Ltd | 積層型セラミックスキャパシタ |

| JP2013239753A (ja) * | 2010-11-25 | 2013-11-28 | Samsung Electro-Mechanics Co Ltd | 積層型セラミックスキャパシタ |

| US8619407B2 (en) | 2010-11-25 | 2013-12-31 | Samsung Electro-Mechanics Co., Ltd | Multilayered ceramic capacitor |

| WO2014132823A1 (ja) * | 2013-02-28 | 2014-09-04 | デクセリアルズ株式会社 | 静電容量デバイス、共振回路及び電子機器 |

| JP2014167960A (ja) * | 2013-02-28 | 2014-09-11 | Dexerials Corp | 静電容量デバイス、共振回路及び電子機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20100003397A1 (en) | 2010-01-07 |

| JP5347350B2 (ja) | 2013-11-20 |

| US8383195B2 (en) | 2013-02-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5332475B2 (ja) | 積層セラミック電子部品およびその製造方法 | |

| KR101565641B1 (ko) | 적층 세라믹 전자부품 및 그 실장 기판 | |

| US8125765B2 (en) | Laminated ceramic electronic component | |

| US9136057B2 (en) | Ceramic electronic component, method of manufacturing the same, and collective component | |

| KR101548798B1 (ko) | 적층 세라믹 전자부품 및 그 실장 기판 | |

| US9190213B2 (en) | Method of manufacturing multilayer ceramic capacitor and multilayer ceramic capacitor | |

| JP6020503B2 (ja) | 積層セラミック電子部品 | |

| KR102061507B1 (ko) | 적층 세라믹 전자부품 및 적층 세라믹 전자부품 실장 기판 | |

| US10340081B2 (en) | Ceramic capacitor | |

| KR101927731B1 (ko) | 적층 세라믹 콘덴서 | |

| US20130141837A1 (en) | Multilayer ceramic electronic part | |

| US20160005539A1 (en) | Multilayer ceramic capacitor, manufacturing method thereof, and board having the same | |

| JP5589982B2 (ja) | 積層セラミック電子部品 | |

| US9818538B2 (en) | Multilayer ceramic electronic component and board for mounting thereof | |

| US9040840B2 (en) | Multilayer ceramic electronic component and mounting board therefor | |

| JP5725678B2 (ja) | 積層セラミック電子部品、その製造方法及びその実装基板 | |

| KR101434103B1 (ko) | 적층 세라믹 전자부품 및 적층 세라믹 전자부품의 실장 기판 | |

| CN102110529A (zh) | 多层陶瓷电容器及其制造方法 | |

| JP5347350B2 (ja) | 積層型電子部品の製造方法 | |

| KR20140128099A (ko) | 적층 세라믹 전자부품 및 적층 세라믹 전자부품 실장 기판 | |

| CN111755248B (zh) | 层叠陶瓷电容器 | |

| JP2004235377A (ja) | セラミック電子部品 | |

| CN110828173A (zh) | 多层陶瓷电容器及制造该多层陶瓷电容器的方法 | |

| US9117592B2 (en) | Multilayer ceramic electronic component and mounting board therefor | |

| KR20160053682A (ko) | 적층 세라믹 커패시터, 적층 세라믹 커패시터의 제조 방법 및 적층 세라믹 커패시터의 실장 기판 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120731 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120821 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121022 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20121022 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130312 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130507 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130723 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130805 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5347350 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |