JP2010008869A - マッハツェンダ型光変調器 - Google Patents

マッハツェンダ型光変調器 Download PDFInfo

- Publication number

- JP2010008869A JP2010008869A JP2008170325A JP2008170325A JP2010008869A JP 2010008869 A JP2010008869 A JP 2010008869A JP 2008170325 A JP2008170325 A JP 2008170325A JP 2008170325 A JP2008170325 A JP 2008170325A JP 2010008869 A JP2010008869 A JP 2010008869A

- Authority

- JP

- Japan

- Prior art keywords

- modulation waveguide

- modulation

- disposed

- waveguide

- ground electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Landscapes

- Optical Modulation, Optical Deflection, Nonlinear Optics, Optical Demodulation, Optical Logic Elements (AREA)

Abstract

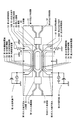

【解決手段】 半導体基板の上に、相互に間隔を隔てて第1及び第2の変調導波路(28,29)が配置される。さらに、第1及び変調導波路に接続される分波器(25)及び合波器(30)が配置される。第1の変調導波路の上に第1の信号電極(35)が配置され、第2の変調導波路の上に第2の信号電極(36)が配置される。第1の信号電極の両側の基板表面のうち、第2の信号電極側に第1の内側接地電極(39)が配置され、その反対側に第1の外側接地電極(37)が配置される。第2の信号電極の両側の基板表面のうち、第1の信号電極側に第2の内側接地電極(39)が配置され、その反対側に第2の外側接地電極(38)が配置される。第1の及び第2の内側接地電極は、第1の変調導波路及び前記第2の変調導波路のいずれとも重ならない。

【選択図】 図1

Description

半導体基板の上に、相互に間隔を隔てて配置された第1及び第2の変調導波路と、

前記半導体基板の上に配置され、前記第1の変調導波路及び第2の変調導波路の入力端に接続された分波器と、

前記半導体基板の上に配置され、前記第1の変調導波路及び第2の変調導波路の出力端に接続された合波器と、

前記第1の変調導波路の上に、該第1の変調導波路に沿って配置された第1の信号電極と、

前記第2の変調導波路の上に、該第2の変調導波路に沿って配置された第2の信号電極と、

前記第1の信号電極の両側の基板表面のうち、前記第2の信号電極側に配置された第1の内側接地電極と、

前記第1の信号電極の両側の基板表面のうち、前記第2の信号電極とは反対側に配置された第1の外側接地電極と、

前記第2の信号電極の両側の基板表面のうち、前記第1の信号電極側に配置された第2の内側接地電極と、

前記第2の信号電極の両側の基板表面のうち、前記第1の信号電極とは反対側に配置された第2の外側接地電極と

を有し、

前記第1の内側接地電極及び前記第2の内側接地電極は、平面視において、前記第1の変調導波路、及び前記第2の変調導波路のいずれとも重ならない。

21 第1の入力導波路

22 第2の入力導波路

25 分波器

28 第1の変調導波路

29 第2の変調導波路

30 合波器

35 第1の信号電極

36 第2の信号電極

37 第1の外側接地電極

38 第2の外側接地電極

39 内側接地電極

41 第1の埋込部材

42 第2の埋込部材

43、44 埋込部材

45 閉じた領域

46 低誘電率層

51 第1の信号源

52 第2の信号源

53 第1の終端抵抗

54 第2の終端抵抗

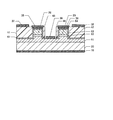

61 下部クラッド層

62 コア層

63 上部クラッド層

64 コンタクト層

65 半絶縁性高抵抗膜

65a 埋込層

67 保護膜

70 背面接地電極

80 波長可変半導体レーザ素子

100、101、102 マスクパターン

Claims (7)

- 半導体基板の上に、相互に間隔を隔てて配置された第1及び第2の変調導波路と、

前記半導体基板の上に配置され、前記第1の変調導波路及び第2の変調導波路の入力端に接続された分波器と、

前記半導体基板の上に配置され、前記第1の変調導波路及び第2の変調導波路の出力端に接続された合波器と、

前記第1の変調導波路の上に、該第1の変調導波路に沿って配置された第1の信号電極と、

前記第2の変調導波路の上に、該第2の変調導波路に沿って配置された第2の信号電極と、

前記第1の信号電極の両側の基板表面のうち、前記第2の信号電極側に配置された第1の内側接地電極と、

前記第1の信号電極の両側の基板表面のうち、前記第2の信号電極とは反対側に配置された第1の外側接地電極と、

前記第2の信号電極の両側の基板表面のうち、前記第1の信号電極側に配置された第2の内側接地電極と、

前記第2の信号電極の両側の基板表面のうち、前記第1の信号電極とは反対側に配置された第2の外側接地電極と

を有し、

前記第1の内側接地電極及び前記第2の内側接地電極は、平面視において、前記第1の変調導波路、及び前記第2の変調導波路のいずれとも重ならない光変調器。 - 前記第1の内側接地電極と前記第2の内側接地電極とが、1つの導電パターンを共有する請求項1に記載の光変調器。

- さらに、前記半導体基板の表面に形成され、それぞれ前記第1の変調導波路及び前記第2の変調導波路に沿う平面形状を持つ第1のメサ構造及び第2のメサ構造を有し、

前記第1の変調導波路及び前記第2の変調導波路は、それぞれ前記第1のメサ構造及び第2のメサ構造内に配置されており、

前記第1の信号電極及び前記第2の信号電極は、それぞれ前記第1のメサ構造及び前記第2のメサ構造の上に配置されている請求項1または2に記載の光変調器。 - さらに、前記第1のメサ構造及び第2のメサ構造の外側の前記半導体基板の上に配置され、前記第1のメサ構造及び前記第2のメサ構造を形成する材料よりも誘電率が低い材料で形成された埋込部材を有し、

前記第1及び第2の外側接地電極が前記埋込部材の上に形成されている請求項3に記載の光変調器。 - 前記半導体基板が、その表層部に形成された導電性半導体材料からなる導電層を含み、前記第1及び第2の内側接地電極が、前記導電層に接している請求項1乃至4のいずれか1項に記載の光変調器。

- 前記半導体基板が導電性半導体材料で形成されており、

さらに、該半導体基板の裏側の表面に形成された背面接地電極を有する請求項1乃至5のいずれか1項に記載の光変調器。 - 前記第1の内側接地電極及び第2の内側接地電極は、平面視において、前記第1の変調導波路、前記第2の変調導波路、前記分波器、及び前記合波器で囲まれた閉じた領域の外側の接地電位が与えられる導電性領域に、基板上の配線を介して接続されない請求項1乃至6のいずれか1項に記載の光変調器。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008170325A JP5104598B2 (ja) | 2008-06-30 | 2008-06-30 | マッハツェンダ型光変調器 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008170325A JP5104598B2 (ja) | 2008-06-30 | 2008-06-30 | マッハツェンダ型光変調器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010008869A true JP2010008869A (ja) | 2010-01-14 |

| JP5104598B2 JP5104598B2 (ja) | 2012-12-19 |

Family

ID=41589423

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008170325A Expired - Fee Related JP5104598B2 (ja) | 2008-06-30 | 2008-06-30 | マッハツェンダ型光変調器 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5104598B2 (ja) |

Cited By (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011203384A (ja) * | 2010-03-24 | 2011-10-13 | Sumitomo Electric Ind Ltd | 半導体光素子及びマッハツェンダー型光変調素子 |

| WO2011126068A1 (ja) | 2010-04-07 | 2011-10-13 | 日産自動車株式会社 | 電解液注入装置及び電解液注入方法 |

| JP2012220530A (ja) * | 2011-04-04 | 2012-11-12 | Mitsubishi Electric Corp | 光変調素子 |

| JP2013250527A (ja) * | 2012-06-04 | 2013-12-12 | Sumitomo Electric Ind Ltd | 半導体マッハツェンダ変調器および半導体マッハツェンダ変調器の製造方法 |

| JP2014038322A (ja) * | 2012-07-19 | 2014-02-27 | Sumitomo Electric Ind Ltd | 光半導体素子の製造方法 |

| JP2014164243A (ja) * | 2013-02-27 | 2014-09-08 | Sumitomo Electric Ind Ltd | 光変調モジュール、半導体光変調素子 |

| JP2015194629A (ja) * | 2014-03-31 | 2015-11-05 | 日本電信電話株式会社 | 半導体光変調器 |

| JP2016024409A (ja) * | 2014-07-23 | 2016-02-08 | 住友電気工業株式会社 | 変調器およびその製造方法 |

| JP2018146729A (ja) * | 2017-03-03 | 2018-09-20 | 住友電気工業株式会社 | 半導体素子の製造方法 |

| JP2018159872A (ja) * | 2017-03-23 | 2018-10-11 | 住友電気工業株式会社 | 半導体光素子及びその製造方法 |

| JP2020057024A (ja) * | 2016-07-27 | 2020-04-09 | 住友大阪セメント株式会社 | 光変調器 |

| JP2022064266A (ja) * | 2020-10-13 | 2022-04-25 | 日本ルメンタム株式会社 | 半導体光素子及び半導体光装置 |

| WO2023095261A1 (ja) * | 2021-11-25 | 2023-06-01 | 三菱電機株式会社 | マッハツェンダ変調器 |

| JP7504330B1 (ja) * | 2024-01-17 | 2024-06-21 | 三菱電機株式会社 | 半導体装置の製造方法 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002122834A (ja) * | 2000-10-19 | 2002-04-26 | Sumitomo Osaka Cement Co Ltd | 光導波路素子 |

| JP2002169131A (ja) * | 2000-12-04 | 2002-06-14 | Fujitsu Ltd | 光半導体素子及び光半導体素子の変調方法 |

| JP2003177368A (ja) * | 2001-12-11 | 2003-06-27 | Fujitsu Ltd | 半導体光変調器、マッハツェンダ型光変調器、及び光変調器一体型半導体レーザ |

| JP2003322831A (ja) * | 2002-05-07 | 2003-11-14 | Fujitsu Ltd | 半導体マッハツェンダ型光変調器 |

| JP2004151590A (ja) * | 2002-10-31 | 2004-05-27 | Fujitsu Ltd | 光半導体装置 |

| WO2007040106A1 (ja) * | 2005-09-30 | 2007-04-12 | Sumitomo Osaka Cement Co., Ltd. | 光変調器及びその製造方法 |

| JP2007510180A (ja) * | 2003-10-28 | 2007-04-19 | フィルトロニク パブリック リミテッド カンパニー | 共平面導波管線路 |

| JP2008210962A (ja) * | 2007-02-26 | 2008-09-11 | Fujitsu Ltd | フレキシブル基板、光学部品、光送信器および光受信器 |

-

2008

- 2008-06-30 JP JP2008170325A patent/JP5104598B2/ja not_active Expired - Fee Related

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002122834A (ja) * | 2000-10-19 | 2002-04-26 | Sumitomo Osaka Cement Co Ltd | 光導波路素子 |

| JP2002169131A (ja) * | 2000-12-04 | 2002-06-14 | Fujitsu Ltd | 光半導体素子及び光半導体素子の変調方法 |

| JP2003177368A (ja) * | 2001-12-11 | 2003-06-27 | Fujitsu Ltd | 半導体光変調器、マッハツェンダ型光変調器、及び光変調器一体型半導体レーザ |

| JP2003322831A (ja) * | 2002-05-07 | 2003-11-14 | Fujitsu Ltd | 半導体マッハツェンダ型光変調器 |

| JP2004151590A (ja) * | 2002-10-31 | 2004-05-27 | Fujitsu Ltd | 光半導体装置 |

| JP2007510180A (ja) * | 2003-10-28 | 2007-04-19 | フィルトロニク パブリック リミテッド カンパニー | 共平面導波管線路 |

| WO2007040106A1 (ja) * | 2005-09-30 | 2007-04-12 | Sumitomo Osaka Cement Co., Ltd. | 光変調器及びその製造方法 |

| JP2008210962A (ja) * | 2007-02-26 | 2008-09-11 | Fujitsu Ltd | フレキシブル基板、光学部品、光送信器および光受信器 |

Cited By (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011203384A (ja) * | 2010-03-24 | 2011-10-13 | Sumitomo Electric Ind Ltd | 半導体光素子及びマッハツェンダー型光変調素子 |

| WO2011126068A1 (ja) | 2010-04-07 | 2011-10-13 | 日産自動車株式会社 | 電解液注入装置及び電解液注入方法 |

| JP2012220530A (ja) * | 2011-04-04 | 2012-11-12 | Mitsubishi Electric Corp | 光変調素子 |

| US9285613B2 (en) | 2012-06-04 | 2016-03-15 | Sumitomo Electric Industries, Ltd. | Semiconductor Mach-Zehnder modulator and method for manufacturing semiconductor Mach-Zehnder modulators |

| JP2013250527A (ja) * | 2012-06-04 | 2013-12-12 | Sumitomo Electric Ind Ltd | 半導体マッハツェンダ変調器および半導体マッハツェンダ変調器の製造方法 |

| JP2014038322A (ja) * | 2012-07-19 | 2014-02-27 | Sumitomo Electric Ind Ltd | 光半導体素子の製造方法 |

| JP2014164243A (ja) * | 2013-02-27 | 2014-09-08 | Sumitomo Electric Ind Ltd | 光変調モジュール、半導体光変調素子 |

| US9046703B2 (en) | 2013-02-27 | 2015-06-02 | Sumitomo Electric Industries, Ltd. | Optical modulator module and semiconductor optical modulator |

| JP2015194629A (ja) * | 2014-03-31 | 2015-11-05 | 日本電信電話株式会社 | 半導体光変調器 |

| JP2016024409A (ja) * | 2014-07-23 | 2016-02-08 | 住友電気工業株式会社 | 変調器およびその製造方法 |

| JP2020057024A (ja) * | 2016-07-27 | 2020-04-09 | 住友大阪セメント株式会社 | 光変調器 |

| JP2018146729A (ja) * | 2017-03-03 | 2018-09-20 | 住友電気工業株式会社 | 半導体素子の製造方法 |

| JP2018159872A (ja) * | 2017-03-23 | 2018-10-11 | 住友電気工業株式会社 | 半導体光素子及びその製造方法 |

| JP2022064266A (ja) * | 2020-10-13 | 2022-04-25 | 日本ルメンタム株式会社 | 半導体光素子及び半導体光装置 |

| JP7596137B2 (ja) | 2020-10-13 | 2024-12-09 | 日本ルメンタム株式会社 | 半導体光素子及び半導体光装置 |

| WO2023095261A1 (ja) * | 2021-11-25 | 2023-06-01 | 三菱電機株式会社 | マッハツェンダ変調器 |

| JP7504330B1 (ja) * | 2024-01-17 | 2024-06-21 | 三菱電機株式会社 | 半導体装置の製造方法 |

| WO2025154209A1 (ja) * | 2024-01-17 | 2025-07-24 | 三菱電機株式会社 | 半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5104598B2 (ja) | 2012-12-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5104598B2 (ja) | マッハツェンダ型光変調器 | |

| US8412008B2 (en) | Semiconductor optical device | |

| US6122414A (en) | Semiconductor Mach-Zehnder modulator | |

| US8412005B2 (en) | Mach-Zehnder interferometer type optical modulator | |

| EP0526023B1 (en) | Semiconductor optical guided-wave device and its production method | |

| US20100284019A1 (en) | Semiconductor integrated optical device and method of making the same | |

| JP2019194637A (ja) | 半導体マッハ・ツェンダ型光変調器およびそれを用いたiq光変調器 | |

| US10027088B2 (en) | Integrated semiconductor optical element and manufacturing method for same | |

| JP2010226062A (ja) | 光導波素子とその製造方法、半導体素子、レーザモジュール及び光伝送システム | |

| JP2003177369A (ja) | 半導体光変調器、それを用いたマッハツェンダ型光変調器、及び半導体光変調器の製造方法 | |

| US20030091287A1 (en) | Multimode interference (MMI) device | |

| US20130336611A1 (en) | Optical device | |

| JP3981864B2 (ja) | ナイトライド系半導体レーザを備えた光集積装置 | |

| US8818142B2 (en) | Optical semiconductor device | |

| US8384980B2 (en) | Semiconductor optical modulation device, Mach-Zehnder interferometer type semiconductor optical modulator, and method for producing semiconductor optical modulation device | |

| JP5497678B2 (ja) | 半導体光集積素子 | |

| JP2012209489A (ja) | 光半導体素子及びその製造方法 | |

| JP6348880B2 (ja) | 半導体マッハツェンダ光変調器 | |

| JP5917645B2 (ja) | 光スイッチ素子 | |

| JP6531525B2 (ja) | 光変調器および光変調器の製造方法 | |

| JP2016194655A (ja) | 光導波路素子 | |

| JP5553151B2 (ja) | 半導体光変調器及びそれを用いた半導体光送信機 | |

| JP2011077329A (ja) | 半導体光集積素子、及びその製造方法 | |

| JP6452451B2 (ja) | 光集積素子およびその製造方法 | |

| JPH05188412A (ja) | 光半導体素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110315 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120316 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120508 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120705 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120904 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120917 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5104598 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151012 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |