JP2009506472A - 不揮発性メモリ・セルのプログラミング - Google Patents

不揮発性メモリ・セルのプログラミング Download PDFInfo

- Publication number

- JP2009506472A JP2009506472A JP2008527982A JP2008527982A JP2009506472A JP 2009506472 A JP2009506472 A JP 2009506472A JP 2008527982 A JP2008527982 A JP 2008527982A JP 2008527982 A JP2008527982 A JP 2008527982A JP 2009506472 A JP2009506472 A JP 2009506472A

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- applying

- programming

- programming voltage

- source

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0408—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors

- G11C16/0425—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells containing floating gate transistors comprising cells containing a merged floating gate and select transistor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

- G11C16/12—Programming voltage switching circuits

Abstract

Description

Claims (20)

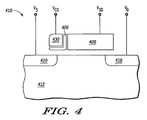

- 読み出し動作中にソースとして機能する第1の電流電極と、読み出し動作中にドレインとして機能する第2の電流電極と、バイアスするゲートとして機能する制御電極とを含む不揮発性メモリ(NVM)セルをプログラミングする方法であって、

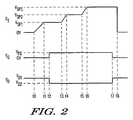

第1のプログラミング電圧を前記第1の電流電極に印加するステップと、

前記第1のプログラミング電圧を印加した後で、当該第1のプログラミング電圧より大きい第2のプログラミング電圧を前記第1の電流電極に印加するステップと、

第1のプログラミング電圧を印加する前記ステップ中にプログラミング電圧を前記制御電圧に印加し、且つ第2のプログラミング電圧を印加する前記ステップ中にプログラミング電圧を前記制御電圧に印加するステップと

を備える方法。 - 第1のプログラミング電圧を印加する前記ステップが、前記第1のプログラミング電圧までランプアップすることにより実行されるよう特徴付けられる請求項1記載の方法。

- 第2のプログラミング電圧を印加する前記ステップが、前記第1のプログラミング電圧から前記第2のプログラミング電圧までランプすることにより実行されるよう特徴付けられる請求項2記載の方法。

- 前記第1のプログラミング電圧が、第1の持続時間にわたり印加され、

前記第2のプログラミング電圧が、第2の持続時間にわたり印加される

請求項1記載の方法。 - 前記第2の持続時間が、前記第1の持続時間より長い請求項4記載の方法。

- 前記NVMセルが、前記第1のプログラミング電圧を印加することと前記第2のプログラミング電圧を印加することとの間で選択解除される請求項1記載の方法。

- 前記第1のプログラミング電圧及び第2のプログラミング電圧が、第1のプログラミング電圧を第1の電流電極に印加する前記ステップ及び第2のプログラミング電圧を第1の電流電極に印加する前記ステップ中に前記制御電極に印加される電圧より大きい請求項1記載の方法。

- 前記第2の電流電極が、第1のプログラミング電圧を第1の電流電極に印加する前記ステップ前に第3の電圧であり、

前記第2の電流電極が、第1のプログラミング電圧を第1の電流電極に印加する前記ステップ中に前記第3の電圧とは異なる電圧であり、

前記第2の電流電極が、第2のプログラミング電圧を第1の電流電極に印加する前記ステップ中に前記第3の電圧とは異なる電圧である

請求項1記載の方法。 - 第2のプログラミング電圧を印加する前記ステップが、第1のプログラミング電圧を印加する前記ステップからとぎれなく続く請求項1記載の方法。

- 第1のプログラミング電圧を印加する前記ステップの後に、前記第2のプログラミング電圧より大きい第3のプログラミング電圧を前記第1の制御電極に印加するステップを更に備える請求項1記載の方法。

- 第3のプログラミング電圧を印加する前記ステップが更に、前記第2のプログラミング電圧から前記第3のプログラミング電圧へランプすることにより実行されるよう特徴付けられる請求項10記載の方法。

- 第3のプログラミング電圧を印加する前記ステップが、第2のプログラミングを印加する前記ステップからとぎれなく続く請求項10記載の方法。

- 前記第1のプログラミング電圧が、第1の持続時間にわたり印加され、

前記第2のプログラミング電圧が、第2の持続時間にわたり印加され、

前記第3のプログラミング電圧が、第3の持続時間にわたり印加される

請求項10記載の方法。 - 前記第3の持続時間が、前記第1の持続時間より長く、

前記第3の持続時間が、前記第2の持続時間より長い

請求項13記載の方法。 - 前記NVMのセルを前記第2のプログラミング電圧を印加することと前記第3のプログラミング電圧を印加することとの間で選択解除するステップを更に備える請求項10記載の方法。

- 前記NVMのセルが、金属層、ポリシリコン層、ナノ結晶の層、及び電荷蓄積誘電体層から成るグループから選択された蓄積層を有する請求項1記載の方法。

- 第1のプログラミング電圧を第1の電流電極に印加する前記ステップ及び第2のプログラミング電圧を第1の電流電極に印加する前記ステップが、前記第1のプログラミング電圧を通って前記第2のプログラミング電圧へランプすることにより実行されるように特徴付けられる請求項1記載の方法。

- 不揮発性(NVM)セルを読み出すためのバイアスするゲート、ソース及びドレインを含む当該不揮発性(NVM)セルをプログラミングする方法であって、

第1の電圧を前記ソースに第1の持続時間にわたり印加するステップと、

第1の電圧を印加する前記ステップ後で且つ前記NVMセルの読み出しを実行する前に、前記第1の電圧より大きい第2の電圧を前記ソースに第2の持続時間にわたり印加するステップと、

第2の電圧を印加する前記ステップ後で且つ前記NVMセルの読み出しを実行する前に、前記第2の電圧より大きい第3の電圧を前記ソースに第3の持続時間にわたり印加するステップと

を備える方法。 - 前記第3の持続時間が、前記第1の持続時間より長く、

前記第3の持続時間が、前記第2の持続時間より長い

請求項18記載の方法。 - 読み出すためのバイアスするゲート、ソース及びソースを含む不揮発性(NVM)セルをプログラミングする方法であって、

第1の電圧を前記ソースに印加するステップと、

前記第1の電圧より大きい第2の電圧を前記ソースに印加するステップと、

前記第2の電圧より大きい第3の電圧を前記ソースに印加するステップと、

第1の電圧を前記ソースに印加する前記ステップ中に電圧を前記バイアスするゲートに印加し、第2の電圧を前記ソースに印加する前記ステップ中に電圧を前記バイアスするゲートに印加し、且つ第3の電圧を前記ソースに印加する前記ステップ中に電圧を前記バイアスするゲートに印加するステップと、を備えるとぎれなしの部分を含む方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/209,294 US7342833B2 (en) | 2005-08-23 | 2005-08-23 | Nonvolatile memory cell programming |

| PCT/US2006/031840 WO2007024565A2 (en) | 2005-08-23 | 2006-08-16 | Nonvolatile memory cell programming |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009506472A true JP2009506472A (ja) | 2009-02-12 |

| JP2009506472A5 JP2009506472A5 (ja) | 2009-09-24 |

Family

ID=37772152

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008527982A Pending JP2009506472A (ja) | 2005-08-23 | 2006-08-16 | 不揮発性メモリ・セルのプログラミング |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7342833B2 (ja) |

| JP (1) | JP2009506472A (ja) |

| CN (1) | CN101243520B (ja) |

| TW (1) | TW200713281A (ja) |

| WO (1) | WO2007024565A2 (ja) |

Cited By (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011204342A (ja) * | 2010-03-24 | 2011-10-13 | Ememory Technology Inc | チャネル熱電子注入プログラミング方法及び関連する装置 |

| US8467245B2 (en) | 2010-03-24 | 2013-06-18 | Ememory Technology Inc. | Non-volatile memory device with program current clamp and related method |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100771520B1 (ko) * | 2006-10-23 | 2007-10-30 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 프로그램 방법 |

| US8320191B2 (en) | 2007-08-30 | 2012-11-27 | Infineon Technologies Ag | Memory cell arrangement, method for controlling a memory cell, memory array and electronic device |

| US7630250B2 (en) * | 2007-10-16 | 2009-12-08 | Spansion Llc | Controlled ramp rates for metal bitlines during write operations from high voltage driver for memory applications |

| JP5384012B2 (ja) * | 2008-01-24 | 2014-01-08 | ローム株式会社 | Eepromおよびそれを用いた電子機器 |

| US7764550B2 (en) * | 2008-11-25 | 2010-07-27 | Freescale Semiconductor, Inc. | Method of programming a non-volatile memory |

| US7929343B2 (en) * | 2009-04-07 | 2011-04-19 | Micron Technology, Inc. | Methods, devices, and systems relating to memory cells having a floating body |

| CN103165188A (zh) * | 2011-12-09 | 2013-06-19 | 中国科学院微电子研究所 | 一种多位非挥发存储单元及阵列的编程方法 |

| EP3773061B1 (en) * | 2019-06-19 | 2023-10-18 | Farouk Systems, Inc. | Lava rock containing hair dryer |

Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02126498A (ja) * | 1988-07-08 | 1990-05-15 | Hitachi Ltd | 不揮発性半導体記憶装置 |

| JPH0773685A (ja) * | 1993-09-06 | 1995-03-17 | Hitachi Ltd | 半導体不揮発性記憶装置 |

| JPH07169284A (ja) * | 1993-12-13 | 1995-07-04 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH10228784A (ja) * | 1997-02-12 | 1998-08-25 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JPH10302486A (ja) * | 1996-08-30 | 1998-11-13 | Sanyo Electric Co Ltd | 半導体記憶装置 |

| JP2002109891A (ja) * | 2000-09-28 | 2002-04-12 | Hitachi Ltd | 不揮発性メモリと不揮発性メモリの書き込み方法 |

| JP2002319289A (ja) * | 2000-12-07 | 2002-10-31 | Saifun Semiconductors Ltd | Nromアレイの基準セルのプログラミングおよび消去方法 |

| JP2004022027A (ja) * | 2002-06-13 | 2004-01-22 | Matsushita Electric Ind Co Ltd | 半導体記憶装置および半導体記憶装置の書き込み方法 |

| JP2004023044A (ja) * | 2002-06-20 | 2004-01-22 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2005063516A (ja) * | 2003-08-08 | 2005-03-10 | Sharp Corp | 不揮発性半導体記憶装置の書き込み方法 |

| JP2005216466A (ja) * | 2004-01-21 | 2005-08-11 | Sharp Corp | 不揮発性半導体記憶装置 |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3553947A (en) | 1968-08-12 | 1971-01-12 | Root Mfg Co Inc | Grass catcher for lawnmowers |

| US3820312A (en) | 1969-11-24 | 1974-06-28 | Scott & Sons Co O | Grass catcher |

| US3822536A (en) | 1973-05-24 | 1974-07-09 | H Leader | Grass catcher |

| JPS62190420U (ja) | 1986-05-24 | 1987-12-03 | ||

| US6198662B1 (en) | 1999-06-24 | 2001-03-06 | Amic Technology, Inc. | Circuit and method for pre-erasing/erasing flash memory array |

| US7076610B2 (en) * | 2000-11-22 | 2006-07-11 | Integrated Device Technology, Inc. | FIFO memory devices having multi-port cache memory arrays therein that support hidden EDC latency and bus matching and methods of operating same |

| US6738289B2 (en) | 2001-02-26 | 2004-05-18 | Sandisk Corporation | Non-volatile memory with improved programming and method therefor |

| KR100390959B1 (ko) * | 2001-06-29 | 2003-07-12 | 주식회사 하이닉스반도체 | 센싱회로를 이용한 멀티레벨 플래시 메모리 프로그램/리드방법 |

| US6741502B1 (en) * | 2001-09-17 | 2004-05-25 | Sandisk Corporation | Background operation for memory cells |

| CN1188909C (zh) * | 2002-02-25 | 2005-02-09 | 力旺电子股份有限公司 | 一种非易失性存储单元的编程及擦除方法 |

| US6649453B1 (en) * | 2002-08-29 | 2003-11-18 | Micron Technology, Inc. | Contactless uniform-tunneling separate p-well (CUSP) non-volatile memory array architecture, fabrication and operation |

| KR100496866B1 (ko) * | 2002-12-05 | 2005-06-22 | 삼성전자주식회사 | 미프로그램된 셀들 및 과프로그램된 셀들 없이 균일한문턱 전압 분포를 갖는 플레쉬 메모리 장치 및 그프로그램 검증 방법 |

| US6882567B1 (en) * | 2002-12-06 | 2005-04-19 | Multi Level Memory Technology | Parallel programming of multiple-bit-per-cell memory cells on a continuous word line |

| US7209983B2 (en) * | 2003-07-03 | 2007-04-24 | Integrated Device Technology, Inc. | Sequential flow-control and FIFO memory devices that are depth expandable in standard mode operation |

| US7093047B2 (en) * | 2003-07-03 | 2006-08-15 | Integrated Device Technology, Inc. | Integrated circuit memory devices having clock signal arbitration circuits therein and methods of performing clock signal arbitration |

-

2005

- 2005-08-23 US US11/209,294 patent/US7342833B2/en active Active

-

2006

- 2006-08-11 TW TW095129481A patent/TW200713281A/zh unknown

- 2006-08-16 WO PCT/US2006/031840 patent/WO2007024565A2/en active Application Filing

- 2006-08-16 CN CN2006800305639A patent/CN101243520B/zh active Active

- 2006-08-16 JP JP2008527982A patent/JP2009506472A/ja active Pending

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH02126498A (ja) * | 1988-07-08 | 1990-05-15 | Hitachi Ltd | 不揮発性半導体記憶装置 |

| JPH0773685A (ja) * | 1993-09-06 | 1995-03-17 | Hitachi Ltd | 半導体不揮発性記憶装置 |

| JPH07169284A (ja) * | 1993-12-13 | 1995-07-04 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JPH10302486A (ja) * | 1996-08-30 | 1998-11-13 | Sanyo Electric Co Ltd | 半導体記憶装置 |

| JPH10228784A (ja) * | 1997-02-12 | 1998-08-25 | Mitsubishi Electric Corp | 不揮発性半導体記憶装置 |

| JP2002109891A (ja) * | 2000-09-28 | 2002-04-12 | Hitachi Ltd | 不揮発性メモリと不揮発性メモリの書き込み方法 |

| JP2002319289A (ja) * | 2000-12-07 | 2002-10-31 | Saifun Semiconductors Ltd | Nromアレイの基準セルのプログラミングおよび消去方法 |

| JP2004022027A (ja) * | 2002-06-13 | 2004-01-22 | Matsushita Electric Ind Co Ltd | 半導体記憶装置および半導体記憶装置の書き込み方法 |

| JP2004023044A (ja) * | 2002-06-20 | 2004-01-22 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP2005063516A (ja) * | 2003-08-08 | 2005-03-10 | Sharp Corp | 不揮発性半導体記憶装置の書き込み方法 |

| JP2005216466A (ja) * | 2004-01-21 | 2005-08-11 | Sharp Corp | 不揮発性半導体記憶装置 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011204342A (ja) * | 2010-03-24 | 2011-10-13 | Ememory Technology Inc | チャネル熱電子注入プログラミング方法及び関連する装置 |

| US8369154B2 (en) | 2010-03-24 | 2013-02-05 | Ememory Technology Inc. | Channel hot electron injection programming method and related device |

| US8467245B2 (en) | 2010-03-24 | 2013-06-18 | Ememory Technology Inc. | Non-volatile memory device with program current clamp and related method |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070058434A1 (en) | 2007-03-15 |

| CN101243520A (zh) | 2008-08-13 |

| TW200713281A (en) | 2007-04-01 |

| CN101243520B (zh) | 2010-12-15 |

| WO2007024565A3 (en) | 2007-11-22 |

| WO2007024565A2 (en) | 2007-03-01 |

| US7342833B2 (en) | 2008-03-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7342833B2 (en) | Nonvolatile memory cell programming | |

| US6744675B1 (en) | Program algorithm including soft erase for SONOS memory device | |

| US7590005B2 (en) | Program and erase methods with substrate transient hot carrier injections in a non-volatile memory | |

| JP5259918B2 (ja) | 反転ビット線、電荷をトラップする不揮発性メモリ、およびその動作方法 | |

| US7394702B2 (en) | Methods for erasing and programming memory devices | |

| US6909639B2 (en) | Nonvolatile memory having bit line discharge, and method of operation thereof | |

| JP2007500938A (ja) | 不揮発性メモリおよびその製造方法 | |

| US20070247924A1 (en) | Methods for erasing memory devices and multi-level programming memory device | |

| US20060250855A1 (en) | Erase and read schemes for charge trapping non-volatile memories | |

| US20080285342A1 (en) | Method of Programming a Nonvolatile Memory Cell and Related Memory Array | |

| JP2006252670A (ja) | 不揮発性メモリの駆動方法およびこれに用いられる不揮発性メモリ | |

| US7933150B2 (en) | Nonvolatile semiconductor memory device and programming method thereof | |

| US7561470B2 (en) | Double-side-bias methods of programming and erasing a virtual ground array memory | |

| US7483299B2 (en) | Devices and operation methods for reducing second bit effect in memory device | |

| CN111326200A (zh) | 非易失性存储器及其编程方法 | |

| US6829166B2 (en) | Method for controlling a non-volatile dynamic random access memory | |

| US7423913B2 (en) | Structures and methods for enhancing erase uniformity in a nitride read-only memory array | |

| US9583195B2 (en) | Systems, methods and devices for a memory having a buried select line | |

| TW200302486A (en) | Charge injection | |

| US7023740B1 (en) | Substrate bias for programming non-volatile memory | |

| US7554851B2 (en) | Reset method of non-volatile memory | |

| US7106629B2 (en) | Split-gate P-channel flash memory cell with programming by band-to-band hot electron method | |

| US20080304320A1 (en) | Memory cell and method of programming the same | |

| US20040105316A1 (en) | Low program power flash memory array and related control method | |

| JP3554572B2 (ja) | 不揮発性半導体回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090731 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090731 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20110909 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111107 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111114 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120209 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120718 |