JP2009158751A - 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 - Google Patents

素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 Download PDFInfo

- Publication number

- JP2009158751A JP2009158751A JP2007335819A JP2007335819A JP2009158751A JP 2009158751 A JP2009158751 A JP 2009158751A JP 2007335819 A JP2007335819 A JP 2007335819A JP 2007335819 A JP2007335819 A JP 2007335819A JP 2009158751 A JP2009158751 A JP 2009158751A

- Authority

- JP

- Japan

- Prior art keywords

- protruding

- electrode

- insulating resin

- resin layer

- protruding electrodes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/114—Manufacturing methods by blanket deposition of the material of the bump connector

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/11—Manufacturing methods

- H01L2224/116—Manufacturing methods by patterning a pre-deposited material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/13—Discrete devices, e.g. 3 terminal devices

- H01L2924/1304—Transistor

- H01L2924/1306—Field-effect transistor [FET]

- H01L2924/13091—Metal-Oxide-Semiconductor Field-Effect Transistor [MOSFET]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1904—Component type

- H01L2924/19041—Component type being a capacitor

Landscapes

- Wire Bonding (AREA)

Abstract

【解決手段】素子搭載用基板10は、絶縁樹脂層12と、絶縁樹脂層12の一方の主表面S1に設けられた配線層14と、配線層14と電気的に接続され、配線層14から絶縁樹脂層12側に突出する複数の突起電極16と、絶縁樹脂層12の他方の主表面S2の、複数の突起電極16のそれぞれに対応する位置に設けられた対向電極18と、を備える。突起電極16のうち、一部の突起電極16aの突出長さは、他の突起電極16bの突出長さよりも短く、突起電極16aとこれに対応する対向電極18aとが容量結合し、突起電極16bとこれに対応する対向電極18bとが電気的に接続されている。

【選択図】図1

Description

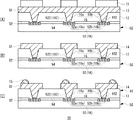

図1は、実施形態1に係る素子搭載用基板10およびこれを用いた半導体モジュール30の構成を示す概略断面図である。半導体モジュール30は、素子搭載用基板10およびこれに搭載された半導体素子50を備える。

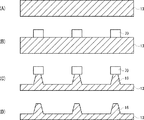

図2(A)〜(D)は、突起電極16の形成方法を示す工程断面図である。

上述の実施形態1では、銅板13と、対向電極18あるいは半導体素子50との間に絶縁樹脂層12を挟持して加圧成形し、これらを一体化して素子搭載用基板10あるいは半導体モジュール30を形成したが、以下のようにして素子搭載用基板10あるいは半導体モジュール30を形成してもよい。以下、本実施形態について説明する。なお、突起電極16の形成方法については、実施形態1と同様である。また、実施形態1と同一の構成については同一の符号を付し、その説明は省略する。

上述の実施形態1および2の構成では、突起電極16aと、対向電極18aあるいは素子電極52aとの間に絶縁樹脂層12が介在しているが、本実施形態に示すように突起電極16aと、対向電極18aあるいは素子電極52aとの間に絶縁樹脂層12よりも誘電率の大きい誘電膜層を設けてもよい。以下、本実施形態について説明する。なお、突起電極16の形成方法については、実施形態1と同様である。また、実施形態1あるいは2と同一の構成については同一の符号を付し、その説明は省略する。

本実施形態は、対向電極18が、絶縁樹脂層12の他方の主表面S2に設けられた他の配線層の一部である構成の例である。以下、本実施形態について説明する。なお、突起電極16の形成方法については、実施形態1と同様である。また、実施形態1ないし3と同一の構成については同一の符号を付し、その説明は省略する。

本実施形態は、対向電極18が、絶縁樹脂層12の他方の主表面S2に設けられた他の配線層の一部である構成の例であるが、実施形態4と製造工程が異なる。以下、本実施形態について説明する。なお、突起電極16の形成方法については、実施形態1と同様である。また、実施形態1ないし4と同一の構成については同一の符号を付し、その説明は省略する。

本実施形態は、突起電極16の形成方法が実施形態1ないし5と異なる。以下、本実施形態について説明する。なお、突起電極16と対向電極18との結合方法については、実施形態1ないし5と同様である。また、実施形態1ないし5と同一の構成については同一の符号を付し、その説明は省略する。

次に、本発明の半導体モジュールを備えた携帯機器について説明する。なお、携帯機器として携帯電話に搭載する例を示すが、たとえば、個人用携帯情報端末(PDA)、デジタルビデオカメラ(DVC)、及びデジタルスチルカメラ(DSC)といった電子機器であってもよい。

Claims (16)

- 絶縁樹脂層と、

前記絶縁樹脂層の一方の主表面に設けられた配線層と、

前記配線層と電気的に接続され、前記配線層から前記絶縁樹脂層側に突出している複数の突起電極と、

前記絶縁樹脂層の他方の主表面の、前記複数の突起電極のそれぞれに対応する位置に設けられ、前記突起電極の頂部面に対向する対向面を有する対向電極と、を備え、

前記複数の突起電極のうち、一部の突起電極の突出長さが、他の突起電極の突出長さよりも短く、当該一部の突起電極とこれに対応する対向電極とが容量結合し、前記他の突起電極とこれに対応する対向電極とが電気的に接続されていることを特徴とする素子搭載用基板。 - 前記対向電極の前記対向面と前記一部の突起電極の前記頂部面との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を有することを特徴とする請求項1に記載の素子搭載用基板。

- 前記絶縁樹脂層の他方の主表面に設けられた他の配線層を備え、

前記対向電極は、前記他の配線層の一部であることを特徴とする請求項1または2に記載の素子搭載用基板。 - 請求項1ないし3のいずれか1項に記載の素子搭載用基板と、

前記素子搭載用基板に搭載された半導体素子と、

を備えたことを特徴とする半導体モジュール。 - 請求項1または2に記載の素子搭載用基板と、

素子電極が設けられ、前記素子搭載用基板に搭載された半導体素子と、

を備え、

前記対向電極は、前記半導体素子の素子電極であることを特徴とする半導体モジュール。 - 請求項4または5に記載の半導体モジュールを搭載したことを特徴とする携帯機器。

- 複数の突起電極が突設された金属板を準備する工程と、

前記複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、

前記突起電極が絶縁樹脂層側に向くようにして前記金属板を絶縁樹脂層の一方の主表面に配置するとともに前記他の突起電極を前記絶縁樹脂層の他方の主表面から露出させ、また、前記突起電極の頂部面に対向する対向面を有する対向電極を前記絶縁樹脂層の他方の主表面の、前記複数の突起電極のそれぞれに対応する位置に配置し、前記一部の突起電極とこれに対応する対向電極とを容量結合させ、前記他の突起電極とこれに対応する対向電極とを電気的に接続させる結合工程と、

前記金属板を選択的に除去して配線層を形成する工程と、

を含むことを特徴とする素子搭載用基板の製造方法。 - 前記対向電極の前記対向面と前記一部の突起電極の前記頂部面との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含むことを特徴とする請求項7に記載の素子搭載用基板の製造方法。

- 前記絶縁樹脂層の他方の主表面に他の配線層を設ける工程を含み、

前記対向電極は、前記他の配線層の一部とすることを特徴とする請求項7または8に記載の素子搭載用基板の製造方法。 - 前記突出長さ調節工程において、

前記他の突起電極の頂部面に金属を被覆することで、前記一部の突起電極の突出長さを他の突起電極の突出長さよりも短くすることを特徴とする請求項7ないし9のいずれか1項に記載の素子搭載用基板の製造方法。 - 前記突出長さ調節工程において、

前記一部の突起電極の一部を除去することで、当該一部の突起電極の突出長さを前記他の突起電極の突出長さよりも短くすることを特徴とする請求項7ないし9のいずれか1項に記載の素子搭載用基板の製造方法。 - 請求項7ないし11のいずれか1項に記載の素子搭載用基板の製造方法により製造された素子搭載用基板に、半導体素子を搭載する工程を含むことを特徴とする半導体モジュールの製造方法。

- 複数の突起電極が突設された金属板を準備する工程と、

前記複数の突起電極のうち、一部の突起電極の突出長さを他の突起電極の突出長さよりも短くする突出長さ調節工程と、

前記突起電極が絶縁樹脂層側に向くようにして前記金属板を絶縁樹脂層の一方の主表面に配置するとともに前記他の突起電極を前記絶縁樹脂層の他方の主表面から露出させ、また、前記突起電極に対応する素子電極が設けられた半導体素子を前記絶縁樹脂層の他方の主表面に配置し、前記一部の突起電極とこれに対応する素子電極とを容量結合させ、前記他の突起電極とこれに対応する素子電極とを電気的に接続させる結合工程と、

前記金属板を選択的に除去して配線層を形成する工程と、

を含むことを特徴とする半導体モジュールの製造方法。 - 前記結合工程において、前記金属板および半導体素子を、前記絶縁樹脂層を介して圧着して、前記一部の突起電極とこれに対応する素子電極とを容量結合させ、前記他の突起電極とこれに対応する素子電極とを電気的に接続させることを特徴とする請求項13に記載の半導体モジュールの製造方法。

- 前記絶縁樹脂層は、加圧によって塑性流動を起こすことを特徴とする請求項14に記載の半導体モジュールの製造方法。

- 前記素子電極と前記一部の突起電極との間に、前記絶縁樹脂層よりも誘電率の大きい誘電膜層を設ける工程を含むことを特徴とする請求項13ないし15のいずれか1項に記載の半導体モジュールの製造方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007335819A JP2009158751A (ja) | 2007-12-27 | 2007-12-27 | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 |

| CN 200810191061 CN101494213A (zh) | 2007-12-27 | 2008-12-26 | 元件安装用基板、半导体组件及其制造方法及便携式设备 |

| US12/345,019 US20090168391A1 (en) | 2007-12-27 | 2008-12-29 | Substrate for mounting device and method for producing the same, semiconductor module and method for producing the same, and portable apparatus provided with the same |

| US12/900,175 US8438724B2 (en) | 2007-12-27 | 2010-10-07 | Method for producing substrate for mounting device and method for producing a semiconductor module |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007335819A JP2009158751A (ja) | 2007-12-27 | 2007-12-27 | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009158751A true JP2009158751A (ja) | 2009-07-16 |

| JP2009158751A5 JP2009158751A5 (ja) | 2010-05-13 |

Family

ID=40924721

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007335819A Pending JP2009158751A (ja) | 2007-12-27 | 2007-12-27 | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP2009158751A (ja) |

| CN (1) | CN101494213A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010087229A (ja) * | 2008-09-30 | 2010-04-15 | Sanyo Electric Co Ltd | 半導体モジュール、半導体モジュールの製造方法および携帯機器 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8592957B2 (en) * | 2009-08-18 | 2013-11-26 | Nec Corporation | Semiconductor device having shield layer and chip-side power supply terminal capacitively coupled therein |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004247483A (ja) * | 2003-02-13 | 2004-09-02 | Fujitsu Ltd | 回路基板の製造方法 |

| JP2004349361A (ja) * | 2003-05-21 | 2004-12-09 | Casio Comput Co Ltd | 半導体装置およびその製造方法 |

| JP2005197532A (ja) * | 2004-01-08 | 2005-07-21 | Nippon Mektron Ltd | 多層回路基板およびその製造方法ならびに回路基材 |

| JP2007059529A (ja) * | 2005-08-23 | 2007-03-08 | Nippon Mektron Ltd | 回路基板の製造方法 |

| JP2007123798A (ja) * | 2005-09-28 | 2007-05-17 | Kyocera Corp | 配線基板および電子装置 |

| WO2007063954A1 (ja) * | 2005-11-30 | 2007-06-07 | Sanyo Electric Co., Ltd. | 回路装置および回路装置の製造方法 |

-

2007

- 2007-12-27 JP JP2007335819A patent/JP2009158751A/ja active Pending

-

2008

- 2008-12-26 CN CN 200810191061 patent/CN101494213A/zh active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2004247483A (ja) * | 2003-02-13 | 2004-09-02 | Fujitsu Ltd | 回路基板の製造方法 |

| JP2004349361A (ja) * | 2003-05-21 | 2004-12-09 | Casio Comput Co Ltd | 半導体装置およびその製造方法 |

| JP2005197532A (ja) * | 2004-01-08 | 2005-07-21 | Nippon Mektron Ltd | 多層回路基板およびその製造方法ならびに回路基材 |

| JP2007059529A (ja) * | 2005-08-23 | 2007-03-08 | Nippon Mektron Ltd | 回路基板の製造方法 |

| JP2007123798A (ja) * | 2005-09-28 | 2007-05-17 | Kyocera Corp | 配線基板および電子装置 |

| WO2007063954A1 (ja) * | 2005-11-30 | 2007-06-07 | Sanyo Electric Co., Ltd. | 回路装置および回路装置の製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010087229A (ja) * | 2008-09-30 | 2010-04-15 | Sanyo Electric Co Ltd | 半導体モジュール、半導体モジュールの製造方法および携帯機器 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101494213A (zh) | 2009-07-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8309864B2 (en) | Device mounting board and manufacturing method therefor, and semiconductor module | |

| US8438724B2 (en) | Method for producing substrate for mounting device and method for producing a semiconductor module | |

| JP5091600B2 (ja) | 半導体モジュール、半導体モジュールの製造方法および携帯機器 | |

| JP2010262992A (ja) | 半導体モジュールおよび携帯機器 | |

| JPWO2012137548A1 (ja) | チップ部品内蔵樹脂多層基板およびその製造方法 | |

| US20100078813A1 (en) | Semiconductor module and method for manufacturing the semiconductor module | |

| JP2009182272A (ja) | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 | |

| JP4588046B2 (ja) | 回路装置およびその製造方法 | |

| JP2009246174A (ja) | 半導体モジュール、半導体モジュールの製造方法、ならびに携帯機器 | |

| JP5134899B2 (ja) | 半導体モジュール、半導体モジュールの製造方法および携帯機器 | |

| JP4588091B2 (ja) | 半導体モジュールの製造方法 | |

| US20090057903A1 (en) | Semiconductor module, method for manufacturing semiconductor modules, semiconductor apparatus, method for manufacturing semiconductor apparatuses, and portable device | |

| US8129846B2 (en) | Board adapted to mount an electronic device, semiconductor module and manufacturing method therefor, and portable device | |

| JP2009158830A (ja) | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 | |

| US20100140797A1 (en) | Device mounting board and method of manufacturing the board, semiconductor module and method of manufacturing the module | |

| JP5295211B2 (ja) | 半導体モジュールの製造方法 | |

| JP2009158751A (ja) | 素子搭載用基板およびその製造方法、半導体モジュールおよびその製造方法、ならびに携帯機器 | |

| JP2010040721A (ja) | 半導体モジュール、半導体装置、携帯機器、半導体モジュールの製造方法および半導体装置の製造方法 | |

| JP4806468B2 (ja) | 半導体モジュール | |

| JP5061010B2 (ja) | 半導体モジュール | |

| JP5306443B2 (ja) | 素子搭載用基板、素子搭載用基板の製造方法、半導体モジュールおよび半導体モジュールの製造方法 | |

| JP2009027042A (ja) | 回路モジュール、回路モジュールの製造方法および携帯機器 | |

| JP5022963B2 (ja) | 突起電極の構造、素子搭載用基板およびその製造方法、半導体モジュール、ならびに携帯機器 | |

| JP5121875B2 (ja) | 回路装置 | |

| JP2011082447A (ja) | 素子搭載用基板、半導体モジュールおよび携帯機器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100330 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100330 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100331 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100414 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100811 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100817 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101018 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101109 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110111 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110201 |