JP2008182163A - 配線基板及びその製造方法と半導体装置 - Google Patents

配線基板及びその製造方法と半導体装置 Download PDFInfo

- Publication number

- JP2008182163A JP2008182163A JP2007016246A JP2007016246A JP2008182163A JP 2008182163 A JP2008182163 A JP 2008182163A JP 2007016246 A JP2007016246 A JP 2007016246A JP 2007016246 A JP2007016246 A JP 2007016246A JP 2008182163 A JP2008182163 A JP 2008182163A

- Authority

- JP

- Japan

- Prior art keywords

- wiring

- wiring pattern

- lead frames

- interlayer connection

- resin

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

Abstract

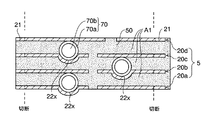

【解決手段】積層された多層構造の配線パターン22a〜22dは、その一部が垂直方向に屈曲して設けられた層間接続部23を備え、上下側の配線パターン22a〜22dが層間接続部23によって相互接続されており、多層構造の配線パターン22a〜22dの間にそれらを一体化する樹脂部50が充填されている。各配線パターン22a〜22dはリードフレームから形成される。

【選択図】図10

Description

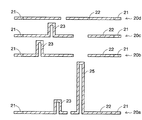

図2〜図8は本発明の第1実施形態の配線基板の製造方法を示す断面図、図9は本発明の第1実施形態の配線基板を示す断面図である。

図11〜図12は本発明の第2実施形態の配線基板の製造方法を示す断面図、図13は本発明の第2実施形態の配線基板を示す断面図である。

図14〜図17は本発明の第3実施形態の配線基板の製造方法を示す断面図、図18は本発明の第3実施形態の配線基板を示す断面図である。

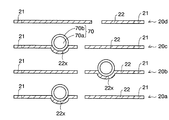

図19は本発明の第4実施形態の配線基板の製造方法を示す断面図、図20は本発明の第4実施形態の配線基板を示す断面図である。第4実施形態の特徴は、リードフレームの配線パターンの層間接続部をはんだを使用することなく配線パターンの開口部にはめ込んでかしめ接続することにある。本実施形態では、第2実施形態においてかしめ接続を行う形態を説明する。

Claims (10)

- 積層された多層構造の配線パターンであって、前記配線パターンはその一部が垂直方向に屈曲して設けられた層間接続部を備え、上下側の前記配線パターンが前記層間接続部によって相互接続された前記多層構造の配線パターンと、

前記多層構造の配線パターンの間に充填され、前記配線パターンを一体化する樹脂部とを有することを特徴とする配線基板。 - 前記配線パターンの前記層間接続部の先端部がはんだを介して他の前記配線パターンに接続されていることを特徴とする請求項1に記載の配線基板。

- 前記配線パターンの前記層間接続部の先端部が他の前記配線パターンの開口部にはめ込まれてかしめ接続されていることを特徴とする請求項1に記載の配線基板。

- 前記配線パターンは3層以上の多層配線パターンであって2層以上の前記樹脂部からなる層間絶縁部を有し、前記配線パターンの層間接続部は、2層以上の前記層間絶縁部を貫通して上下側の前記配線パターンを相互接続する積層貫通接続部を含むことを特徴とする請求項1乃至3のいずれか一項に記載の配線基板。

- 請求項1乃至4のいずれか一項の配線基板と、

前記配線基板の外面の前記配線パターンに接続されて実装された半導体チップとを有することを特徴とする半導体装置。 - 枠部に繋がる配線パターンを備えたリードフレームを複数用意する工程であって、前記複数のリードフレームは、前記配線パターンの一部が垂直方向に屈曲されて設けられた層間接続部を有する前記リードフレームを含み、

前記複数のリードフレームを重ねて積層し、上下側の前記リードフレームの配線パターンを前記層間接続部によって接続する工程と、

トランスファモールド法によって、前記リードフレームの間に樹脂を充填することにより、前記複数のリードフレームを一体化する樹脂部を形成する工程と、

前記積層されたリードフレームの前記枠部に対応する部分を切断する工程とを有することを特徴とする配線基板の製造方法。 - 前記層間接続部を有する前記配線パターンを備えたリードフレームは、

金属薄板を加工することにより、前記枠部に繋がる前記配線パターン形成する工程と、

前記配線パターンの一部を金型によって加工することにより、前記層間接続部を形成する工程とによって形成されることを特徴とする請求項6に記載の配線基板の製造方法。 - 前記上下側のリードフレームの配線パターンを層間接続部によって接続する工程において、

前記層間接続部の先端部をはんだを介して他の前記配線パターンに接続するか、あるいは、前記層間接続部の先端部を他の前記配線パターンの開口部にはめ込んでかしめ接続することを特徴とする請求項6又は7に記載の配線基板の製造方法。 - 枠部に繋がる配線パターンを備えたリードフレームを複数用意する工程と、

前記複数のリードフレームの配線パターンの間に導電性ボールを配置した状態で、前記複数のリードフレームを重ねて積層し、上下側の前記リードフレームの前記配線パターンを前記導電性ボールで接続する工程と、

トランスファモールド法によって、前記リードフレームの間に樹脂を充填することにより、前記複数のリードフレームを一体化する樹脂部を形成する工程と、

前記積層されたリードフレームの前記枠部に対応する部分を切断する工程とを有することを特徴とする配線基板の製造方法。 - 前記配線パターンの間に導電性ボールを配置する際に、前記配線パターンに設けられた凹部に前記導電性ボールを接合して配置することを特徴とする請求項9に記載の配線基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007016246A JP2008182163A (ja) | 2007-01-26 | 2007-01-26 | 配線基板及びその製造方法と半導体装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007016246A JP2008182163A (ja) | 2007-01-26 | 2007-01-26 | 配線基板及びその製造方法と半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2008182163A true JP2008182163A (ja) | 2008-08-07 |

| JP2008182163A5 JP2008182163A5 (ja) | 2010-02-12 |

Family

ID=39725810

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007016246A Pending JP2008182163A (ja) | 2007-01-26 | 2007-01-26 | 配線基板及びその製造方法と半導体装置 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2008182163A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010129998A (ja) * | 2008-11-28 | 2010-06-10 | Samsung Electro-Mechanics Co Ltd | 金属バンプを持つプリント基板及びその製造方法 |

| JP2011091111A (ja) * | 2009-10-20 | 2011-05-06 | Freesia Makurosu Kk | 電子部品搭載用基板の製造方法及び電子部品搭載用基板 |

| JP2013157566A (ja) * | 2012-01-31 | 2013-08-15 | Sumitomo Electric Printed Circuit Inc | プリント配線板及び該プリント配線板の製造方法 |

| JP7483595B2 (ja) | 2020-11-13 | 2024-05-15 | 新光電気工業株式会社 | 配線基板、電子装置及び配線基板の製造方法 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07170077A (ja) * | 1993-12-16 | 1995-07-04 | Hitachi Cable Ltd | 射出成形回路部品の製造方法 |

| JPH10322027A (ja) * | 1997-02-03 | 1998-12-04 | Ibiden Co Ltd | プリント配線板及びその製造方法 |

| JP2001076785A (ja) * | 1999-09-08 | 2001-03-23 | Sato Seiki:Kk | 電気的接合構造体並びにその成形方法 |

| JP2001077488A (ja) * | 1999-06-28 | 2001-03-23 | Matsushita Electric Ind Co Ltd | 回路基板とその製造方法およびリードフレーム |

| JP2001223289A (ja) * | 2000-02-08 | 2001-08-17 | Sony Corp | リードフレームと、その製造方法と、半導体集積回路装置と、その製造方法 |

| JP2005051155A (ja) * | 2003-07-31 | 2005-02-24 | Sony Corp | 半導体集積回路装置 |

-

2007

- 2007-01-26 JP JP2007016246A patent/JP2008182163A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07170077A (ja) * | 1993-12-16 | 1995-07-04 | Hitachi Cable Ltd | 射出成形回路部品の製造方法 |

| JPH10322027A (ja) * | 1997-02-03 | 1998-12-04 | Ibiden Co Ltd | プリント配線板及びその製造方法 |

| JP2001077488A (ja) * | 1999-06-28 | 2001-03-23 | Matsushita Electric Ind Co Ltd | 回路基板とその製造方法およびリードフレーム |

| JP2001076785A (ja) * | 1999-09-08 | 2001-03-23 | Sato Seiki:Kk | 電気的接合構造体並びにその成形方法 |

| JP2001223289A (ja) * | 2000-02-08 | 2001-08-17 | Sony Corp | リードフレームと、その製造方法と、半導体集積回路装置と、その製造方法 |

| JP2005051155A (ja) * | 2003-07-31 | 2005-02-24 | Sony Corp | 半導体集積回路装置 |

Cited By (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2010129998A (ja) * | 2008-11-28 | 2010-06-10 | Samsung Electro-Mechanics Co Ltd | 金属バンプを持つプリント基板及びその製造方法 |

| US8141241B2 (en) | 2008-11-28 | 2012-03-27 | Samsung Electro-Mechanics Co., Ltd. | Method of manufacturing a printed circuit board having metal bumps |

| US8464423B2 (en) | 2008-11-28 | 2013-06-18 | Samsung Electro-Mechanics Co., Ltd. | Method of manufacturing a printed circuit board having metal bumps |

| JP2011091111A (ja) * | 2009-10-20 | 2011-05-06 | Freesia Makurosu Kk | 電子部品搭載用基板の製造方法及び電子部品搭載用基板 |

| JP2013157566A (ja) * | 2012-01-31 | 2013-08-15 | Sumitomo Electric Printed Circuit Inc | プリント配線板及び該プリント配線板の製造方法 |

| JP7483595B2 (ja) | 2020-11-13 | 2024-05-15 | 新光電気工業株式会社 | 配線基板、電子装置及び配線基板の製造方法 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6076653B2 (ja) | 電子部品内蔵基板及び電子部品内蔵基板の製造方法 | |

| KR101690549B1 (ko) | 내장 칩 패키지 | |

| TWI436717B (zh) | 可內設功能元件之電路板及其製造方法 | |

| JP4271590B2 (ja) | 半導体装置及びその製造方法 | |

| JP5221315B2 (ja) | 配線基板及びその製造方法 | |

| KR100800478B1 (ko) | 적층형 반도체 패키지 및 그의 제조방법 | |

| JP4055717B2 (ja) | 半導体装置およびその製造方法 | |

| US7768119B2 (en) | Carrier structure embedded with semiconductor chip | |

| JP5132101B2 (ja) | スタックパッケージ構造体及びその製造に用いる単体パッケージと、それらの製造方法 | |

| JP5193898B2 (ja) | 半導体装置及び電子装置 | |

| US8209856B2 (en) | Printed wiring board and method for manufacturing the same | |

| US20080150164A1 (en) | Carrier structure embedded with semiconductor chips and method for manufacturing the same | |

| JP2006196860A (ja) | 半導体パッケージ及びその製造方法 | |

| JP2013535825A (ja) | エリアアレイユニットコネクタを備えるスタック可能モールド超小型電子パッケージ | |

| JP4489821B2 (ja) | 半導体装置及びその製造方法 | |

| JP5406572B2 (ja) | 電子部品内蔵配線基板及びその製造方法 | |

| JP2016021475A (ja) | プリント配線板 | |

| CN108461406B (zh) | 衬底结构、半导体封装结构及其制造方法 | |

| JP2009252942A (ja) | 部品内蔵配線板、部品内蔵配線板の製造方法 | |

| JP4074040B2 (ja) | 半導体モジュール | |

| JP2008182163A (ja) | 配線基板及びその製造方法と半導体装置 | |

| JP2008182039A (ja) | 多層配線板およびその製造方法 | |

| JP2003110091A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP5174355B2 (ja) | 配線基板及びその製造方法と半導体装置 | |

| JP4110161B2 (ja) | 半導体装置および半導体装置の製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091216 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20091216 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111108 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120228 |